# One-PLL General-Purpose Flash-Programmable Clock Generator

#### **Features**

- Integrated phase-locked loop (PLL)

- Commercial and Industrial operation

- Flash-programmable

- Field-programmable

- Low-skew, low-jitter, high-accuracy outputs

- 3.3 V operation with 2.5 V output option

- 16-pin TSSOP package (CY22050)

- Input frequency range:

- □ 8 MHz-30 MHz (external crystal)

- □ 1 MHz–133 MHz (driven clock)

- Output frequency range:

- □ Commercial temperature

- 8 kHz-200 MHz (3.3 V)

- 8 kHz-166.6 MHz (2.5 V)

- □ Industrial temperature

- 8 kHz-166.6 MHz (3.3 V)

- 8 kHz-150 MHz (2.5 V)

# **Functional Description**

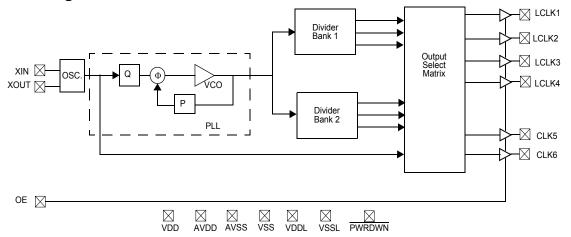

The CY22050 is programmable clock generator for use in networking, telecommunication, datacom, and other general-purpose applications. The CY22050 offers up to six configurable outputs in a 16-pin TSSOP, running off a 3.3 V power supply. The on-chip reference oscillator is designed to run off an 8–30-MHz crystal, or a 1–133-MHz external clock signal.

The CY22050 has a single PLL driving 6 programmable output clocks. The output clocks are derived from the PLL or the reference frequency (REF). Output post dividers are available for either. Four of the outputs can be set as 3.3 V or 2.5 V, for use in a wide variety of portable and low-power applications.

For a complete list of related documentation, click here.

# **Logic Block Diagram**

# Contents

| Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Pin Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

| Programming Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                         |

| Field Programming the CY22050F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                         |

| CyberClocks™ Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                         |

| CY3672 Development Kit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                         |

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Controlling Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

| CY22050 Frequency Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                         |

| CY22050 Frequency Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |

| The state of the s | 5                         |

| Clock Output Settings: Crosspoint Switch Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5<br>6                    |

| Clock Output Settings: Crosspoint Switch Matrix Reference Crystal Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>5</b><br><b>6</b><br>6 |

| Clock Output Settings: Crosspoint Switch Matrix  Reference Crystal Input  Crystal Drive Level and Power  Absolute Maximum Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6<br>6                    |

| Clock Output Settings: Crosspoint Switch Matrix  Reference Crystal Input  Crystal Drive Level and Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6<br>6<br>6               |

| Clock Output Settings: Crosspoint Switch Matrix  Reference Crystal Input  Crystal Drive Level and Power  Absolute Maximum Conditions  Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5<br>6<br>6<br>7          |

| lest Circuit                            | 9  |

|-----------------------------------------|----|

| Switching Waveforms                     | 9  |

| Ordering Information                    |    |

| Possible Configurations                 | 10 |

| Ordering Code Definitions               | 10 |

| 16-pin TSSOP Package Characteristics    | 11 |

| Package Drawing and Dimensions          | 11 |

| Acronyms                                | 12 |

| Document Conventions                    | 12 |

| Units of Measure                        | 12 |

| Document History Page                   | 13 |

| Sales, Solutions, and Legal Information | 15 |

| Worldwide Sales and Design Support      | 15 |

| Products                                | 15 |

| PSoC® Solutions                         | 15 |

| Cypress Developer Community             | 15 |

| Technical Support                       | 15 |

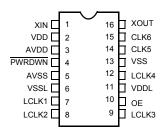

# **Pin Configuration**

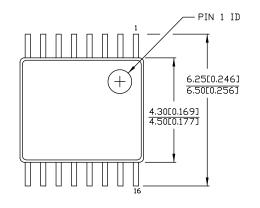

Figure 1. 16-pin TSSOP pinout

# **Pin Definitions**

| Name       | Pin Number | Description                                                                                                                                                                                                                              |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN        | 1          | Reference Input. Driven by a crystal (8 MHz–30 MHz) or external clock (1 MHz–133 MHz). Programmable input load capacitors allow for maximum flexibility in selecting a crystal, based on manufacturer, process, performance, or quality. |

| VDD        | 2          | 3.3 V voltage supply                                                                                                                                                                                                                     |

| AVDD       | 3          | 3.3 V analog voltage supply                                                                                                                                                                                                              |

| PWRDWN [1] | 4          | Power Down. When pin 4 is driven LOW, the CY22050 goes into shut down mode.                                                                                                                                                              |

| AVSS       | 5          | Analog ground                                                                                                                                                                                                                            |

| VSSL       | 6          | LCLK ground                                                                                                                                                                                                                              |

| LCLK1      | 7          | Configurable clock output 1 at V <sub>DDL</sub> level (3.3 V or 2.5 V)                                                                                                                                                                   |

| LCLK2      | 8          | Configurable clock output 2 at V <sub>DDL</sub> level (3.3 V or 2.5 V)                                                                                                                                                                   |

| LCLK3      | 9          | Configurable clock output 3 at V <sub>DDL</sub> level (3.3 V or 2.5 V)                                                                                                                                                                   |

| OE [1]     | 10         | Output Enable. When pin 10 is driven LOW, all outputs are three-stated.                                                                                                                                                                  |

| VDDL       | 11         | LCLK voltage supply (2.5 V or 3.3 V)                                                                                                                                                                                                     |

| LCLK4      | 12         | Configurable clock output 4 at V <sub>DDL</sub> level (3.3 V or 2.5 V)                                                                                                                                                                   |

| VSS        | 13         | Ground                                                                                                                                                                                                                                   |

| CLK5       | 14         | Configurable clock output 5 (3.3 V)                                                                                                                                                                                                      |

| CLK6       | 15         | Configurable clock output 6 (3.3 V)                                                                                                                                                                                                      |

| XOUT [2]   | 16         | Reference output                                                                                                                                                                                                                         |

Notes

1. The CY22050 has no internal pull up or pull down resistors. PWRDWN and OE pins need to be driven as appropriate or tied to power or ground.

2. Float XOUT if XIN is driven by an external clock source.

# **Programming Description**

#### Field Programming the CY22050F

The CY22050 is programmed at the package level, that is, in a programmer socket, prior to installation on a PCB. The CY22050 is flash-technology based, so the parts can be reprogrammed up to 100 times. This allows for fast and easy design changes and product updates, and eliminates any issues with old and out-of-date inventory.

Samples and small prototype quantities can be programmed on the CY3672 programmer. Cypress's value-added distribution partners and third-party programming systems from BP Microsystems, HiLo Systems, and others are available for large-production quantities.

#### CyberClocks™ Software

CyberClocks is an easy-to-use software application that allows the user to custom-configure the CY22050. Within CyberClocks, select the CyClocksRT™ tool. Users can specify the REF, PLL frequency, output frequencies and/or post-dividers, and different functional options. CyClocksRT outputs an industry-standard JEDEC file used for programming the CY22050.

CyClocksRT can be downloaded free of charge from the Cypress website at http://www.cypress.com. Install and run it on any PC running the Windows operating system.

#### CY3672 Development Kit

The Cypress CY3672 Development Kit comes complete with everything needed to design with the CY22050 and program samples and small prototype quantities. The kit comes with the latest version of CyClocksRT and a small portable programmer that connects to a PC for on-the-fly programming of custom frequencies.

The JEDEC file output of CyClocksRT can be downloaded to the portable programmer for small-volume programming, or for use with a production programming system for larger volumes.

### **Applications**

#### **Controlling Jitter**

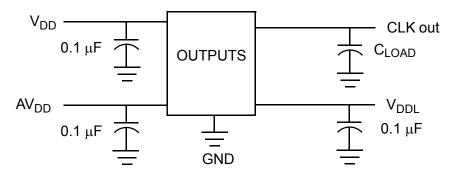

Jitter is defined in many ways, including: phase noise, long-term jitter, cycle-to-cycle jitter, period jitter, absolute jitter, and deterministic jitter. These jitter terms are usually given in terms of rms, peak-to-peak, or in the case of phase noise dBC/Hz with respect to the fundamental frequency. Actual jitter is dependent on XIN jitter and edge rate, number of active outputs, output frequencies,  $V_{DDL}$  (2.5 V or 3.3 V), temperature, and output load.

Power supply noise and clock output loading are two major system sources of clock jitter. Power supply noise can be mitigated by proper power supply decoupling (0.1-µF ceramic cap) of the clock and ensuring a low-impedance ground to the chip. Reducing capacitive clock output loading to a minimum lowers current spikes on the clock edges and thus reduces jitter.

Reducing the total number of active outputs also reduce jitter in a linear fashion. However, it is better to use two outputs to drive two loads than one output to drive two loads.

The rate and magnitude that the PLL corrects the VCO frequency is directly related to jitter performance. If the rate is too slow, then long term jitter and phase noise is poor. Therefore, to improve long-term jitter and phase noise, reducing Q to a minimum is advisable. This technique increases the speed of the phase frequency detector, which in turn drives the input voltage of the VCO. In a similar manner, increasing P until the VCO is near its maximum rated speed also decreases long term jitter and phase noise. For example: input reference of 12 MHz; desired output frequency of 33.3 MHz. One might arrive at the following solution: Set Q = 3, P = 25, Post Div = 3. However, the best jitter results are Q = 2, P = 50, Post Div = 9.

For additional information, refer to the application note, "Jitter in PLL-based Systems: Causes, Effects, and Solutions," available at <a href="http://www.cypress.com">http://www.cypress.com</a> (click on "Application Notes"), or contact your local Cypress Field Applications Engineer.

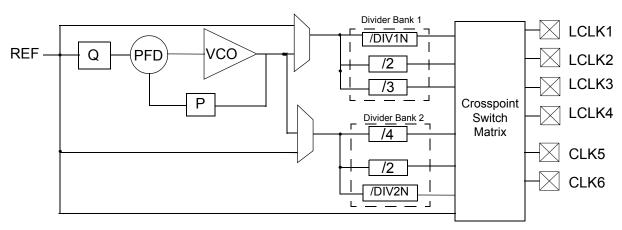

# CY22050 Frequency Calculation

The CY22050 is an extremely flexible clock generator with up to six individual outputs, generated from an integrated PLL.

There are four variables used to determine the final output frequency. They are: the input REF, the P and Q dividers, and the post divider. The three basic formulas for determining the final output frequency of a CY22150-based design are:

- CLK = ((REF \* P)/Q)/Post Divider

- CLK = REF/Post Divider

- CLK = REF

The basic PLL block diagram is shown in Figure 2. Each of the six clock outputs has a total of seven output options available to it. There are six post divider options: /2 (two of these), /3, /4, /DIV1N, and DIV2N. DIV1N and DIV2N are separately calculated and can be independent of each other. The post divider options can be applied to the calculated PLL frequency or to the REF directly.

In addition to the six post divider options, the seventh option bypasses the PLL and passes the REF directly to the crosspoint switch matrix.

Figure 2. Basic PLL Block Diagram

# **Clock Output Settings: Crosspoint Switch Matrix**

Each of the six clock outputs can come from any of seven unique frequency sources. The crosspoint switch matrix defines which

source is attached to each individual clock output. Although it may seem that there are an unlimited number of divider options, there are several rules that must be taken into account when selecting divider options.

**Table 1. Clock Output Definition**

| Clock Output Divider | Definition and Notes                                                                                                                                           |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| None                 | Clock output source is the reference input frequency.                                                                                                          |

| /DIV1N               | Clock output uses a generated /DIV1N option from Divider Bank 1. Allowable values for DIV1N are 4 to 130. If Divider Bank 1 is not being used, set DIV1N to 8. |

| /2                   | Clock output uses a fixed /2 option from Divider Bank 1. If this option is used, DIV1N must be divisible by 4.                                                 |

| /3                   | Clock output uses a fixed /3 option from Divider Bank 1. If this option is used, set DIV1N to 6.                                                               |

| /DIV2N               | Clock output uses a generated /DIV2N option from Divider Bank 2. Allowable values for DIV2N are 4 to 130. If Divider Bank 2 is not being used, set DIV2N to 8. |

| /2                   | Clock output uses a fixed /2 option from Divider Bank 2. If this option is used, DIV2N must be divisible by 4.                                                 |

| /4                   | Clock output 2 uses a fixed /4 option from Divider Bank 2. If this option is used, DIV2N must be divisible by 8.                                               |

# **Reference Crystal Input**

The input crystal oscillator of the CY22050 is an important feature because of the flexibility it allows the user in selecting a crystal as a reference clock source. The oscillator inverter has programmable gain, allowing for maximum compatibility with a reference crystal, based on manufacturer, process, performance, and quality.

The value of the input load capacitors is determined by eight bits in a programmable register. Total load capacitance is determined by the formula:

CapLoad =

$$(C_L - C_{BRD} - C_{CHIP})/0.09375 pF$$

In CyClocksRT, enter the crystal capacitance ( $C_L$ ). The value of CapLoad is determined automatically and programmed into the CY22050.

If you require greater control over the CapLoad value, consider using the CY22150 for serial configuration and control of the input load capacitors. For an external clock source, the default is 0

Input load capacitors are placed on the CY22050 die to reduce external component cost. These capacitors are true parallel-plate capacitors, designed to reduce the frequency shift that occurs when non-linear load capacitance is affected by load, bias, supply, and temperature changes.

#### **Crystal Drive Level and Power**

Crystals are specified to accept a maximum drive level. Generally, larger crystals can accept more power. The drive level specification in the table below is a general upper bound for the power driven by the oscillator circuit in the CY22050.

For a given voltage swing, power dissipation in the crystal is proportional to ESR and proportional to the square of the crystal frequency. (Note that actual ESR is sometimes much less than the value specified by the crystal manufacturer.) Power is also almost proportional to the square of  $C_{\rm I}$ .

Power can be reduced to less than the DL specification in the table below by selecting a reduced frequency crystal with low  $C_L$  and low  $R_1$  (ESR).

#### **Absolute Maximum Conditions**

| Parameter      | Description                                           | Min                   | Max                   | Unit |

|----------------|-------------------------------------------------------|-----------------------|-----------------------|------|

| $V_{DD}$       | Supply Voltage                                        | -0.5                  | 7.0                   | V    |

| $V_{DDL}$      | I/O Supply Voltage                                    | -0.5                  | 7.0                   | V    |

| T <sub>S</sub> | Storage Temperature [3]                               | -65                   | 125                   | °C   |

| TJ             | Junction Temperature                                  | _                     | 125                   | °C   |

|                | Package Power Dissipation—Commercial Temp             | _                     | 450                   | mW   |

|                | Package Power Dissipation—Industrial Temp             | _                     | 380                   | mW   |

|                | Digital Inputs                                        | $AV_{SS} - 0.3$       | $AV_{DD} + 0.3$       | V    |

|                | Digital Outputs referred to V <sub>DD</sub>           | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V    |

|                | Digital Outputs referred to V <sub>DDL</sub>          | $V_{SS} - 0.3$        | V <sub>DDL</sub> +0.3 | V    |

| ESD            | Static Discharge Voltage per MIL-STD-833, Method 3015 | _                     | 2000                  | V    |

3. Rated for 10 years

# **Recommended Operating Conditions**

| Parameter          | Description                                                                                         | Min   | Тур | Max   | Unit |

|--------------------|-----------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| $V_{DD}$           | Operating Voltage                                                                                   | 3.135 | 3.3 | 3.465 | V    |

| VDDL <sub>HI</sub> | Operating Voltage                                                                                   | 3.135 | 3.3 | 3.465 | V    |

| VDDL <sub>LO</sub> | Operating Voltage                                                                                   | 2.375 | 2.5 | 2.625 | V    |

| T <sub>AC</sub>    | Ambient Commercial Temp                                                                             | 0     | _   | 70    | °C   |

| T <sub>AI</sub>    | Ambient Industrial Temp                                                                             | -40   | _   | 85    | °C   |

| C <sub>LOAD</sub>  | Max. Load Capacitance V <sub>DD</sub> /V <sub>DDL</sub> = 3.3 V                                     | _     | _   | 15    | pF   |

| C <sub>LOAD</sub>  | Max. Load Capacitance V <sub>DDL</sub> = 2.5 V                                                      | _     | _   | 15    | pF   |

| f <sub>REFD</sub>  | Driven REF                                                                                          | 1     | _   | 133   | MHz  |

| f <sub>REFC</sub>  | Crystal REF                                                                                         | 8     | _   | 30    | MHz  |

| t <sub>PU</sub>    | Power up time for all $V_{DD}$ s to reach minimum specified voltage (power ramps must be monotonic) | 0.05  | _   | 500   | ms   |

# **Recommended Crystal Specifications**

| Parameter         | Description                        | Comments                             | Min | Тур | Max | Unit |

|-------------------|------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>NOM</sub>  | Nominal crystal frequency          | Parallel resonance, fundamental mode | 8   | _   | 30  | MHz  |

| C <sub>LNOM</sub> | Nominal load capacitance           |                                      | 10  | _   | 20  | pF   |

| R <sub>1</sub>    | Equivalent series resistance (ESR) | Fundamental mode                     | _   | _   | 50  | Ω    |

| DL                | Crystal drive level                | No external series resistor assumed  | _   | 0.5 | 2   | mW   |

## **DC Electrical Characteristics**

| Parameter [4]                          | Description         | Condition                                                           | Min | Тур | Max | Unit     |

|----------------------------------------|---------------------|---------------------------------------------------------------------|-----|-----|-----|----------|

| I <sub>OH3.3</sub>                     | Output High Current | $V_{OH} = V_{DD} - 0.5 \text{ V}, V_{DD} / V_{DDL} = 3.3 \text{ V}$ | 12  | 24  | _   | mA       |

| I <sub>OL3.3</sub>                     | Output Low Current  | $V_{OL} = 0.5 \text{ V}, V_{DD}/V_{DDL} = 3.3 \text{ V}$            | 12  | 24  | _   | mA       |

| I <sub>OH2.5</sub>                     | Output High Current | $V_{OH} = V_{DDL} - 0.5 \text{ V}, V_{DDL} = 2.5 \text{ V}$         | 8   | 16  | _   | mA       |

| I <sub>OL2.5</sub>                     | Output Low Current  | V <sub>OL</sub> = 0.5 V, V <sub>DDL</sub> = 2.5 V                   | 8   | 16  | _   | mA       |

| V <sub>IH</sub>                        | Input High Voltage  | CMOS levels, 70% of V <sub>DD</sub>                                 | 0.7 | _   | 1.0 | $V_{DD}$ |

| V <sub>IL</sub>                        | Input Low Voltage   | CMOS levels, 30% of V <sub>DD</sub>                                 | 0   | _   | 0.3 | $V_{DD}$ |

| I <sub>VDD</sub> <sup>[5, 6]</sup>     | Supply Current      | AV <sub>DD</sub> /V <sub>DD</sub> Current                           | _   | 45  | _   | mA       |

| I <sub>VDDL3.3</sub> [5, 6]            | Supply Current      | V <sub>DDL</sub> Current (V <sub>DDL</sub> = 3.465 V)               | -   | 25  | _   | mA       |

| I <sub>VDDL2.5</sub> <sup>[5, 6]</sup> | Supply Current      | V <sub>DDL</sub> Current (V <sub>DDL</sub> = 2.625 V)               | _   | 17  | _   | mA       |

| I <sub>DDS</sub>                       | Power Down Current  | $V_{DD} = V_{DDL} = AV_{DD} = 3.465 \text{ V}$                      | _   | _   | 50  | μА       |

| I <sub>OHZ</sub><br>I <sub>OLZ</sub>   | Output Leakage      | $V_{DD} = V_{DDL} = AV_{DD} = 3.465 V$                              | -   | _   | 10  | μА       |

## **AC Electrical Characteristics**

| Parameter [4]                 | Description                                       | Condition                                                                           | Min           | Тур  | Max   | Unit |

|-------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|---------------|------|-------|------|

| t <sub>1</sub>                | Output frequency,                                 | Clock output limit, 3.3 V                                                           | 0.008 (8 kHz) | -    | 200   | MHz  |

|                               | commercial temperature                            | Clock output limit, 2.5 V                                                           | 0.008 (8 kHz) | _    | 166.6 | MHz  |

|                               | Output frequency,                                 | Clock output limit, 3.3 V                                                           | 0.008 (8 kHz) | _    | 166.6 | MHz  |

|                               | industrial temperature                            | Clock output limit, 2.5 V                                                           | 0.008 (8 kHz) | _    | 150   | MHz  |

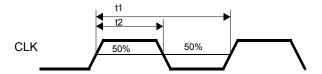

| t <sub>2</sub>                | Output duty cycle                                 | Duty cycle is defined in Figure 4, $t_1/t_2$ , $t_{OUT} > 166$ MHz, 50% of $V_{DD}$ | 40            | 50   | 60    | %    |

|                               |                                                   | Duty cycle is defined in Figure 4, $t_1/t_2$ , $t_{OUT}$ < 166 MHz, 50% of $V_{DD}$ | 45            | 50   | 55    | %    |

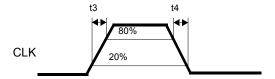

| t <sub>3LO</sub>              | Rising edge slew rate (V <sub>DDL</sub> = 2.5 V)  | Output clock rise time, 20%–80% of $V_{DDL}$ , defined in Figure 5                  | 0.6           | 1.2  | _     | V/ns |

| t <sub>4LO</sub>              | Falling edge slew rate (V <sub>DDL</sub> = 2.5 V) | Output clock fall time, 80%–20% of $V_{DDL}$ , defined in Figure 5                  | 0.6           | 1.2  | _     | V/ns |

| t <sub>3HI</sub>              | Rising edge slew rate (V <sub>DDL</sub> = 3.3 V)  | Output clock rise time, 20%–80% of $V_{DD}/V_{DDL}$ , defined in Figure 5           | 0.8           | 1.4  | _     | V/ns |

| t <sub>4HI</sub>              | Falling edge slew rate (V <sub>DDL</sub> = 3.3 V) | Output clock fall time, $80\%$ – $20\%$ of $V_{DD}/V_{DDL}$ , defined in Figure 5   | 0.8           | 1.4  | _     | V/ns |

| t <sub>5</sub> <sup>[7]</sup> | Skew                                              | Output-output skew between related outputs                                          | -             | -    | 250   | ps   |

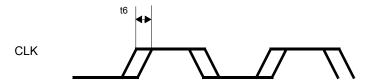

| t <sub>6</sub> <sup>[8]</sup> | Clock jitter                                      | Peak-to-peak period jitter (see Figure 6)                                           | _             | 250  | _     | ps   |

| t <sub>10</sub>               | PLL lock time                                     |                                                                                     | _             | 0.30 | 3     | ms   |

#### Notes

- 4. Not 100% tested, guaranteed by design.

- I<sub>VDD</sub> currents specified for two CLK outputs running at 125 MHz, two LCLK outputs running at 80 MHz, and two LCLK outputs running at 66.6 MHz. All outputs are loaded with 15 pF.

- Use CyClocksRT to calculate actual I<sub>VDD</sub> and I<sub>VDDL</sub> for specific output frequency configurations.

Skew value guaranteed when outputs are generated from the same divider bank. See Logic Block Diagram for more information.

- Jitter measurement will vary. Actual jitter is dependent on X<sub>IN</sub> jitter and edge rate, number of active outputs, output frequencies, V<sub>DDL</sub> (2.5 V or 3.3 V), temperature, and output load. For more information, refer to the application note, "Jitter in PLL-based Systems: Causes, Effects, and Solutions," available at http://www.cypress.com, or contact your local Cypress Field Applications Engineer.

Document Number: 38-07006 Rev. \*O

# **Test Circuit**

Figure 3. Test Circuit

# **Switching Waveforms**

Figure 4. Duty Cycle Definition: DC = t2/t1

Figure 5. Rise and Fall Time Definitions

Figure 6. Peak-to-Peak Jitter

# **Ordering Information**

| Ordering Code | Package Type                                      | Temperature Operating Range  | Operating Voltage |  |  |  |

|---------------|---------------------------------------------------|------------------------------|-------------------|--|--|--|

| CY22050KFI    | 16-pin TSSOP                                      | Industrial (–40 °C to 85 °C) | 3.3 V             |  |  |  |

| Pb-free       | Pb-free                                           |                              |                   |  |  |  |

| CY22050KFZXC  | 16-pin TSSOP                                      | Commercial (0 °C to 70 °C)   | 3.3 V             |  |  |  |

| CY22050KFZXCT | 16-pin TSSOP – Tape and Reel                      |                              |                   |  |  |  |

| CY22050KFZXI  | 16-pin TSSOP                                      | Industrial (–40 °C to 85 °C) | 3.3 V             |  |  |  |

| Programmer    |                                                   |                              |                   |  |  |  |

| CY3672-USB    | Programming Kit                                   |                              |                   |  |  |  |

| CY3695        | CY22050F, CY22050KF Adapter for CY3672 Programmer |                              |                   |  |  |  |

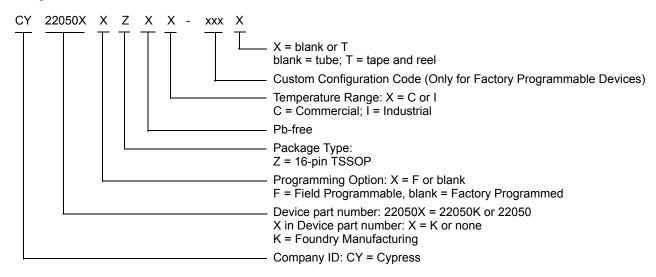

Some product offerings are factory programmed customer specific devices with customized part numbers. The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE or Sales Representative for more information.

## **Possible Configurations**

| Ordering Code                  | Package Type                 | Temperature Operating Range  | Operating Voltage |

|--------------------------------|------------------------------|------------------------------|-------------------|

| CY22050ZXC-xxx [9]             | 16-pin TSSOP                 | Commercial (0 °C to 70 °C)   | 3.3 V             |

| CY22050ZXC-xxxT [9]            | 16-pin TSSOP – Tape and Reel | Commercial (0 °C to 70 °C)   | 3.3 V             |

| CY22050ZXI-xxx [9]             | 16-pin TSSOP                 | Industrial (–40 °C to 85 °C) | 3.3 V             |

| CY22050ZXI-xxxT [9]            | 16-pin TSSOP – Tape and Reel | Industrial (–40 °C to 85 °C) | 3.3 V             |

| CY22050KZXC-xxx [9]            | 16-pin TSSOP                 | Commercial (0 °C to 70 °C)   | 3.3 V             |

| CY22050KZXC-xxxT [9]           | 16-pin TSSOP – Tape and Reel | Commercial (0 °C to 70 °C)   | 3.3 V             |

| CY22050KZXI-xxx <sup>[9]</sup> | 16-pin TSSOP                 | Industrial (–40 °C to 85 °C) | 3.3 V             |

| CY22050KZXI-xxxT [9]           | 16-pin TSSOP – Tape and Reel | Industrial (–40 °C to 85 °C) | 3.3 V             |

### **Ordering Code Definitions**

#### Note

Document Number: 38-07006 Rev. \*O Page 10 of 15

These are factory-programmed configurations. Factory programming is available for high-volume design opportunities of 100 Ku/year or more in production. For more details, contact your local Cypress field application engineer or Cypress sales representative.

# 16-pin TSSOP Package Characteristics

| Parameter     | Name             | Value  | Unit        |

|---------------|------------------|--------|-------------|

| $\theta_{JA}$ | theta JA         | 115    | °C/W        |

| Complexity    | Transistor Count | 74,600 | Transistors |

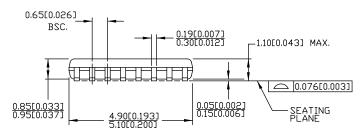

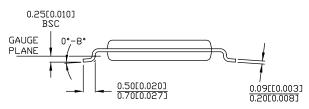

# **Package Drawing and Dimensions**

Figure 7. 16-pin TSSOP 4.40 mm Body Z16.173/ZZ16.173 Package Outline, 51-85091

DIMENSIONS IN MM[INCHES] MIN. MAX.

REFERENCE JEDEC MO-153

PACKAGE WEIGHT 0.05gms

| PART #   |                |  |  |

|----------|----------------|--|--|

| Z16.173  | STANDARD PKG.  |  |  |

| ZZ16.173 | LEAD FREE PKG. |  |  |

51-85091 \*E

Document Number: 38-07006 Rev. \*O

# Acronyms

| Acronym | Description                                |  |  |  |  |

|---------|--------------------------------------------|--|--|--|--|

| ESR     | Equivalent Series Resistance               |  |  |  |  |

| FAE     | Field Application Engineer                 |  |  |  |  |

| I/O     | Input/Output                               |  |  |  |  |

| JEDEC   | Joint Electron Devices Engineering Council |  |  |  |  |

| OE      | Output Enable                              |  |  |  |  |

| PC      | Personal Computer                          |  |  |  |  |

| PCB     | Printed Circuit Board                      |  |  |  |  |

| PLL     | Phase-Locked Loop                          |  |  |  |  |

| TSSOP   | Thin Shrunk Small Outline Package          |  |  |  |  |

| VCO     | Voltage Controlled Oscillator              |  |  |  |  |

# **Document Conventions**

# **Units of Measure**

| Symbol | Unit of Measure              |  |  |  |

|--------|------------------------------|--|--|--|

| °C     | degree Celsius               |  |  |  |

| dBC    | decibels relative to carrier |  |  |  |

| Hz     | hertz                        |  |  |  |

| kHz    | kilohertz                    |  |  |  |

| MHz    | megahertz                    |  |  |  |

| μΑ     | microampere                  |  |  |  |

| μF     | microfarad                   |  |  |  |

| mA     | milliampere                  |  |  |  |

| mm     | millimeter                   |  |  |  |

| ms     | millisecond                  |  |  |  |

| mW     | milliwatt                    |  |  |  |

| ns     | nanosecond                   |  |  |  |

| Ω      | ohm                          |  |  |  |

| %      | percent                      |  |  |  |

| pF     | picofarad                    |  |  |  |

| ps     | picosecond                   |  |  |  |

| V      | volt                         |  |  |  |

| W      | watt                         |  |  |  |

# **Document History Page**

| Document Number: 38-07006  Pour ECN Orig. of Submission Description of Change |         |        |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------------------------------------------------|---------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev.                                                                          | ECN     | Change | Date       | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| **                                                                            | 108185  | CKN    | 08/08/01   | New data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| *A                                                                            | 110054  | CKN    | 03/04/02   | Changed status from Preliminary to Final.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| *B                                                                            | 121862  | RBI    | 12/14/02   | Power up requirements added to Operating Conditions Information.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| *C                                                                            | 310575  | RGL    | 01/20/05   | Added Lead-free devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *D                                                                            | 314233  | RGL    | 01/31/05   | Removed the Tape and Reel devices in the non-dash parts.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *E                                                                            | 2440826 | AESA   | 05/15/08   | Added Note "Not recommended for new designs." and "38-07409, CY3672 PTG Programming Kit". Corrected "FTG" to "PTG" in Ordering information table. Added part numbers CY22050KFC, CY22050KFI, CY22050KFZXC, CY22050KFZXI, CY22050KZXC-xxx, CY22050KZXC-xxxT, CY22050KZXI-xxx, and CY22050KZXI-xxxT in ordering information table. Changed Lead-Free to Pb-free. Updated to new template.                                                                                          |  |

| *F                                                                            | 2642064 | KVM    | 01/21/09   | Added CY220501 to title. Added CY220501KFZXI to ordering table.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| *G                                                                            | 2743347 | KVM    | 07/24/09   | Revised the Device Selection table on page 1 and renamed it. Updates to programmer and software descriptions. Clarified that I <sub>VDD</sub> and I <sub>VDDL</sub> are for loaded outputs. Updated footnotes to show that the standard part numbers are now with a "K Changed CY3672 part number to CY3672-USB, changed CY3672ADP000 to CY3695, and repositioned them in the Ordering Information table. Deleted part numbers CY22050ZC-xxxT, CY22050ZI-xxx and CY22050ZI-xxxT. |  |

| *H                                                                            | 2899683 | KVM    | 03/26/10   | Updated Ordering Information: Removed inactive parts from ordering information table. Updated Possible Configurations: Moved xxx parts to 'Possible Configurations' table. Updated Package Drawing and Dimensions.                                                                                                                                                                                                                                                               |  |

| *                                                                             | 3167517 | BASH   | 02/09/11   | Add crystal parameter table on page 6, ordering code definition, acronym and units tables. Remove references to FTG.  Deleted table 1 from page 1, device selection: this table provides no additional information. Consolidated its input/output range information as a "features" bullet.  Removed "benefits" section.  Updated footnote#9 on page 8.                                                                                                                          |  |

| *J                                                                            | 3210223 | BASH   | 03/30/2011 | Updated Ordering Information (Removed CY220501KFZXI, CY22050KZXC-139 and CY22050KZXC-139T). Updated Package Drawing and Dimensions (spec 51-85091 (Changed revision from *B to *C)).                                                                                                                                                                                                                                                                                             |  |

| *K                                                                            | 3366417 | PURU   | 09/08/2011 | Updated to new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| *L                                                                            | 3776296 | PURU   | 10/12/2012 | Updated Ordering Information (Updated part numbers (Added a new MPN namely CY22050KFZXCT)). Updated Package Drawing and Dimensions (spec 51-85091 (Changed revision from *C to *D)).                                                                                                                                                                                                                                                                                             |  |

# **Document History Page (continued)**

| Rev. | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                    |