The following document contains information on Cypress products. Although the document is marked with the name "Spansion" and "Fujitsu", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

#### **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

#### **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress (NASDAQ: CY) delivers high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. With a broad, differentiated product portfolio that includes NOR flash memories, F-RAM™ and SRAM, Traveo™ microcontrollers, the industry's only PSoC® programmable system-on-chip solutions, analog and PMIC Power Management ICs, CapSense® capacitive touch-sensing controllers, and Wireless BLE Bluetooth® Low-Energy and USB connectivity solutions, Cypress is committed to providing its customers worldwide with consistent innovation, best-in-class support and exceptional system value.

# Linear IC Converter

# D/A Converter for Digital Tuning

(12-channel, 8-bit, on-chip OP amp., low-voltage)

# **MB88146A**

#### **■ DESCRIPTION**

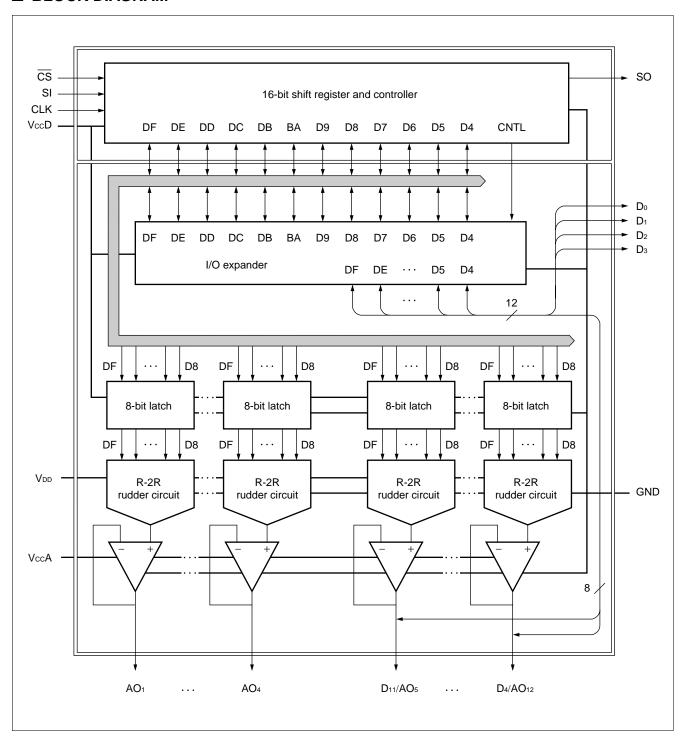

The MB88146A is an 8-bit D/A converter with twelve built-in channels. The 12 analog outputs each have a built-in OP amplifier with large current drive-capability.

The data input/output format is CS (chip select) with serial bus connection available.

A built-in 12-bit I/O expander enables serial  $\leftrightarrow$  parallel conversion (8 of the 12 bits can also be used for analog output).

This product can be used for microcontroller port expansion, electronic level adjustment, replacement of semifixed resistance for tuning, etc.

#### **■ FEATURES**

- Ultra low power consumption (1.2 mW/chl: typical)

- Ultra compact package

- Built-in 12-channel R-2R type 8-bit D/A converter

- Built-in 12-bit I/O expander (8 bits also function as analog output)

- Built-in analog output amplifier (sink current 1.0 mA maximum, source current 1.0 mA maximum)

- Built-in power-on detection circuit (initialized at detection of VccD power-on)

- MCU interface compatible with 3 V to 5 V systems

- Power divided into MCU interface power supply (VccD) and OP amplifier power supply (VccA), D/A converter power supply (VccD)

- · Analog output capability from 0 V to VccA

- Serial data I/O operates to maximum of 2.5 MHz (in cascade connection, up to 2.5 MHz when VccD = 5 V, up to 1.5 MHz when VccD = 3 V)

- CMOS process

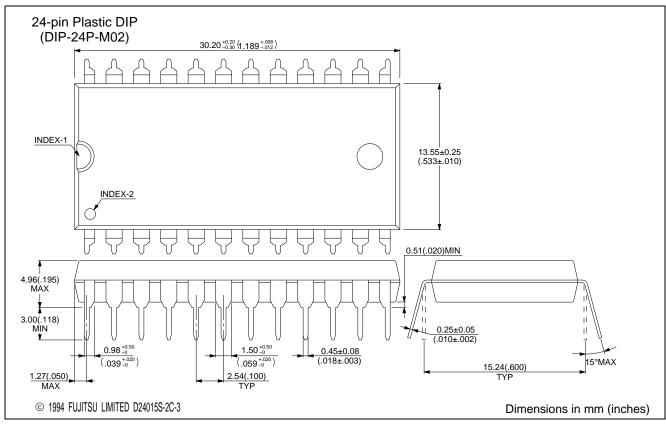

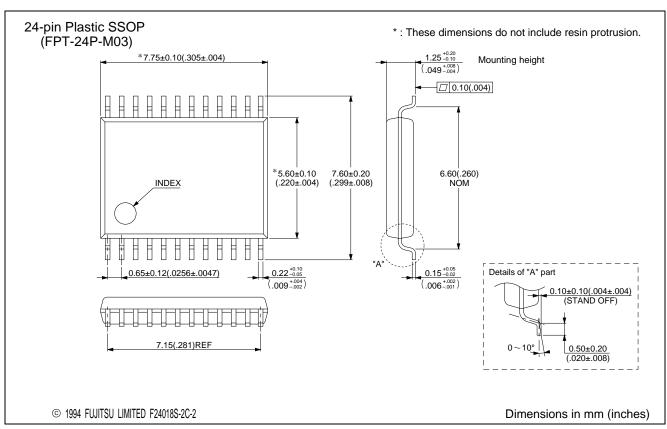

- Choice of two packages: SDIP-24 pin and SSOP-24 pin.

#### **■ PACKAGES**

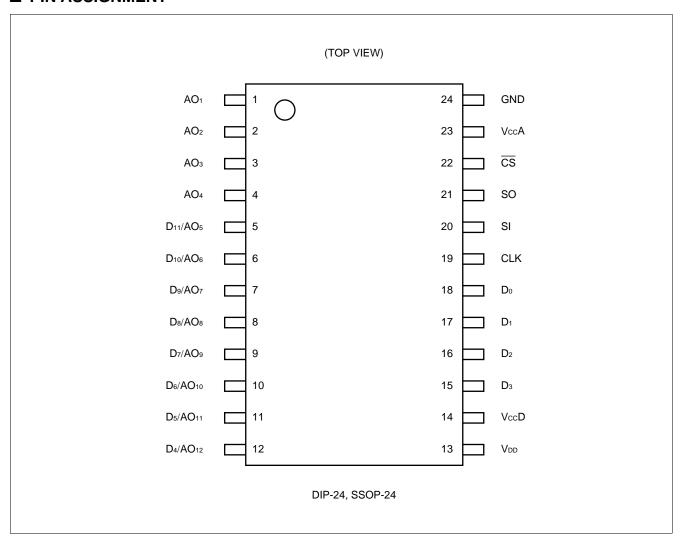

#### **■ PIN ASSIGNMENT**

#### **■ PIN DESCRIPTION**

| Pin no.  | Pin name                                                                | Description                                                                                                                                                                                                                                                              |

|----------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 4   | AO <sub>1</sub> to AO <sub>4</sub>                                      | D/A converter analog output pins (V <sub>DD</sub> to GND output). (Default: output #00 setting level)                                                                                                                                                                    |

| 5 to 12  | D <sub>11</sub> /AO <sub>5</sub> to<br>D <sub>4</sub> /AO <sub>12</sub> | These pins may be used either as I/O expander parallel input/output (VccA/GND output 0.5 VccA/0.2 VccA input) or D/A converter analog output (Vbb to GND output).  Pin status is controlled by input data.  See "■Data Configuration". (Default: Input mode, Hi-Z state) |

| 13       | V <sub>DD</sub> *1                                                      | D/A converter reference power pin.                                                                                                                                                                                                                                       |

| 14       | VccD*1                                                                  | MCU interface power supply pin (power supply for I/O expander).                                                                                                                                                                                                          |

| 15 to 18 | D₃ toD₀                                                                 | I/O expander parallel input/output pins.  (VccD/GND output: When VccD ≧ 4.0 V, 0.5 VccD/0.2 VccD input,  When VccD < 4.0 V, 2 V/0.2 VccD input)  Pin status is controlled by input data.  See "■Data Configuration." (Default: Input mode, Hi-Z state)                   |

| 19       | CLK*2                                                                   | Shift clock signal input pin. When $\overline{CS}$ = "L," SI data is loaded into the shift register at the rising edge of the shift clock.                                                                                                                               |

| 20       | SI*2                                                                    | Data input pin (serial input pin). Used for 16-bit serial data input.                                                                                                                                                                                                    |

| 21       | SO                                                                      | Data output pin (serial output pin). The first bit (LSB) data of the 16-bit shift register is output simultaneously with the falling edge of the shift clock. When CS output = "H," this pin goes to high impedance state.                                               |

| 22       | ŪS*²                                                                    | Chip select signal input pin. Input to shift registers is enabled when the $\overline{\text{CS}}$ signal falling edges. Shift register contents can be executed when the $\overline{\text{CS}}$ signal rising edges.                                                     |

| 23       | VccA*1                                                                  | Analog unit power supply pin (OP amplifier power supply).                                                                                                                                                                                                                |

| 24       | GND                                                                     | Common GND pin.                                                                                                                                                                                                                                                          |

<sup>\*1:</sup> Be sure that  $V_{CC}A \geqq V_{CC}D$ , and that  $V_{CC}A \geqq V_{DD}$ . \*2: Do not leave this pin in floating state.

#### **■ BLOCK DIAGRAM**

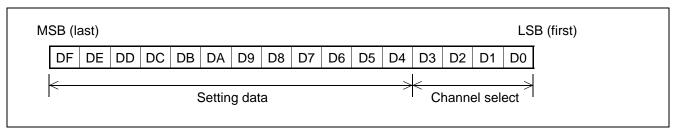

#### **■ DATA CONFIGURATION**

#### 1. Data Configuration

#### 2. Channel Select

| D3 | D2 | D1 | D0 | Function                                     |  |  |  |  |

|----|----|----|----|----------------------------------------------|--|--|--|--|

| 0  | 0  | 0  | 0  | Don't Care/special function                  |  |  |  |  |

| 0  | 0  | 0  | 1  | AO <sub>1</sub> selected                     |  |  |  |  |

| 0  | 0  | 1  | 0  | AO <sub>2</sub> selected                     |  |  |  |  |

| to | to | to | to | to                                           |  |  |  |  |

| 1  | 0  | 1  | 1  | AO <sub>11</sub> selected                    |  |  |  |  |

| 1  | 1  | 0  | 0  | AO <sub>12</sub> selected                    |  |  |  |  |

| 1  | 1  | 0  | 1  | I/O expander (serial → parallel)             |  |  |  |  |

| 1  | 1  | 1  | 0  | I/O expander (parallel $\rightarrow$ serial) |  |  |  |  |

| 1  | 1  | 1  | 1  | Expander status register (ESR)               |  |  |  |  |

#### 3. Setting Data

• Don't Care/special function (Channel select = "0000")

| DF | DE | DD | DC | DB | DA | D9 | D8 | D7 | D6 | D5 | D4 | Analog output voltage level               |

|----|----|----|----|----|----|----|----|----|----|----|----|-------------------------------------------|

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 0  | 0  | 0  | 0  | Don't Care                                |

| to | Don't Care                                |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 1  | 0  | 1  | 1  | Don't Care                                |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | GND (all channels)                        |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | V <sub>DD</sub> /256 × 1 (all channels)   |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | V <sub>DD</sub> /256 × 2 (all channels)   |

| to                                        |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | V <sub>DD</sub> /256 × 254 (all channels) |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | V <sub>DD</sub> /256 × 255 (all channels) |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 1  | 1  | 0  | 1  | Hi-Z (I/O expander state)*                |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 1  | 1  | 1  | 0  | Reset (state when power is ON)            |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 1  | 1  | 1  | 1  | Don't Care                                |

- $\times$ : Don't care \*: Hi-Z output on all channels of AO5 through AO12

- D/A Converter (Channel select = "0001" to "1100")

| DF | DE | DD | DC | DB | DA | D9 | D8 | D7 | D6 | D5 | D4 | Analog output voltage level |

|----|----|----|----|----|----|----|----|----|----|----|----|-----------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | GND                         |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | V <sub>DD</sub> /256 × 1    |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | Vpb/256 × 2                 |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | Vpb/256 × 3                 |

| to                          |

| 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | V <sub>DD</sub> /256 × 253  |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | V <sub>DD</sub> /256 × 254  |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | V <sub>DD</sub> /256 × 255  |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 0  | 0  | 0  | 1  | Hi-Z (I/O expander state)*  |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 0  | 0  | 1  | 0  | Don't Care                  |

| to | Don't Care                  |

| ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | 1  | 1  | 1  | 1  | Don't Care                  |

×: Don't care \*: Only AO₅ through AO₁₂ output is valid

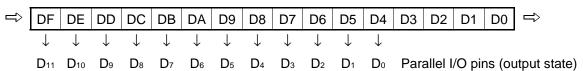

I/O Expander [Channel select = "1101"]: Serial → Parallel Conversion

Performs parallel conversion of data bits D4 to DF for output on pins D₀ to D₁₁.

Note that only those pins designated for output in the ESR (expander status register) are output.

#### Shift register

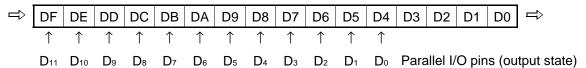

I/O Expander [Channel select = "1110"]: Parallel → Serial Conversion

Writes data from D<sub>0</sub> to D<sub>11</sub> pins to bits D4 to DF in the shift register.

Data is output to the SO pin on the shift clock (CLK) signal (The first 4 bits output data D0 to D3, so the converted output should be read as data bits 5 through 16.).

Note that the data value is "0" for pins designated for output in the ESR (expander status register) as well as analog output pins.

#### Shift register

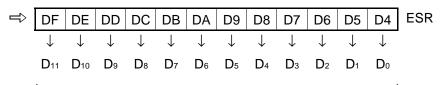

• Expander Status Register [Channel select = "1111"]

#### Shift register

This register sets the status of each pin.

| Setting | Pin status                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| "0"     | <ul> <li>Input standby status (Hi-Z output)</li> <li>D<sub>11</sub> to D<sub>4</sub> pins used for analog output should be set to "0."</li> </ul> |

| "1"     | Output state                                                                                                                                      |

Note: After power VccD is turned on, the state of pins and registers is as follows.

| Pin                                                                  | State                    |

|----------------------------------------------------------------------|--------------------------|

| AO <sub>1</sub> to AO <sub>4</sub>                                   | "L" output               |

| D <sub>11</sub> /AO <sub>5</sub> to D <sub>4</sub> /AO <sub>12</sub> | Hi-Z state (input state) |

| D <sub>3</sub> to D <sub>0</sub>                                     | Hi-Z state (input state) |

| Register                       | State                                                                     |

|--------------------------------|---------------------------------------------------------------------------|

| Shift register                 | Bits DF to D8 are "0," and D7 to D0 are not defined (retain prior state). |

| D/A register                   | All reset to "0."                                                         |

| Parallel output register       | Not defined (retain prior state).                                         |

| Expander status register (ESR) | All reset to "0."                                                         |

- ESR settings have priority in determining pin states. Switching between input standby state and analog output state is enabled even when the ESR value is "1." When the ESR value returns to "0", the pin returns to its previously defined state.

- In input standby state with AO set for Hi-Z output, the AO output setting can be used for transition to AO output state.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Doromotor             | Cumbal           | Conditions                           | Ra   | ting       | l lmi4 |

|-----------------------|------------------|--------------------------------------|------|------------|--------|

| Parameter             | Symbol           | Conditions                           | Min. | Max.       | Unit   |

|                       | VccA             |                                      | -0.3 | +7.0       | V      |

| Power supply voltage  | VccD             | Based on GND<br>(Ta = +25°C)         | -0.3 | VccA*      | V      |

|                       | V <sub>DD</sub>  | (14 120 0)                           | -0.3 | VccA*      | V      |

| Input voltage 1       | Vin1             | SI, CLK, <del>CS</del> ,             | -0.3 | VccD + 0.3 | V      |

| Output voltage 1      | Vout1            | SO, D <sub>0</sub> to D <sub>3</sub> | -0.3 | VccD + 0.3 | V      |

| Input voltage 2       | Vin2             | D. to D.                             | -0.3 | VccA + 0.3 | V      |

| Output voltage 2      | Vout2            | D4 to D <sub>11</sub>                | -0.3 | VccA + 0.3 | V      |

| Power consumption     | PD               | _                                    | _    | 250        | mW     |

| Operating temperature | Та               | _                                    | -20  | +85        | °C     |

| Storage temperature   | T <sub>stg</sub> | _                                    | -55  | +150       | °C     |

<sup>\*:</sup>  $VccA \ge VccD$ ,  $VccA \ge V_{DD}$

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Doromotor                         | Cumbal          | Conditions             |      |      | l lni4 |      |

|-----------------------------------|-----------------|------------------------|------|------|--------|------|

| Parameter                         | Symbol          | Conditions             | Min. | Тур. | Max.   | Unit |

|                                   | VccA            | _                      | 4.5  | 5.0  | 5.5    | V    |

| Davier aventy valtage             | VccD            | $VccA \geqq VccD$      | 2.7  | _    | VccA   | V    |

| Power supply voltage              | V <sub>DD</sub> | $V_{CC}A \geqq V_{DD}$ | 2.0  | _    | VccA   | V    |

|                                   | GND             | _                      | _    | 0    | _      | V    |

| Analog autout augent              | IAL             | Source current         | _    | _    | 1.0    | mA   |

| Analog output current             | Іан             | Sink current           | _    | _    | 1.0    | mA   |

| Oscillation limit output capacity | Соь             | _                      | _    | _    | 1.0    | μF   |

| Operation temperature             | Та              | _                      | -20  | _    | +85    | °C   |

WARNING: Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representative beforehand.

#### **■ ELECTRICAL CHARACTERISTIC**

#### 1. DC Characteristics

#### (1) Digital section

$(VccD \le VccA, Ta = -20^{\circ}C \text{ to } +85^{\circ}C)$

| Davamatar                   | Cumbal           | Din nome                         | Conditions                                           |                   | Value |            | 11:4:4 |

|-----------------------------|------------------|----------------------------------|------------------------------------------------------|-------------------|-------|------------|--------|

| Parameter                   | Symbol           | Pin name                         | Conditions                                           | Min.              | Тур.  | Max.       | Unit   |

| Power supply voltage        | VccD             |                                  | _                                                    | 2.7               | 5.0   | 5.5        | V      |

| Power supply current        | IccD             | VccD                             | CLK =1 MHz,<br>(Unloaded)                            | _                 | 0.2   | 0.5        | mA     |

| Standby current             | IccS             |                                  | CLK, SI, CS Stop<br>V <sub>in</sub> = VccD or<br>GND | -10               | _     | +10        | μΑ     |

| Input leak current          | IILK1            |                                  | Vin = 0 to VccD                                      | -10               | _     | +10        | μΑ     |

| "H" level input voltage     | V <sub>IH1</sub> | CL <u>K,</u> SI,<br>CS,          | $VccD \ge 4.0 V$                                     | $0.5 \times VccD$ | _     | _          | V      |

| n level input voitage       | V IH1            | D₀ to D₃                         | VccD < 4.0 V                                         | 2.0               | _     | _          | V      |

| "L" level input voltage     | VIL1             |                                  | _                                                    | _                 | _     | 0.2 × VccD | V      |

| High-impedance leak current | Іоьк             | SO                               | Vin = 0 to VccD                                      | -10               | _     | +10        | μΑ     |

| "H" level output voltage    | Vон1             | SO,                              | Iон = $-0.4  mA$                                     | VccD-0.4          | _     | _          | V      |

| "L" level output voltage    | V <sub>OL1</sub> | D <sub>0</sub> to D <sub>3</sub> | IoL = 2.5 mA                                         | _                 | _     | 0.4        | V      |

#### (2) D/A converter section

$(VccA = 5 V \pm 10\%, Ta = -20^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter                    | Symbol          | Pin name                            | Conditions                 |      | Unit |      |       |

|------------------------------|-----------------|-------------------------------------|----------------------------|------|------|------|-------|

| Parameter                    | Symbol          | rin name                            | Conditions                 | Min. | Тур. | Max. | Offic |

| Power supply voltage         | V <sub>DD</sub> | V <sub>DD</sub>                     | $V_{DD} \leqq V_{CC}A$     | 2.0  | 5.0  | 5.5  | V     |

| Power supply current         | IDD             |                                     | $V_{DD} \leqq V_{CC}A$     | _    | 1.2  | 2.5  | mA    |

| Resolution                   | Res             |                                     | Unload                     | _    | 8    | _    | bits  |

| Monotonic increase           | Rem             | AO <sub>1</sub> to AO <sub>12</sub> | $V_{DD} = V_{CC}A - 0.1 V$ | _    | 8    | _    | bits  |

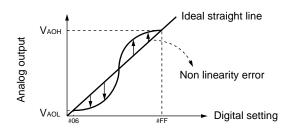

| Nonlinearity error           | LE              |                                     | Digital value: #06         | -1.5 | _    | +1.5 | LSB   |

| Differential linearity error | DLE             |                                     | to #FF                     | -1.0 |      | +1.0 | LSB   |

Nonlinearity error: Deviation (error) in input/output

curves with respect to an ideal straight line connecting output voltage at "06" and output voltage

at "FF."

Differential linearity error:

ity Deviation (error) in amplification with respect to theoretical increase in amplification per 1-bit increase in

digital value.

Note: The value of VaoH and Vdd, and the value of VaoL and GND are not necessarily equivalent.

#### (3) Operational Amplifier/Analog output section

$(V_{DD} = V_{CC}A = 5.0 \text{ V}, Ta = -20^{\circ}\text{C to } +85^{\circ}\text{C})$

| Danamatan                          | Coursels ad        | D:                                  | O a malitia ma                          | Value      |      |            |      |

|------------------------------------|--------------------|-------------------------------------|-----------------------------------------|------------|------|------------|------|

| Parameter                          | Symbol             | Pin name                            | Conditions                              | Min.       | Тур. | Max.       | Unit |

| Power supply voltage               | Vcca               |                                     | _                                       | 4.5        | 5.0  | 5.5        | V    |

| Power supply current               | ICCA               |                                     | #80 setting<br>(Unloaded)               | _          | 1.0  | 3.7        | mA   |

| Input leak current                 | IILK2              |                                     | Vin = 0 to VccA                         | -10        | _    | +10        | μΑ   |

| "H" level digital input voltage    | V <sub>IH2</sub>   |                                     | _                                       | 0.5 × VccA | _    | _          | V    |

| "L" level digital input voltage    | V <sub>IL2</sub>   | D4 to D11                           | _                                       | _          | _    | 0.2 × VccA | V    |

| "H" level digital output voltage   | V <sub>OH2</sub>   |                                     | Iон = -0.4 mA                           | VccA - 0.4 | _    | _          | V    |

| "L" level digital output voltage   | V <sub>OL2</sub>   |                                     | IoL = 2.5 mA                            | _          | _    | 0.4        | V    |

| Analog output minimum voltage 1    | V <sub>A</sub> OL1 |                                     | I <sub>AL</sub> = 0 A<br>#00 setting    | GND        | _    | 0.1        | V    |

| Analog output minimum voltage 2    | V <sub>AOL2</sub>  |                                     | I <sub>AL</sub> = 0.5 mA<br>#00 setting | -0.2       | GND  | 0.2        | V    |

| Analog output minimum voltage 3    | V <sub>AOL3</sub>  | AO <sub>1</sub> to AO <sub>12</sub> | I <sub>AH</sub> = 0.5 mA<br>#00 setting | GND        | _    | 0.2        | V    |

| Analog output minimum voltage 4    | V <sub>AOL4</sub>  |                                     | I <sub>AL</sub> = 1.0 mA<br>#00 setting | -0.3       | GND  | 0.3        | V    |

| Analog output minimum voltage 5    | V <sub>AOL5</sub>  |                                     | I <sub>AH</sub> = 1.0 mA<br>#00 setting | GND        | _    | 0.3        | V    |

| Analog output<br>maximum voltage 1 | V <sub>АОН1</sub>  |                                     | I <sub>AL</sub> = 0 A<br>#FF setting    | VccA - 0.1 | _    | VccA       | V    |

| Analog output maximum voltage 2    | V <sub>AOH2</sub>  |                                     | I <sub>AL</sub> = 0.5 mA<br>#FF setting | VccA - 0.2 | _    | VccA       | V    |

| Analog output maximum voltage 3    | Vаонз              | AO <sub>1</sub> to AO <sub>12</sub> | I <sub>AH</sub> = 0.5 mA<br>#FF setting | VccA - 0.2 | VccA | VccA+0.2   | V    |

| Analog output maximum voltage 4    | <b>V</b> AOH4      |                                     | I <sub>AL</sub> = 1.0 mA<br>#FF setting | VccA - 0.3 | _    | VccA       | V    |

| Analog output maximum voltage 5    | V <sub>AOH5</sub>  |                                     | I <sub>AH</sub> = 1.0 mA<br>#FF setting | VccA - 0.3 | VccA | VccA+0.3   | V    |

Note: IAH: Analog output sink current IAL: Analog output source current

#### 2. AC Characteristics

• For operation at VccD = 5.0 V

$$(V_{DD} = V_{CC}A = 5.0 \text{ V}, \text{ Ta} = -20^{\circ}\text{C to } +85^{\circ}\text{C})$$

| Parameter                                         | Symbol       | Conditions             | Value |      |      | 11 '4 |

|---------------------------------------------------|--------------|------------------------|-------|------|------|-------|

|                                                   |              |                        | Min.  | Тур. | Max. | Unit  |

| Clock "L" level pulse width                       | <b>t</b> ckL | _                      | 200   | _    | _    | ns    |

| Clock "H" level pulse width                       | <b>t</b> ckH | _                      | 200   | _    | _    | ns    |

| Clock rise time                                   | <b>t</b> Cr  | _                      | _     | _    | 200  | ns    |

| Clock fall time                                   | <b>t</b> Cf  | _                      | _     | _    | 200  | ns    |

| Serial input setup time                           | <b>t</b> ssu | _                      | 30    | _    | _    | ns    |

| Serial input hold time                            | <b>t</b> shd | _                      | 60    | _    | _    | ns    |

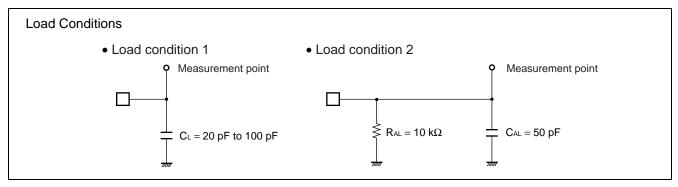

| Serial output delay time                          | tsod         | See "Load condition 1" | 0     | 80   | 170  | ns    |

| CS input setup time                               | <b>t</b> csu | _                      | 100   | _    | _    | ns    |

| CS hold time                                      | <b>t</b> ccH | _                      | 200   | _    | _    | ns    |

| CS "H" level hold time                            | <b>t</b> csH | _                      | 100   | _    | _    | ns    |

| Data output enable time                           | <b>t</b> so  | _                      | _     | _    | 200  | ns    |

| Data output float time                            | tsoz         | _                      | _     | _    | 200  | ns    |

| Parallel input setup time                         | <b>t</b> PSU | _                      | 30    | _    | _    | ns    |

| Parallel input hold time                          | <b>t</b> PHD | _                      | 60    | _    | _    | ns    |

| Parallel output delay time                        | <b>t</b> POD | See "Load condition 1" | _     | 100  | 170  | ns    |

| Analog output delay time                          | <b>t</b> aod | See "Load condition 2" | _     | 30   | 100  | μs    |

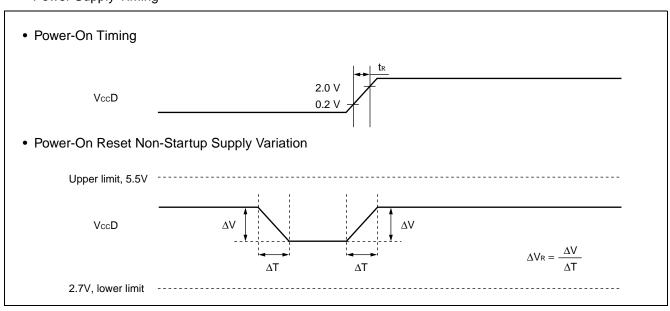

| Power supply rise time                            | <b>t</b> R   | _                      | _     | _    | 50   | ms    |

| Power-on reset non-startup power supply variation | $\Delta V_R$ | _                      | -10   | _    | 10   | V/µs  |

• For operation at VccD = 3.0 V \*1

$$(VccD = 3.0 \text{ V}, Ta = -20^{\circ}\text{C to } +85^{\circ}\text{C})$$

| Parameter                  | Symbol       | Conditions               | Value |      |      | Unit  |

|----------------------------|--------------|--------------------------|-------|------|------|-------|

| Farameter                  |              |                          | Min.  | Тур. | Max. | Offic |

| Serial output delay time   | tsod         | See "Load condition 1"*2 | 0     | 120  | 300  | ns    |

| Parallel output delay time | <b>t</b> POD | See "Load condition 2"*3 | _     | 120  | 300  | ns    |

- \*1: Items not listed are identical to characteristics for VccD = 5.0 V.

- \*2: Cascade connection enabled at 1.5 MHz.

- \*3: Applied to D0 to D3 operating at VccD.

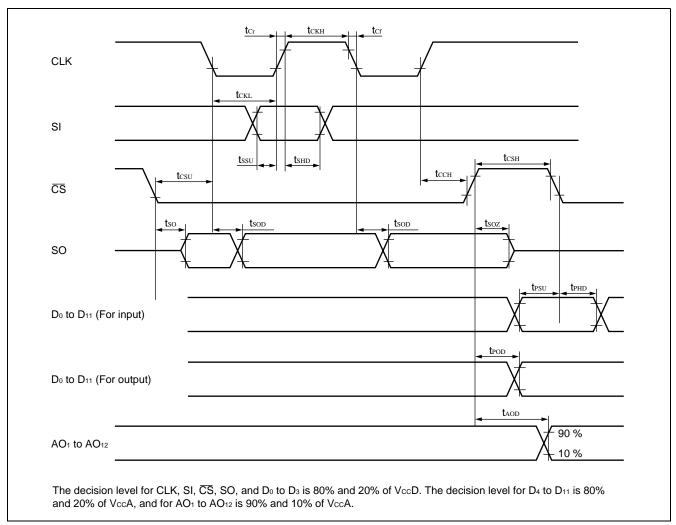

#### • Input/Output Timing (CS method)

#### • Power Supply Timing

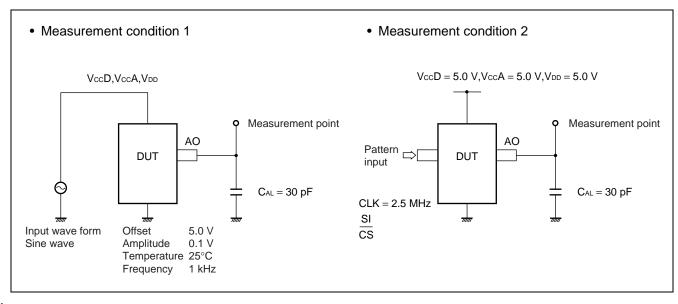

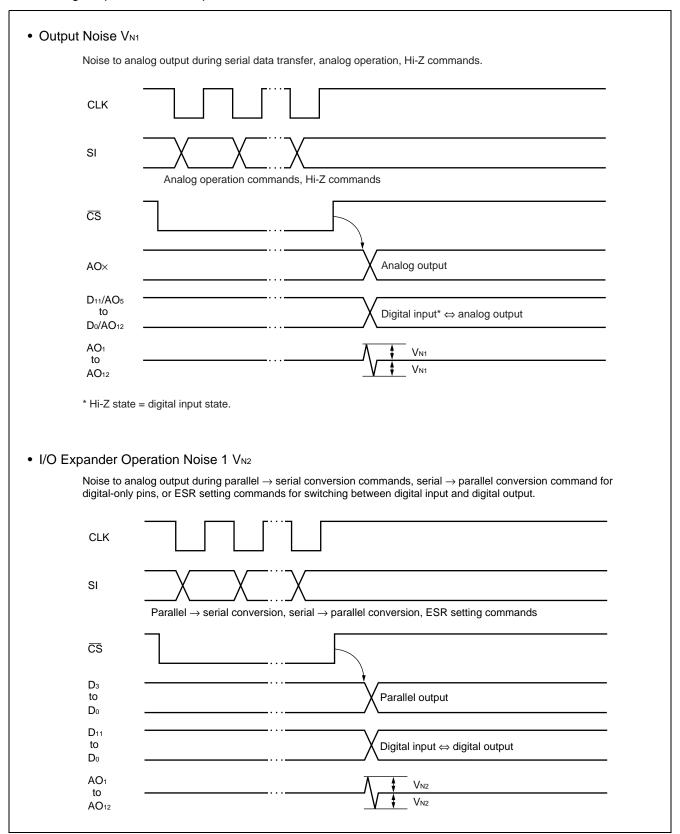

#### 3. Analog Output Noise Characteristic

$$(V_{DD} = V_{CC}D = V_{CC}A = 5.0 \text{ V}, Ta = +25^{\circ}C)$$

| Doromotor                            | Cumbal          | 0                                                                                                                                                                                                                                                                                                 | Measurement | Value |      |      | 11   |

|--------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|------|------|------|

| Parameter                            | Symbol          | Conditions                                                                                                                                                                                                                                                                                        | condition   | Min.  | Тур. | Max. | Unit |

| Digital supply noise reduction ratio | Psrd            | fnoise = 1 kHz                                                                                                                                                                                                                                                                                    | 1           | _     | _    | 20   | dB   |

| Analog supply noise reduction ratio  | Psra            | f <sub>NOISE</sub> = 1 kHz                                                                                                                                                                                                                                                                        | 1           | _     | _    | 20   | dB   |

| D/A supply noise reduction ratio     | Psrda           | f <sub>NOISE</sub> = 1 kHz                                                                                                                                                                                                                                                                        | 1           | _     | _    | 0    | dB   |

| Operating noise                      | V <sub>N1</sub> | <ul> <li>During serial transfer</li> <li>During analog operation</li> <li>During Hi-Z commands.</li> <li>See "Operating Noise V<sub>N1</sub>."</li> </ul>                                                                                                                                         | 2           | -30   | _    | 30   | mV   |

| I/O expander operating noise 1       | V <sub>N2</sub> | <ul> <li>Serial → parallel conversion         See "I/O Expander Operating         Noise 1 V<sub>N2</sub>."         During digital-only pin operation         • During parallel → serial conversion         • ESR setting         During digital input/digital output         switching</li> </ul> | 2           | -30   | _    | 30   | mV   |

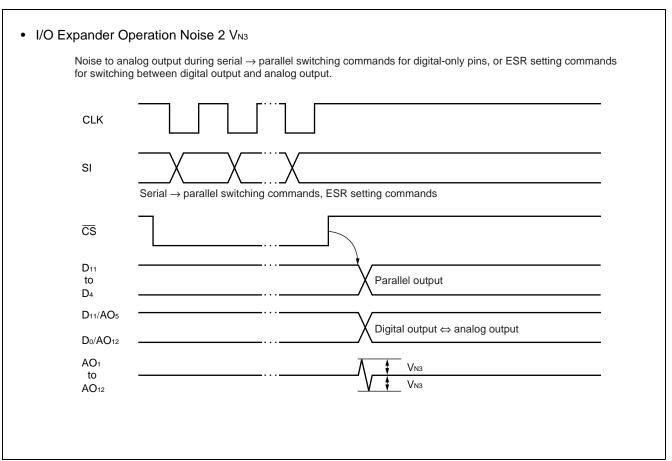

| I/O expander operating noise 2       | Vиз             | <ul> <li>During serial → parallel conversion<br/>See "I/O Expander Operating<br/>Noise 2 V<sub>N3</sub>."<br/>During digital/analog capable pin<br/>operation</li> <li>ESR setting<br/>During digital output/digital output<br/>switching</li> </ul>                                              | 2           | -0.1  | _    | 0.1  | V    |

#### • Analog Output Noise Description

#### (Continued)

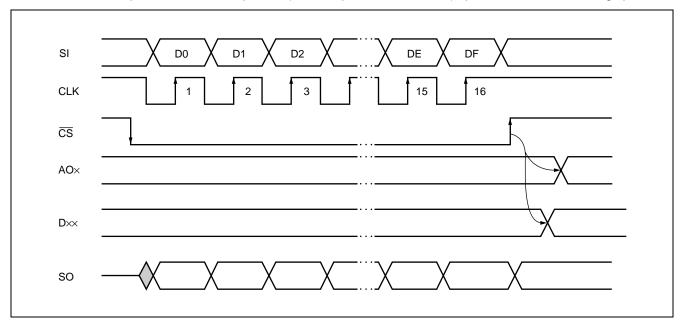

#### ■ DATA INPUT/OUTPUT TIMING

#### MB88146A Data Input/Output Timing (Serial Bus Format)

D/A converter operation, and I/O expander (serial → parallel conversion) operation, and ESR writing operation.

Data input is enabled at the falling edge of the  $\overline{CS}$  signal. 16-bit data is input, and the shift register command is executed at the rising edge of  $\overline{CS}$ .

In D/A converter operation, the analog output selected at the rising edge of  $\overline{CS}$  is the conversion result. In serial  $\rightarrow$  parallel conversion, the digital output selected at the rising edge of  $\overline{CS}$  is the conversion result. In ESR write operation, ESR data is set and pin status determined at the rising edge of  $\overline{CS}$ .

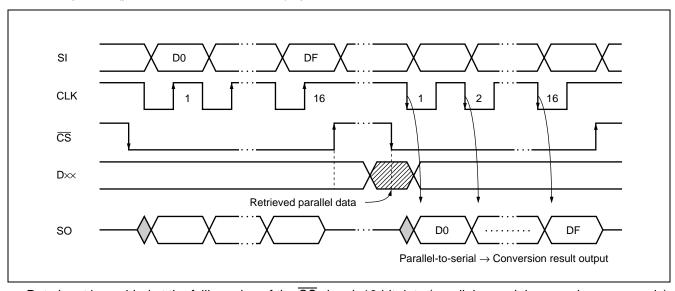

I/O expander (parallel → serial conversion) operation

Data input is enabled at the falling edge of the  $\overline{CS}$  signal. 16-bit data (parallel  $\rightarrow$  serial conversion commands) is input and commands accepted at the rising edge of  $\overline{CS}$ . At the falling edge of  $\overline{CS}$ , data from the parallel input is loaded into bits D4 to DF of the shift register, and output from the SO pin timed to the falling edge of the CLK signal.

#### **■ USAGE PRECAUTIONS**

#### 1. Preventing Latch-Up

A condition known as "latch-up" may occur when the input or output pins of a CMOS IC device are exposed to voltages higher then VccD or VccA or lower than GND voltage, or when voltages are applied to the device in excess of rated values for VccD, VccA, or Vpd to GND voltages. Latchup produces a rapid increase in power supply current, and may result in thermal destruction of elements. Users should take sufficient precautions to ensure that absolute maximum ratings are not exceeded at any time during use.

#### 2. Power Supply Pins

The power supply should be connected to the VccD, VccA, VDD, and GND terminals of the MB88146A with as low an impedance as possible.

In addition, it is recommended that ceramic capacitors or approximately 0.1  $\mu$ F be connected as bypass capacitors between the VccD, VccA, and VpD terminals and the GND terminals.

#### **■ ORDERING INFORMATION**

| Part number | Package                              | Remarks |

|-------------|--------------------------------------|---------|

| MB88146AP   | 24-pin Plastic DIP<br>(DIP-24P-M02)  |         |

| MB88146APFV | 24-pin Plastic SSOP<br>(FPT-24P-M03) |         |

#### ■ PACKAGE DIMENSIONS

#### **FUJITSU MICROELECTRONICS LIMITED**

Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0722, Japan Tel: +81-3-5322-3347 Fax: +81-3-5322-3387 http://jp.fujitsu.com/fml/en/

For further information please contact:

#### **North and South America**

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

#### Europe

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany

Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 206 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu,Seoul 135-280 Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

http://www.fmk.fujitsu.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD.

151 Lorong Chuan, #05-08 New Tech Park,

Singapore 556741

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm.3102, Bund Center, No.222 Yan An Road(E), Shanghai 200002, China Tel: +86-21-6335-1560 Fax: +86-21-6335-1605 http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD.

10/F., World Commerce Centre, 11 Canton Road

Tsimshatsui, Kowloon

Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/tw

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.