## General Description

The MAX366 and MAX367 are multiple, two-terminal circuit protectors. Placed in series with signal lines, each two-terminal device guards sensitive circuit components against voltages near and beyond the normal supply voltages. These devices are used at interfaces where sensitive circuits are connected to the external world and could encounter damaging voltages (up to 35V beyond the supply rails) during power-up, power-down, or fault conditions.

The MAX366 contains three independent protectors and the MAX367 contains eight. They can protect analog signals using either unipolar (4.5V to 36V) or bipolar (±2.25V to ±18V) power supplies. Each protector is symmetrical. Input and output terminals may be freely interchanged.

These devices are voltage-sensitive MOSFET transistor arrays that are normally on when power is applied and normally open circuit when power is off. With ±10V supplies, on-resistance is  $100\Omega$  max and leakage is less than 1nA at +25°C.

When signal voltages exceed or are within approximately 1.5V of either power-supply voltage (including when power is off), the two-terminal resistance increases dramatically, limiting fault current as well as output voltage to sensitive circuits. The protected side of the switch maintains the correct polarity and clamps approximately 1.5V below the supply rail. There are no "glitches" or polarity reversals going into or coming out of a fault condition.

#### **Applications**

Process Control Systems Redundant/Backup Systems Hot-Insertion Boards/Systems ATE Equipment **Data-Acquisition Systems** Sensitive Instruments

Features **★ ±40V Overvoltage Protection**

- **♦ Open Signal Paths with Power Off** 100 $\Omega$  Signal Paths with Power On

- ↑ 1nA Max Path Leakage at +25°C

- ♦ 44V Maximum Supply Voltage Rating

- **♦** Automatic Protection; No Programming or Controls

## Ordering Information

| PART <sup>†</sup> | TEMP. RANGE     | PIN-PACKAGE    |

|-------------------|-----------------|----------------|

| MAX366CPA         | 0°C to +70°C    | 8 Plastic DIP  |

| MAX366CSA         | 0°C to +70°C    | 8 SO           |

| MAX366C/D         | 0°C to +70°C    | Dice*          |

| MAX366EPA         | -40°C to +85°C  | 8 Plastic DIP  |

| MAX366ESA         | -40°C to +85°C  | 8 SO           |

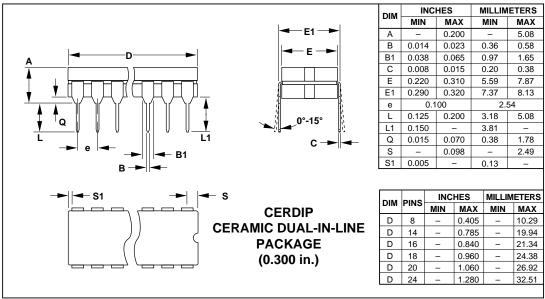

| MAX366MJA         | -55°C to +125°C | 8 CERDIP**     |

| MAX367CPN         | 0°C to +70°C    | 18 Plastic DIP |

| MAX367CWN         | 0°C to +70°C    | 18 Wide SO     |

| MAX367C/D         | 0°C to +70°C    | Dice*          |

| MAX367EPN         | -40°C to +85°C  | 18 Plastic DIP |

| MAX367EWN         | -40°C to +85°C  | 18 Wide SO     |

| MAX367MJN         | -55°C to +125°C | 18 CERDIP**    |

- † MAX367 available after January 1, 1995.

- \* Dice are tested at TA = +25°C only.

- \* Contact factory for availability.

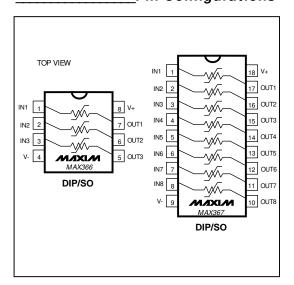

Pin Configurations appear at end of data sheet.

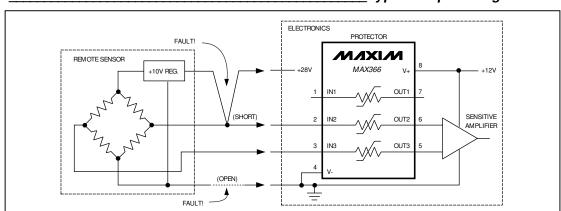

## Typical Operating Circuit

MIXIM

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

#### **ABSOLUTE MAXIMUM RATINGS**

| V+ to V0.3V, +44V IN_OUT(V- + 44V), (V+ - 44V) Continuous Current into Any Terminal±30mA                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peak Current into Any Terminal (pulsed at 1ms, 10% duty cycle)±70mA Continuous Power Dissipation (T <sub>A</sub> = +70°C)                                 |

| 8-Pin Plastic DIP (derate 9.09mW/°C above +70°C)727mW<br>8-Pin SO (derate 5.88mW/°C above +70°C)471mW<br>8-Pin CERDIP (derate 8.00mW/°C above +70°C)640mW |

| 18-Pin Plastic DIP (derate 11.11mW/°C abo | ove +70°C)889mW |

|-------------------------------------------|-----------------|

| 18-Pin Wide SO (derate 9.52mW/°C abov     | e +70°C)762mW   |

| 18-Pin CERDIP (derate 10.53mW/°C above    | re +70°C)842mW  |

| Operating Temperature Ranges              |                 |

| MAX36_C                                   | 0°C to +70°C    |

| MAX36_E                                   | 40°C to +85°C   |

| MAX36_M                                   | 55°C to +125°C  |

| Storage Temperature Range                 | 65°C to +150°C  |

|                                           |                 |

Lead Temperature (soldering, 10sec) .....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V+ = +15V, V- = -15V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                   | TEMP.<br>RANGE                        | MIN       | TYP | MAX        | UNITS |   |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------|---------------------------------------|-----------|-----|------------|-------|---|

| Analog Signal Range                             | VIN, VOUT            | (Note 1)                                                                                     | All                                   | (V+ - 40) |     | (V- + 40)  | V     |   |

| Fault-Free Analog Signal Range                  | VIN, VOUT            | V+ = 15V, V- = -15V (Note 2)                                                                 | All                                   | -11       |     | 11         | V     |   |

| Analog-Signal Output<br>Range (Fault)           | Vout                 | $V_{IN} = V_{+} \text{ or } V_{-},$<br>$100k\Omega < R_{OUT} < 1000M\Omega \text{ (Note 1)}$ | All                                   | (V- + 3)  |     | (V+ - 1.5) | ٧     |   |

|                                                 |                      | V+ = 15V, V- = -15V, V <sub>IN</sub> = ±10V,<br>I <sub>OUT</sub> = 1mA                       | +25°C                                 |           | 62  | 85         | Ω     |   |

|                                                 |                      |                                                                                              | C, E                                  |           |     | 100        |       |   |

|                                                 |                      |                                                                                              | М                                     |           |     | 125        |       |   |

| Analan Cinnal Bath Basistana                    | D                    | .,                                                                                           | +25°C                                 |           | 62  | 100        |       |   |

| Analog-Signal-Path Resistance                   | R(IN-OUT)            | $V+ = 10V, V- = -10V, V_{IN} = \pm 5V,$                                                      | C, E                                  |           |     | 125        |       |   |

|                                                 |                      | I <sub>OUT</sub> = 1mA                                                                       | М                                     |           |     | 150        |       |   |

|                                                 |                      | V+ = 5V, V- = -5V, V <sub>IN</sub> = ±2V,                                                    | +25°C                                 |           | 140 | 350        |       |   |

|                                                 |                      | IOUT = 1mA                                                                                   | C, E, M                               |           |     | 400        |       |   |

| Signal-Path Resistance Match                    | ΔR(IN-OUT)           | $V_{IN} = \pm 10V$ , $I_{OUT} = 1$ mA                                                        | +25°C                                 |           |     | 7          | Ω     |   |

|                                                 |                      |                                                                                              | C, E, M                               |           |     | 10         |       |   |

| Signal-Path Leakage                             | I <sub>IN(OFF)</sub> | l                                                                                            | $V+ = V- = 0V$ , $V_{IN} = \pm 35V$ , | +25°C     | -10 |            | 10    | ^ |

| (Power Off)                                     |                      | V <sub>OUT</sub> = open circuit                                                              | C, E, M                               | -1000     |     | 1000       | nA    |   |

| Signal-Path Leakage                             | IOUT(ON)             | ON) VIN = VOUT = ±10V                                                                        | +25°C                                 | -1        |     | 1          | nA    |   |

| (without Fault Condition)                       | IOUT(ON)             |                                                                                              | C, E, M                               | -100      |     | 100        | 1 114 |   |

| Signal-Path Leakage                             | I <sub>IN</sub> (ON) | V <sub>IN</sub> = ±25V, V <sub>OUT</sub> = open circuit                                      | +25°C                                 | -10       |     | 10         | nA    |   |

| (with Fault Condition)                          | TIIN(OIN)            | VIIV = ±25 V, VOOT = Open circuit                                                            | C, E, M                               | -1000     |     | 1000       | IIA   |   |

| Signal-Path Leakage                             | I <sub>IN(OFF)</sub> | $V_{+} = V_{-} = 0V, V_{OUT} = 0V,$                                                          | +25°C                                 | -10       |     | 10         | nA    |   |

| (with Overvoltage)                              | 114(011)             | $V_{IN} = \pm 35V$                                                                           | C, E, M                               | -1000     |     | 1000       | 11/1  |   |

| POWER SUPPLY                                    |                      |                                                                                              |                                       |           |     |            |       |   |

| Power-Supply Range                              | V+, V-               |                                                                                              | +25°C,<br>C, E, M                     | 0         |     | ±18        | V     |   |

| Power-Supply Range<br>(without Fault Condition) | V+, V-               | R <sub>(IN-OUT)</sub> < 1000Ω (Note 2)                                                       | +25°C,<br>C, E, M                     | ±2.25     |     | ±18        | ٧     |   |

| Power-Supply Current                            | l+, l-               |                                                                                              | +25°C                                 | -1        |     | 1          | μА    |   |

| Fower-Supply Guiterit                           |                      |                                                                                              | C, E, M                               | -10       |     | 10         |       |   |

Note 1: Guaranteed, but not tested.

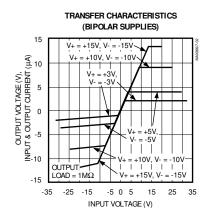

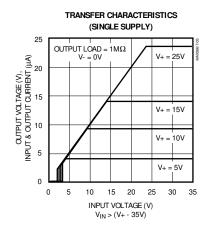

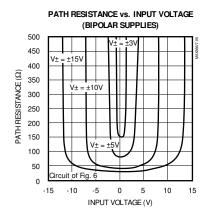

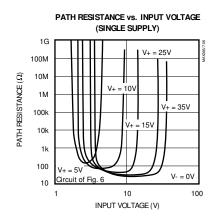

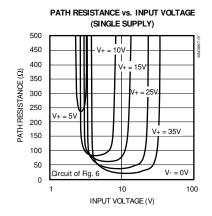

Note 2: See Typical Operating Characteristics curves for fault-free analog signal range at various supply voltages.

N/X/N/

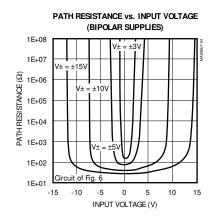

\_Typical Operating Characteristics

$(V+ = +15V, V- = -15V, T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V+ = +15V, V- = -15V, T_A = +25^{\circ}C, unless otherwise noted.)$

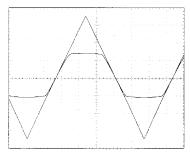

#### OVERVOLTAGE RAMP

CHAN 1: INPUT OVERVOLTAGE RAMP  $\pm 7V$ , 2V/div CHAN 2: OUTPUT; OUTPUT LOAD =  $1000\Omega$ , 2V/div

#### Pin Description

|         | PIN        | NAME*               | FUNCTION                      |  |

|---------|------------|---------------------|-------------------------------|--|

| MAX366  | MAX367     | NAME                |                               |  |

| 1, 2, 3 | 1, 2, 3    | IN1, IN2, IN3       | Signal Inputs 1, 2, 3         |  |

| -       | 4–8        | IN4-IN8             | Signal Inputs 4–8             |  |

| 4       | 9          | V-                  | Negative Supply Voltage Input |  |

| -       | 10–14      | OUT8-OUT4           | Signal Outputs 4–8            |  |

| 5, 6, 7 | 15, 16, 17 | OUT3, OUT2,<br>OUT1 | Signal Outputs 1, 2, 3        |  |

| 8       | 18         | V+                  | Positive Supply Voltage Input |  |

<sup>\*</sup> Inputs and outputs are names for convenience only; inputs and outputs are identical and interchangeable.

#### Background Information

When a voltage outside the supply range is applied to most integrated circuits, there is a strong possibility they will be damaged or "latch up" (that is, fail to operate properly even after the offending voltage is removed). If an IC's input or output pin is supplied with a voltage when the IC's power is off, and power is subsequently applied, the device may act as an SCR and destroy itself and/or other circuitry. Such "faults" are commonly encountered in modular control systems where power and signals to interconnected modules may be interrupted and re-established at random. They can happen during production testing, maintenance, start-up, or a power "brownout."

The MAX366/MAX367 are designed to protect delicate input and output circuitry from overvoltage faults up to ±40V (with or without power applied), in devices such as op amps, analog-to-digital/digital-to-analog converters, and voltage references. These circuit protectors automatically limit signal voltages and currents to safe levels without degrading normal signal performance, even in very high-impedance circuits. They are powered by the power supply of the protected circuit and inserted into the signal lines. There are no control lines, programming pins, or adjustments

Unlike shunt diode networks, these devices are low-impedance FETs that become high impedance during a fault condition, so fault current and power dissipation are extremely low. Equally important, leakage current during normal and fault conditions is extremely low. In addition, unlike most discrete networks, these parts protect circuits both when power is off and during power transitions.

## \_Detailed Description

#### Internal Construction

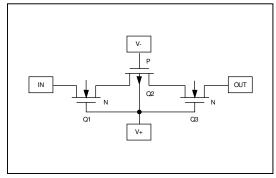

Figure 1 shows the simplified internal construction of each protector inside the MAX366/MAX367. Each circuit consists of two N-channel FETs and one P-channel FET. All the FETs are enhancement types; that is, the N channels must have approximately 1.3V of positive gate voltage in order to conduct, and the P channel must have approximately 2V of negative gate voltage in order to conduct.

During normal operation, V+ is connected to a positive potential and V- is connected to a negative potential. Since their gates are tied to V+, transistors Q1 and Q3 conduct as long as their sources are at least 1.3V below V+ (the N-channel gate threshold.) Transistor Q2's gate is tied to V-, so it conducts as long as its source is 2V or more above V- (the P-channel gate threshold.)

Figure 1. Simplified Internal Structure

As long as the signal is within these limits, all three transistors conduct and a low-resistance path is maintained from the IN to OUT pin. (Note that, since the device is symmetrical, IN and OUT pins can be interchanged.) When the signal is beyond the gate threshold of either Q2 or Q1/Q3, the path resistance rises dramatically. When power is off, none of the transistors have gate bias, so the circuit from IN to OUT is open.

#### **Normal Operation**

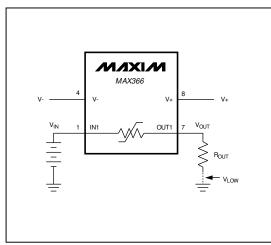

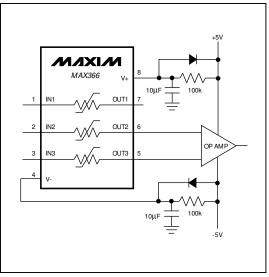

In normal operation, the protector is placed in series with the signal line and the power supplies are connected to V+ and V- (see Figure 2). V- is ground when operating with a single supply. When power is applied, each protector acts as a resistor in the signal path. Any voltage source on the "input" side of the switch will be conducted through the protector to the output. (Note that, since the protector is symmetrical, IN and OUT pins can be interchanged.)

If the output load is resistive, it will draw current, and a voltage divider will be formed with the internal resistance so the output voltage will be lower than the input voltage. Since the internal resistance is typically less than  $10\Omega$ , high-impedance loads will be relatively unaffected by the presence of the protector. The protector's path resistance is a function of the supply voltage and the signal voltage (see *Typical Operating Characteristics*).

Figure 2. Application Circuit

#### Power Off

When power is off (i.e.,  $V_+ = V_- = 0V$ ), the protector is a virtual open circuit, and all voltages on each side are isolated from each other up to  $\pm 40V$ . With  $\pm 40V$  applied to the input pin, the output pin will be 0V, regardless of its resistance to ground.

#### **Fault Conditions**

A fault condition exists when the voltage on either signal pin is within about 1.5V of either supply rail or exceeds either supply rail. This definition is valid when power is applied and when it is off, as well as during all the states as power ramps up or down.

During a fault, the protector acts as a variable resistor, conducting only enough to sustain the other side of the switch within about 1.5V of the supply rail. This voltage is known as the "fault knee voltage," and is not symmetrical. It is approximately 1.3V down from the positive supply (V+ pin) or approximately 2.0V up from the negative supply (V- pin). Each fault knee voltage varies slightly with supply voltage, with output current, and from device to device.

During a fault condition, all the fault current flows from one signal pin through the protector and out the other signal pin. No fault current flows through either supply pin. (There will be a few pico-amps of leakage current from each signal pin to each supply pin, but this is independent of fault current.)

During the fault condition, enough current will flow to maintain the output voltage at the fault knee voltage, so the fault current is a function of the output resistance and the supply voltage. The output voltage and current have the same polarity as the fault.

The maximum input fault voltage is 40V from the "opposite-polarity supply rail." This means the input can go to  $\pm 35V$  with  $\pm 5V$  supplies or to  $\pm 25V$  with  $\pm 15V$  supplies. The fault voltage is highest ( $\pm 40V$ ) when the supplies are off (V+ = V- = 0V).

Using the circuit of Figure 2, the approximate fault currents are as follows:

1) For positive faults:

$$I(F) \approx (V+ - 1.3V - V_{LOW}) \div ROUT$$

2) For negative faults:

$$I(F) \approx (V- + 2V + VLOW) \div ROUT$$

where VLOW is the terminating voltage at the far end of ROUT. VLOW = 0V when ROUT is grounded.

The current through each protector should never exceed 30mA. Always calculate the power dissipated by all the protectors in worst-case conditions (maximum voltage and current through each protector) to ensure the package dissipation limit is not reached.

With single-supply operation, grounded loads will have zero voltage (and current) whenever the input voltage is below approximately 2V. In effect, both the IN and OUT pins are in fault condition.

A special case arises when power is off: The part is in a perpetual fault condition but no fault current flows because all the internal FETs are off.

#### Single-Supply Output Operation

Single-supply operation is a special case. Signals cannot go to ground, since from 0V to approximately +2V is a fault condition.

#### **Extremely Low-Current Operation**

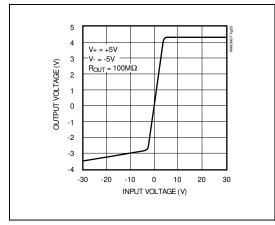

Figure 3 shows the typical high-impedance transfer characteristics with a  $100M\Omega$  load. Compared to the transfer characteristic at  $1M\Omega$  (see  $\it Typical Operating Characteristics$ ), the two knees are closer to the supply voltages and the slopes of the flat portions of the curve (fault conditions) are steeper. As the load resistance is increased even further, the positive and negative knees increase, and the slopes in fault conditions increase even more. Eventually, at some extremely high output resistance (e.g., Tera ohms), the output voltage can exceed the supply voltage during fault conditions. This is due to extremely low leakage currents from the input to output.

When the protector's output side is connected to very high-resistance, very low-current loads (such as opamp inputs), a small leakage current flows from the input to the output during fault conditions. This current is typically below a nano-ampere (<10-9A) but, if the output resistance is high enough, it can cause the output voltage to exceed the supply voltages during fault conditions

This condition can be self-correcting, however, if the high-resistance load has protection diodes to the supply rails (either external or internal to the op amp). These diodes conduct the leakage current to the supply rails and safely limit the output voltage. An alternative is to add a high-value resistor to ground in parallel with the load. This resistor may be as low as  $1000 M\Omega$ ; its value must be determined experimentally at the highest anticipated operational temperature.

The fault protectors will not normally be used with highimpedance FET-input amplifiers that lack input protection diodes. Such amplifiers are fragile and are normally

Figure 3. High-Impedance Transfer Characteristic

reserved for use when ultra-low leakage (pA) is needed. The MAX366/MAX367 have nano-amperes of leakage, which would negate the low leakage of the unprotected amplifier.

## Low-Voltage Operation

The MAX366/MAX367 "operate" with supply voltages all the way down to 0V, but what they do to the signal is not obvious. With a total supply voltage of 3.5V, the protector is in a fault condition with nearly any input that is not close to 2.0V. Below 3.5V (including power off), the protector is perpetually in a fault condition (i.e., high impedance).

When the supply voltage(s) ramps up (and/or down) from zero, the signal path is initially in a fault condition (open), until the supply voltage passes the input voltage. The output starts at zero and is delayed from reaching the input voltage as the part comes out of the fault condition. If the supply voltage exceeds about 3.5V, but never exceeds the input voltage, the output will follow the supply, always remaining about 1.3V below the positive supply voltage or 2V above the negative supply voltage. If the input voltage subsequently comes out of the fault condition, the output returns to the input value. This set of conditions is exactly reversed when power ramps down to zero.

Since the input and output pins are identical and interchangeable, predicting whether or not the part is in a fault condition is easy: If either IN or OUT exceeds V+ or V-, a fault condition exists and the current that flows will be just enough to cause the other signal pin (OUT or IN) to approach the appropriate supply rail.

#### **Bipolar Faults**

The MAX366/MAX367 V+ and V- pins are normally connected to a circuit's most positive and most negative power supplies. When a circuit has multiple power supplies (such as ±5V and ±12V) and the MAX366/MAX367 V+ and V- pins are connected to the lower supply, it is possible to have fault conditions on both sides of the signal path at once, if both sides of the switch have paths to higher voltages. If the polarity of these faults is the same, the signal path will be open and there is no conflict.

If the IN and OUT pins are driven in opposite polarities from low-impedance sources, the lower of the two impedances will overcome the higher impedance, just as if the protector were not present. (Make sure the current does not exceed the 30mA absolute maximum rating.) As the lower impedance source approaches and exceeds the fault knee voltage, the protector will conduct enough current to maintain the other signal pin near the fault knee voltage. This means when the fault knee voltage is reached, the current through the protector shifts from the higher current capability of the lower impedance source to the lower current capability of the higher impedance source.

## \_Typical Applications

#### **Driven Switches**

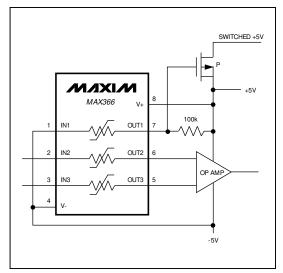

The MAX366/MAX367 have low supply currents (<1 $\mu$ A), which allows the supply pins to be driven directly by other active circuitry, instead of connected directly to the power sources. In this configuration, the parts can be used as driven fault-protected switches with V+ or V- pins used as the control pins. For example, if the V- pin is grounded, you can turn the V+ pin on and off by driving it with the output of a CMOS gate. This effectively connects and disconnects three or eight separate signal lines at once. (If bipolar signals or signals that go to ground are being switched, the V- pin must be driven simultaneously to a negative potential.) Always ensure that the driving source(s) does not drive the V+ pin more negative than the V- pin.

Figure 4 shows a simple turn-on delay that takes advantage of the MAX366's low power consumption. The two RC networks cause gradual application of power to the MAX366, which in turn applies the input signals smoothly after the amplifier has stabilized. The two diodes discharge the two capacitors rapidly when power is turned off.

Figure 4. Turn-On Delay

This circuit can be tailored to nearly any rate of turnon by selecting the RC time constants in the V+ and V- pins, without affecting the time constant of the measuring circuit.

## **Protectors as Circuit Elements**

Any of the individual protectors in a MAX366 or MAX367 may be used as a switched resistor, independent of the functions of other elements in the same package. For example, Figure 5 shows a MAX366 with two of the protectors used to protect the input of an op amp, and the third element used to sequence a power supply. Combining the circuits of Figures 4 and 5 produces a delayed action on the switched +5V, as well as smooth application of signals to the amplifier input.

## \_Testing Circuit Protectors

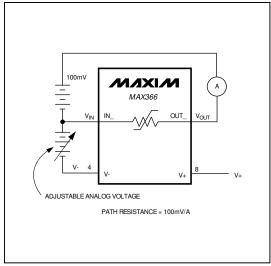

#### Measuring Path Resistance

Measuring path resistance requires special techniques, since path resistance varies dramatically with the IN and OUT voltages relative to the supply voltages. Conventional ohmmeters should not be used, for two reasons: 1) the applied voltage and currents are usually not predictable, and 2) the true resistance is a function of the applied voltage, which is dramatically altered by the ohmmeter itself. Autoranging ohmmeters are particularly unreliable.

Figure 5. Power-Supply Sequencing

Figure 6 shows a circuit that can give reliable results. This circuit uses a 100mV voltage source and a low-voltage-drop ammeter as the measuring circuit, and an adjustable supply to sweep the analog voltage across its whole range. The ammeter must have a voltage drop of less than one millivolt (at any current) for accurate results. (A Keithley Model 617 Electrometer has a suitable ammeter circuit, appropriate ranges, and a built-in voltage source designed for this type of measurement.) Measurements are made by setting the analog voltage, measuring the current, and calculating the path resistance. The procedure is repeated at each analog voltage and supply voltage.

It is important to use a voltage source of 100mV or less. As shown in Figure 4, this voltage is added to the  $V_{IN}$  voltage to form the  $V_{OUT}$  voltage. Using a higher voltage could cause the OUT pin to go into a fault condition prematurely.

Figure 6. Path-Resistance Measuring Circuit

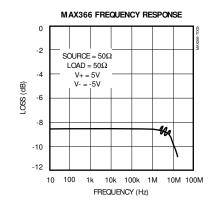

#### High-Frequency Performance

In  $50\Omega$  systems, signal response is reasonably flat up to several megahertz (see *Typical Operating Characteristics*). Above 5MHz, the response has several minor peaks, which are highly layout dependent. Because the path resistance is dependent on the supply voltage and signal amplitude, the impedance is not controlled. Adjacent channel attenuation up to 5MHz is about 3dB above that of a bare IC socket, and is due entirely to capacitive coupling.

Pulse response is reasonable, but because the impedance changes rapidly, fast rise times may induce ringing as the signal approaches the fault voltage. At very high amplitudes (such as noise spikes), the capacitive coupling across the signal pins will transfer considerable energy, despite the fact that the DC path is a virtual open circuit

## \_High-Voltage Surge Suppression

These devices are not high-voltage arresters, nor are they substitutes for surge suppressers. In systems that use these forms of protection, however, the MAX366/MAX367 can fill a vital gap. Figure 7 shows a typical circuit. Although the surge suppressers are extremely fast shunt elements, they have very soft current knees. Their clamp voltage must be chosen well above the normal signal levels, because they have excessive leakage currents as the knee is approached. This current can interfere with normal operation when signal levels are low or impedances are high. If the clamp voltage is too high, however, the input can be damaged.

Using a MAX366/MAX367 after the surge suppresser allows the surge-suppresser voltage to be set above the supply voltage (but within the overvoltage limits), dramatically reducing the effects of leakage (Figure 7). During a surge, the surge suppresser clamps the input voltage to  $roughly \pm 10V$ . This protects the MAX366/MAX367, but the MAX366/MAX367 still disconnect the signal from the op amp well within the  $\pm 5V$  supply.

# MAX366 V<sub>+</sub> 1 IN1 OUT1 7 2 IN2 OUT2 6 3 IN3 OUT3 5 OP AMP SURGE SUPPRESSERS (+10V)

Figure 7. Surge-Suppression Circuit

#### Pin Configurations

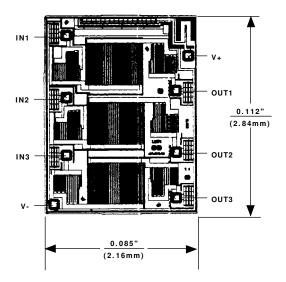

## Chip Topography

TRANSISTOR COUNT: 21 SUBSTRATE CONNECTED TO V+

MAX

5.08

4.45

2.03

0.56

1.65

0.30

2.03

8.26

7.87

10.16

3.81

9.91

# Signal-Line Circuit Protectors

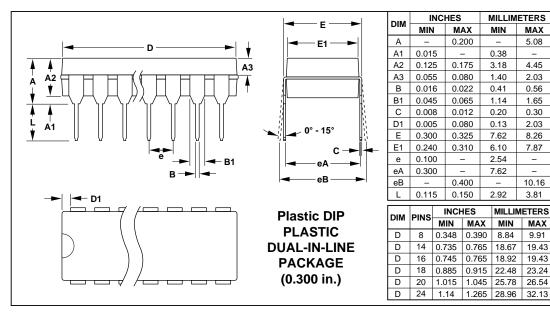

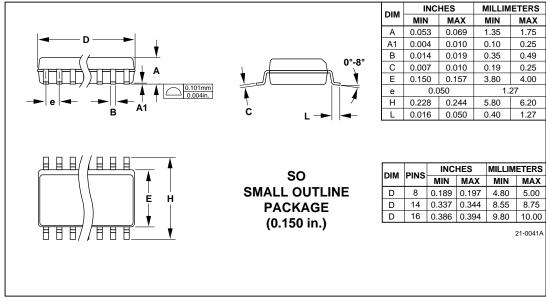

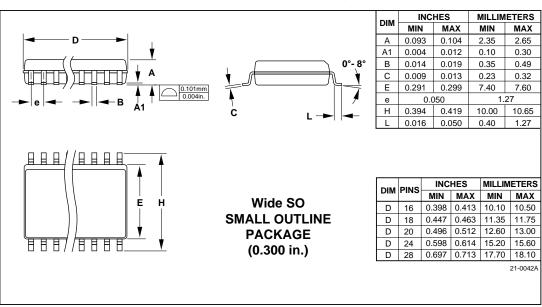

## Package Information

## \_Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600