- Provides up to 2K-Address Matching System

- **VLAN Support for Single or Multiple** ThunderSWITCH™ Devices

- **Provides Glueless External-Address Match** Interface to the TNETX3150/TNETX3150A

- **Uses Standard Off-the-Shelf SRAMs**

- **EEPROM Interface for Auto-Configuration,** No CPU Needed

- **Automatic Aging Through User-Selectable** Aging (AGE) Threshold

- Fabricated in 3.3-V Low-Voltage **Technology**

- Requires 3.3-V and 5-V Power Supplies

- 5-V Tolerant I/Os

- **Provides Direct Input/Output (DIO) Interface** for Management Access and Control of the **Address-Lookup Table**

- Address Lookups, Adds, and Deletes Are **Automatically Performed in Hardware**

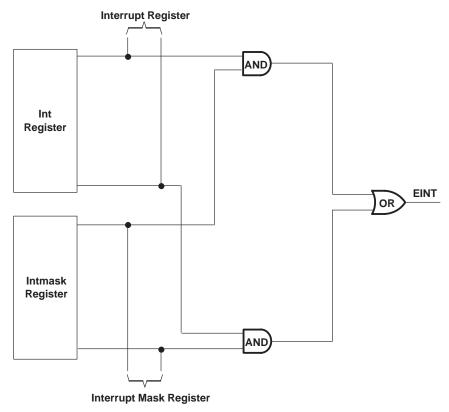

- User-Selectable Interrupts Simplify the Management Operations

- **Provides Spanning-Tree Support**

- **Secure Addresses From Changing Ports**

- MII Data I/O (MDIO) PHY Management Interface

- Management Access to Statistic Registers

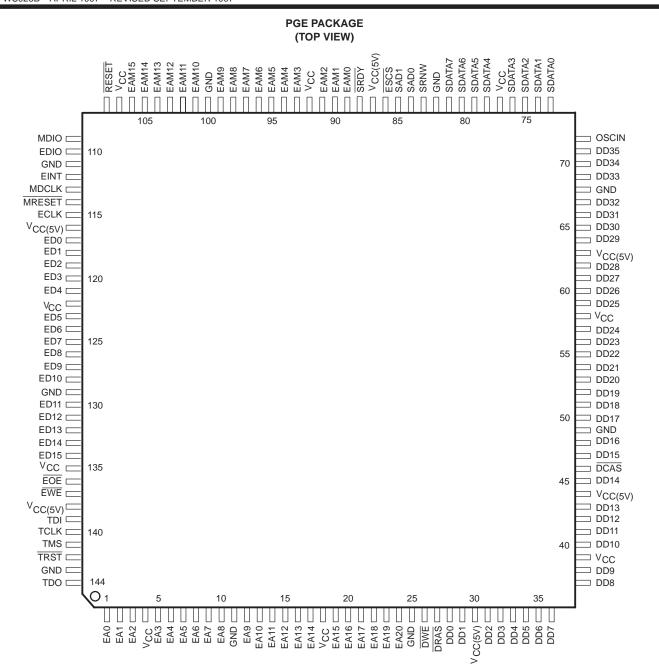

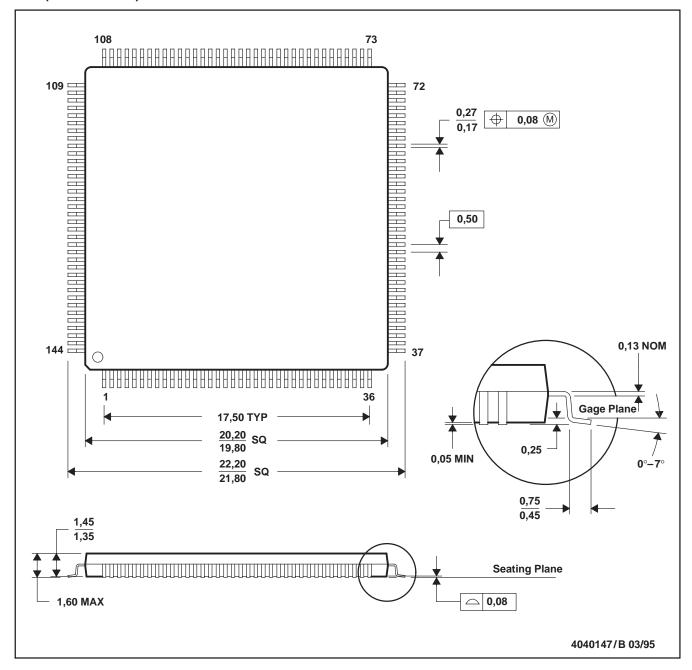

- Packaged in 144-Terminal Plastic Quad **Flatpack**

- **JTAG Compliant**

## description

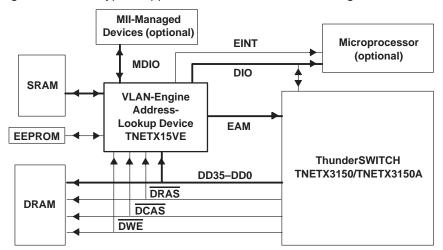

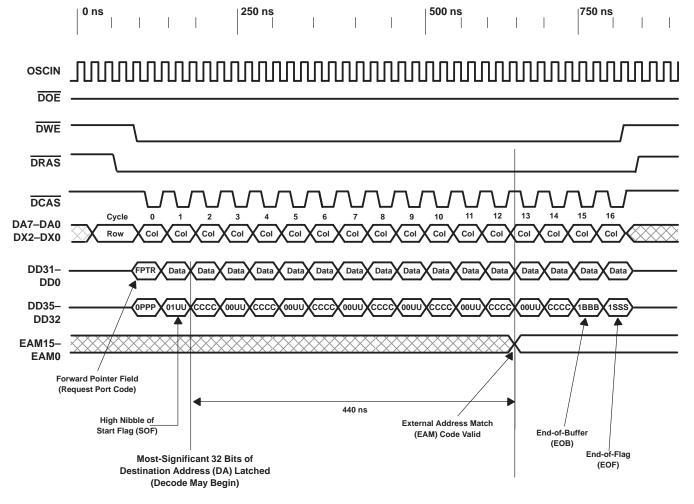

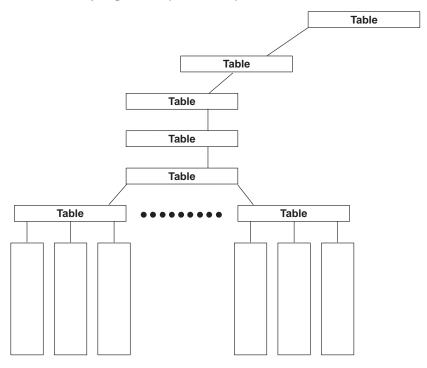

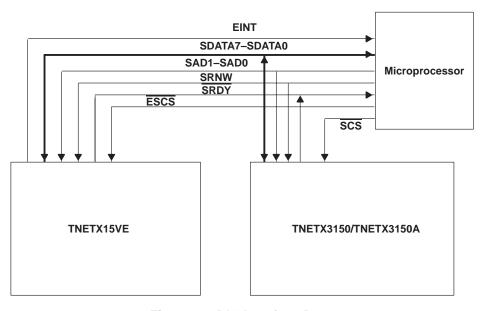

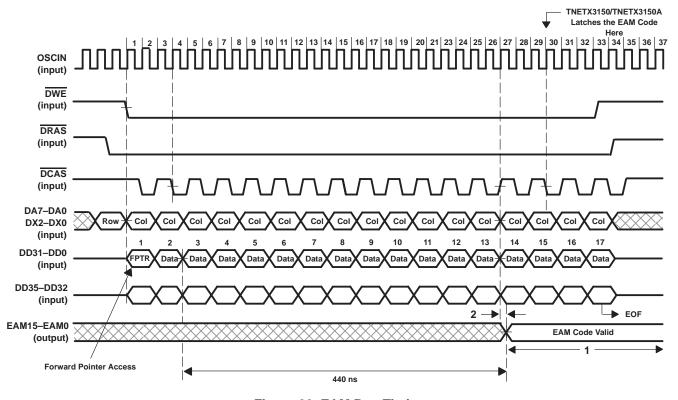

The TNETX15VE performs the VLAN-engine address-lookup function for the TNETX3150/TNETX3150A Ethernet™ switch using a glueless interface. The TNETX15VE device determines the addresses to use and match from the TNETX3150/TNETX3150A DRAM bus. The address-lookup table is maintained in external SRAM. The frame-matching and routing information is given to the TNETX3150/TNETX3150A through the external address-matching (EAM) interface.

The TNETX15VE is designed to work in either unmanaged or managed mode. Unmanaged operation is accomplished through EEPROM support. Startup options are auto-loaded into the TNETX15VE registers using the EEPROM interface. If the TNETX15VE is initialized by automatic loading from the EEPROM, it begins operation automatically.

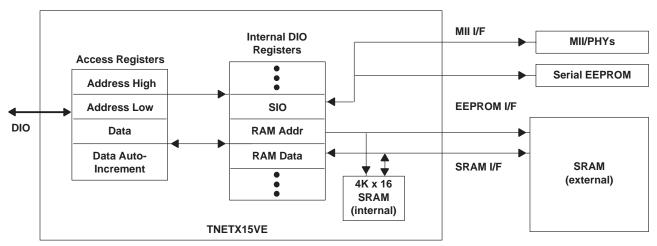

All functions of this device are fully controllable by management through a direct input/output (DIO) interface. In addition, this device can interrupt the external management processor with user-selectable interrupts.

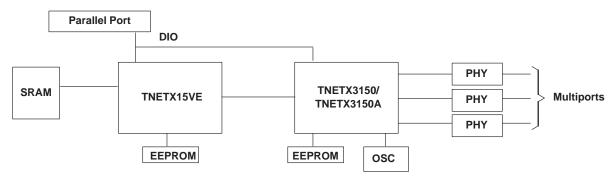

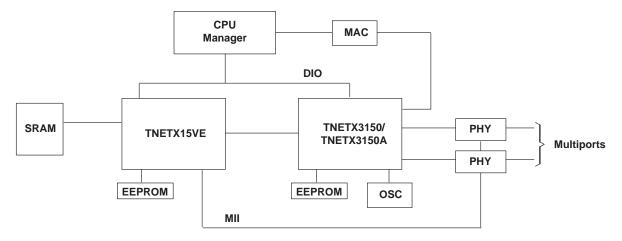

This device also provides support for easy management control of IEEE Std 802.3u media-independent interface (MII) managed devices. A typical application is shown in the following:

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

ThunderSWITCH is a trademark of Texas Instruments Incorporated Ethernet is a trademark of Xerox Corporation.

## functional block diagram

SPWS028B - APRIL 1997 - REVISED SEPTEMBER 1997

## general description

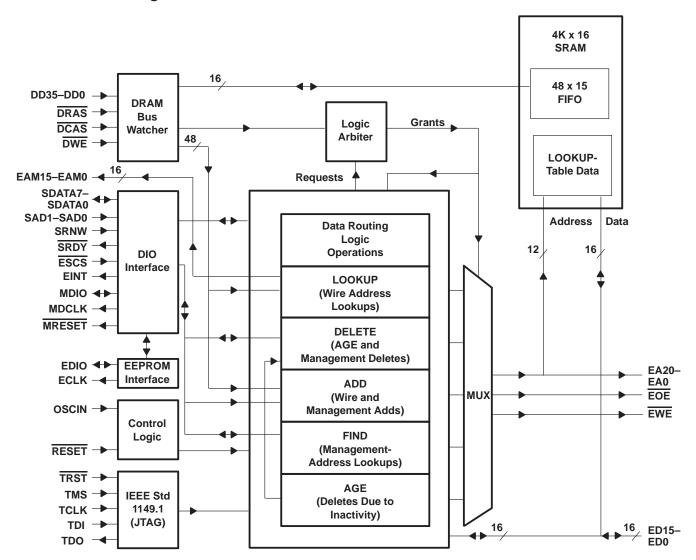

#### bus watcher

The bus watcher interfaces to the TNETX3150/TNETX3150A DRAM interface and extracts destination, source addresses, VLAN information, and the originating port number. The bus watcher is responsible for identifying the frame's start-of-frame and end-of-frame tags. It also interfaces to the arbiter and the TNETX15VE logic to perform off-the-wire address LOOKUPs and ADDs.

#### **DIO** interface

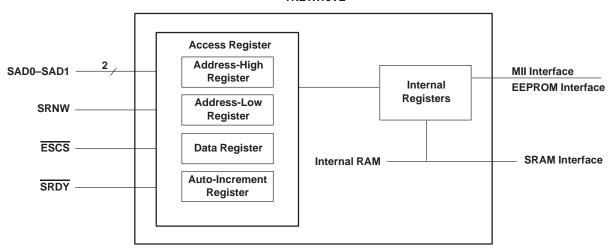

The DIO interface enables an attached microprocessor to access the TNETX15VE internal registers. The DIO interface is used to select control modes, read statistics, receive interrupts, read/write to attached MII devices, read/write to an attached EEPROM, and perform management LOOKUPs, ADDs, and DELETEs.

#### **EEPROM** interface

The EEPROM interface allows accesses to the EEPROM. It also interfaces with the EEPROM for automatic loading of selected registers from the EEPROM at startup or reset.

#### arbiter

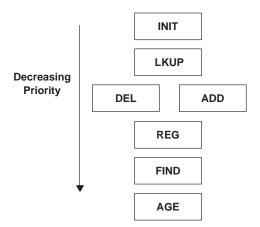

The arbiter manages the SRAM access for the TNETX15VE logic operations by assigning priorities to the logic operations. Wire lookups have the highest priority, followed by DELETEs, ADDs, management LOOKUPs, and AGEs. The individual logic operations request the bus by asserting a request signal. The arbiter grants the SRAM bus by controlling the SRAM-bus address/data multiplexer.

## SRAM address/data multiplexer (MUX)

The address/data MUX is controlled by the arbiter and selects the logic operation that has ownership of the SRAM bus.

## **TNETX15VE logic operations**

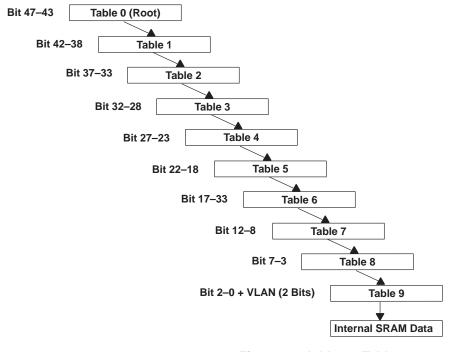

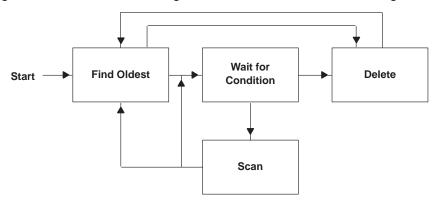

The TNETX15VE logic operations consist of LOOKUP, DELETE, ADD, FIND, and AGE operations. Each logic operation is assigned a priority on the SRAM bus and is controlled by the arbiter. The LOOKUP operation has the highest priority and is responsible for wire lookups. The DELETE operation is responsible for either deletes from the AGE operation or for management-delete requests. The ADD operation is responsible for wire adds as well as for management-add requests. The FIND operation is responsible for management searches of the lookup table. The AGE operation is responsible for deleting addresses that have no activity in a fixed time period.

SPWS028B - APRIL 1997 - REVISED SEPTEMBER 1997

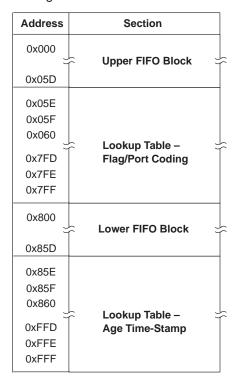

#### internal 4K × 16 SRAM

The TNETX15VE integrates an internal 4K × 16 SRAM that is used to store the following:

- A one-address-per-port FIFO as part of the bus watcher

- A 32-address FIFO for bridge protocol data unit (BPDU) sources during spanning-tree resolution

- A two-word data entry for each address it has learned

The addresses that the TNETX15VE recognizes are stored as a series of pointers in external ( $\times$ 16) static RAM. The size of the internal RAM imposes a hard limit to the number of addresses that the TNETX15VE can support.

## IEEE Std 1149.1 test port (JTAG)

The test-access port is composed of five terminals that are used to interface serially with the device and the board on which it is installed for boundary-scan testing. The TNETX15VE is fully JTAG compliant, with the exception of requiring external pullup resistors on terminals TDI, TMS, and TRST.

SPWS028B - APRIL 1997 - REVISED SEPTEMBER 1997

| Coi                                                  | ntents                                                    |

|------------------------------------------------------|-----------------------------------------------------------|

| Terminal Functions 7                                 | Internal Operation (Continued)                            |

| Register Descriptions13                              | Software Reset 73                                         |

| General Notation Notes                               | EEPROM Initialization/Automatic Loading (LOAD)            |

| Node Address Format                                  | TNETX15VE Operational Modes                               |

| DIO Register Access                                  | NAUTO Mode                                                |

| DIO Address Register                                 | NCRC Mode                                                 |

| DIO Data Auto-Increment Register                     | Aging Modes (Agingtimer Register)                         |

| Internal Register Map15                              | NLRN Mode77                                               |

| Default Register Values at Reset                     | TX Block Mode                                             |

| EEPROM Auto-Configuration From an                    | RX Block Mode                                             |

| External x24C02 EEPROM                               | Lookup Table SRAM Initialization (START)                  |

| Internal Register Descriptions                       | Frame Forwarding-LKUP Logic Operation                     |

| Revision Register                                    | Management-Based Lookups (FIND)                           |

| Age-Deletion Time-Select Register                    | FIND, FINDFIRST, FINDNEXT, and FINDNEW 79                 |

| Learning-Disable Register                            | VLAN and Port Find Modifier Bits                          |

| Mode-Control Status Register                         | FIFO FINDS (NBFR-No Broadcast FIFO Reads)                 |

| Serial Interface I/O Register                        | Summary of FIND Operations Supported                      |

| Management-Table Lookup Interface                    | NAUTO Mode                                                |

| Statistics Registers                                 | NLRN Mode85                                               |

| SRAM Address Register                                | NCRC Mode 85                                              |

| Interrupt Register                                   | Management Address Adding85                               |

| Interrupt Masking Register                           | Adding Unicasts and Multicast Addresses                   |

| New-Add Aged-Del Register Set                        | Deleting an Address                                       |

| New-Node/Port-Change/Security-Violation Interrupt 35 | Aging (AGE Logic Operation)                               |

| Agednode Interrupt Interface Group                   | Time-Threshold Aging                                      |

| Management Add/Edit Address Interface                | DEL Logic Operation (Management Address Deletions) 88     |

| Lookup Table Add/Delete Command Register             | Interrupts                                                |

| Management Delete Address Interface Group41          | Masking Interrupts                                        |

| VLAN Registers                                       | Test Interrupts (INT)                                     |

| VLAN Routing Mask Registers                          | ADD Interrupts90                                          |

| Port 00 Tag VLAN Array45                             | Aging Interrupts (AGE, AGEM)                              |

| Port VLANID Assignment Registers 46                  | Statistic Interrupt (STAT) 90 FIND Interrupt (FNDCPLT) 90 |

| Monitor Registers                                    | NBLCK RX FIFO Interrupt (RXFIFO) 90                       |

| Uplink Routing Register                              | IEEE Std 1149.1 Test-Access Port (JTAG)                   |

| Mirror Port Select Register                          | Absolute Maximum Ratings 92                               |

| Forwarding Block Register                            | Recommended Operating Conditions                          |

| Receive Block Register                               | Electrical Characteristics                                |

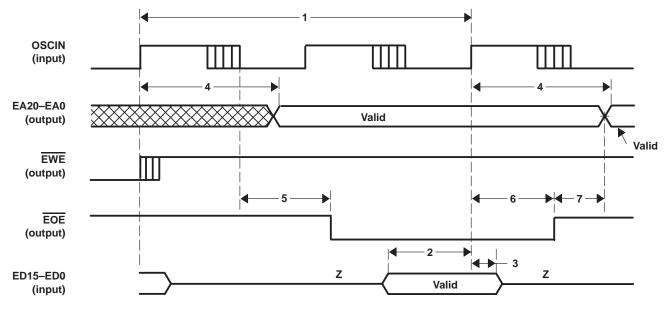

| Attached Microprocessor's Define/Routing Register 49 | Timing Requirements – External SRAM Read Cycle            |

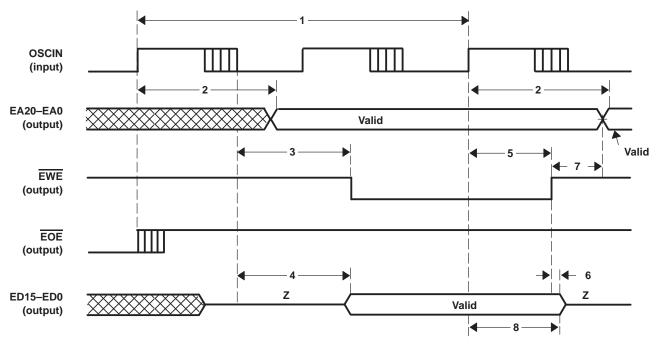

| Principles of Operation50                            | Timing Requirements – External SRAM Write Cycle 94        |

| Internal Operation50                                 | Operating Characteristics – External SRAM Write Cycle 94  |

| EAM Codings and In-Order Broadcasts (IOB)50          | Operating Characteristics – EAM Routing Code 95           |

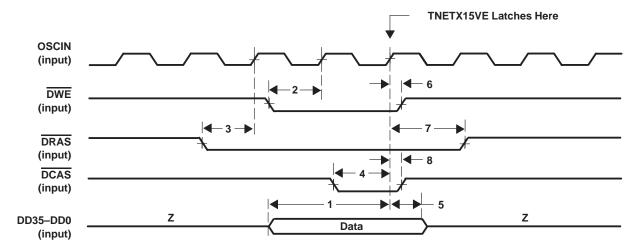

| TNETX15VE DRAM and EAM Interface                     | Timing Requirements – DRAM Interface96                    |

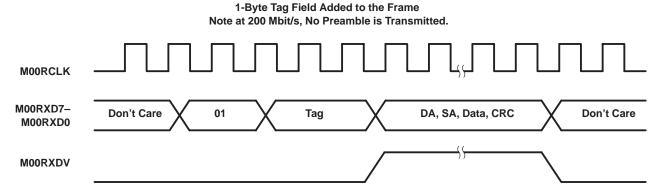

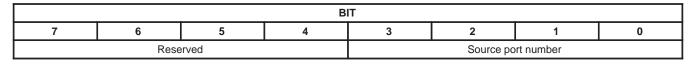

| Tag Field                                            | Timing Requirements – DIO Read Cycle                      |

| CRC Checking and Valid Frames                        | Operating Characteristics – DIO Read Cycle                |

| Operating Logic Arbitration                          | Operating Characteristics – DIO Write Cycle98             |

| Lookup Algorithm55                                   | Operating Characteristics – EEPROM Interface Timing 99    |

| A Graphical Example of the Lookup Algorithm 57       | Timing Requirements – OSCIN Clock                         |

| SRAM Data Storage                                    | Timing Requirements – Power-On Reset                      |

| Internal SRAM Allocation                             | Timing Requirements – RESET (Software) Timing 101         |

| Lookup Table SRAM Allocation                         | Parameter Measurement Information                         |

| Source Port is 01 Through 14                         | Application Information                                   |

| Source Port is 00 (Uplink)                           | TNETX15VE/TNETX3150/TNETX3150A                            |

| RAMsize and Number of Nodes Supported 65             | Stand-Alone Applications                                  |

| Register Spaces/External Devices Accessible 66       | Unmanaged Switch                                          |

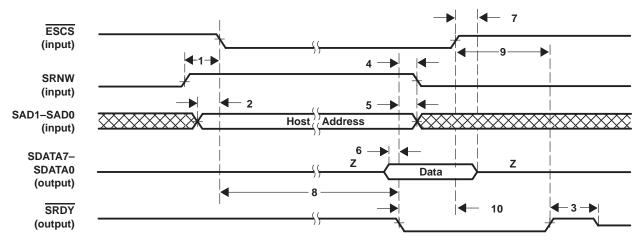

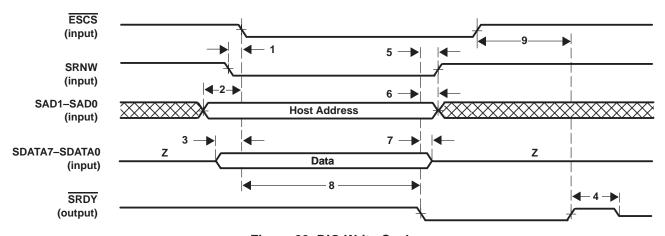

| DIO Interface                                        | Managed Switch                                            |

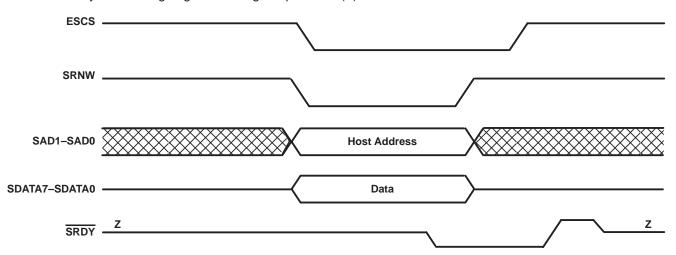

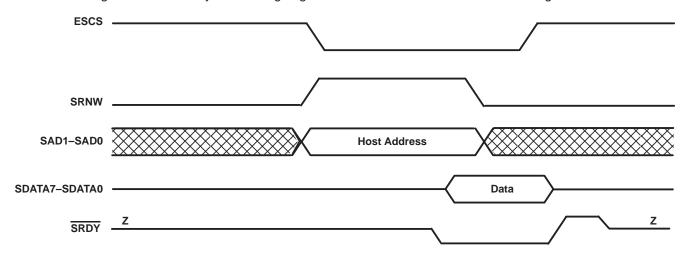

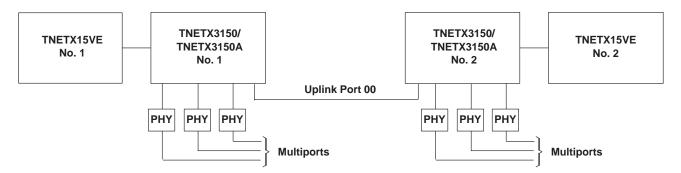

| DIO Write Cycle                                      | Expansion Through Uplink                                  |

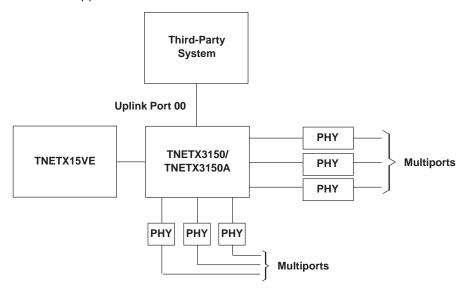

| Host (Access) Register Space70                       | VLAN Support for Proprietary Systems                      |

| Internal Registers                                   | Duplicate Address Support Through VLAN                    |

| Lookup-Table SRAM Access71                           | TNETX15VE VLAN Support                                    |

| Serial Interface – MII-Managed Devices               | VLAN Support for Cascaded Systems                         |

| x24C02 EEPROM Interface                              | Spanning-Tree Support110                                  |

| Initialization                                       | Transmitting BPDÜ Frames                                  |

| TNETX3150/TNETX3150A Initialization                  | iniccitatifical Data                                      |

| Hardware Reset73                                     |                                                           |

## **Terminal Functions**

## **EAM** interface

| TERMIN             | IAL | .,, | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

|--------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| NAME               | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| EAM15 <sup>†</sup> | 106 |     | External address match single-/multiple-port routing code select. When EAM15 is high, the EAM-interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|                    |     |     | terminals contain a single-port routing code. When EAM15 is low, the EAM-interface terminals contain a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

| EAM14              | 105 |     | multiple-port routing code (VLAN).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| EAM13              | 104 |     | sternal address match port routing code select. When EAM15 is high, the EAM14–EAM0 terminals are aced in the single-port mode. In this mode EAM14–EAM0 terminals encode a single port to which the time is routed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| EAM12              | 103 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

|                    |     |     | EAM14–EAM5 are don't-care bits and are set to 0. The single-port codes (EAM15–EAM0 terminals) are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

| EAM11              | 102 |     | own in the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM10              | 101 |     | TNETX3150/TNETX3150A EAM15-EAM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| E4140              | 00  |     | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM9               | 99  |     | Port 00 (uplink) 1 0 0 0 0 0 0 0 0 0 0 0 0 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| EAM8               | 98  |     | Port 01 1 0 0 0 0 0 0 0 0 0 0 0 0 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|                    |     | 0   | Port 02 1 0 0 0 0 0 0 0 0 0 0 0 1 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM7               | 97  |     | Port 03 1 0 0 0 0 0 0 0 0 0 0 0 1 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM6               | 96  |     | Port 04 1 0 0 0 0 0 0 0 0 0 0 1 0 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| LAMO               | 50  |     | Port 05 1 0 0 0 0 0 0 0 0 0 0 0 1 0 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| EAM5               | 95  |     | Port 06 1 0 0 0 0 0 0 0 0 0 0 1 1 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM4               | 94  |     | Port 07 1 0 0 0 0 0 0 0 0 0 0 1 1 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAIVI4             | 34  |     | Port 08 1 0 0 0 0 0 0 0 0 0 1 0 0 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM3               | 93  |     | Port 09 1 0 0 0 0 0 0 0 0 0 1 0 0 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|                    | 04  |     | Port 10 1 0 0 0 0 0 0 0 0 0 1 0 1 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM2               | 91  |     | Port 11 1 0 0 0 0 0 0 0 0 0 1 0 1 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| EAM1               | 90  |     | Port 12 1 0 0 0 0 0 0 0 0 0 1 1 0 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|                    |     |     | Port 13 1 0 0 0 0 0 0 0 0 0 0 1 1 0 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| EAM0 <sup>‡</sup>  | 89  |     | Port 14 1 0 0 0 0 0 0 0 0 0 1 1 1 0 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|                    |     |     | Reserved 1 0 0 0 0 0 0 0 0 0 1 1 1 1 b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

|                    |     |     | No-operation code 1 x x x x x x x x x x x x x b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

|                    |     |     | the no-operation code signals that the EAM device does not take part in forwarding decisions on this cket. The TNETX15VE does not put out this code in normal operations. To successfully disable the IETX15VE, it is reset and not started. This causes the EAM interface to float, and external pullup sistors are required on EAM15 and EAM04 (minimally) to supply the no-operation code to the IETX3150/TNETX3150A device. Erratic operation occurs if the TNETX3150/TNETX3150A address atching is not enabled when the TNETX15VE is disabled. The TNETX15VE, when enabled, overrides a operations of the TNETX3150/TNETX3150A matching circuitry; but, it is strongly advised to disable a TNETX3150/TNETX3150A address matching if the TNETX15VE is active. This prevents two logic books from attempting to control port suspension and other functions. |  |  |  |  |  |  |  |  |  |  |

<sup>†</sup> Most-significant bit

<sup>‡</sup> Least-significant bit

# **Terminal Functions (Continued)**

# **EAM** interface (continued)

| TERMI | TERMINAL |     |                                                               |                                                  |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                                        |                                         | ECCD                       | IDTIO                                |                                        |                                    |                            |                                       |                   |                        |           |     |

|-------|----------|-----|---------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|-----------------------------------------|----------------------------|--------------------------------------|----------------------------------------|------------------------------------|----------------------------|---------------------------------------|-------------------|------------------------|-----------|-----|

| NAME  | NO.      | 1/0 |                                                               | DESCRIPTION                                      |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                                        |                                         |                            |                                      |                                        |                                    |                            |                                       |                   |                        |           |     |

|       |          |     | – A (<br>Terminal n<br>following:                             | ch bit<br>1 on th<br>0 on th<br>umbe             | on the<br>ne bit s<br>ne bit s                  | EAM<br>signifie<br>signifie<br>nmen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14–Eas thates thates thates have    | AM0 b<br>t the d<br>t the d<br>ve a or | us is o<br>ata fra<br>ata fra<br>ne-to- | coded ame is ame is one co | as fol<br>route<br>not ro<br>prrespo | lows: d to the outed to onden  6  Port | at port                            | t. port. the po            |                                       | bers a            | as sho                 | own in    | the |

|       |          |     | For examp or 0x0125 Some pact are applied (EAM15 = To discard | is sen<br>kets, o<br>d (VLA<br>1) to r<br>a fran | it.<br>originall<br>N, one<br>reduce<br>ne, a c | ly dese of the october of the octobe | tined<br>e dest<br>perati<br>f 0x00 | for mu<br>inatior<br>ions re<br>000 is | ltiple ports<br>equired<br>outpu        | oorts, is a south          | need t<br>irce po<br>ne TNE          | o be s<br>ort, etc<br>ETX31<br>outing  | ent on<br>:.). TN<br>50/TN<br>code | lly to a<br>ETX15<br>NETX3 | single<br>5VE us<br>3150A.<br>o ports | port a<br>ses sir | after rengle-potential | estrictio | ons |

|       |          |     |                                                               |                                                  | Dis                                             | scard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fram                                | е                                      | 0                                       | 0 0                        | 0                                    | 0 0                                    | 0 0                                | 0 (                        | 0 0                                   | 0 0               | 0 0                    |           |     |

# **Terminal Functions (Continued)**

## **DRAM** interface

| TERMIN |     | 1/0 | DESCRIPTION                                                              |

|--------|-----|-----|--------------------------------------------------------------------------|

| NAME   | NO. |     |                                                                          |

| DD35†  | 71  |     |                                                                          |

| DD34   | 70  |     |                                                                          |

| DD33   | 69  |     |                                                                          |

| DD32   | 67  |     |                                                                          |

| DD31   | 66  |     |                                                                          |

| DD30   | 65  |     |                                                                          |

| DD29   | 64  |     |                                                                          |

| DD28   | 62  |     |                                                                          |

| DD27   | 61  |     |                                                                          |

| DD26   | 60  |     |                                                                          |

| DD25   | 59  |     |                                                                          |

| DD24   | 57  |     |                                                                          |

| DD23   | 56  |     |                                                                          |

| DD22   | 55  |     |                                                                          |

| DD21   | 54  |     |                                                                          |

| DD20   | 53  |     |                                                                          |

| DD19   | 52  |     |                                                                          |

| DD18   | 51  | ı   | DRAM data bus. Data bus is sourced by the TNETX3150/TNETX3150A.          |

| DD17   | 50  | '   | DRAIN data bus. Data bus is sourced by the TNETASTSO/TNETASTSOA.         |

| DD16   | 48  |     |                                                                          |

| DD15   | 47  |     |                                                                          |

| DD14   | 45  |     |                                                                          |

| DD13   | 43  |     |                                                                          |

| DD12   | 42  |     |                                                                          |

| DD11   | 41  |     |                                                                          |

| DD10   | 40  |     |                                                                          |

| DD9    | 38  |     |                                                                          |

| DD8    | 37  |     |                                                                          |

| DD7    | 36  |     |                                                                          |

| DD6    | 35  |     |                                                                          |

| DD5    | 34  |     |                                                                          |

| DD4    | 33  |     |                                                                          |

| DD3    | 32  |     |                                                                          |

| DD2    | 31  |     |                                                                          |

| DD1    | 29  |     |                                                                          |

| DD0‡   | 28  |     |                                                                          |

| DCAS   | 46  | I   | DRAM column address select. DCAS is sourced by the TNETX3150/TNETX3150A. |

| DRAS   | 27  | I   | DRAM row address select. DRAS is sourced by the TNETX3150/TNETX3150A.    |

| DWE    | 26  | Ι   | DRAM write enable. DWE is sourced by the TNETX3150/TNETX3150A.           |

<sup>†</sup> Most-significant bit ‡ Least-significant bit

# **Terminal Functions (Continued)**

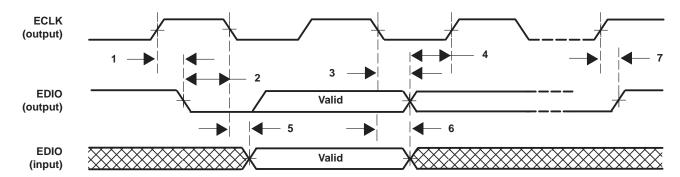

## external SRAM interface

| TERMIN            | IAL | 1/0 | DESCRIPTION                                                                                       |  |  |  |  |  |  |  |  |

|-------------------|-----|-----|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| NAME              | NO. | "0  | DESCRIPTION                                                                                       |  |  |  |  |  |  |  |  |

| EA20              | 24  |     | EA20 indicates an internal or external RAM access. 0 = external, 1 = internal.                    |  |  |  |  |  |  |  |  |

| EA19 <sup>†</sup> | 23  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA18              | 22  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA17              | 21  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA16              | 20  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA15              | 19  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA14              | 17  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA13              | 16  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA12              | 15  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA11              | 14  | 1   |                                                                                                   |  |  |  |  |  |  |  |  |

| EA10              | 13  | 0   | External address bus. EA20–EA0 is the external SRAM address bus. This bus is always driven except |  |  |  |  |  |  |  |  |

| EA9               | 12  |     | during reset.                                                                                     |  |  |  |  |  |  |  |  |

| EA8               | 10  |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA7               | 9   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA6               | 8   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA5               | 7   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA4               | 6   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA3               | 5   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA2               | 3   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA1               | 2   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EA0‡              | 1   |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED15 <sup>†</sup> | 134 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED14              | 133 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED13              | 132 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED12              | 131 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED11              | 130 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED10              | 128 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED9               | 127 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED8               | 126 | 1/0 | Futament data hije FD45 FD0 is the enternal SDAM data hije                                        |  |  |  |  |  |  |  |  |

| ED7               | 125 | I/O | External data bus. ED15–ED0 is the external SRAM data bus.                                        |  |  |  |  |  |  |  |  |

| ED6               | 124 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED5               | 123 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED4               | 121 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED3               | 120 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED2               | 119 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED1               | 118 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| ED0‡              | 117 |     |                                                                                                   |  |  |  |  |  |  |  |  |

| EOE               | 136 | 0   | External output enable. EOE is the active-low external SRAM output-enable signal.                 |  |  |  |  |  |  |  |  |

| EWE               | 137 | 0   | External write enable. EWE is the active-low external SRAM write-enable signal.                   |  |  |  |  |  |  |  |  |

<sup>†</sup> Most-significant bit ‡ Least-significant bit

# **Terminal Functions (Continued)**

# DIO interface statistics interface

| TERMIN              | AL  | 1/0  | DESCRIPTION                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 |                                         |  |  |  |  |  |  |

|---------------------|-----|------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| NAME                | NO. |      |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 | •                                       |  |  |  |  |  |  |

| EINT                | 112 | 0    | microproces<br>operationals<br>(0x28, 0x29 | TNETX15VE interrupt. EINT is an interrupt request from the TNETX15VE to an optional attached microprocessor. Its purpose is to reduce the polling that is required for the processor to be current on the operational states of the TNETX15VE. The interrupt cause is determined by reading the interrupt register (0x28, 0x29). It is not required to acknowledge or act on the interrupts (unmanaged operation). EINT is active high and level sensitive; it is high when any of the interrupt triggers are active. |         |                                                                 |                                         |  |  |  |  |  |  |

| ESCS                | 86  | I    |                                            | TNETX15VE chip select. When ESCS is active (low), a port access is valid for the TNETX15VE device. ESCS must not be tied to any other chip-select signal (such as the TNETX3150/TNETX3150A SCS).                                                                                                                                                                                                                                                                                                                      |         |                                                                 |                                         |  |  |  |  |  |  |

|                     |     |      | DIO address                                | s bus. SA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AD1-SAD | 00 selects the TNETX15VE h                                      | ost registers.                          |  |  |  |  |  |  |

|                     |     |      |                                            | SAD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SAD0    | DESCRIPTION                                                     |                                         |  |  |  |  |  |  |

| SAD1                | 85  | ١, ١ |                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0       | DIO address low                                                 |                                         |  |  |  |  |  |  |

| SAD0                | 84  | l '  |                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1       | DIO address high                                                |                                         |  |  |  |  |  |  |

|                     |     |      |                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0       | DIO data                                                        |                                         |  |  |  |  |  |  |

|                     |     |      |                                            | 1 1 DIO data auto-increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                                                                 |                                         |  |  |  |  |  |  |

| SDATA7 <sup>†</sup> | 81  |      |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 |                                         |  |  |  |  |  |  |

| SDATA6              | 80  |      |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 |                                         |  |  |  |  |  |  |

| SDATA5              | 79  |      |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 |                                         |  |  |  |  |  |  |

| SDATA4              | 78  |      | 5.5                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 | 15101                                   |  |  |  |  |  |  |

| SDATA3              | 76  | I/O  | DIO data bu                                | is. SDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A7-SDAI | A0 is a byte-wide bidirection                                   | al DIO bus.                             |  |  |  |  |  |  |

| SDATA2              | 75  |      |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 |                                         |  |  |  |  |  |  |

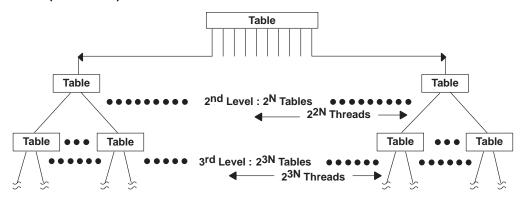

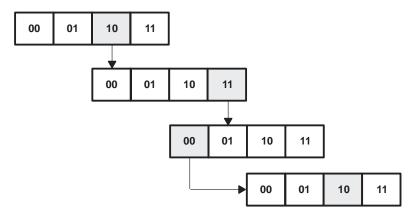

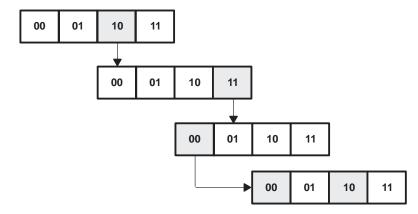

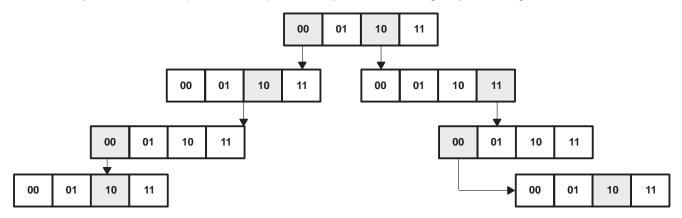

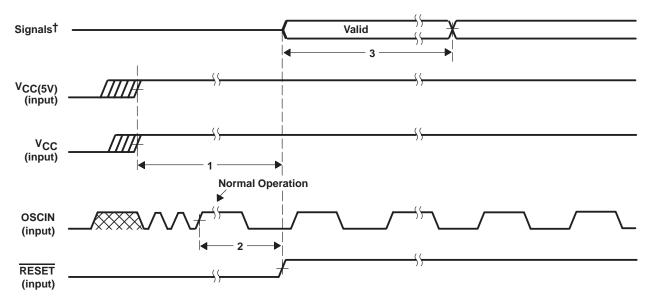

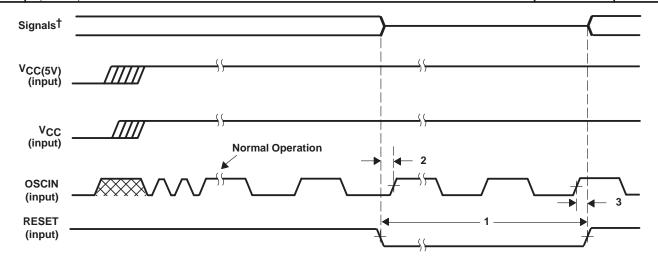

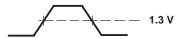

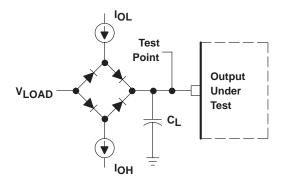

| SDATA1              | 74  |      |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                 |                                         |  |  |  |  |  |  |