#### **General Description**

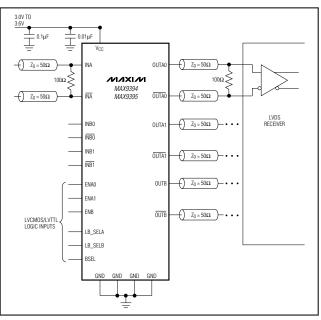

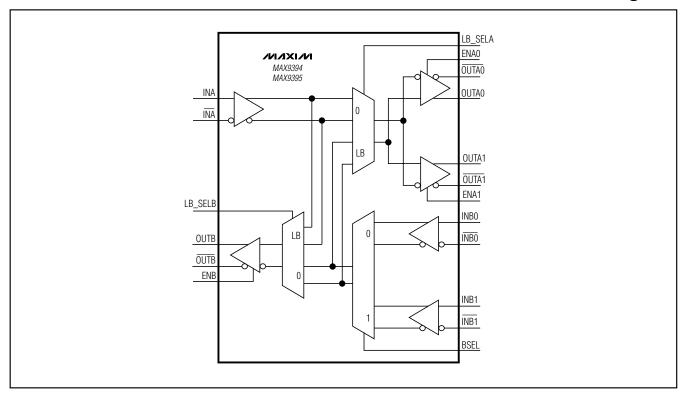

The MAX9394/MAX9395 consist of a 2:1 multiplexer and a 1:2 demultiplexer with loopback. The multiplexer section (channel B) accepts two low-voltage differential signaling (LVDS) inputs and generates a single LVDS output. The demultiplexer section (channel A) accepts a single LVDS input and generates two parallel LVDS outputs. The MAX9394/MAX9395 feature a loopback mode that connects the input of channel A to the output of channel B and connects the selected input of channel B to the outputs of channel A.

Three LVCMOS/LVTTL logic inputs control the internal connections between inputs and outputs, one for the multiplexer portion of channel B (BSEL), and the other two for loopback control of channels A and B (LB\_SELA and LB\_SELB). Independent enable inputs for each differential output pair provide additional flexibility.

Fail-safe circuitry forces the outputs to a differential low condition for undriven inputs or when the commonmode voltage exceeds the specified range. The MAX9394 provides high-level input fail-safe detection for HSTL, LVDS, and other GND-referenced differential inputs. The MAX9395 provides low-level fail-safe detection for CML, LVPECL, and other V<sub>CC</sub>-referenced differential inputs.

Ultra low 91ps<sub>P-P</sub> (max) pseudorandom bit sequence (PRBS) jitter ensures reliable communications in highspeed links that are highly sensitive to timing error, especially those incorporating clock-and-data recovery, or serializers and deserializers. The high-speed switching performance guarantees 1.5GHz operation and less than 87ps (max) skew between channels.

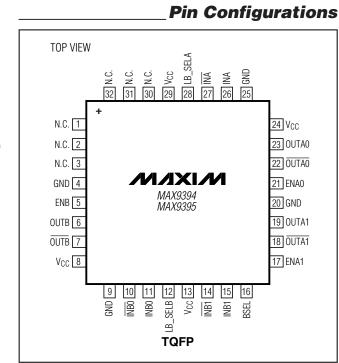

LVDS inputs and outputs are compatible with the TIA/EIA-644 LVDS standard. The LVDS outputs drive 100 $\Omega$  loads. The MAX9394/MAX9395 are offered in a 32-pin TQFP package and operate over the extended temperature range (-40°C to +85°C).

#### **Applications**

High-Speed Telecom/Datacom Equipment

Central Office Backplane Clock Distribution

DSLAM

Protection Switching

Fault-Tolerant Systems

Pin Configurations and Functional Diagram appear at end of data sheet.

#### \_\_ Features

Guaranteed 1.5GHz Operation with 250mV Differential Output Swing

- Simultaneous Loopback Control

- 2ps<sub>(RMS)</sub> (max) Random Jitter

- AC Specifications Guaranteed for 150mV Differential Input

- Signal Inputs Accept Any Differential Signaling Standard

- LVDS Outputs for Clock or High-Speed Data

- ♦ High-Level Input Fail-Safe Detection (MAX9394)

- Low-Level Input Fail-Safe Detection (MAX9395)

- ♦ 3.0V to 3.6V Supply Voltage Range

- LVCMOS/LVTTL Logic Inputs

#### \_Ordering Information

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|-------------|----------------|-----------------|-------------|

| MAX9394EHJ  | -40°C to +85°C | 32 TQFP         | H32-1       |

| MAX9394EHJ+ | -40°C to +85°C | 32 TQFP         | H32-1       |

| MAX9395EHJ  | -40°C to +85°C | 32 TQFP         | H32-1       |

| MAX9395EHJ+ | -40°C to +85°C | 32 TQFP         | H32-1       |

+Denotes a lead-free package.

#### **\_Typical Operating Circuit**

#### M/XI/M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +4.1V                   | / |

|-------------------------------------------------------|---|

| N, TN, OUT, OUT, EN, _SEL, LB_SEL_                    |   |

| o GND0.3V to (V <sub>CC</sub> + 0.3V                  | ) |

| N to IN±3\                                            |   |

| Short-Circuit Duration (OUT, OUT)Continuous           | 3 |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |   |

| 32-Pin TQFP (derate 13.1mW/°C above +70°C)1047mW      | [ |

| Junction-to-Ambient Thermal Resistance in Still Air   |   |

32-Pin TQFP.....+76.4°C/W

| Operating Temperature Range       | 40°C to +85°C      |

|-----------------------------------|--------------------|

| Junction Temperature              | +150°C             |

| Storage Temperature Range         | 65°C to +150°C     |

| ESD Protection (Human Body Model) |                    |

| (IN, ĪN, OUT, OUT, EN,            | SEL_, LB_SEL_)±2kV |

| Soldering Temperature (10s)       | +300°C             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.0V \text{ to } 3.6V, R_{L} = 100\Omega \pm 1\%, EN_{_} = V_{CC}, V_{CM} = +0.05V \text{ to } (V_{CC} - 0.6V) (MAX9394), V_{CM} = +0.06V \text{ to } (V_{CC} - 0.05V) (MAX9395), T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = 3.3V$ ,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = 1.2V$ ,  $T_{A} = +25^{\circ}C$ .) (Notes 1, 2, and 3)

| PARAMETER                                                                        | SYMBOL            |                                       | CONDITIONS                                              | MIN   | ТҮР  | MAX                       | UNITS |

|----------------------------------------------------------------------------------|-------------------|---------------------------------------|---------------------------------------------------------|-------|------|---------------------------|-------|

| LVCMOS/LVTTL INPUTS (EN,                                                         | BSEL, LB_S        | EL_)                                  |                                                         |       |      |                           |       |

| Input High Voltage                                                               | VIH               |                                       |                                                         | 2.0   |      | V <sub>CC</sub>           | V     |

| Input Low Voltage                                                                | VIL               |                                       |                                                         | 0     |      | 0.8                       | V     |

| Input High Current                                                               | Ιн                | $V_{IN} = 2.0V$ to V                  | CC                                                      | 0     |      | 20                        | μA    |

| Input Low Current                                                                | ١ <sub>١Ľ</sub>   | $V_{IN} = 0V \text{ to } 0.8'$        | V                                                       | 0     |      | 10                        | μA    |

| DIFFERENTIAL INPUTS (IN, $\overline{IN}$                                         | ī)                |                                       |                                                         |       |      |                           |       |

| Differential Input Voltage                                                       | VID               | $V_{ILD} \ge 0V$ and $V_{ILD} \ge 0V$ | V <sub>IHD</sub> <u>&lt;</u> V <sub>CC</sub> , Figure 1 | 0.1   |      | 3.0                       | V     |

| Input Common-Mode Range                                                          |                   | MAX9394                               |                                                         | 0.05  |      | V <sub>CC</sub> -<br>0.6  | v     |

| input common-mode nange                                                          | V <sub>CM</sub>   | MAX9395                               |                                                         | 0.6   |      | V <sub>CC</sub> -<br>0.05 | V     |

| Input Current                                                                    | I <sub>IN</sub> , | MAX9394                               | $ V_{ID}  \le 3.0V$                                     | -75   |      | 10                        |       |

| Input Current                                                                    | ITN               | MAX9395                               | $ V_{ID}  \le 3.0V$                                     | -10   |      | 100                       | μA    |

| LVDS OUTPUTS (OUT, OUT                                                           | _)                |                                       |                                                         |       |      |                           |       |

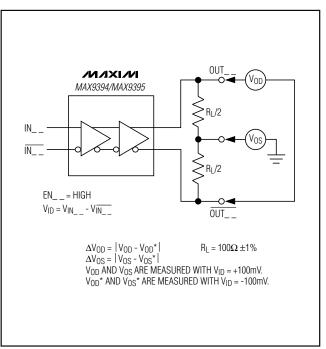

| Differential Output Voltage                                                      | Vod               | $R_L = 100\Omega$ , Fig               | ure 2                                                   | 250   | 350  | 450                       | mV    |

| Change in Magnitude of V <sub>OD</sub><br>Between Complementary Output<br>States | $\Delta V_{OD}$   | Figure 2                              |                                                         |       | 1.0  | 50                        | mV    |

| Offset Common-Mode Voltage                                                       | V <sub>OS</sub>   | Figure 2                              |                                                         | 1.125 | 1.25 | 1.375                     | V     |

| Change in Magnitude of V <sub>OS</sub><br>Between Complementary Output<br>States | ΔV <sub>OS</sub>  | Figure 2                              |                                                         |       | 1.0  | 50                        | mV    |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 3.0V \text{ to } 3.6V, R_L = 100\Omega \pm 1\%, EN_{-} = V_{CC}, V_{CM} = 0.05V \text{ to } (V_{CC} - 0.6V) \text{ (MAX9394)}, V_{CM} = 0.06V \text{ to } (V_{CC} - 0.05V) \text{ (MAX9395)}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = 3.3V, IV_{ID}I = 0.2V, V_{CM} = 1.2V, T_A = +25^{\circ}C.) \text{ (Notes 1, 2, and 3)}$

| ( , , ,                                                    |                     |                                              |                                         |     |     |     | -     |

|------------------------------------------------------------|---------------------|----------------------------------------------|-----------------------------------------|-----|-----|-----|-------|

| PARAMETER                                                  | SYMBOL              | CO                                           | NDITIONS                                | MIN | TYP | MAX | UNITS |

| Output Short-Circuit Current                               |                     | VID = ±100mV                                 | $V_{OUT}$ or $V_{\overline{OUT}}$ = 0V  |     | 30  | 40  |       |

| (Output(s) Shorted to GND)                                 | llosi               | (Note 4)                                     | V <sub>OUT</sub> =<br>V <u>OUT</u> = 0V |     | 17  | 24  | mA    |

| Output Short-Circuit Current<br>(Outputs Shorted Together) | ll <sub>OSB</sub> l | $V_{ID} = \pm 100 \text{mV}, V_O$            | UT= V <del>OUT</del> _ (Note 4)         |     | 5   | 12  | mA    |

| SUPPLY CURRENT                                             |                     |                                              |                                         |     |     |     |       |

|                                                            |                     | $R_L = 100\Omega$ , $EN_{-}$                 | = V <sub>CC</sub>                       |     | 53  | 65  |       |

| Supply Current                                             | ICC                 | R <sub>L</sub> = 100Ω, EN<br>670MHz (1.34Gbp | = V <sub>CC</sub> , switching at<br>os) |     | 53  | 65  | mA    |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0V \text{ to } 3.6V, f_{IN} < 1.34GHz, t_{R_IN} = t_{F_IN} = 125ps, R_L = 100\Omega \pm 1\%, |V_{ID}| \ge 150mV, V_{CM} = 0.075V \text{ to } (V_{CC} - 0.6V) \text{ (MAX9394 only)}, V_{CM} = 0.6V \text{ to } (V_{CC} - 0.075V) \text{ (MAX9395 only)}, EN_{\_} = V_{CC}, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted}. Typical values are at V_{CC} = 3.3V, |V_{ID}| = 0.2V, V_{CM} = 1.2V, f_{IN} = 1.34GHz, T_A = +25^{\circ}C.) \text{ (Note 5)}$

| PARAMETER                                          | SYMBOL           | CONDITIONS                                         | MIN | ТҮР  | MAX | UNITS   |

|----------------------------------------------------|------------------|----------------------------------------------------|-----|------|-----|---------|

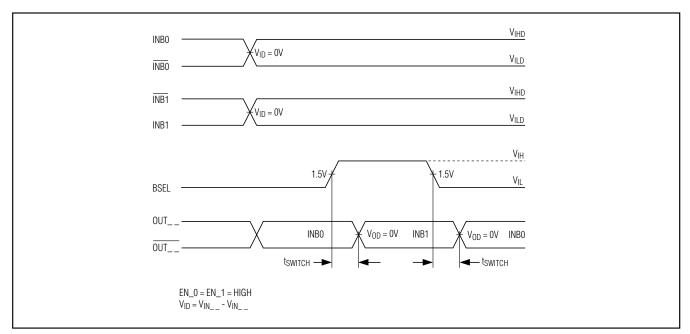

| SEL to Switched Output                             | tSWITCH          | Figure 3                                           |     |      | 1.1 | ns      |

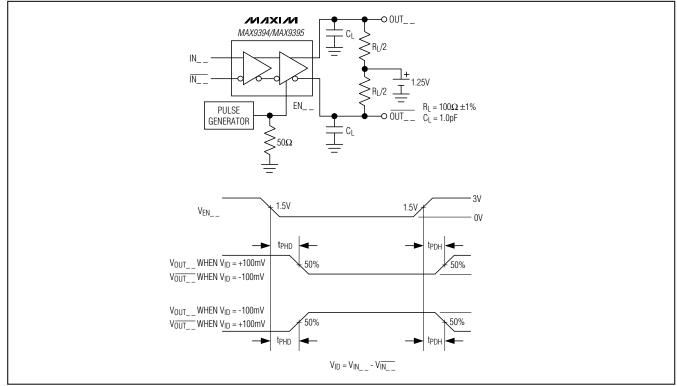

| Disable Time to Differential<br>Output Low         | t <sub>PHD</sub> | Figure 4                                           |     |      | 1.7 | ns      |

| Enable Time to Differential Output<br>High         | t <sub>PDH</sub> | Figure 4                                           |     |      | 1.7 | ns      |

| Switching Frequency                                | fMAX             | V <sub>OD</sub> ≥ 250mV                            | 1.5 | 2.2  |     | GHz     |

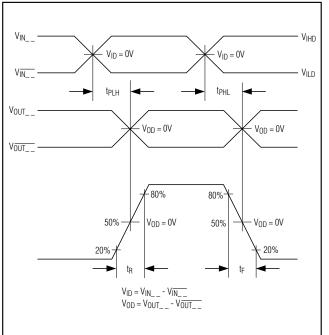

| Low-to-High Propagation Delay                      | <b>t</b> PLH     | Figures 1, 5                                       | 340 | 567  | 720 | ps      |

| High-to-Low Propagation Delay                      | t <sub>PHL</sub> | Figures 1, 5                                       | 340 | 562  | 720 | ps      |

| Pulse Skew It <sub>PLH</sub> – t <sub>PHL</sub> I  | <b>t</b> SKEW    | Figures 1, 5 (Note 6)                              |     | 12.4 | 86  | ps      |

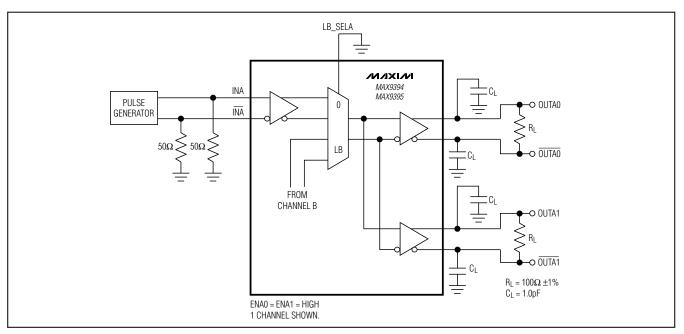

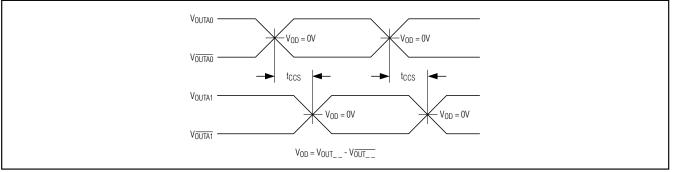

| Output Channel-to-Channel Skew                     | tccs             | Figure 6 (Note 7)                                  |     | 16   | 87  | ps      |

| Output Low-to-High Transition<br>Time (20% to 80%) | t <sub>R</sub>   | $f_{IN_{-}} = 100MHz$ , Figures 1, 5               | 112 | 154  | 187 | ps      |

| Output High-to-Low Transition<br>Time (80% to 20%) | t <sub>F</sub>   | $f_{IN_{-}} = 100MHz$ , Figures 1, 5               | 112 | 152  | 187 | ps      |

| Added Random Jitter                                | t <sub>RJ</sub>  | f <sub>IN_</sub> = 1.34GHz, clock pattern (Note 8) |     |      | 2   | ps(RMS) |

| Added Deterministic Jitter                         | tDJ              | 1.34Gbps, 223 - 1 PRBS (Note 8)                    |     | 60   | 91  | psp-p   |

**Note 1:** Measurements obtained with the device in thermal equilibrium. All voltages referenced to GND except  $V_{ID}$ ,  $V_{OD}$ , and  $\Delta V_{OD}$ . **Note 2:** Current into the device defined as positive. Current out of the device defined as negative.

**Note 3:** DC parameters production tested at  $T_A = +25^{\circ}C$  and guaranteed by design and characterization for  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . **Note 4:** Current through either output.

**Note 5:** Guaranteed by design and characterization. Limits set at  $\pm 6$  sigma.

Note 6: t<sub>SKEW</sub> is the magnitude difference of differential propagation delays for the same output over the same conditions. t<sub>SKEW</sub> = lt<sub>PHL</sub> - t<sub>PLH</sub>l.

**Note 7:** Measured between outputs of the same device at the signal crossing points for a same-edge transition under the same conditions. Does not apply to loopback mode.

Note 8: Device jitter added to the differential input signal.

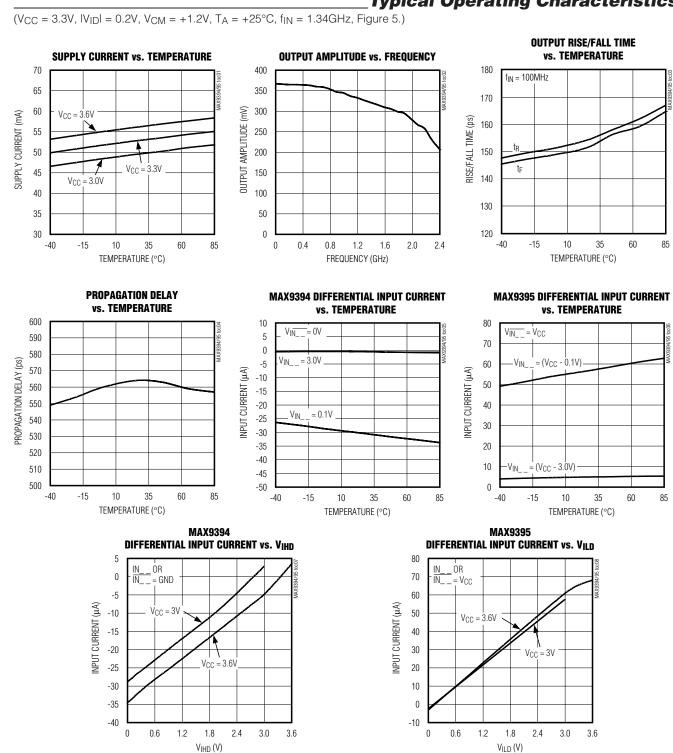

**Typical Operating Characteristics**

#### \_Pin Description

| PIN                    | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                    |

|------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 30,<br>31, 32 | N.C.    | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                    |

| 4, 9, 20, 25           | GND     | Ground                                                                                                                                                                                                                                                                                                                                                      |

| 5                      | ENB     | Channel B Output Enable. Drive ENB high to enable the LVDS outputs for channel B. An internal 435k $\Omega$ resistor to GND pulls ENB low when unconnected.                                                                                                                                                                                                 |

| 6                      | OUTB    | Channel B LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTB and $\overline{\text{OUTB}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                 |

| 7                      | OUTB    | Channel B LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTB and $\overline{\text{OUTB}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                    |

| 8, 13, 24,<br>29       | Vcc     | Power-Supply Input. Bypass each $V_{CC}$ to GND with a 0.1µF and 0.01µF ceramic capacitor. Install both bypass capacitors as close to the device as possible, with the 0.01µF capacitor closest to the device.                                                                                                                                              |

| 10                     | ĪNB0    | LVDS/HSTL (MAX9394) or LVPECL/CML (MAX9395) Inverting Input. An internal 128k $\Omega$ pullup resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9394). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9395).                                                                                         |

| 11                     | INB0    | LVDS/HSTL (MAX9394) or LVPECL/CML (MAX9395) Noninverting Input. An internal 128k $\Omega$ pullup resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9394). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9395).                                                                                      |

| 12                     | LB_SELB | Loopback Select for Channel B Output. Connect LB_SELB to GND or leave unconnected to reproduce the INB_ (INB_) differential inputs at OUTB (OUTB). Connect LB_SELB to V <sub>CC</sub> to loop back the INA (INA) differential inputs to OUTB (OUTB). An internal $435k\Omega$ resistor to GND pulls LB_SELB low when unconnected.                           |

| 14                     | ĪNB1    | LVDS/HSTL (MAX9394) or LVPECL/CML (MAX9395) Inverting Input. An internal 128k $\Omega$ pullup resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9394). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9395).                                                                                         |

| 15                     | INB1    | LVDS/HSTL (MAX9394) or LVPECL/CML (MAX9395) Noninverting Input. An internal 128k $\Omega$ pullup resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9394). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9395).                                                                                      |

| 16                     | BSEL    | Channel B Multiplexer Control Input. Selects the differential input to reproduce at the B channel differential output. Connect BSEL to GND or leave unconnected to select the INB0 (INB0) set of inputs. Connect BSEL to V <sub>CC</sub> to select the INB1 (INB1) set of inputs. An internal $435k\Omega$ resistor to GND pulls BSEL low when unconnected. |

| 17                     | ENA1    | Channel A1 Output Enable. Drive ENA1 high to enable the A1 LVDS outputs. An internal $435$ k $\Omega$ resistor to GND pulls the ENA1 low when unconnected.                                                                                                                                                                                                  |

| 18                     | OUTA1   | Channel A1 LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTA1 and $\overline{\text{OUTA1}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                 |

| 19                     | OUTA1   | Channel A1 LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTA1 and OUTA1 at the receiver inputs to ensure proper operation.                                                                                                                                                                                                  |

| -                      |         |                                                                                                                                                                                                                                                                                                                                                             |

|     |         | Pin Description (continued)                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |

| 21  | ENA0    | Channel A0 Output Enable. Drive ENA0 high to enable the A0 LVDS outputs. An internal $435k\Omega$ resistor to GND pulls ENA0 low when unconnected.                                                                                                                                                                                                                               |

| 22  | OUTA0   | Channel A0 LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTA0 and $\overline{\text{OUTA0}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                      |

| 23  | OUTA0   | Channel A0 LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTA0 and OUTA0 at the receiver inputs to ensure proper operation.                                                                                                                                                                                                                       |

| 26  | INA     | LVDS/HSTL (MAX9394) or LVPECL/CML (MAX9395) Noninverting Input. An internal 128k $\Omega$ pullup resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9394). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9395).                                                                                                           |

| 27  | ĪNĀ     | LVDS/HSTL (MAX9394) or LVPECL/CML (MAX9395) Inverting Input. An internal 128k $\Omega$ pullup resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9394). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9395).                                                                                                              |

| 28  | LB_SELA | Loopback Select for Channel A Output. Connect LB_SELA to GND or leave unconnected to reproduce the INA (INA) differential inputs at OUTA_ ( $\overline{OUTA}$ ). Connect LB_SELA to V <sub>CC</sub> to loop back the INB_ ( $\overline{INB}$ ) differential inputs to OUTA_ ( $\overline{OUTA}$ ). An internal 435k $\Omega$ resistor to GND pulls LB_SELA low when unconnected. |

Figure 1. Output Transition Time and Propagation Delay Timing Diagram

Figure 2. Test Circuit for VOD and VOS

Figure 3. Input to Rising/Falling Edge Select and Mux Switch Timing Diagram

M/IXI/M

Figure 4. Output Active-to-Disable and Disable-to-Active Test Circuit and Timing Diagram

Figure 5. Output Transition Time, Propagation Delay, and Output Channel-to-Channel Skew Test Circuit

M/IXI/M

Figure 6. Output Channel-to-Channel Skew

#### **Detailed Description**

The LVDS interface standard provides a signaling method for point-to-point communication over a controlled-impedance medium as defined by the ANSI TIA/EIA-644 standard. LVDS utilizes a lower voltage swing than other communication standards, achieving higher data rates with reduced power consumption, while reducing EMI emissions and system susceptibility to noise.

The MAX9394/MAX9395 high-speed, low-power 2:1 multiplexers and 1:2 demultiplexers with loopback provide signal redundancy switching in telecom and storage applications. These devices select one of two remote signal sources for local input and buffer a single local output signal to two remote receivers.

The multiplexer section (channel B) accepts two differential inputs and generates a single LVDS output. The demultiplexer section (channel A) accepts a single differential input and generates two parallel LVDS outputs. The MAX9394/MAX9395 feature a loopback mode that connects the input of channel A to the output of channel B and connects the selected input of channel B to the outputs of channel A. LB\_SELA and LB\_SELB provide independent loopback control for each channel.

Three LVCMOS/LVTTL logic inputs control the internal connections between inputs and outputs, one for the multiplexer portion of channel B (BSEL), and the other two for loopback control of channels A and B (LB\_SELA and LB\_SELB). Independent enable inputs for each differential output pair provide additional flexibility.

#### Input Fail-Safe

The differential inputs of the MAX9394/MAX9395 possess internal fail-safe protection. Fail-safe circuitry forces the outputs to a differential-low condition for undriven inputs or when the common-mode voltage exceeds the specified range. The MAX9394 provides high-level input fail-safe detection for LVDS, HSTL, and other GND-referenced differential inputs. The MAX9395 provides low-level input fail-safe detection for LVPECL, CML, and other V<sub>CC</sub>-referenced differential inputs.

#### **Select Function**

BSEL selects the differential input pair to transmit through OUTB (OUTB) for LB\_SELB = GND or through OUTA\_ (OUTA\_) for LB\_SELA = V<sub>CC</sub>. LB\_SEL\_ controls the loopback function for each channel. Connect LB\_SEL\_ to GND to select the normal inputs for each channel. Connect LB\_SEL\_ to V<sub>CC</sub> to enable the loopback function. The loopback function routes the input of channel A to the output of channel B, and the inputs of channel B to the outputs of channel A. See Tables 1 and 2 for a summary of the input/output routing between channels.

#### **Enable Function**

The EN\_ \_ logic inputs enable and disable each set of differential outputs. Connect EN\_ 0 to  $V_{CC}$  to enable the OUT\_0/OUT\_0 differential output pair. Connect EN\_0 to GND to disable the OUT\_0/OUT\_0 differential output pair. The differential output pairs assert to a differential low condition when disabled.

#### Applications Information

#### **Differential Inputs**

The MAX9394/MAX9395 inputs accept any differential signaling standard within the specified common-mode voltage range. The fail-safe feature detects common-mode input signal levels and generates a differential output low condition for undriven inputs or when the common-mode voltage exceeds the specified range (V<sub>CM</sub>  $\geq$  V<sub>CC</sub> - 0.6V, MAX9394; V<sub>CM</sub>  $\leq$  0.6V, MAX9395). Leave unused inputs unconnected or connect to V<sub>CC</sub> for the MAX9394 or to GND for the MAX9395.

#### Table 1. Input Select Truth Table

|         | LOGIC INPUTS |      | DIFFERENTIA   | L OUTPUTS     |

|---------|--------------|------|---------------|---------------|

| LB_SELA | LB_SELB      | BSEL | OUTA_/OUTA_   | OUTB / OUTB   |

| 0       | 0            | 0    | INA selected  | INB0 selected |

| 0       | 0            | 1    | INA selected  | INB1 selected |

| 0       | 1            | Х    | INA selected  | INA selected  |

| 1       | 0            | 0    | INB0 selected | INB0 selected |

| 1       | 0            | 1    | INB1 selected | INB1 selected |

| 1       | 1            | 0    | INB0 selected | INA selected  |

| 1       | 1            | 1    | INB1 selected | INA selected  |

X = Don't care.

#### **Differential Outputs**

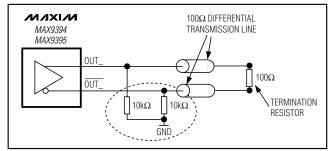

The output common-mode voltage is not properly established if the LVDS output is higher than 0.6V when the supply voltage is ramping up at power-on. This condition can occur when an LVDS output drives an LVDS input on the same chip. To avoid this situation for the MAX9394/MAX9395, connect a 10k $\Omega$  resistor from the noninverting output (OUT\_) to ground, and connect a 10k $\Omega$  resistor from the inverting output (OUT\_) to ground. These pulldown resistors keep the output below 0.6V when the supply is ramping up (Figure 7).

#### **Power-Supply Bypassing**

Bypass each V<sub>CC</sub> to GND with high-frequency surfacemount ceramic  $0.1\mu$ F and  $0.01\mu$ F capacitors in parallel as close to the device as possible. Install the  $0.01\mu$ F capacitor closest to the device.

#### **Differential Traces**

Input and output trace characteristics affect the performance of the MAX9394/MAX9395. Connect each input and output to a 50 $\Omega$  characteristic impedance trace. Maintain the distance between differential traces and eliminate sharp corners to avoid discontinuities in differential impedance and maximize common-mode noise immunity. Minimize the number of vias on the differential input and output traces to prevent impedance discontinuities. Reduce reflections by maintaining the 50 $\Omega$  characteristic impedance through connectors and across cables. Minimize skew by matching the electrical length of the traces.

#### **Output Termination**

Terminate LVDS outputs with a  $100\Omega$  resistor between the differential outputs at the receiver inputs. LVDS outputs require  $100\Omega$  termination for proper operation.

Ensure that the output currents do not exceed the current limits specified in the *Absolute Maximum Ratings*.

#### Table 2. Loopback Select Truth Table

| LB_SEL_     | OUT                       |

|-------------|---------------------------|

| GND or open | Normal inputs selected.   |

| Vcc         | Loopback inputs selected. |

Figure 7. Pulldown Resistor Configuration for LVDS Outputs

Observe the total thermal limits of the MAX9394/ MAX9395 under all operating conditions.

#### **Cables and Connectors**

Use matched differential impedance for transmission media. Use cables and connectors with matched differential impedance to minimize impedance discontinuities. Avoid the use of unbalanced cables.

Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to canceling effects.

#### **Board Layout**

Use a four-layer printed circuit (PC) board providing separate signal, power, and ground planes for high-speed signaling applications. Bypass V<sub>CC</sub> to GND as close to the device as possible. Install termination resistors as close to receiver inputs as possible. Match the electrical length of the differential traces to minimize signal skew.

### Functional Diagram

Chip Information

TRANSISTOR COUNT: 1565 PROCESS: BIPOLAR

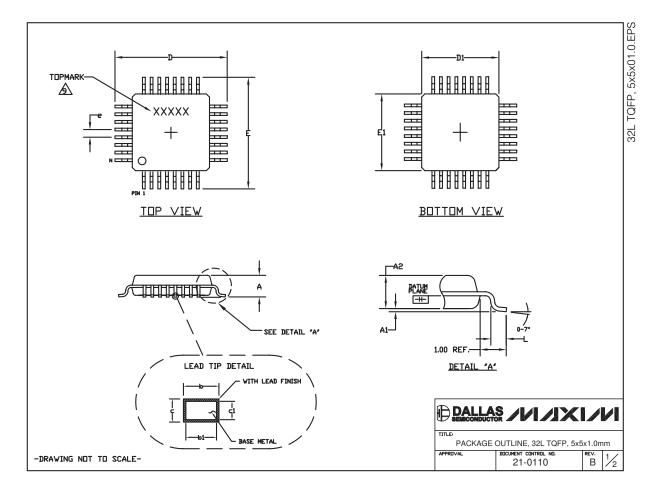

#### \_Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

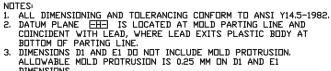

- DIMENSIONS. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE 4.

- THE TOP OF PACKAGE IS SMALLER THAN THE BUTTOM OF PACKAGE BY 0.15 MILLIMETERS.

DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE b DIMENSION AT MAXIMUM MATERIAL CONDITION.

ALL DIMENSIONS ARE IN MILLIMETERS.

THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION MS-026

- NS-026. LEADS SHALL BE COPLANAR WITHIN .004 INCH. TOPMARK SHOWN IS FOR PACKAGE DRIENTATION REFERENCE ONLY.

- 8.

|    |       | ARIATIONS<br>N MILLIMETERS |

|----|-------|----------------------------|

|    | AA    | ۱A                         |

|    | 5×5×1 | .0 MM                      |

|    | MIN.  | MAX.                       |

| A  | 74    | 1.20                       |

| A1 | 0.05  | 0.15                       |

| A2 | 0.95  | 1.05                       |

| D  | 6.80  | 7.20                       |

| D1 | 4.80  | 5.20                       |

| Ε  | 6.80  | 7.20                       |

| E1 | 4.80  | 5.20                       |

| L  | 0.45  | 0.75                       |

| z  | 3     | 2                          |

| e  | 0.50  | BSC.                       |

| b  | 0.17  | 0.27                       |

| o1 | 0.17  | 0.23                       |

| c  | 0.09  | 0.20                       |

| =1 | 0.09  | 0.16                       |

|        | \$ <i>/</i> 1//X       |        |    |

|--------|------------------------|--------|----|

| TITLE  |                        |        |    |

| (I)CE) |                        |        |    |

|        | OUTLINE, 32L TQFP, 5x5 | ix1.0m | nm |

-DRAWING NOT TO SCALE-

#### **Revision History**

All pages changed at Rev 1

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2007 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products, Inc.