# TMS320VC5441 Fixed-Point Digital Signal Processor

# Data Manual

Literature Number: SPRS122F December 1999 – Revised October 2008

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### **REVISION HISTORY**

This data sheet revision history highlights the technical changes made to the SPRS122E device-specific data sheet to make it an SPRS122F revision.

**Scope:** This document has been reviewed for technical accuracy; the technical content is up-to-date as of the specified release date with the following changes.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17             | Table 2–3, Signal Descriptions:  - Updated DESCRIPTION of TRST  - Added footnote about TRST                                                                                                                                                                      |

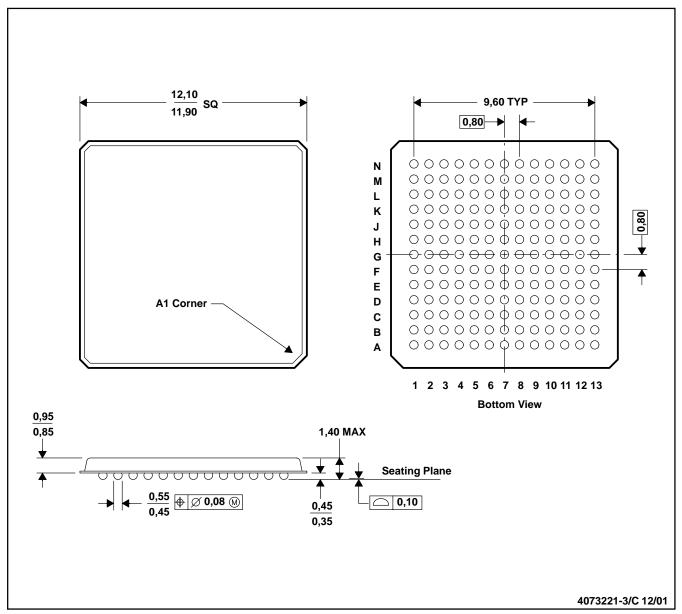

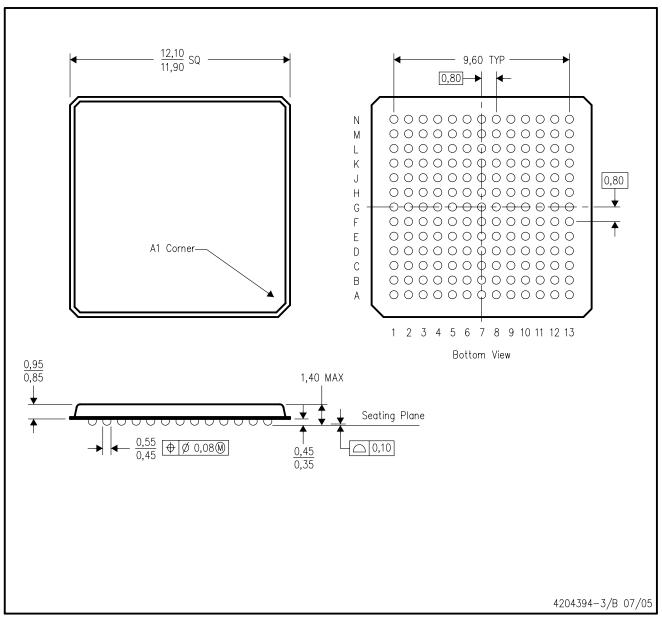

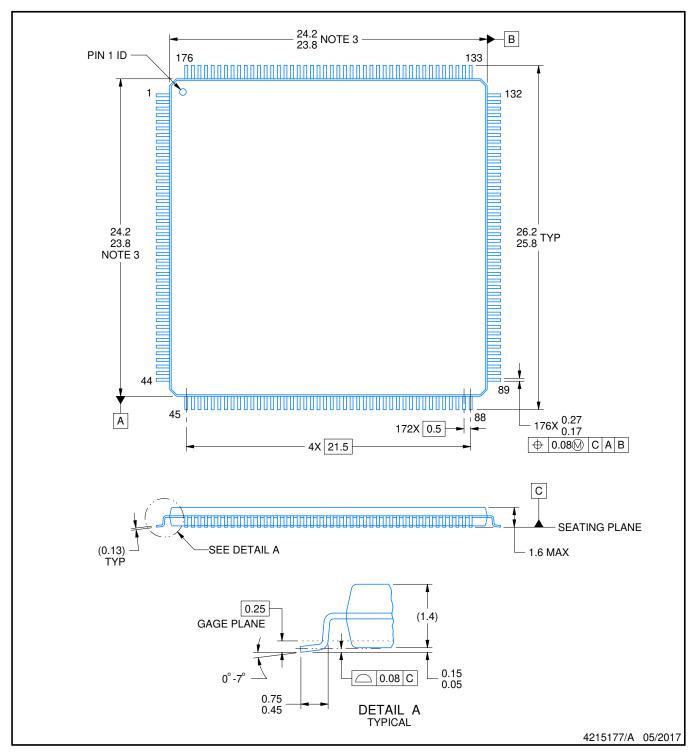

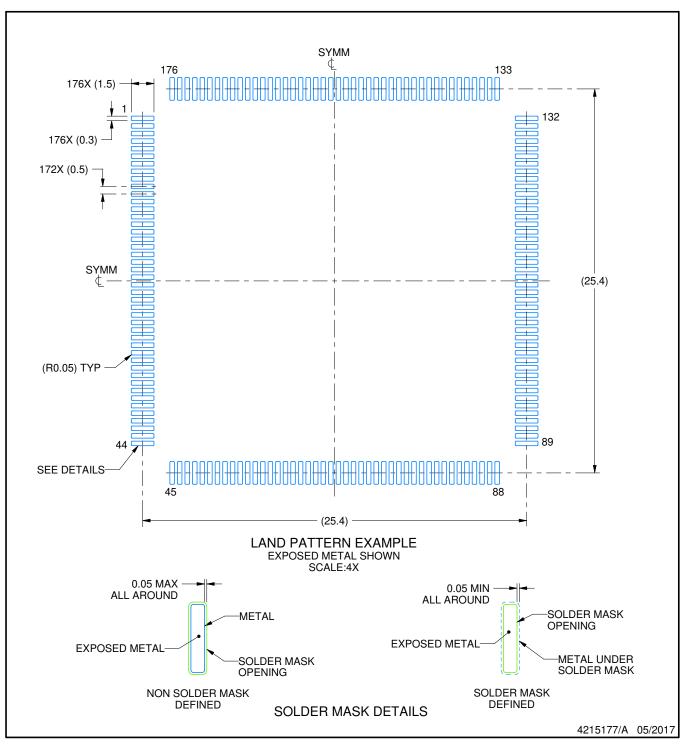

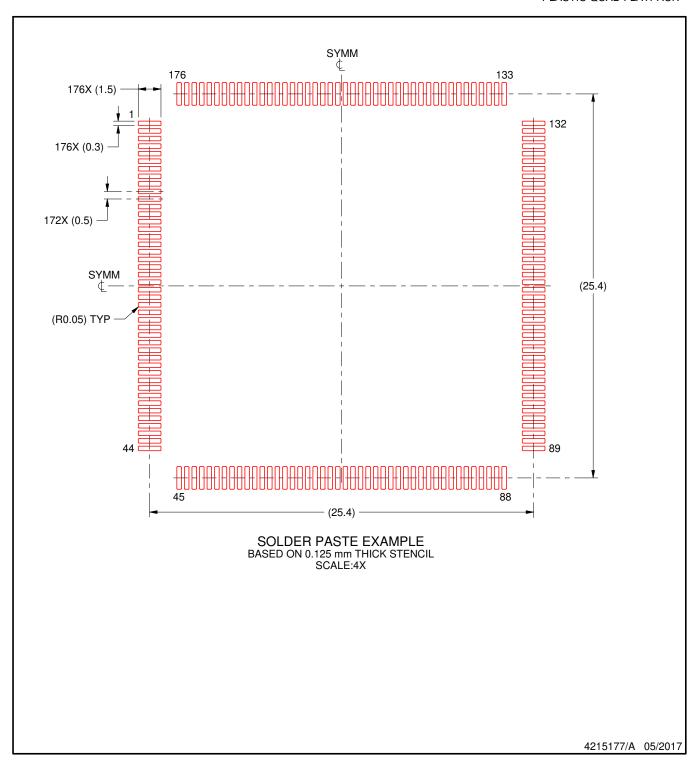

| 85             | Section 6, Mechanical Data:  - Moved "Package Thermal Resistance Characteristics" section (Section 5.4 in SPRS122E) to Section 6.1  - Added Section 6.2, Packaging Information  - Mechanical drawings will be appended to this document via an automated process |

## **Contents**

| Se | ction   |                       |                                                                   | Page |  |  |  |  |  |  |

|----|---------|-----------------------|-------------------------------------------------------------------|------|--|--|--|--|--|--|

| 1  | TMS32   | TMS320VC5441 Features |                                                                   |      |  |  |  |  |  |  |

| 2  | Introdu | ıction                |                                                                   | 12   |  |  |  |  |  |  |

|    | 2.1     |                       | on                                                                | 12   |  |  |  |  |  |  |

|    | 2.2     |                       | From the 5421 to the 5441                                         | 13   |  |  |  |  |  |  |

|    | 2.3     |                       | gnments                                                           | 13   |  |  |  |  |  |  |

|    |         | 2.3.1                 | Pin Assignments for the GGU Package                               | 13   |  |  |  |  |  |  |

|    |         | 2.3.2                 | Pin Assignments for the PGF Package                               | 15   |  |  |  |  |  |  |

|    | 2.4     | _                     | escriptions                                                       | 17   |  |  |  |  |  |  |

|    |         |                       |                                                                   |      |  |  |  |  |  |  |

| 3  |         |                       | view                                                              | 23   |  |  |  |  |  |  |

|    | 3.1     | •                     |                                                                   | 24   |  |  |  |  |  |  |

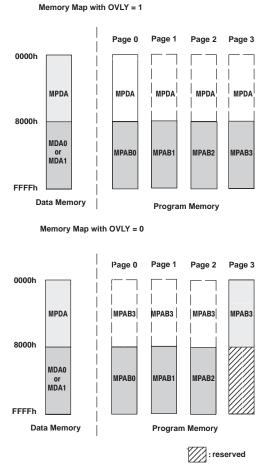

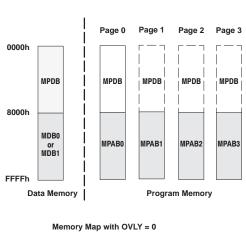

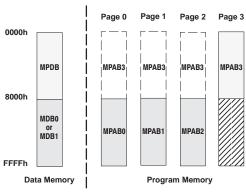

|    |         | 3.1.1                 | Memory Maps                                                       | 24   |  |  |  |  |  |  |

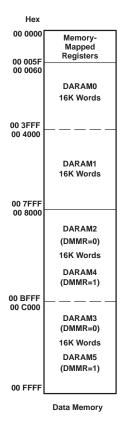

|    |         | 3.1.2                 | On-Chip Dual-Access RAM (DARAM)                                   | 28   |  |  |  |  |  |  |

|    |         | 3.1.3                 | On-Chip Two-Way Shared RAM                                        | 28   |  |  |  |  |  |  |

|    |         | 3.1.4                 | Extended Data Memory                                              | 29   |  |  |  |  |  |  |

|    |         | 3.1.5                 | Extended Program Memory                                           | 29   |  |  |  |  |  |  |

|    |         | 3.1.6                 | Program Memory                                                    | 29   |  |  |  |  |  |  |

|    |         | 3.1.7                 | Data Memory                                                       | 29   |  |  |  |  |  |  |

|    |         | 3.1.8                 | I/O Memory                                                        | 29   |  |  |  |  |  |  |

|    |         | 3.1.9                 | Multicore Reset Signals                                           | 30   |  |  |  |  |  |  |

|    |         | 3.1.10                | Device Bootload                                                   | 30   |  |  |  |  |  |  |

|    | 3.2     | On-Chip               | Peripherals                                                       | 30   |  |  |  |  |  |  |

|    |         | 3.2.1                 | Direct Memory Access (DMA) Controller                             | 30   |  |  |  |  |  |  |

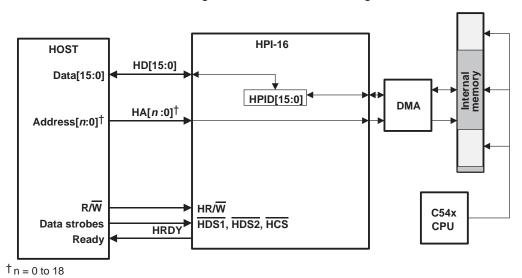

|    |         | 3.2.2                 | 16-Bit Bidirectional Host-Port Interface (HPI16)                  | 34   |  |  |  |  |  |  |

|    |         | 3.2.3                 | Multichannel Buffered Serial Port (McBSP)                         | 39   |  |  |  |  |  |  |

|    |         | 3.2.4                 | Hardware Timer                                                    | 43   |  |  |  |  |  |  |

|    |         | 3.2.5                 | Watchdog Timer                                                    | 45   |  |  |  |  |  |  |

|    |         | 3.2.6                 | Software-Programmable Phase-Locked Loop (PLL)                     | 50   |  |  |  |  |  |  |

|    |         | 3.2.7                 | General-Purpose I/O                                               | 52   |  |  |  |  |  |  |

|    |         | 3.2.8                 | Chip Subsystem ID Register                                        | 54   |  |  |  |  |  |  |

|    |         | 3.2.9                 | Data Memory Map Register                                          | 54   |  |  |  |  |  |  |

|    | 3.3     |                       | Mapped Registers                                                  | 55   |  |  |  |  |  |  |

|    | 3.4     |                       | Control Registers and Subaddresses                                | 57   |  |  |  |  |  |  |

|    | 3.5     |                       | bbank Addressed Registers                                         | 58   |  |  |  |  |  |  |

|    | 3.6     |                       | S                                                                 | 60   |  |  |  |  |  |  |

|    | 3.7     |                       | ower-Down Mode                                                    | 62   |  |  |  |  |  |  |

|    | 3.8     |                       | g the 5441 Device                                                 | 62   |  |  |  |  |  |  |

|    |         | ·                     | -                                                                 |      |  |  |  |  |  |  |

| 4  | Docum   | entation              | Support                                                           | 63   |  |  |  |  |  |  |

| 5  | Electri | cal Specif            | fications                                                         | 64   |  |  |  |  |  |  |

|    | 5.1     | Absolute              | Maximum Ratings                                                   | 64   |  |  |  |  |  |  |

|    | 5.2     |                       | ended Operating Conditions                                        | 64   |  |  |  |  |  |  |

|    | 5.3     | Electrical            | Characteristics Over Recommended Operating Case Temperature Range | 0.5  |  |  |  |  |  |  |

|    |         | (unless (             | Otherwise Noted)                                                  | 65   |  |  |  |  |  |  |

#### Contents

| Secti | on     |            |                                                                          | Page |

|-------|--------|------------|--------------------------------------------------------------------------|------|

| 5     | 5.4    | Timing F   | Parameter Symbology                                                      | 66   |

| 5     | 5.5    | Clock O    | otions                                                                   | 67   |

|       |        | 5.5.1      | Divide-By-Two, Divide-By-Four, and Bypass Clock Options - PLL Disabled   | 67   |

|       |        | 5.5.2      | Multiply-By-N Clock Option – PLL Enabled                                 | 68   |

| 5     | 5.6    | Reset, x   | BIO, and Interrupt Timings                                               | 69   |

| 5     | 5.7    |            | Flag (x_XF), Timer (x_TOUT), and Watchdog Timer Output (x_WTOUT) Timings | 71   |

| 5     | 5.8    | General-   | Purpose Input/Output (GPIO) Timing                                       | 72   |

| 5     | .9     |            | nnel Buffered Serial Port Timing                                         | 73   |

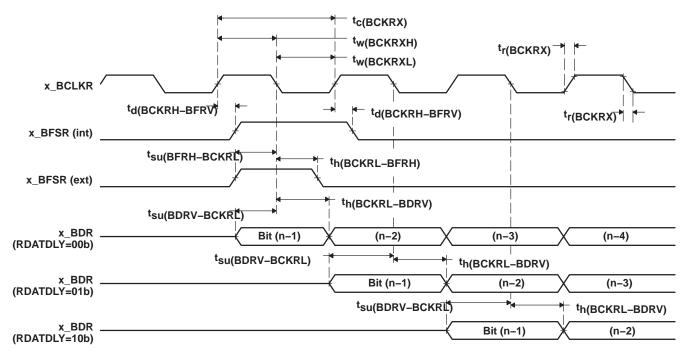

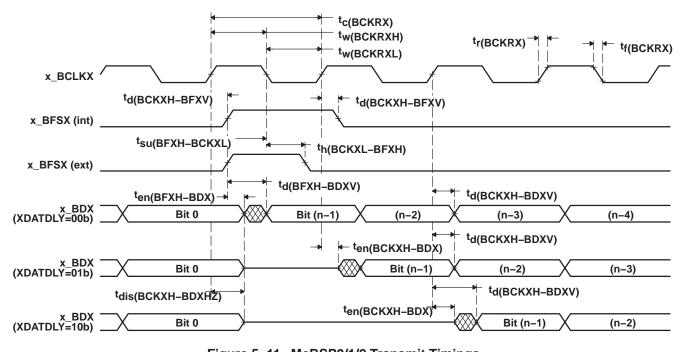

|       |        | 5.9.1      | McBSP0/1/2 Transmit and Receive Timings                                  | 73   |

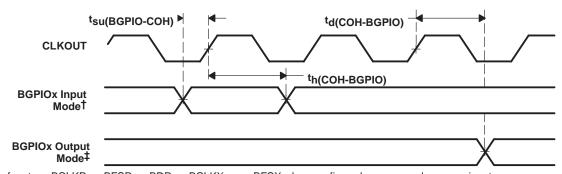

|       |        | 5.9.2      | McBSP0 General-Purpose I/O Timing                                        | 76   |

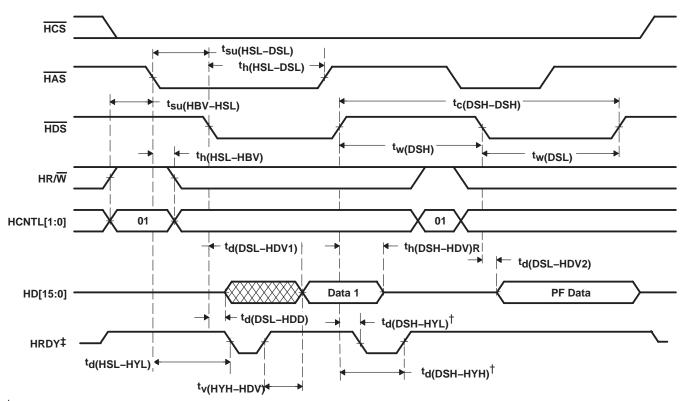

| 5     | 5.10   | Host-Po    | rt Interface (HPI16) Timing                                              | 77   |

| 6 N   | /lecha | ınical Dat | a                                                                        | 85   |

|       | 5.1    |            | Thermal Resistance Characteristics                                       | 85   |

| 6     | 2      | Ū          | ng Information                                                           | 85   |

# **List of Figures**

| Figure |                                                                                    | Pa |

|--------|------------------------------------------------------------------------------------|----|

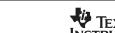

| 2–1    | 169-Ball GGU MicroStar BGA (Bottom View)                                           |    |

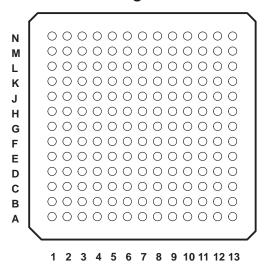

| 2–2    | 176-Pin PGF Low-Profile Quad Flatpack (Top View)                                   | •  |

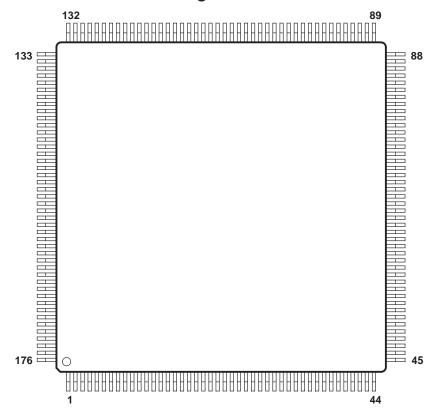

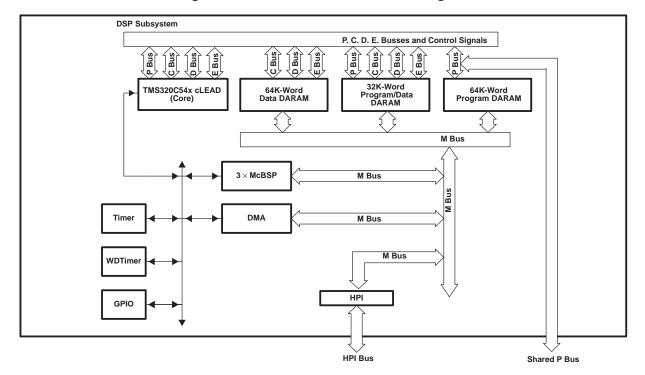

| 3–1    | Overall Functional Block Diagram                                                   | 4  |

| 3–2    | Typical Subsystem Functional Block Diagram                                         | 2  |

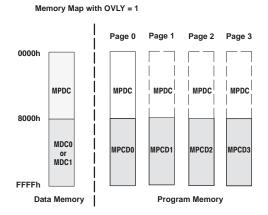

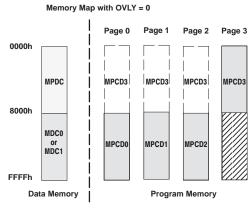

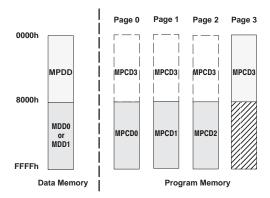

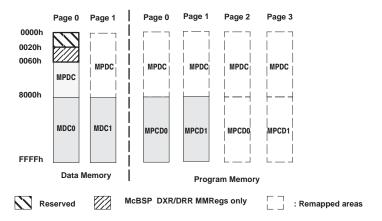

| 3–3    | Subsystem A CPU Memory Map                                                         | 2  |

| 3–4    | Subsystem B CPU Memory Map                                                         | 2  |

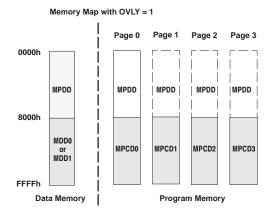

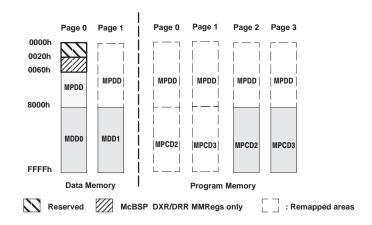

| 3–5    | Subsystem C CPU Memory Map                                                         | :  |

| 3–6    | Subsystem D CPU Memory Map                                                         |    |

| 3–7    | Detailed Memory Map of Local Data Memory Relative to CPU Subsystems A, B, C, and D |    |

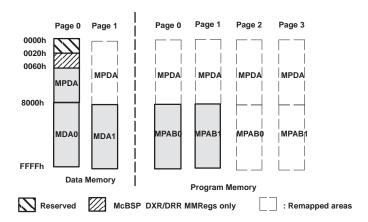

| 3–8    | Subsystem A Local DMA Memory Map                                                   | ;  |

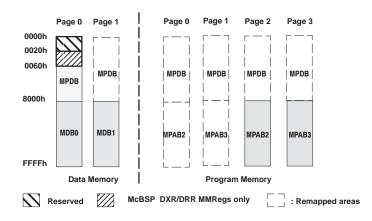

| 3–9    | Subsystem B Local DMA Memory Map                                                   |    |

| 3–10   | Subsystem C Local DMA Memory Map                                                   |    |

| 3–11   | Subsystem D Local DMA Memory Map                                                   |    |

| 3–12   | Interfacing to the HPI-16 in Non-Multiplexed Mode                                  |    |

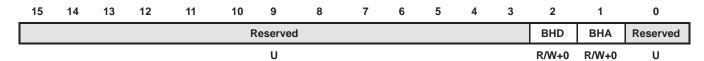

| 3–13   | BSCR Register Bit Layout for Subsystem A                                           |    |

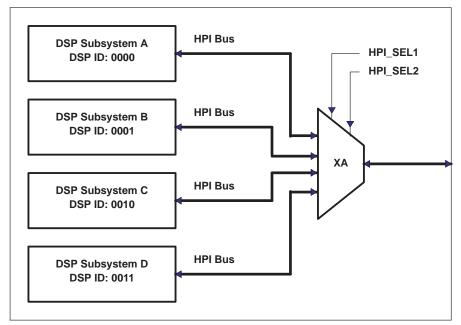

| 3–14   | XA Multiplexer for HPI Access                                                      |    |

| 3–15   | Pin Control Register (PCR)                                                         |    |

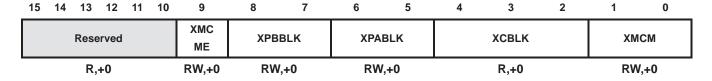

| 3–16   | Multichannel Control Register 2 for McBSPx (MCR2x)                                 |    |

| 3–17   | Multichannel Control Register 1 for McBSPx (MCR1x)                                 |    |

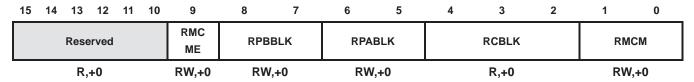

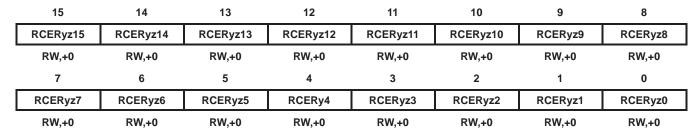

| 3–18   | Receive Channel Enable Registers Bit Layout for Partitions A to H                  |    |

| 3–19   | Transmit Channel Enable Registers Bit Layout for Partitions A to H                 |    |

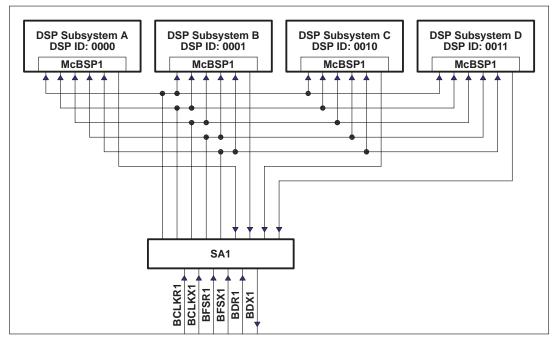

| 3–20   | SA Multiplexer for McBSP1 Operation                                                |    |

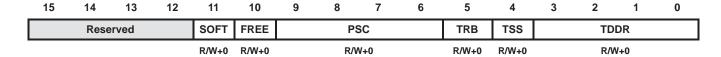

| 3–21   | Timer Control Register (TCR)                                                       |    |

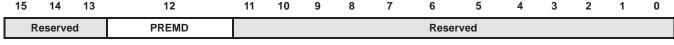

| 3–22   | Timer Second Control Register (TSCR)                                               |    |

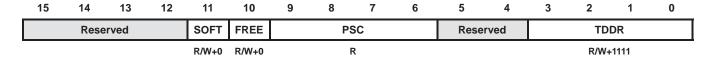

| 3–23   | Watchdog Timer Control Register (WDTCR)                                            |    |

| 3–24   | Watchdog Timer Second Control Register (WDTSCR)                                    |    |

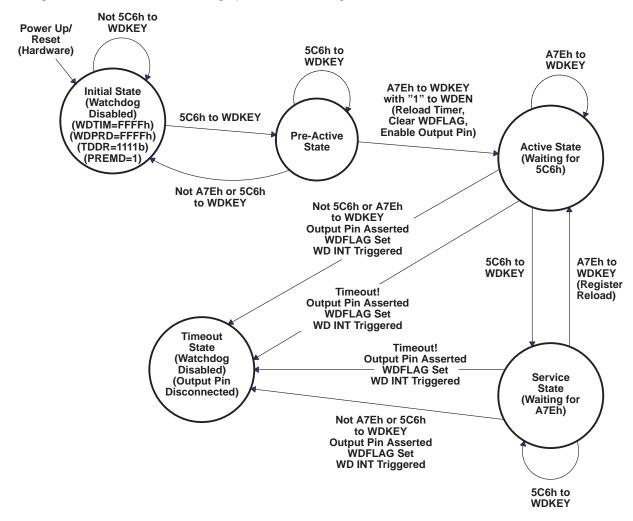

| 3–25   | Watchdog Operation State Diagram                                                   |    |

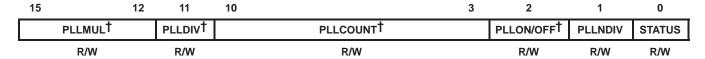

| 3–26   | Clock Mode Register (CLKMD)                                                        |    |

| 3–27   | General-Purpose I/O Control Register                                               |    |

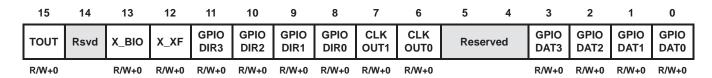

| 3–28   | Chip Subsystem ID Register (CSIDR)                                                 |    |

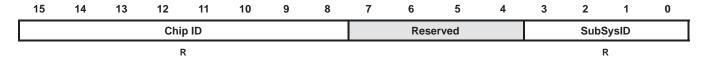

| 3–29   | Data Memory Map Register (DMMR)                                                    |    |

| 3–30   | Bit Layout of the IMR and IFR Registers for Each Subsystem                         |    |

| 5–1    | 3.3-V Test Load Circuit                                                            |    |

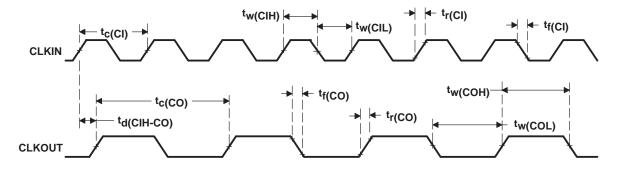

| 5–2    | External Divide-by-Two Clock Timing                                                |    |

| 5–3    | External Multiply-by-One Clock Timing                                              |    |

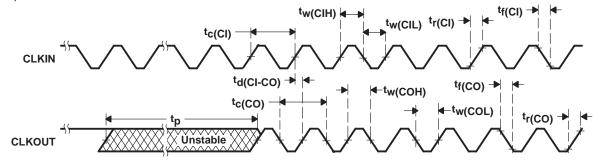

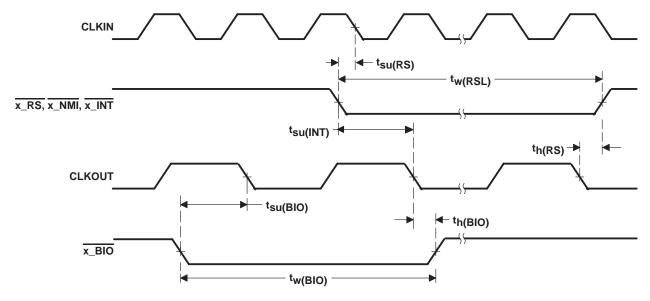

| 5–4    | Reset and x_BIO Timings                                                            |    |

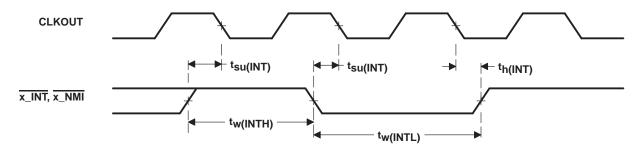

| 5–5    | Interrupt Timing                                                                   |    |

| •      |                                                                                    |    |

#### Figures

| Figure |                                              | Page |

|--------|----------------------------------------------|------|

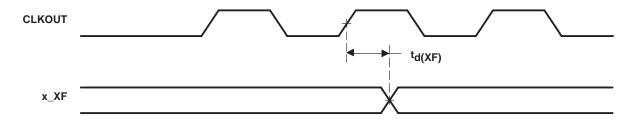

| 5–6    | External Flag (x_XF) Timing                  | 71   |

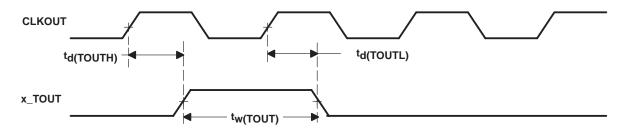

| 5–7    | Timer (x_TOUT) Timing                        | 71   |

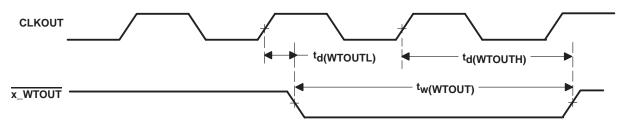

| 5–8    | Watchdog Timer (x_WTOUT) Timing              | 71   |

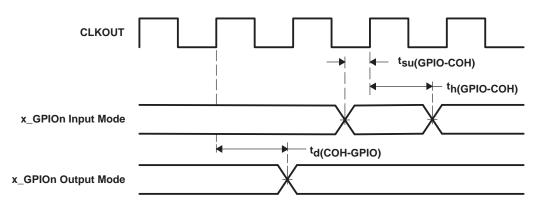

| 5–9    | GPIO Timings                                 | 72   |

| 5–10   | McBSP0/1/2 Receive Timings                   | 75   |

| 5–11   | McBSP0/1/2 Transmit Timings                  | 75   |

| 5–12   | McBSP0 General-Purpose I/O Timings           | 76   |

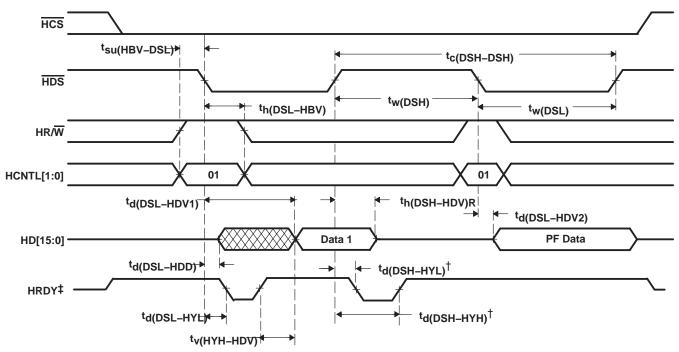

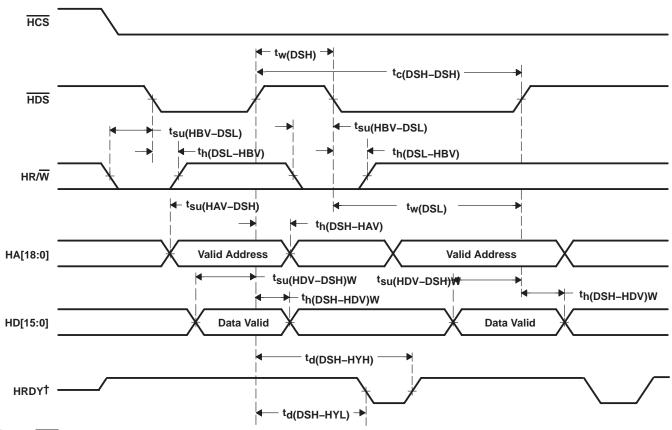

| 5–13   | Multiplexed Read Timings Using HAS           | 79   |

| 5–14   | Multiplexed Read Timings With HAS Held High  | 80   |

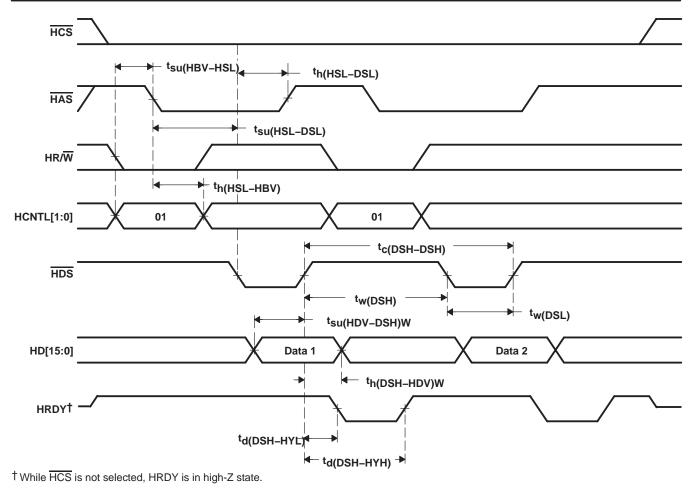

| 5–15   | Multiplexed Write Timings Using HAS          | 81   |

| 5–16   | Multiplexed Write Timings With HAS Held High | 82   |

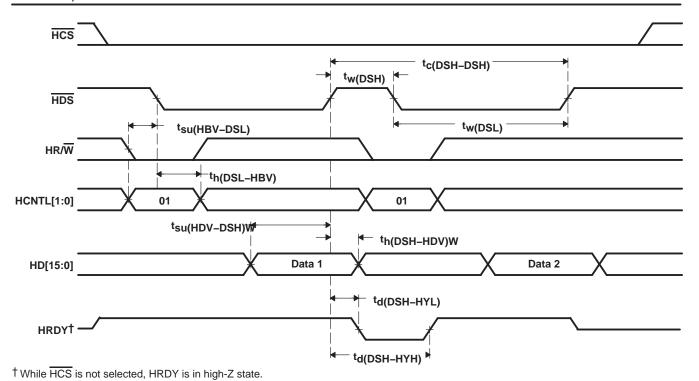

| 5–17   | Nonmultiplexed Read Timings                  | 83   |

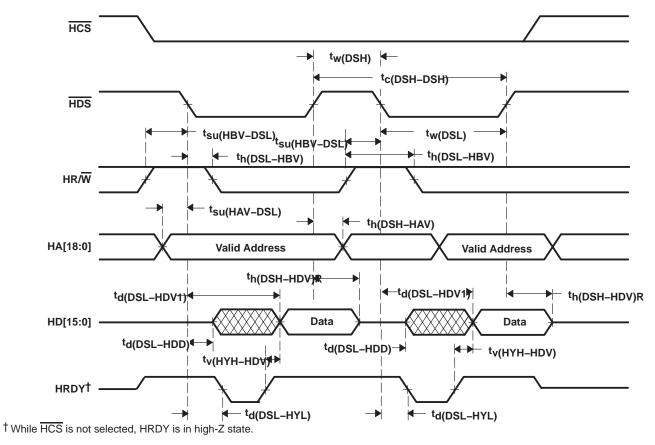

| 5–18   | Nonmultiplexed Write Timings                 | 84   |

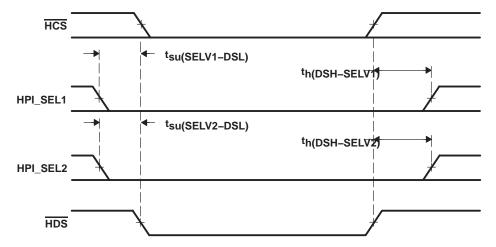

| 5-19   | HPL SEL1 and HPL SEL2 Timing                 | 84   |

# **List of Tables**

| Table |                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------|

| 2–1   | Pin Assignments for TMS320VC5441GGU (169-Ball BGA Package)                                          |

| 2-2   | Pin Assignments for TMS320VC5441PGF (176-Pin LQFP Package)                                          |

| 2–3   | Signal Descriptions                                                                                 |

| 3–1   | DMA Synchronization Events                                                                          |

| 3–2   | DMA Channel Interrupt Selection                                                                     |

| 3–3   | HPI Local/Shared Memory Selection Via HA[20]                                                        |

| 3-4   | HPI Local/Shared Memory Selection Via HA[18]                                                        |

| 3–5   | BSCR Register Bit Functions for Subsystem A                                                         |

| 3–6   | HPI Module Selection                                                                                |

| 3–7   | Sample Rate Generator Clock Source Selection                                                        |

| 3–8   | Receive Channel Enable Registers for Partitions A to H                                              |

| 3–9   | Transmit Channel Enable Registers for Partitions A to H                                             |

| 3–10  | TCR Bit Description                                                                                 |

| 3–11  | TSCR Bit Description                                                                                |

| 3–12  | WDTCR Bit Description                                                                               |

| 3–13  | WDTSCR Bit Description                                                                              |

| 3–14  | Clock Mode Register (CLKMD) Bit Functions                                                           |

| 3–15  | Multiplier Related to PLLNDIV, PLLDIV, and PLLMUL                                                   |

| 3–16  | VCO Truth Table                                                                                     |

| 3–17  | VCO Lockup Time                                                                                     |

| 3–18  | PLL Initialization at Reset                                                                         |

| 3–19  | General-Purpose I/O Control Register Bit Functions                                                  |

| 3–20  | Chip Subsystem ID Register Bit Functions                                                            |

| 3–21  | Data Memory Map Register Functions                                                                  |

| 3–22  | Processor Memory-Mapped Registers for Each DSP Subsystem                                            |

| 3–23  | Peripheral Memory-Mapped Registers for Each DSP Subsystem                                           |

| 3-24  | McBSP Control Registers and Subaddresses                                                            |

| 3-25  | DMA Subbank Addressed Registers                                                                     |

| 3–26  | 5441 Interrupt Locations and Priorities for Each DSP Subsystem                                      |

| 3–27  | Bit Functions for IMR and IFR Registers for Each DSP Subsystem                                      |

| 5–1   | Divide-By-Two, Divide-By-Four, and Bypass Clock Options Timing Requirements                         |

| 5–2   | Divide-By-Two, Divide-By-Four, and Bypass Clock Options Switching Characteristics                   |

| 5–3   | Multiply-By-N Clock Option Timing Requirements                                                      |

| 5–4   | Multiply-By-N Clock Option Switching Characteristics                                                |

| 5–5   | Reset, x_BIO, and Interrupt Timing Requirements                                                     |

| 5–6   | External Flag (x_XF), Timer (x_TOUT), and Watchdog Timer Output (x_WTOUT) Switching Characteristics |

| 5–7   | GPIO Timing Requirements                                                                            |

| 5–8   | GPIO Switching Characteristics                                                                      |

| 5–9   | McBSP0/1/2 Transmit and Receive Timing Requirements                                                 |

| 5–10  | McBSP0/1/2 Transmit and Receive Switching Characteristics                                           |

| 5–11  | McBSP0 General-Purpose I/O Timing Requirements                                                      |

| 5–12  | McBSP0 General-Purpose I/O Switching Characteristics                                                |

|       | -                                                                                                   |

#### Tables

| Table |                                    | Page |

|-------|------------------------------------|------|

|       | HPI16 Timing Requirements          |      |

| 6–1   | Thermal Resistance Characteristics | 85   |

#### 1 TMS320VC5441 Features

- 532-MIPS Quad-Core DSP Consisting of Four Independent Subsystems

- Each Core has an Advanced Multibus Architecture With Three Separate 16-Bit Data Memory Buses and One Program Bus

- 40-Bit Arithmetic Logic Unit (ALU)

Including a 40-Bit Barrel-Shifter and Two

40-Bit Accumulators Per Core

- Each Core has a 17-Bit × 17-Bit Parallel Multiplier Coupled to a 40-Bit Adder for Non-Pipelined Single-Cycle Multiply/ Accumulate (MAC) Operations

- Each Core has a Compare, Select, and Store Unit (CSSU) for the Add/Compare Selection of the Viterbi Operator

- Each Core has an Exponent Encoder to Compute an Exponent Value of a 40-Bit Accumulator Value in a Single Cycle

- Each Core has Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Total 640K-Word x 16-Bit Dual-Access On-Chip RAM (256K-Word x 16-Bit Shared Memory and 96K-Word x 16-Bit Local Memory Per Subsystem)

- Single-Instruction Repeat and Block-Repeat Operations

- Instructions With 32-Bit Long Word Operands

- Instructions With 2 or 3 Operand Reads

- Fast Return From Interrupts

- Arithmetic Instructions With Parallel Store and Parallel Load

- Conditional Store Instructions

- Output Control of CLKOUT

- Output Control of Timer Output (TOUT)

- Power Consumption Control With IDLE1, IDLE2, and IDLE3 Instructions

- Dual 1.6-V (Core) and 3.3-V (I/O) Power Supplies for Low-Power, Fast Operations

- 7.5-ns Single-Cycle Fixed-Point Instruction

- Twenty-Four Channels of Direct Memory Access (DMA) for Data Transfers With No CPU Loading (Six Channels Per Subsystem)

- Twelve Multichannel Buffered Serial Ports (McBSPs), Each With 128-Channel Selection Capability (Three McBSPs per Subsystem)

- 16-Bit Host-Port Interface (HPI)

- Software-Programmable Phase-Locked Loop (PLL) Provides Several Clocking Options (Requires External TTL Oscillator)

- On-Chip Scan-Based Emulation Logic, IEEE Standard 1149.1<sup>†</sup> (JTAG) Boundary-Scan Logic

- Four Software-Programmable Timers (One Per Subsystem)

- Four Software-Programmable Watchdog Timers (One Per Subsystem)

- Sixteen General-Purpose I/Os (Four Per Subsystem)

- Provided in 176-pin Plastic Low-Profile Quad Flatpack (LQFP) Package (PGF Suffix)

- Provided in 169-ball MicroStar BGA™ Package (GGU Suffix)

MicroStar BGA is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

† IEEE Standard 1149.1-1990, Standard Test-Access Port and Boundary Scan Architecture.

#### 2 Introduction

This section describes the main features of the TMS320VC5441 digital signal processor (DSP), lists the pin assignments, and describes the function of each pin. This data manual also provides a detailed description section, electrical specifications, parameter measurement information, and mechanical data about the available packaging.

**NOTE:** This data manual is designed to be used in conjunction with the *TMS320C54x* ™ *DSP Functional Overview* (literature number SPRU307).

#### 2.1 Description

The TMS320VC5441 fixed-point digital signal processor is a quad-core solution running at 532-MIPS performance. The 5441 consists of four DSP subsystems with shared program memory. Each subsystem consists of one TMS320C54x™ DSP core, 32K-word program/data DARAM, 64K-word data DARAM, three multichannel buffered serial ports, DMA logic, one watchdog timer, one general-purpose timer, and other miscellaneous circuitry.

The 5441 also contains a host-port interface (HPI) that allows the 5441 to be viewed as a memory-mapped peripheral to a host processor.

Each subsystem has its separate program and data spaces, allowing simultaneous accesses to program instructions and data. Two read operations and one write operation can be performed in one cycle. Instructions with parallel store and application-specific instructions can fully utilize this architecture. Furthermore, data can be transferred between program and data spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. The 5441 includes the control mechanisms to manage interrupts, repeated operations, and function calls. In addition, the 5441 has a total of 256K words of shared program memory (128K words shared by subsystems A and B, and another 128K words shared by subsystems C and D).

The 5441 is intended as a high-performance, low-cost, high-density DSP for remote data access or voice-over IP subsystems. It is designed to maintain the current modem architecture with minimal hardware and software impacts, thus maximizing reuse of existing modem technologies and development efforts.

The 5441 is offered in two temperature ranges and individual part numbers are shown below. (Please note that the industrial temperature device part numbers do not follow the typical numbering tradition.)

Commercial temperature devices (0°C to 85°C)

TMS320VC5441PGF532 (176-pin LQFP)

TMS320VC5441GGU532 (169-ball BGA)

Industrial temperature range devices (-40°C to 100°C)

TMS320VC5441APGF532 (176-pin LQFP)

TMS320VC5441AGGU532 (169-ball BGA)

**NOTE:** Leading "x" in signal names identifies the subsystem; x = A, B, C, or D for subsystem A, B, C, or D, respectively. Trailing "n" in signal names identifies the McBSP; n = 0, 1, or 2 for McBSP0, McBSP1, or McBSP2, respectively.

#### 2.2 Migration From the 5421 to the 5441

Customers who are migrating from the 5421 to the 5441 need to take into account the following differences between the two devices.

- The 5441 provides four cores in a 169-ball ball grid array (BGA) and a 176-pin low-profile quad flatpack (LQFP).

- The 5441 does not have a XIO interface for external memory connection.

- Each subsystem includes a 32K-word DARAM program/data memory and a 64K-word DARAM data memory.

- The DMA has been changed and now provides no access to external memory.

- The HPI and DMA memory maps have been changed to incorporate the new 5441 memory structure.

- The 2K words of ROM on the 5421 is not implemented on the 5441.

- The four McBSP1s and four McBSP2s have been internally multiplexed onto two sets of external pins.

- The HPI\_SEL1 and HPI\_SEL2 pins on 5441 are used to facilitate HPI module selection among the four subsystems.

- The 5441 provides four watchdog timers (one per subsystem).

- GPIO0 and GPIO1 pins are multiplexed with x XF and x BIO pins, respectively.

- Only the global reset (RESET) will reset the PLL.

#### 2.3 Pin Assignments

Figure 2–1 illustrates the ball locations for the 169-ball ball grid array (BGA) package and is used in conjunction with Table 2–1 to locate signal names and ball grid numbers. Figure 2–2 illustrates the pin locations for the 176-pin low-profile quad flatpack (LQFP); Table 2–2 lists each pin number and its associated pin name for this package.

#### 2.3.1 Pin Assignments for the GGU Package

Figure 2–1. 169-Ball GGU MicroStar BGA™ (Bottom View)

Table 2–1. Pin Assignments for TMS320VC5441GGU (169-Ball BGA Package)<sup>†</sup>

| BALL# | SIGNAL NAME      |

|-------|------------------|-------|------------------|-------|------------------|-------|------------------|

| A1    | HA[0]/HCNTL0     | A2    | DV <sub>DD</sub> | A3    | V <sub>SS</sub>  | A4    | B_BDR0           |

| A5    | CV <sub>DD</sub> | A6    | V <sub>SS</sub>  | A7    | $DV_DD$          | A8    | V <sub>SS</sub>  |

| A9    | CV <sub>DD</sub> | A10   | D_BDR0           | A11   | Vss              | A12   | DV <sub>DD</sub> |

| A13   | D_BFSX0          | B1    | HA[1]/HCNTL1     | B2    | B_BFSX0          | В3    | B_BFSR0          |

| B4    | B_BDX0           | B5    | CV <sub>DD</sub> | B6    | HD[7]            | В7    | HD[3]            |

| B8    | HD[0]            | В9    | CV <sub>DD</sub> | B10   | D_GPIO0/D_XF     | B11   | D_BDX0           |

| B12   | D_BFSR0          | B13   | HA[18]           | C1    | Vss              | C2    | HA[3]/B_HINT     |

| C3    | B_GPIO1/B_BIO    | C4    | B_GPIO0/B_XF     | C5    | CV <sub>DD</sub> | C6    | B_BCLKR0         |

| C7    | HD[4]            | C8    | D_GPIO3/D_TOUT   | C9    | CV <sub>DD</sub> | C10   | D_BCLKX0         |

| C11   | HA[17]           | C12   | HA[15]           | C13   | V <sub>SS</sub>  | D1    | CLKMD            |

| D2    | B_NMI            | D3    | B_RS             | D4    | HA[4]/C_HINT     | D5    | CV <sub>DD</sub> |

| D6    | B_BCLKX0         | D7    | HD[5]            | D8    | D_GPIO1/D_BIO    | D9    | CV <sub>DD</sub> |

| D10   | D_BCLKR0         | D11   | D_RS             | D12   | D_INT            | D13   | TRST             |

| E1    | $DV_DD$          | E2    | TESTB            | E3    | TDI              | E4    | B_INT            |

| E5    | HA[2]/A_HINT     | E6    | B_GPIO3/B_TOUT   | E7    | HD[6]            | E8    | HD[1]            |

| E9    | D_GPIO2/D_WTOUT  | E10   | TESTD            | E11   | TMS              | E12   | TCK              |

| E13   | $DV_DD$          | F1    | VSSA             | F2    | Vss              | F3    | HCS              |

| F4    | HAS              | F5    | CLKIN            | F6    | B_GPIO2/B_WTOUT  | F7    | HD[2]            |

| F8    | HA[16]           | F9    | D_NMI            | F10   | EMU1/OFF         | F11   | HPI_SEL2         |

| F12   | HPI_SEL1         | F13   | V <sub>SS</sub>  | G1    | VCCA             | G2    | CV <sub>DD</sub> |

| G3    | EMU0             | G4    | BCLKR2           | G5    | BCLKX2           | G6    | HRDY             |

| G7    | BDR1             | G8    | HMODE            | G9    | HDS2             | G10   | C_NMI            |

| G11   | RESET            | G12   | HR/W             | G13   | CV <sub>DD</sub> | H1    | V <sub>SS</sub>  |

| H2    | BFSR2            | H3    | BFSX2            | H4    | CLKOUT           | H5    | A_INT            |

| H6    | HA[7]            | H7    | HD[9]            | H8    | C_GPIO1/C_BIO    | H9    | BCLKX1           |

| H10   | BCLKR1           | H11   | BFSR1            | H12   | BFSX1            | H13   | $V_{SS}$         |

| J1    | $DV_DD$          | J2    | BDR2             | J3    | BDX2             | J4    | A_RS             |

| J5    | A_GPIO1/A_BIO    | J6    | HD[8]            | J7    | HD[13]           | J8    | C_BCLKR0         |

| J9    | HA[11]           | J10   | C_INT            | J11   | C_RS             | J12   | BDX1             |

| J13   | DV <sub>DD</sub> | K1    | V <sub>SS</sub>  | K2    | A_NMI            | K3    | TDO              |

| K4    | A_GPIO3/A_TOUT   | K5    | CV <sub>DD</sub> | K6    | A_GPIO2/A_WTOUT  | K7    | HD[12]           |

| K8    | C_BCLKX0         | K9    | CV <sub>DD</sub> | K10   | HA[13]           | K11   | HA[14]           |

| K12   | TESTC            | K13   | HDS1             | L1    | HA[5]/D_HINT     | L2    | HA[6]            |

| L3    | HA[8]            | L4    | A_GPIO0/A_XF     | L5    | CV <sub>DD</sub> | L6    | A_BCLKR0         |

| L7    | HD[11]           | L8    | HD[15]           | L9    | CV <sub>DD</sub> | L10   | C_GPIO0/C_XF     |

| L11   | C_GPIO2/C_WTOUT  | L12   | HA[12]           | L13   | V <sub>SS</sub>  | M1    | V <sub>SS</sub>  |

| M2    | HA[9]            | М3    | A_BFSR0          | M4    | A_BDR0           | M5    | CV <sub>DD</sub> |

| M6    | A_BCLKX0         | M7    | HD[10]           | M8    | HD[14]           | M9    | CV <sub>DD</sub> |

| M10   | C_GPIO3/C_TOUT   | M11   | C_BDX0           | M12   | C_BFSR0          | M13   | HA[10]           |

| N1    | A_BFSX0          | N2    | DV <sub>DD</sub> | N3    | V <sub>SS</sub>  | N4    | A_BDX0           |

| N5    | CV <sub>DD</sub> | N6    | V <sub>SS</sub>  | N7    | DV <sub>DD</sub> | N8    | V <sub>SS</sub>  |

| N9    | CV <sub>DD</sub> | N10   | C_BDR0           | N11   | V <sub>SS</sub>  | N12   | DV <sub>DD</sub> |

| N13   | C_BFSX0          |       |                  |       |                  |       |                  |

$<sup>\</sup>ensuremath{^{\dagger}}$  Cells highlighted in gray indicate pins that perform a multiplexed function.

## 2.3.2 Pin Assignments for the PGF Package

Figure 2–2. 176-Pin PGF Low-Profile Quad Flatpack (Top View)

Table 2–2. Pin Assignments for TMS320VC5441PGF (176-Pin LQFP Package)<sup>†</sup>

| PIN NO. | SIGNAL NAME PIN NO. SIGNAL NAME PIN NO. SIGNAL NAME |     | SIGNAL NAME      | PIN NO. | SIGNAL NAME      |     |                  |

|---------|-----------------------------------------------------|-----|------------------|---------|------------------|-----|------------------|

| 1       | HA[0]/HCNTL0                                        | 2   | HA[1]/HCNTL1     | 3       | HA[2]/A_HINT     | 4   | HA[3]/B_HINT     |

| 5       | HA[4]/C_HINT                                        | 6   | V <sub>SS</sub>  | 7       | V <sub>SS</sub>  | 8   | B_RS             |

| 9       | B_NMI                                               | 10  | B_INT            | 11      | CLKMD            | 12  | TDI              |

| 13      | TESTB                                               | 14  | $DV_DD$          | 15      | HAS              | 16  | HCS              |

| 17      | V <sub>SS</sub>                                     | 18  | VSSA             | 19      | CLKIN            | 20  | HRDY             |

| 21      | VCCA                                                | 22  | CV <sub>DD</sub> | 23      | C∨ <sub>DD</sub> | 24  | EMU0             |

| 25      | BCLKR2                                              | 26  | BCLKX2           | 27      | V <sub>SS</sub>  | 28  | BFSR2            |

| 29      | BFSX2                                               | 30  | CLKOUT           | 31      | $DV_DD$          | 32  | BDR2             |

| 33      | BDX2                                                | 34  | V <sub>SS</sub>  | 35      | A_RS             | 36  | A_NMI            |

| 37      | A_INT                                               | 38  | TDO              | 39      | HA[5]/D_HINT     | 40  | HA[6]            |

| 41      | HA[7]                                               | 42  | HA[8]            | 43      | V <sub>SS</sub>  | 44  | HA[9]            |

| 45      | A_BFSX0                                             | 46  | DV <sub>DD</sub> | 47      | A_GPIO1/A_BIO    | 48  | A_BFSR0          |

| 49      | A_GPIO3/A_TOUT                                      | 50  | V <sub>SS</sub>  | 51      | A_GPIO0/A_XF     | 52  | A_BDR0           |

| 53      | CV <sub>DD</sub>                                    | 54  | A_BDX0           | 55      | CV <sub>DD</sub> | 56  | CV <sub>DD</sub> |

| 57      | CV <sub>DD</sub>                                    | 58  | A_GPIO2/A_WTOUT  | 59      | A_BCLKR0         | 60  | A_BCLKX0         |

| 61      | VSS                                                 | 62  | HD[8]            | 63      | HD[9]            | 64  | DV <sub>DD</sub> |

| 65      | DV <sub>DD</sub>                                    | 66  | HD[10]           | 67      | HD[11]           | 68  | HD[12]           |

| 69      | HD[13]                                              | 70  | V <sub>SS</sub>  | 71      | HD[14]           | 72  | HD[15]           |

| 73      | C_BCLKX0                                            | 74  | CV <sub>DD</sub> | 75      | CV <sub>DD</sub> | 76  | CV <sub>DD</sub> |

| 77      | C_BDR0                                              | 78  | CV <sub>DD</sub> | 79      | C_GPIO3/C_TOUT   | 80  | C_BCLKR0         |

| 81      | C_GPIO0/C_XF                                        | 82  | V <sub>SS</sub>  | 83      | C_BDX0           | 84  | C_GPIO1/C_BIO    |

| 85      | C_GPIO2/C_WTOUT                                     | 86  | DV <sub>DD</sub> | 87      | $DV_DD$          | 88  | C_BFSR0          |

| 89      | C_BFSX0                                             | 90  | HA[10]           | 91      | HA[11]           | 92  | HA[12]           |

| 93      | HA[13]                                              | 94  | V <sub>SS</sub>  | 95      | HA[14]           | 96  | TESTC            |

| 97      | C_INT                                               | 98  | HDS1             | 99      | C_RS             | 100 | BDX1             |

| 101     | BDR1                                                | 102 | BCLKR1           | 103     | $DV_DD$          | 104 | BFSR1            |

| 105     | BFSX1                                               | 106 | V <sub>SS</sub>  | 107     | BCLKX1           | 108 | HMODE            |

| 109     | C∨ <sub>DD</sub>                                    | 110 | HR/W             | 111     | RESET            | 112 | C_NMI            |

| 113     | HDS2                                                | 114 | V <sub>SS</sub>  | 115     | HPI_SEL1         | 116 | HPI_SEL2         |

| 117     | EMU1/OFF                                            | 118 | DV <sub>DD</sub> | 119     | TCK              | 120 | TMS              |

| 121     | TRST                                                | 122 | TESTD            | 123     | D_INT            | 124 | D_NMI            |

| 125     | D_RS                                                | 126 | V <sub>SS</sub>  | 127     | V <sub>SS</sub>  | 128 | HA[15]           |

| 129     | HA[16]                                              | 130 | HA[17]           | 131     | HA[18]           | 132 | D_BFSR0          |

| 133     | D_BFSX0                                             | 134 | DV <sub>DD</sub> | 135     | DV <sub>DD</sub> | 136 | D_GPIO2/D_WTOUT  |

| 137     | D_BDX0                                              | 138 | D_BCLKR0         | 139     | V <sub>SS</sub>  | 140 | D_BCLKX0         |

| 141     | D_GPIO0/D_XF                                        | 142 | C∨ <sub>DD</sub> | 143     | D_BDR0           | 144 | CV <sub>DD</sub> |

| 145     | CV <sub>DD</sub>                                    | 146 | CV <sub>DD</sub> | 147     | D_GPIO1/D_BIO    | 148 | D_GPIO3/D_TOUT   |

| 149     | HD[0]                                               | 150 | V <sub>SS</sub>  | 151     | HD[1]            | 152 | HD[2]            |

| 153     | DV <sub>DD</sub>                                    | 154 | HD[3]            | 155     | HD[4]            | 156 | HD[5]            |

| 157     | HD[6]                                               | 158 | V <sub>SS</sub>  | 159     | HD[7]            | 160 | B_BCLKR0         |

| 161     | B_BCLKX0                                            | 162 | CV <sub>DD</sub> | 163     | CV <sub>DD</sub> | 164 | CV <sub>DD</sub> |

| 165     | B_BDR0                                              | 166 | CV <sub>DD</sub> | 167     | B_BDX0           | 168 | B_GPIO3/B_TOUT   |

| 169     | B_GPIO0/B_XF                                        | 170 | V <sub>SS</sub>  | 171     | B_BFSR0          | 172 | B_GPIO2/B_WTOUT  |

| 173     | B_GPIO1/B_BIO                                       | 174 | DV <sub>DD</sub> | 175     | DV <sub>DD</sub> | 176 | B_BFSX0          |

$<sup>\</sup>ensuremath{^{\dagger}}$  Cells highlighted in gray indicate pins that perform a multiplexed function.

#### 2.4 Signal Descriptions

Table 2–3 lists all the signals, grouped by function. See Section 2.3 for the exact pin locations based on the package type. Pin functions highlighted in gray are secondary (multiplexed) functions.

Table 2-3. Signal Descriptions

| NAME                                                                                                                     | TYPE <sup>†</sup>           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                          | HOST-PORT INTERFACE SIGNALS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| HA18 (MSB)<br>HA17<br>HA16<br>HA15<br>HA14<br>HA13<br>HA12<br>HA11<br>HA10<br>HA9<br>HA8<br>HA7                          | ı‡                          | HPI address pins when HPI is in nonmultiplexed mode. HA18 is used to facilitate program (shared) memory and data (local) memory selection.  The pins include bus holders to reduce power dissipation caused by floating, unused pins. The bus holders also eliminate the need for external pullup resistors on unused pins. When the address bus is not being driven by the external host, the bus holders keep address pins at the last driven logic level. The address bus keepers are disabled at global reset or subsystem A reset, and can be enabled/disabled via the BHA bit of the BSCR register in subsystem A. |  |  |  |  |  |  |

| HA5<br>HA4<br>HA3<br>HA2<br>HA1<br>HA0 (LSB)                                                                             |                             | D_HINT C_HINT B_HINT A_HINT HCNTL1 HCNTL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| HD15 (MSB)<br>HD14<br>HD13<br>HD12<br>HD11<br>HD10<br>HD9<br>HD8<br>HD7<br>HD6<br>HD5<br>HD4<br>HD3<br>HD2<br>HD1<br>HD1 | I/O/Z‡§                     | Parallel bidirectional data bus. These pins are the HPI data bus.  The pins include bus holders to reduce power dissipation caused by floating, unused pins. The bus holders also eliminate the need for external pullup resistors on unused pins. When the data bus is not being driven by the 5441, the bus holders keep data pins at the last driven logic level. The data bus keepers are disabled at global reset or subsystem A reset, and can be enabled/disabled via the BHD bit of the BSCR register in subsystem A.                                                                                            |  |  |  |  |  |  |

<sup>†</sup> I = Input, O = Output, S = Supply, Z = High Impedance

<sup>‡</sup> This pin has an internal bus holder controlled by way of the BSCR register in TMS320C54x<sup>TM</sup> cLEAD core of DSP subsystem A.

<sup>§</sup> This pin is placed in high-impedance when the EMU1/OFF pin operates as OFF and when EMU1/OFF = 0, this case is exclusively for testing and emulation purposes.

<sup>¶</sup> This pin has an internal pullup resistor.

<sup>#</sup> These pins are Schmitt triggered inputs.

This pin is used by Texas Instruments for device testing and should be left unconnected.

<sup>★</sup>This pin has an internal pulldown resistor.

$<sup>\</sup>Box$  Although this pin includes an internal pulldown resistor, a 470- $\Omega$  external pulldown is required. If the  $\overline{TRST}$  pin is connected to multiple DSPs, a buffer is recommended to ensure the V<sub>IL</sub> and V<sub>IH</sub> specifications are met.

Table 2-3. Signal Descriptions (Continued)

| NAME                                             | TYPET                                   | DESCRIPTION                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                     |  |  |  |  |

|--------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                  | HOST-PORT INTERFACE SIGNALS (CONTINUED) |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                     |  |  |  |  |

| HMODE¶                                           | ı                                       | mode allows hos<br>Host-to-DSP and<br>When HMODE is<br>address/data buse | HPI mode select. When this pin is low, it selects the HPI multiplexed address/data mode. The multiplexed address/data mode allows hosts with multiplexed address/data lines access to the HPI registers HPIA, HPIC, and HPID. Host-to-DSP and DSP-to-host interrupts are supported in this mode.  When HMODE is high, it selects the HPI nonmultiplexed mode. HPI nonmultiplexed mode allows hosts with separate address/data buses to access the HPI address range by way of the 19-bit address bus and the HPI data (HPID) register |                                                                                                                                                                                                                                     |  |  |  |  |

|                                                  |                                         |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Host-to-DSP and DSP-to-host interrupts are not supported in this mode.                                                                                                                                                              |  |  |  |  |

| HAS¶#                                            | I                                       |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | le (ALE) or address strobe input. Hosts with multiplexed address and data pins require HAS in the HPIA register. This signal is used only in HPI multiplexed address/data mode                                                      |  |  |  |  |

| HRDY                                             | O/Z§                                    |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | The ready output informs the host when the HPI is ready for the next transfer. While driving, while not driving, it is in high-Z state.                                                                                             |  |  |  |  |

| HR/W                                             | I                                       | HPI read/write str                                                       | obe. T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | his signal is used by the host to control the direction of an HPI transfer.                                                                                                                                                         |  |  |  |  |

| HDS1¶#<br>HDS2¶#                                 | 1                                       | HPI data strobes.                                                        | Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | n by the host read and write strobes to control HPI transfers.                                                                                                                                                                      |  |  |  |  |

| HCS¶#                                            | ı                                       | HPI chip select. M                                                       | lust b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e active during HPI transfers and can remain active between concurrent transfers.                                                                                                                                                   |  |  |  |  |

|                                                  |                                         | PRIMARY                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                     |  |  |  |  |

| D_HINT<br>C_HINT<br>B_HINT<br>A_HINT             | O/Z§                                    | HA5<br>HA4<br>HA3<br>HA2                                                 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Host interrupt pins. HPI can interrupt the host by asserting this low. The host can clear this interrupt by writing a "1" to the HINT bit of the HPIC register. Only supported in HPI multiplexed address/data mode (HMODE pin low) |  |  |  |  |

| HCNTL1<br>HCNTL0                                 | I                                       | HA1<br>HA0                                                               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | HPI control pins. These pins select a host access to the HPIA, HPIC, and HPID registers. Only supported in HPI multiplexed address/data mode (HMODE pin low)                                                                        |  |  |  |  |

| HPI_SEL1<br>HPI_SEL2                             | 1                                       | Subsystem HPI m                                                          | nodule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | select                                                                                                                                                                                                                              |  |  |  |  |

|                                                  |                                         | MULTICH                                                                  | ANN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EL BUFFERED SERIAL PORTS 0, 1, AND 2 SIGNALS                                                                                                                                                                                        |  |  |  |  |

| A_BCLKR0#<br>B_BCLKR0#<br>C_BCLKR0#<br>D_BCLKR0# | I/O/Z§                                  | clock source for                                                         | Receive clocks. x_BCLKR0 serve as the serial shift clocks for the buffered serial-port receiver. Input from an external clock source for clocking data into the McBSP. When not being used as clocks, these pins can be used as general-purpose I/Os by setting RIOEN = 1.                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                     |  |  |  |  |

| _                                                |                                         | x_BCLKR0 can be                                                          | x_BCLKR0 can be configured as outputs by way of the CLKRM bit in the PCR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     |  |  |  |  |

| A_BCLKX0#<br>B_BCLKX0#<br>C_BCLKX0#<br>D_BCLKX0# | I/O/Z§                                  | inputs by setting (                                                      | ransmit clocks. Clock signals used to clock data from the transmit register. These pins can also be configured as a puts by setting CLKXM = 0 in the PCR register. x_BCLKX0 can be sampled as inputs by way of the IN1 bit in the PCR register. When not being used as clocks, these pins can be used as general-purpose I/Os by setting XIOEN = 1.                                                                                                                                                                                   |                                                                                                                                                                                                                                     |  |  |  |  |

| A_BDR0<br>B_BDR0<br>C_BDR0<br>D_BDR0             | I                                       |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ceive (input) pins. When not being used as data-receive pins, these pins can be used as y setting RIOEN = 1.                                                                                                                        |  |  |  |  |

<sup>†</sup> I = Input, O = Output, S = Supply, Z = High Impedance

<sup>&</sup>lt;sup>‡</sup> This pin has an internal bus holder controlled by way of the BSCR register in TMS320C54x™ cLEAD core of DSP subsystem A.

<sup>§</sup> This pin is placed in high-impedance when the EMU1/OFF pin operates as OFF and when EMU1/OFF = 0, this case is exclusively for testing and emulation purposes.

<sup>¶</sup> This pin has an internal pullup resistor.

<sup>#</sup>These pins are Schmitt triggered inputs.

This pin is used by Texas Instruments for device testing and should be left unconnected.

<sup>★</sup>This pin has an internal pulldown resistor.

$<sup>\</sup>Box$  Although this pin includes an internal pulldown resistor, a 470- $\Omega$  external pulldown is required. If the  $\overline{\text{TRST}}$  pin is connected to multiple DSPs, a buffer is recommended to ensure the V<sub>IL</sub> and V<sub>IH</sub> specifications are met.

Table 2-3. Signal Descriptions (Continued)

| NAME                                     | TYPE†  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                          |        | MULTICHANNEL BUFFERED SERIAL PORTS 0, 1, AND 2 SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                   |  |  |

| A_BDX0<br>B_BDX0<br>C_BDX0<br>D_BDX0     | O/Z§   | Buffered serial-port transmit (output) pins. When not being used as data-transmit pins, x_BDX0 can be used as general-purpose I/Os by setting XIOEN = 1.                                                                                                                                                                                                                                                             |  |  |

| A_BFSR0<br>B_BFSR0<br>C_BFSR0<br>D_BFSR0 | I/O/Z§ | Frame synchronization pins for buffered serial-port input data. The x_BFSR0 pulse initiates the receive-data process over x_BDR0. When not being used as data-receive synchronization pins, these pins can be used as general-purpose I/Os by setting RIOEN = 1.                                                                                                                                                     |  |  |

| A_BFSX0<br>B_BFSX0<br>C_BFSX0<br>D_BFSX0 | I/O/Z§ | Buffered serial-port frame synchronization pins for transmitting data. The $x_BFSX0$ pulse initiates the transmit-data process over the $x_BDX0$ pin. If $x_RS$ is asserted when $x_BFSX0$ is configured as output, then $x_BFSX0$ is turned into input mode by the reset operation. When not being used as data-transmit synchronization pins, these pins can be used as general-purpose I/Os by setting XIOEN = 1. |  |  |

| BCLKR1#                                  |        | Receive clock, multiplexed McBSP1                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| BCLKX1#                                  | ı      | Transmit clock, multiplexed McBSP1                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| BDR1                                     |        | Receive data, multiplexed McBSP1                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| BDX1                                     | O/Z§   | Transmit data, multiplexed McBSP1                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| BFSR1                                    |        | Receive frame sync, multiplexed McBSP1                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| BFSX1                                    |        | Transmit frame sync, multiplexed McBSP1                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| BCLKR2#                                  |        | Receive clock, multiplexed McBSP2                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| BCLKX2#                                  | ı      | Transmit clock, multiplexed McBSP2                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| BDR2                                     |        | Receive data, multiplexed McBSP2                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| BDX2                                     | O/Z§   | Transmit data, multiplexed McBSP2                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| BFSR2                                    |        | Receive frame sync, multiplexed McBSP2                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| BFSX2                                    |        | Transmit frame sync, multiplexed McBSP2                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                          |        | CLOCKING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| CLKOUT                                   | O/Z§   | Master clock output signal. CLKOUT cycles at the machine-cycle rate of the CPU. The internal machine cycle is bounded by the falling edges of this signal. The CLKOUT pin can be turned off by writing a "1" to the CLKOUT bit of the PMST register.                                                                                                                                                                 |  |  |

|                                          |        | Multiplexed as shown below based on the selection bits in the GPIO register                                                                                                                                                                                                                                                                                                                                          |  |  |

|                                          |        | GPIO[7] GPIO[6]                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                          |        | A_CLKOUT 0 0 (default)                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                          |        | B_CLKOUTII 0 1                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                          |        | C_CLKOUT   1 0                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                          |        | D_CLKOUT   1 1                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CLKIN#                                   | I      | Input clock to the device. CLKIN connects to a PLL.                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CLKMD#                                   | I      | Clock mode configuration pin at reset. When CLKMD = 0, bypasses PLL; when CLKMD = 1, CLKINx2                                                                                                                                                                                                                                                                                                                         |  |  |

| +                                        |        | - Cupily 7 - Light Impedance                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

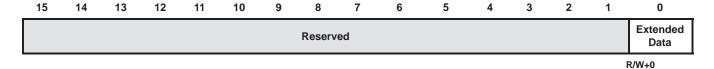

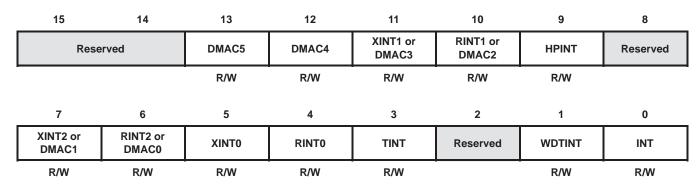

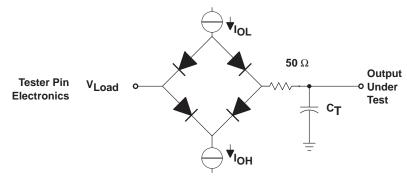

$<sup>\</sup>dagger$  I = Input, O = Output, S = Supply, Z = High Impedance