# TVS3300DRV 33-V Precision Surge Protection Clamp Evaluation Module

This user guide describes the characteristics, operation, and use of the TVS3300DRV Precision Surge Protection Diode Evaluation Module (EVM). The TVS3300DRV is a precision clamp that keeps ultra-low and flat clamping voltage during transient over-voltage events like surge. This user guide includes setup instructions, schematic diagrams, a bill of materials, and printed-circuit board layout drawings for the EVM.

#### Contents

|   | Contents                                         |   |

|---|--------------------------------------------------|---|

| 1 | Introduction                                     | 2 |

| 2 | Board Setup                                      |   |

| 3 | Testing                                          |   |

|   | 3.1 Surge Testing                                |   |

|   | 3.2 ESD Testing                                  |   |

| 4 | Schematic                                        |   |

| 5 | Board Layout                                     |   |

| 6 | Bill of Materials                                | 8 |

|   | List of Figures                                  |   |

| 1 | TVS3300DRV EVM Circuit Board Setup               | 2 |

| 2 | 2-Wire Protection Model                          |   |

| 3 | 2-Wire Protection Test Circuit                   | 3 |

| 4 | 3-Wire Digital I/O Protection Test Circuit       | 4 |

| 5 | TVS3300DRV 4-Wire Interface Schematic            | 4 |

| 6 | TVS3300DRV Surge Test Waveform                   | 5 |

| 7 | TVS3300DRV EVM Board Schematic                   | 6 |

| 8 | TVS3300DRV EVM Top Layer                         | 7 |

| 9 | TVS3300DRV EVM Bottom Layer                      | 7 |

|   | List of Tables                                   |   |

| 1 | ESD Test Probe Point Required Jumper Connections | 5 |

| 2 | Pill of Materials                                | 0 |

Introduction www.ti.com

#### 1 Introduction

Texas Instrument's TVS3300DRV evaluation module helps designers evaluate the operation and performance of the TVS3300DRV device. The TVS3300DRV is a precision clamp that keeps ultra-low and flat clamping voltage during transient over-voltage events like surge. With TI's precision surge technology, the TVS3300DRV's clamping voltage barely changes no matter how high the surge current. The TVS3300DRV also responds fast to the surge to limit overshoot voltage during clamping. Used in the system, its superior voltage suppression performance ensures a safe environment for downstream protected circuits.

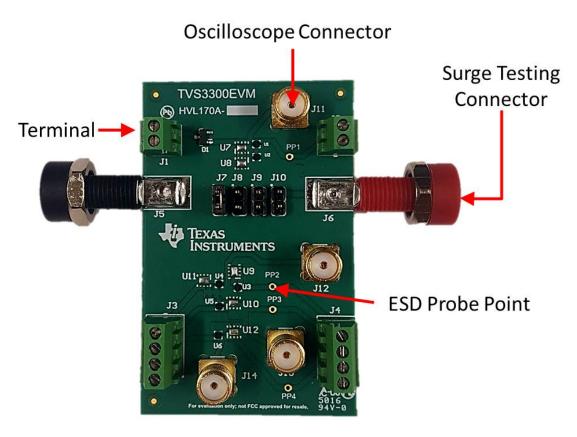

## 2 Board Setup

This TVS3300DRV EVM board includes two sets of screw terminal headers for general purpose inline testing of various connector configurations. There are also two banana plug input ports for easy testing along with 4-50- $\Omega$  SMA connectors for convenient connection to an oscilloscope for testing. Figure 1 shows the basic setup of the EVM along with important connector locations.

Figure 1. TVS3300DRV EVM Circuit Board Setup

www.ti.com Testing

#### 3 Testing

Section 3.1 and Section 3.2 outline the testing procedures for the TVS3300DRV EVM circuit board along with their respective results. Care must be taken when testing any EVM in order to avoid potential damage to the board.

### 3.1 Surge Testing

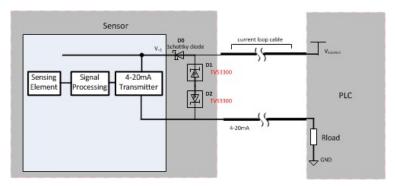

Figure 2. 2-Wire Protection Model

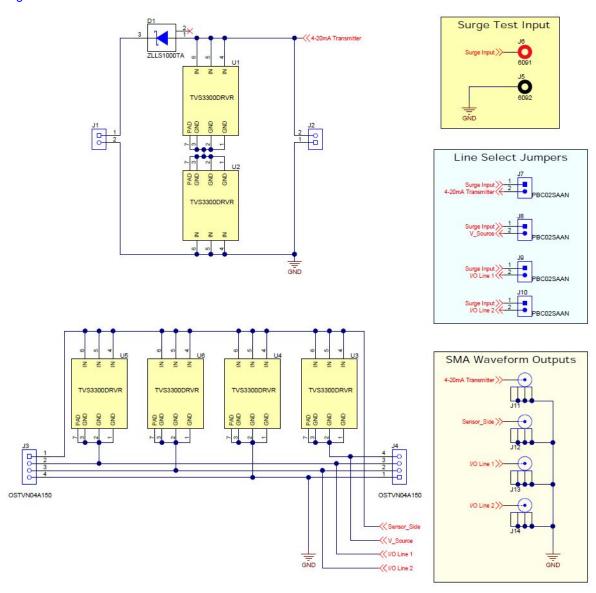

For the surge testing, there are two distinct setups. In Figure 2, two TVS3300DRV's D1 (U1) and D2 (U2) protect the 4-20-mA sensor transmitter in a back-to-back configuration by limiting the voltage difference between the two wires connected to the transmitter. In mis-wiring and negative surge situations, Schottky diode D0 (D1 in Figure 3) keeps the current from flowing reversely from the transmitter.

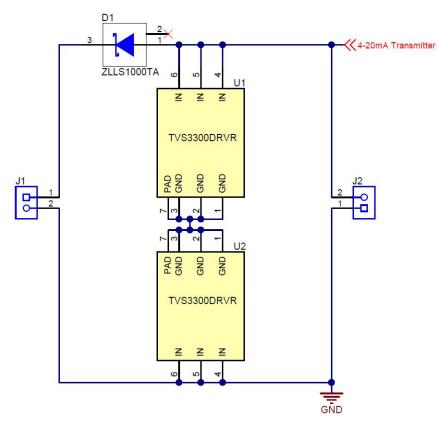

Figure 3. 2-Wire Protection Test Circuit

Testing www.ti.com

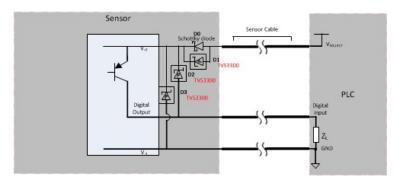

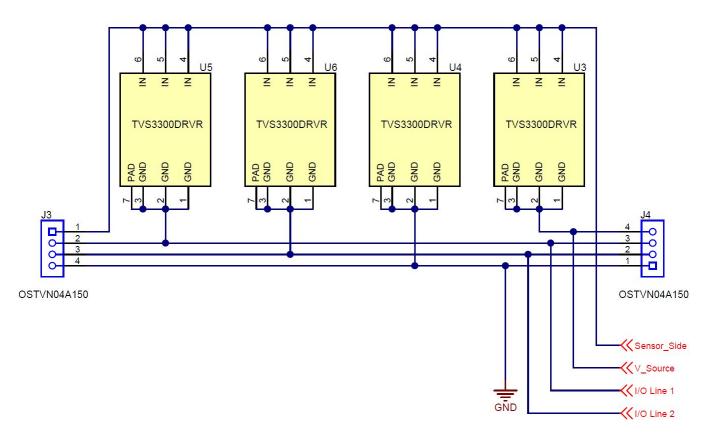

The next surge test is modeled from Figure 4 with the addition of a second I/O line. The EVM jumpers J7-J10 can be used to select which line is to be tested. Table 1 shows the corresponding SMA connector for each jumper position.

Figure 4. 3-Wire Digital I/O Protection Test Circuit

Figure 5. TVS3300DRV 4-Wire Interface Schematic

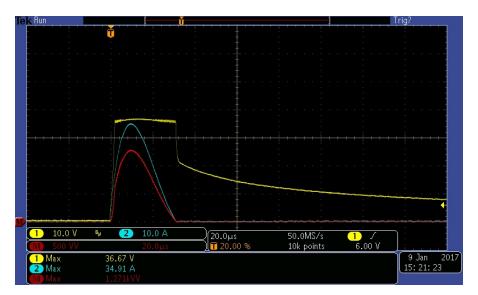

From Figure 5, four TVS3300DRV's protect the switch output sensor transmitter from surge and mis-wiring conditions. U3 blocks the reverse current when the system is mis-wired and takes most of the current during positive and negative surge. U5 and U6 protects the sensor transmitter by clamping the voltage between power supply and the digital output during surge. U4 protects the sensor transmitter by clamping the voltage between power supply and the ground return during surge. Figure 6 shows a 35-A surge test done on the TVS3300DRV EVM. As can be seen from the waveform, the TVS3300 effectively handles this surge and returns to normal conditions in less than  $40~\mu s$ .

www.ti.com Testing

Figure 6. TVS3300DRV Surge Test Waveform

### 3.2 ESD Testing

The TVS3300DRV also provides ESD protection up to ±8-kV contact and ±15-kV air gap according to IEC 6100-4-2. After connecting to the appropriate test equipment, evaluate the ESD protection provided by the TVS3300DRV by using an ESD simulator on one of the probe points (PP#) to create an ESD event. For specific information on ESD testing procedures, see the application report, *IEC 61000-4-x Tests for TI's Protection Devices*.

Table 1 shows the correlating jumper position for the EVM based on the target probe point to be tested. Further test connection details can be seen in Figure 7.

**Table 1. ESD Test Probe Point Required Jumper Connections**

| ESD Probe Point | Required Jumper Position | Output Waveform SMA Connector |

|-----------------|--------------------------|-------------------------------|

| PP1             | J7                       | J11                           |

| PP2             | J8                       | J12                           |

| PP3             | J9                       | J13                           |

| PP4             | J10                      | J14                           |

Schematic www.ti.com

### 4 Schematic

Figure 7 shows the circuit schematic for the TVS3300DRV EVM.

Figure 7. TVS3300DRV EVM Board Schematic

www.ti.com Board Layout

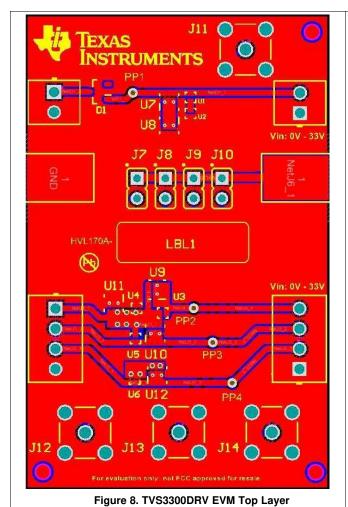

# 5 Board Layout

TEXAS

INSTRUMENTS

PP1

U7

U8

Vin: 0V - 33V

Vin: 0V - 33V

Vin: 0V - 33V

J12

J13

J14

For evaluation only: not FCC approved for recale.

Figure 9. TVS3300DRV EVM Bottom Layer

Bill of Materials www.ti.com

# 6 Bill of Materials

### **Table 2. Bill of Materials**

| Designator                | Qty | Valu<br>e | Description                                                 | Package Reference        | Part Number | Manufacturer           |

|---------------------------|-----|-----------|-------------------------------------------------------------|--------------------------|-------------|------------------------|

| D1                        | 1   | _         | Diode, Schottky, 40 V, 1.16 A, AEC-Q101, SOT-23             | SOT-23                   | ZLLS1000TA  | Zetex                  |

| J1, J2                    | 2   | _         | Terminal Block, 2.54 mm, 2×1, Brass, TH                     | On-<br>Shore_OSTVN02A150 | OSTVN02A150 | On Shore<br>Technology |

| J3, J4                    | 2   | _         | Terminal Block, 2.54 mm, 4×1, Brass, TH                     | On-<br>Shore_OSTVN04A150 | OSTVN04A150 | On Shore<br>Technology |

| J5                        | 1   | _         | Standard Banana Jack, Insulated, Black                      | 6092                     | 6092        | Keystone               |

| J6                        | 1   | _         | Standard Banana Jack, Insulated, Red                        | 6091                     | 6091        | Keystone               |

| J7, J8, J9, J10           | 4   | _         | Header, 100 mil, 2×1, Gold, TH                              | Sullins_PBC02SAAN        | PBC02SAAN   | Sullins                |

| J11, J12, J13, J14        | 4   | _         | SMA Straight PCB Socket Die Cast, 50 $\Omega$ , TH          | TE_5-1814832-1           | 5-1814832-1 | TE<br>Connectivity     |

| SH-J5                     | 1   | _         | Shunt, 2.54 mm, Gold, Black                                 | Wurth_60900213421        | 60900213421 | Wurth<br>Electronics   |

| U1, U2, U3, U4,<br>U5, U6 | 6   | _         | 33-V Precision Surge Protection Clamp,<br>DRV0006A (WSON-6) | DRV0006A                 | TVS3300DRVR | Texas<br>Instruments   |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated