## Introduction

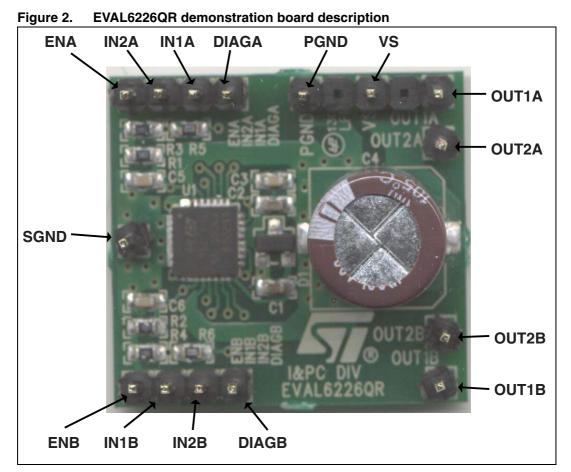

This application note describes the demonstration board of the DMOS dual full-bridge L6226Q designed for motor control applications. The board implements a typical application that can be used as a reference design to drive two-phase bipolar stepper motors with currents up to 1A DC, multiple DC motors and a wide range of inductive loads.

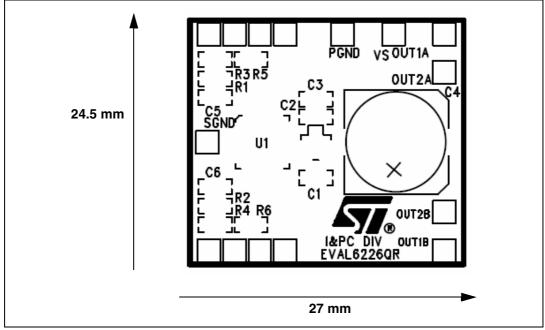

Thanks to the small footprint of the L6226Q (QFN 5 x 5 mm, 32-lead) the PCB is very compact (27 x 24.5 mm).

#### Figure 1. EVAL6226QR demonstration board

# 1 Demonstration board description

| Table 1. EVAL6226R pin connections |                                                                                                                                                                                                                                                                                                                        |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Туре                               | Function                                                                                                                                                                                                                                                                                                               |  |  |

| Power supply                       | Bridge A and bridge B power supply                                                                                                                                                                                                                                                                                     |  |  |

| Ground                             | Power ground terminal                                                                                                                                                                                                                                                                                                  |  |  |

| Logic input                        | Bridge A logic input 1                                                                                                                                                                                                                                                                                                 |  |  |

| Logic Input                        | Bridge A logic input 2                                                                                                                                                                                                                                                                                                 |  |  |

| Logic input                        | Bridge A enable (active high). When low, the power DMOSs of bridge A are switched OFF.                                                                                                                                                                                                                                 |  |  |

| Logic input                        | Bridge B logic input 1                                                                                                                                                                                                                                                                                                 |  |  |

| Logic input                        | Bridge B logic input 2                                                                                                                                                                                                                                                                                                 |  |  |

| Logic input                        | Bridge B enable (active high). When low, the power DMOSs of bridge B are switched OFF.                                                                                                                                                                                                                                 |  |  |

| Open drain output                  | Bridge A overcurrent detection and thermal protection pin.<br>An internal open drain transistor pulls to GND when<br>overcurrent on bridge A is detected or in case of thermal<br>protection.                                                                                                                          |  |  |

| Open drain output                  | Bridge B overcurrent detection and thermal protection pin.<br>An internal open drain transistor pulls to GND when<br>overcurrent on bridge B is detected or in case of thermal<br>protection.                                                                                                                          |  |  |

| Ground                             | Signal ground terminal                                                                                                                                                                                                                                                                                                 |  |  |

| Power output                       | Bridge A output 1                                                                                                                                                                                                                                                                                                      |  |  |

| Power output                       | Bridge A output 2                                                                                                                                                                                                                                                                                                      |  |  |

| Power output                       | Bridge B output 1                                                                                                                                                                                                                                                                                                      |  |  |

| Power output                       | Bridge B output 2                                                                                                                                                                                                                                                                                                      |  |  |

|                                    | Type         Power supply         Ground         Logic input         Open drain output         Open drain output         Ground         Power output         Power output         Power output |  |  |

### Table 1. EVAL6226R pin connections

The INx input pins drive the corresponding half-bridge. When low logic level is applied the low side MOS is switched on, whereas a high logic level turns on the high side MOS.

Pins ENA and ENB are used to implement overcurrent and thermal protection when connected respectively to the outputs DIAGA and DIAGB.

The output current detection thresholds are selected by the resistor connected between the IC dedicated pins and ground.

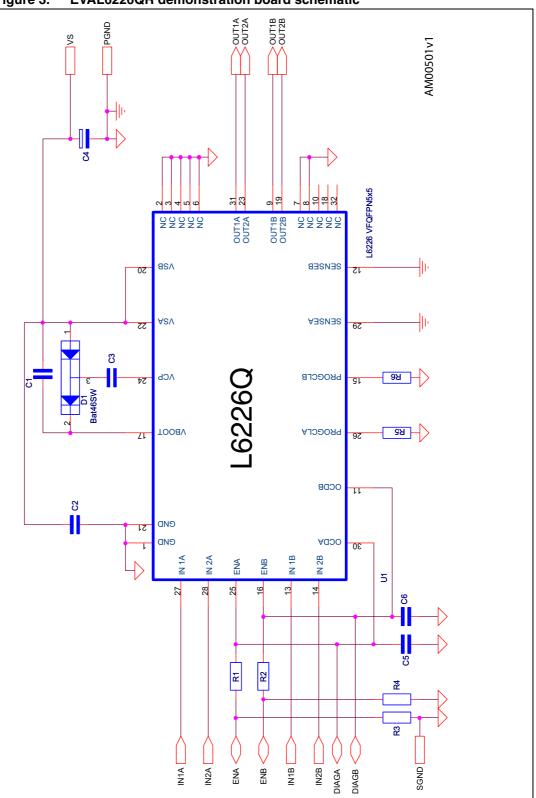

*Table 2* summarizes the electrical specification of the application and *Figure 3* shows the electrical schematic.

| Parameter                                     | Value         |

|-----------------------------------------------|---------------|

| Supply voltage range (VS)                     | 8 to 52 Vdc   |

| RMS output current rating (OUTx)              | up to 1.4 A   |

| Switching frequency                           | up to 100 kHz |

| Input and enable voltage range                | 0 to + 5 V    |

| OCD pins voltage range                        | -0.3 to 10 V  |

| Operating temperature range                   | -25 to +125°C |

| L6226Q thermal resistance junction to ambient | 42°C/W        |

Table 2.

EVAL6226QR electrical specification (recommended value)

Figure 3. EVAL6226QR demonstration board schematic

| Part reference | Part value       | Part description              |

|----------------|------------------|-------------------------------|

| C1             | 220 nF/25 V      | Capacitor                     |

| C2             | 220 nF/63 V      | Capacitor                     |

| C3             | 10 nF/25 V       | Capacitor                     |

| C4             | 100 μF/63 V      | Capacitor                     |

| C5, C6         | 5.6 nF           | Capacitor                     |

| D1             | BAT46SW          | Diodes                        |

| R1, R2, R3, R4 | 100 kΩ 5% 0.25 W | Resistor                      |

| R5, R6         | 10 kΩ 1% 0.25 W  | Resistor                      |

| R9, R10        | 0.4 kΩ 1 W       | Resistor                      |

| U1             | L6226Q           | Dual full-bridge in VFQFPN5x5 |

Table 3.EVAL6226QR part list

D1, C1 and C3 constitute a charge pump circuit, which generates the supply voltage for the high-side integrated MOSFETs. Due to voltage and current switching at relatively high frequency, these components are connected through short paths in order to minimize induced noise on other circuitries.

R1, R2 and C5, C6 are used by the overcurrent protection integrated circuitry (disable time  $t_{DISABLE}$  is about 200 µs and delay time  $t_{DELAY}$  about 1 µs using the values in *Table 3*).

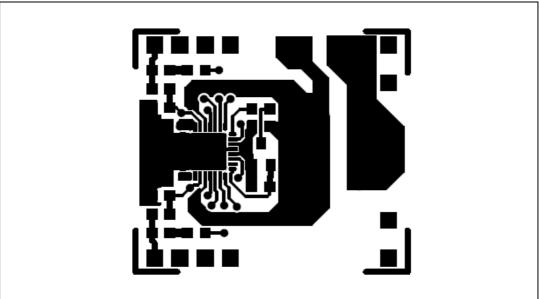

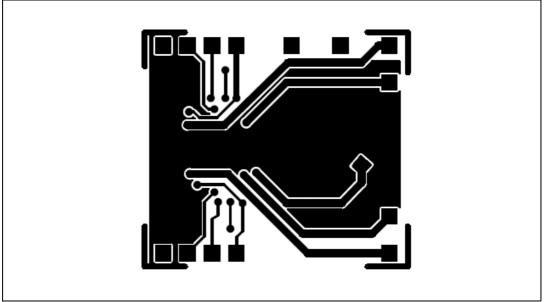

R5 and R6 are used to set the output current detection threshold at about 1.1 A typical value. *Figure 4, Figure 5* and *Figure 6* show the placement of the components and the layout of the two layers of the EVAL6226QR reference design board. A GND area has been used to improve the IC power dissipation.

57

# 2 Revision history

### Table 4. Document revision history

| Date        | Revision | Changes                                                                                            |

|-------------|----------|----------------------------------------------------------------------------------------------------|

| 06-Oct-2008 | 1        | Initial release                                                                                    |

| 28-Jan-2009 | 2        | Updated value in <i>Table 2: EVAL6226QR electrical specification</i> (recommended value) on page 3 |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com