### Document Number: MC33981 Rev. 12.0, 7/2023

10

# Single High Side Switch (4.0 mOhm), PWM clock up to 60 kHz

The 33981 is a high frequency, self-protected 4.0 m $\Omega$  R<sub>DS(ON)</sub> high side switch used to replace electromechanical relays, fuses, and discrete devices in power management applications.

The 33981 can be controlled by pulse-width modulation (PWM) with a frequency up to 60 kHz. It is designed for harsh environments, and it includes self-recovery features. The 33981 is suitable for loads with high inrush current, as well as motors and all types of resistive and inductive loads.

The 33981 is packaged in a 12 x 12 mm non-leaded power-enhanced PQFN package with exposed tabs.

### **Features**

- Single 4.0 m $\Omega$  R<sub>DS(ON)</sub> maximum high side switch

- PWM capability up to 60 kHz with duty cycle from 5 % to 100 %

- · Very low standby current

- · Slew-rate control with external capacitor

- Over-current and over-temperature protection, under-voltage shutdown, and fault reporting

- · Reverse battery protection

- Gate drive signal for external low side N-channel MOSFET with protection features

- · Output current monitoring

- · Temperature feedback

### 33981

### HIGH SIDE SWITCH

Bottom View FK (Pb-Free Suffix) 98ARL10521D 98ASA00815D 16-PIN PQFN (12 X 12)

| ORDER                                          | ORDERING INFORMATION                   |         |  |  |  |  |

|------------------------------------------------|----------------------------------------|---------|--|--|--|--|

| Device<br>(Add R2 Suffix for<br>Tape and Reel) | Temperature<br>Range (T <sub>A</sub> ) | Package |  |  |  |  |

| MC33981BHFK                                    |                                        |         |  |  |  |  |

| MC33981ABHFK                                   | -40 to 125 °C                          | 16 PQFN |  |  |  |  |

| MC33981ADHFK                                   |                                        |         |  |  |  |  |

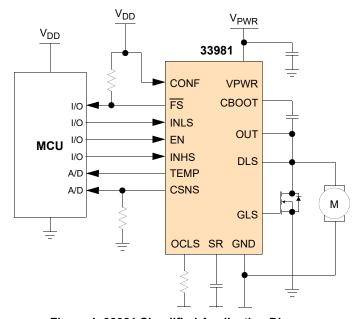

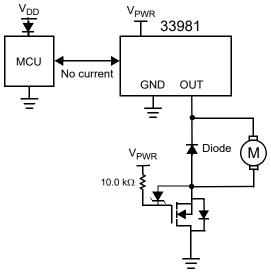

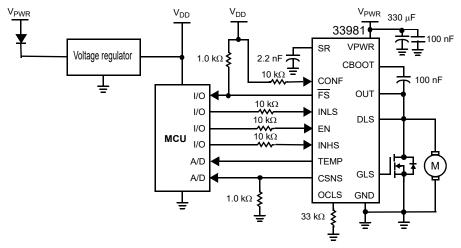

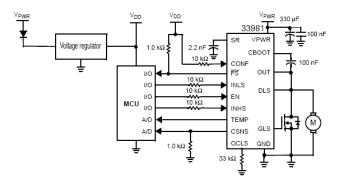

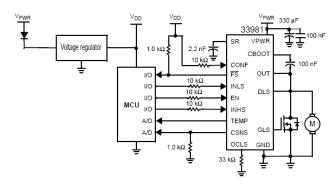

Figure 1. 33981 Simplified Application Diagram

### **DEVICE VARIATIONS**

**Table 1. Device Peak Solder Temperature**

| Device       | Description <sup>(1)</sup>                                      |

|--------------|-----------------------------------------------------------------|

| MC33981BHFK  | Original BOM and lower Peak Package Temperature solderability.  |

| MC33981ABHFK | Improved BOM and higher Peak Package Temperature solderability. |

| MC33981ADHFK | Improved BOM and higher Peak Package Temperature solderability. |

### Notes

PPT values can be found on NXP's web site, or contact sales. Reference Peak Package Reflow Temperature

During Reflow<sup>(6)</sup>, <sup>(7)</sup>

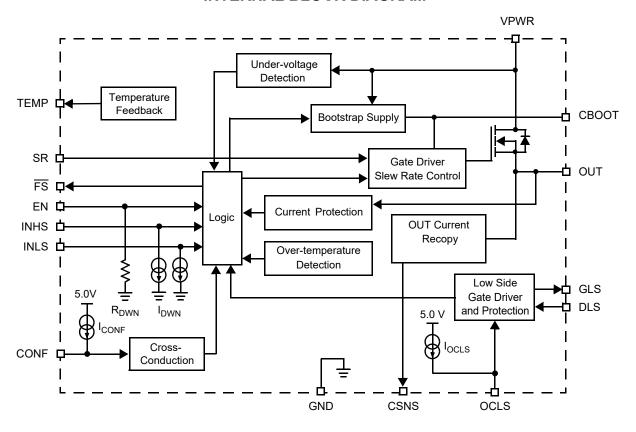

### INTERNAL BLOCK DIAGRAM

Figure 2. 33981 Simplified Internal Block Diagram

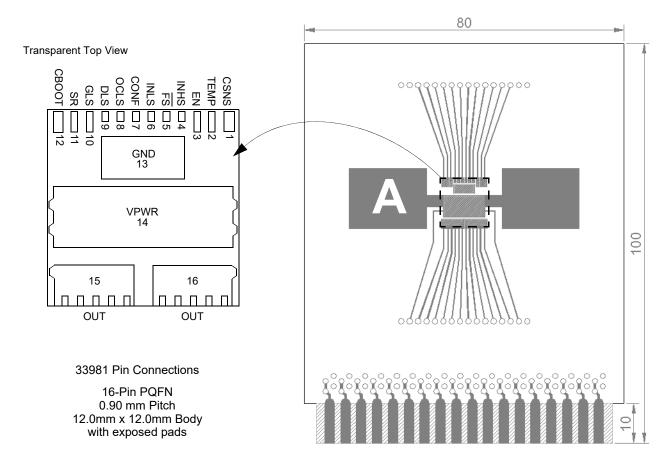

### **PIN CONNECTIONS**

# Package Transparent Top View CBOOT REMPOSITION CSNS CONFIDENT FISTER CSNS CSNS CNHS CSNS CNHS CSNS CNHS CSNS CNHS CNHS

Figure 3. Pin Connections

### **Table 2. PIN DEFINITIONS**

Descriptions of the pins listed in the table below can be found in the Functional Description section located on page 16.

| Pin<br>Number | Pin Name | Pin<br>Function | Formal Name                  | Definition                                                                                                        |

|---------------|----------|-----------------|------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1             | CSNS     | Reports         | Output Current Monitoring    | This pin is used to generate a ground-referenced voltage for the microcontroller (MCU) to monitor output current. |

| 2             | TEMP     | Reports         | Temperature Feedback         | This pin is used by the MCU to monitor board temperature.                                                         |

| 3             | EN       | Input           | Enable<br>(Active High)      | This pin is used to place the device in a low-current Sleep mode.                                                 |

| 4             | INHS     | Input           | Serial Input High Side       | This input pin is used to control the output of the device.                                                       |

| 5             | FS       | Reports         | Fault Status<br>(Active Low) | This pin monitors fault conditions and is active LOW.                                                             |

| 6             | INLS     | Input           | Serial Input Low Side        | This pin is used to control an external low side N-channel MOSFET.                                                |

| 7             | CONF     | Input           | Configuration Input          | This input manages MOSFET N-channel cross-conduction.                                                             |

| 8             | OCLS     | Input           | Low Side Overload            | This pin sets the V <sub>DS</sub> protection level of the external low side MOSFET.                               |

| 9             | DLS      | Input           | Drain Low Side               | This pin is the drain of the external low side N-channel MOSFET.                                                  |

| 10            | GLS      | Output          | Low Side Gate                | This output pin drives the gate of the external low side N-channel MOSFET.                                        |

| 11            | SR       | Input           | Slew Rate Control            | This pin controls the output slew rate.                                                                           |

| 12            | СВООТ    | Input           | Bootstrap Capacitor          | This pin provides the high pulse current to drive the device.                                                     |

| 13            | GND      | Ground          | Ground                       | This is the ground pin of the device.                                                                             |

| 14            | VPWR     | Input           | Positive Power Supply        | This pin is the source input of operational power for the device.                                                 |

| 15, 16        | OUT      | Output          | Output                       | These pins provide a protected high side power output to the load connected to the device.                        |

### **ELECTRICAL CHARACTERISTICS**

### **MAXIMUM RATINGS**

### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted.

| Rating                                   | Rating Symbol                              |              | Unit |

|------------------------------------------|--------------------------------------------|--------------|------|

| ELECTRICAL RATINGS                       | ,                                          |              |      |

| Power Supply Voltage                     | $V_{PWR}$                                  |              | V    |

| Steady-state                             |                                            | -16 to 41    |      |

| Input/Output Pins Voltage <sup>(2)</sup> | INHS, INLS,<br>CONF, CSNS, FS,<br>TEMP, EN | -0.3 to 7.0  | V    |

| Output Voltage                           | V <sub>OUT</sub>                           |              | V    |

| Positive                                 |                                            | 41.0         |      |

| Negative                                 |                                            | -5.0         |      |

| Continuous Output Current <sup>(3)</sup> | I <sub>OUT</sub>                           | 40.0         | Α    |

| CSNS Input Clamp Current                 | I <sub>CL(CSNS)</sub>                      | 15.0         | mA   |

| EN Input Clamp Current                   | I <sub>CL(EN)</sub>                        | 2.5          | mA   |

| SR Voltage                               | V <sub>SR</sub>                            | -0.3 to 54.0 | V    |

| C <sub>BOOT</sub> Voltage                | C <sub>BOOT</sub>                          | -0.3 to 54.0 | V    |

| OCLS Voltage                             | V <sub>OCLS</sub>                          | -5.0 to 7.0  | V    |

| Low Side Gate Voltage                    | V <sub>GLS</sub>                           | -0.3 to 15.0 | V    |

| Low Side Drain Voltage                   | $V_{DLS}$                                  | -5.0 to 41.0 | V    |

| ESD Voltage <sup>(4)</sup>               | V <sub>ESD</sub>                           |              | V    |

| Human Body Model (HBM)                   |                                            | ±2000        |      |

| Charge Device Model (CDM)                |                                            |              |      |

| Corner Pins (1, 12, 15, 16)              |                                            | ±750         |      |

| All Other Pins (2-11, 13-14)             |                                            | ±500         |      |

- 2. Exceeding voltage limits on INHS, INLS, CONF, CSNS, FS, TEMP, and EN pins may cause a malfunction or permanent damage to the

- 3. Continuous high side output rating as long as maximum junction temperature is not exceeded. Calculation of maximum output current using package thermal resistance is required.

- 4. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ) and the Charge Device Model (CDM), Robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

## ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted.

| Rating                                                                        | Symbol            | Value      | Unit |

|-------------------------------------------------------------------------------|-------------------|------------|------|

| THERMAL RATINGS                                                               |                   |            |      |

| Operating Temperature                                                         |                   |            | °C   |

| Ambient                                                                       | T <sub>A</sub>    | -40 to 125 |      |

| Junction                                                                      | $T_J$             | -40 to 150 |      |

| Storage Temperature                                                           | T <sub>STG</sub>  | -55 to 150 | °C   |

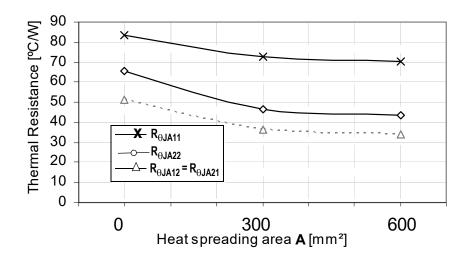

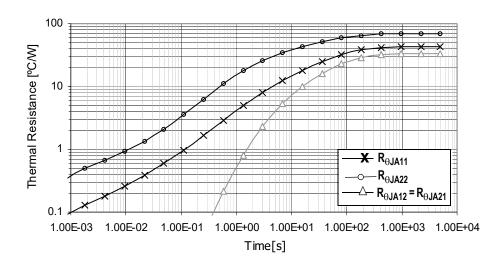

| Thermal Resistance <sup>(5)</sup>                                             |                   |            | °C/W |

| Junction to Power Die Case                                                    | $R_{	heta JC}$    | 1.0        |      |

| Junction to Ambient                                                           | $R_{	hetaJA}$     | 30.0       |      |

| Peak Package Reflow Temperature During Reflow <sup>(6)</sup> , <sup>(7)</sup> | T <sub>PPRT</sub> | Note 7     | °C   |

- 5. Device mounted on a 2s2p test board per JEDEC JESD51-2.

- 6. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 7. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.nxp.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

### STATIC ELECTRICAL CHARACTERISTICS

**Table 4. Static Electrical Characteristics**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                                         | Symbol                  | Min  | Тур     | Max  | Unit |

|--------------------------------------------------------------------------------------------------------|-------------------------|------|---------|------|------|

| POWER INPUT (VPWR)                                                                                     |                         |      | 1       | •    |      |

| Battery Supply Voltage Range                                                                           | $V_{PWR}$               |      |         |      | V    |

| Fully Operational                                                                                      |                         | 6.0  | _       | 27.0 |      |

| Extended <sup>(8)</sup>                                                                                |                         | 4.5  | _       | 27.0 |      |

| VPWR Supply Current                                                                                    | I <sub>PWR(ON)</sub>    |      |         |      | mA   |

| INHS = 1 and OUT Open, INLS = 0                                                                        | , ,                     | _    | 10.0    | 12.0 |      |

| VPWR Supply Current                                                                                    | I <sub>PWR(SBY)</sub>   |      |         |      | mA   |

| INHS = INLS = 0, EN = 5.0 V, OUT Connected to GND                                                      |                         | _    | 10.0    | 12.0 |      |

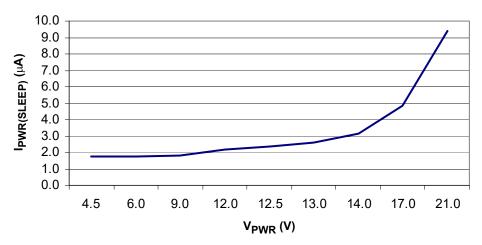

| Sleep-state Supply Current                                                                             | I <sub>PWR(SLEEP)</sub> |      |         |      | μА   |

| (V <sub>PWR</sub> < 14 V, EN = 0 V, OUT Connected to GND)                                              |                         |      |         |      |      |

| T <sub>A</sub> = 25 °C                                                                                 |                         | -    | _       | 5.0  |      |

| T <sub>A</sub> = 125 °C                                                                                |                         | _    | _       | 50.0 |      |

| Under-voltage Shutdown                                                                                 | V <sub>PWR(UV)</sub>    | 2.0  | 4.0     | 4.5  | V    |

| Under-voltage Hysteresis                                                                               | V <sub>PWR(UVHYS)</sub> | 0.05 | 0.15    | 0.3  | V    |

| POWER OUTPUT (IOUT, VPWR)                                                                              | <u> </u>                |      | 1       |      |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 20 A, T <sub>A</sub> = 25 °C)                 | R <sub>DS(ON)25</sub>   |      |         |      | mΩ   |

| $V_{PWR} = 6.0 V$                                                                                      | , ,                     | _    | _       | 6.0  |      |

| V <sub>PWR</sub> = 9.0 V                                                                               |                         | _    | _       | 5.0  |      |

| V <sub>PWR</sub> = 13.0 V                                                                              |                         | -    | _       | 4.0  |      |

| Output Drain-to-Source ON Resistance (I <sub>OUT</sub> = 20 A, T <sub>A</sub> = 150 °C)                | R <sub>DS(ON)150</sub>  |      |         |      | mΩ   |

| V <sub>PWR</sub> = 6.0 V                                                                               | , ,                     | _    | _       | 10.2 |      |

| V <sub>PWR</sub> = 9.0 V                                                                               |                         | _    | _       | 8.5  |      |

| V <sub>PWR</sub> = 13.0 V                                                                              |                         | _    | _       | 6.8  |      |

| Output Source-to-Drain ON Resistance (I <sub>OUT</sub> = -20 A, T <sub>A</sub> = 25 °C) <sup>(9)</sup> | R <sub>SD(ON)</sub>     |      |         |      | mΩ   |

| V <sub>PWR</sub> = - 12 V                                                                              | ( ,                     | _    | _       | 8.0  |      |

| Output Over-current Detection Level                                                                    | I <sub>OCH</sub>        |      |         |      | Α    |

| 9.0 V < V <sub>PWR</sub> < 16 V                                                                        |                         |      |         |      |      |

| MC33981BHFK and M33981ABHFK                                                                            |                         | 75   | 100     | 125  |      |

| MC33981ADHFK                                                                                           |                         | 70   | 100     | 135  |      |

| Current Sense Ratio                                                                                    | C <sub>SR</sub>         |      |         |      | _    |

| $9.0 \text{ V} \leq \text{V}_{\text{PWR}} \leq 16 \text{ V}, \text{CSNS} \leq 4.5 \text{ V}$           |                         |      |         |      |      |

| MC33981BHFK and M33981ABHFK                                                                            |                         | _    | 1/20000 | _    |      |

| MC33981ADHFK                                                                                           |                         | _    | 1/20400 | _    |      |

### **Table 4. Static Electrical Characteristics (continued)**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                               | Symbol              | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| Current Sense Ratio (C <sub>SR</sub> ) Accuracy                                              | C <sub>SR_ACC</sub> |     |     |     | %    |

| $9.0 \text{ V} \leq \text{V}_{\text{PWR}} \leq 16 \text{ V}, \text{CSNS} \leq 4.5 \text{ V}$ | _                   |     |     |     |      |

| Output Current                                                                               |                     |     |     |     |      |

| MC33981BHFK and M33981ABHFK                                                                  |                     |     |     |     |      |

| 5.0 A                                                                                        |                     | -20 | _   | 20  |      |

| 15 A, 20 A, and 30 A                                                                         |                     | -15 | _   | 15  |      |

| MC33981ADHFK                                                                                 |                     |     |     |     |      |

| 5.0 A, 15 A, 20 A, and 30 A                                                                  |                     | -25 | _   | 25  |      |

### Notes

- 8. OUT can be commanded fully on, PWM is available at room. Low Side Gate driver is available. Protections and Diagnosis are not available. Min/max parameters are not guaranteed.

- 9. Source-Drain ON Resistance (Reverse Drain-to-Source ON Resistance) with negative polarity V<sub>PWR</sub>.

### POWER OUTPUT (VPWR) (continued)

| Current Sense Voltage Clamp                  | V <sub>CL(CSNS)</sub>   |     |     |     | V  |

|----------------------------------------------|-------------------------|-----|-----|-----|----|

| I <sub>CSNS</sub> = 15 mA                    |                         | 4.5 | 6.0 | 7.0 |    |

| Current Sense Leakage <sup>(10)</sup>        | I <sub>LEAK(CSNS)</sub> |     |     |     | μА |

| INHS = 1 with OUT opened of load or INHS = 0 |                         | 0   | 13  | 17  |    |

| Over-temperature Shutdown                    | T <sub>SD</sub>         | 160 | 175 | 190 | °C |

| · ·                                          | 05                      |     |     |     |    |

### LOW SIDE GATE DRIVER (VPWR, VGLS, VOCLS)

| Low Side Gate Voltage                                           | $V_{GLS}$           |      |      |      | V  |

|-----------------------------------------------------------------|---------------------|------|------|------|----|

| V <sub>PWR</sub> = 6.0 V                                        |                     | 5.0  | 5.4  | 6.0  |    |

| V <sub>PWR</sub> = 9.0 V                                        |                     | 8.0  | 8.4  | 9.0  |    |

| V <sub>PWR</sub> = 13 V                                         |                     | 12.0 | 12.4 | 13.0 |    |

| V <sub>PWR</sub> = 27 V                                         |                     | 12.0 | 12.4 | 13.0 |    |

| Low Side Gate Sinked Current                                    | I <sub>GLSNEG</sub> |      |      |      | mA |

| V <sub>GLS</sub> = 2.0 V, V <sub>PWR</sub> = 13 V               |                     | _    | 100  | -    |    |

| Low Side Gate Sourced Current                                   | I <sub>GLSPOS</sub> |      |      |      | mA |

| V <sub>GLS</sub> = 2.0 V, V <sub>PWR</sub> = 13 V               |                     | _    | 100  | -    |    |

| Low Side Overload Detection Level versus Low Side Drain Voltage | V <sub>DS_LS</sub>  |      |      |      | mV |

| $V_{OCLS} - V_{DLS}$ , $(V_{OCLS} \le 4.0 \text{ V})$           |                     |      |      |      |    |

| MC33981BHFK and M33981ABHFK                                     |                     | -50  | -    | 50   |    |

| MC33981ADHFK                                                    |                     | -75  | _    | 75   |    |

### CONTROL INTERFACE (CONF, INHS, INLS, EN, OCLS)

| Input Logic High-voltage (CONF, INHS, INLS)       | V <sub>IH</sub>    | 3.3 | _   | _    | V  |

|---------------------------------------------------|--------------------|-----|-----|------|----|

| Input Logic Low-voltage (CONF, INHS, INLS)        | V <sub>IL</sub>    | -   | _   | 1.0  | V  |

| Input Logic Voltage Hysteresis (CONF, INHS, INLS) | V <sub>INHYS</sub> | 100 | 600 | 1200 | mV |

| Input Logic Active Pull-down Current (INHS, INLS) | I <sub>DWN</sub>   | 5.0 | 10  | 20   | μΑ |

| Enable Pull-down Resistor (EN)                    | R <sub>DWN</sub>   | 100 | 200 | 400  | kΩ |

| Enable Voltage Threshold (EN)                     | V <sub>EN</sub>    |     | 2.5 |      | V  |

### 33981

### **Table 4. Static Electrical Characteristics (continued)**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                      | Symbol             | Min  | Тур | Max  | Unit |

|-------------------------------------|--------------------|------|-----|------|------|

| Input Clamp Voltage (EN)            | V <sub>CLEN</sub>  |      |     |      | V    |

| I <sub>EN</sub> < 2.5 mA            |                    | 7.0  | _   | 14   |      |

| Input Forward Voltage (EN)          | V <sub>F(EN)</sub> | -2.0 | -   | -0.3 | V    |

| Input Active Pull-up Current (OCLS) | I <sub>OCLSp</sub> | 50   | 100 | 200  | μА   |

| Input Active Pull-up Current (CONF) | I <sub>CONF</sub>  | 5.0  | 10  | 20   | μА   |

- 10. This parameter is achieved by the design characterization by measuring a statistically relevant sample size across process variations but not tested in production.

- 11. Parameter is guaranteed by process monitoring but is not production tested.

# ELECTRICAL CHARACTERISTICS STATIC ELECTRICAL CHARACTERISTICS

### **Table 4. Static Electrical Characteristics (continued)**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                             | Symbol             | Min  | Тур  | Max  | Unit  |

|------------------------------------------------------------|--------------------|------|------|------|-------|

| CONTROL INTERFACE (CONF, INHS, INLS, EN, OCLS) (continued) | <b>"</b>           | 1    |      | l    |       |

| FS Tri-state Capacitance <sup>(12)</sup>                   | C <sub>FS</sub>    | _    | _    | 20   | pF    |

| FS Low-state Output Voltage                                | V <sub>FSL</sub>   |      |      |      | V     |

| $I_{\overline{FS}} = -1.6 \text{ mA}$                      |                    | _    | 0.2  | 0.4  |       |

| Temperature Feedback                                       | V <sub>TFEED</sub> |      |      |      | V     |

| $T_A = 25^{\circ}C$ for $V_{PWR} = 14 \text{ V}$           |                    |      |      |      |       |

| MC33981BHFK and M33981ABHFK                                |                    | 3.35 | 3.45 | 3.55 |       |

| MC33981ADHFK                                               |                    | 3.35 | 3.45 | 3.63 |       |

| Temperature Feedback Derating <sup>(12)</sup>              | DT <sub>FEED</sub> | -8.5 | -8.9 | -9.3 | mV/°C |

<sup>12.</sup> Parameter is guaranteed by process monitoring but is not production tested.

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

### **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Characteristic                                                                              | Symbol               | Min | Тур  | Max  | Unit |

|---------------------------------------------------------------------------------------------|----------------------|-----|------|------|------|

| CONTROL INTERFACE AND POWER OUTPUT TIMING (CBOOT, VP                                        | WR)                  | l   | l    | l    | 1    |

| Charge Blanking Time (CBOOT) <sup>(14)</sup>                                                | t <sub>ON</sub>      | 10  | 25   | 50   | μs   |

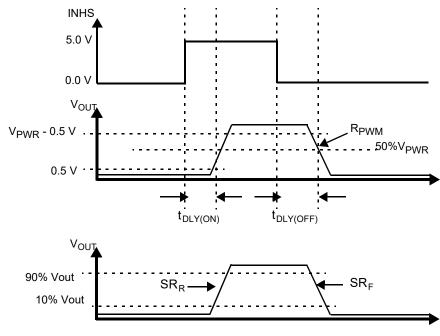

| Output Rising Slew Rate                                                                     | SR <sub>R</sub>      |     |      |      | V/μs |

| $V_{PWR}$ = 13 V, from 10% to 90% of $V_{OUT,}$ SR Capacitor = 4.7 nF, $R_L$ = 5.0 $\Omega$ |                      |     |      |      |      |

| MC33981BHFK and M33981ABHFK                                                                 |                      | 8.0 | 16   | 35   |      |

| MC33981ADHFK                                                                                |                      | 8.0 | 16   | 45   |      |

| Output Falling Slew Rate                                                                    | SR <sub>F</sub>      |     |      |      | V/μs |

| $V_{PWR}$ = 13 V, from 90% to 10% of $V_{OUT,}$ SR Capacitor = 4.7 nF, $R_L$ = 5.0 $\Omega$ |                      |     |      |      |      |

| MC33981BHFK and M33981ABHFK                                                                 |                      | 8.0 | 16   | 35   |      |

| MC33981ADHFK                                                                                |                      | 8.0 | 16   | 45   |      |

| Output Turn-ON Delay Time <sup>(15)</sup>                                                   | t <sub>DLYON</sub>   |     |      |      | ns   |

| V <sub>PWR</sub> = 13 V, SR Capacitor = 4.7 nF                                              |                      |     |      |      |      |

| MC33981BHFK and M33981ABHFK                                                                 |                      | 200 | 400  | 700  |      |

| MC33981ADHFK                                                                                |                      | 200 | 400  | 800  |      |

| Output Turn-OFF Delay Time <sup>(16)</sup>                                                  | t <sub>DLYOFF</sub>  |     |      |      | ns   |

| V <sub>PWR</sub> = 13 V, SR Capacitor = 4.7 nF                                              |                      |     |      |      |      |

| MC33981BHFK and M33981ABHFK                                                                 |                      | 500 | 1000 | 1500 |      |

| MC33981ADHFK                                                                                |                      | 450 | 1000 | 1500 |      |

| Input Switching Frequency <sup>(13)</sup>                                                   | f <sub>PWM</sub>     | -   | 20   | 60   | kHz  |

| Output PWM ratio at 60 kHz <sup>(17)</sup>                                                  | R <sub>PWM</sub>     | 5.0 | -    | 95   | %    |

| Time to Reset Fault Diagnosis                                                               | t <sub>RSTDIAG</sub> |     |      |      | μs   |

| (overload on high side or external low side)                                                |                      | 100 | 200  | 400  |      |

| Output Over-current Detection Time                                                          | t <sub>och</sub>     | 1.0 | 10   | 20   | μs   |

- 13. The MC33981 fully operates down to DC. To reset a latched Fault the INHS pin must go low for the "Time to reset Fault Diagnosis" (trender of the "Time to reset Fault Diagnosis").

- 14. Values for CBOOT=100 nF. Refer to Sleep Mode on page 17. Parameter is guaranteed by design and not production tested.

- 15. Turn-ON delay time measured from rising edge of INHS that turns the output ON to  $V_{OUT}$  = 0.5 V with  $R_L$ = 5.0  $\Omega$  resistive load.

- 16. Turn-OFF delay time measured from falling edge of INHS that turns the output OFF to  $V_{OUT} = V_{PWR}$  -0.5 V with  $R_L = 5.0~\Omega$  resistive load.

- 17. The ratio is measured at  $V_{OUT}$  = 50%  $V_{PWR}$  without SR capacitor. The device is capable of 100% duty cycle.

### **TIMING DIAGRAMS**

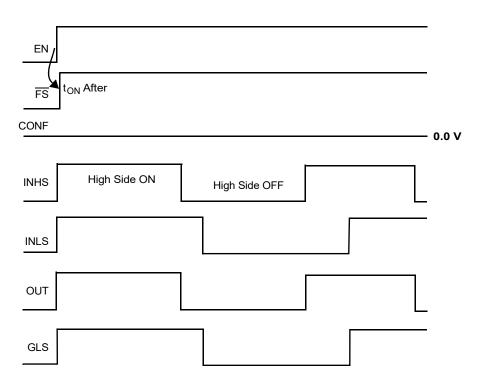

Figure 4. Time Delays Functional Diagrams

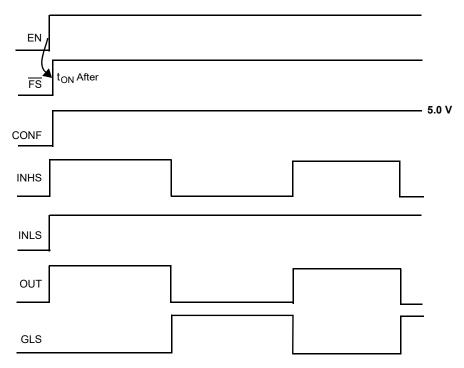

Figure 5. Normal Mode, Cross-Conduction Management

Figure 6. Normal Mode, Independent High Side and Low Side

### **ELECTRICAL PERFORMANCE CURVES**

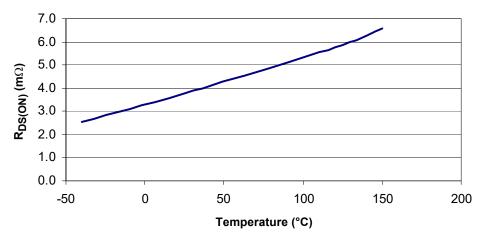

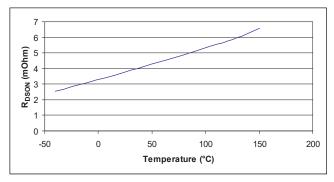

Figure 7. Typical  $R_{DS(ON)}$  vs. Temperature at  $V_{PWR}$  = 13 V

Figure 8. Typical Sleep-state Supply Current vs. VPWR at 150 °C

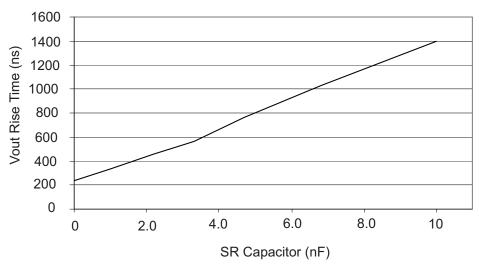

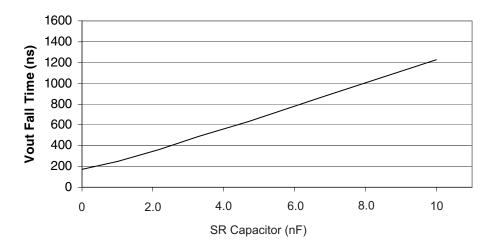

Figure 9.  $V_{OUT}$  Rise Time vs. SR Capacitor From 10% to 90% of  $V_{OUT}$  at 25 °C and  $V_{PWR}$  = 13 V

Figure 10.  $V_{OUT}$  Fall Time vs. SR Capacitor From 10% to 90% of  $V_{OUT}$  at 25 °C and  $V_{PWR}$  = 13 V

### **FUNCTIONAL DESCRIPTION**

### INTRODUCTION

The 33981 is a high-frequency self-protected silicon  $4.0~\text{m}\Omega~\text{R}_{\text{DS(ON)}}$  high side switch used to replace electromechanical relays, fuses, and discrete devices in power management applications. The 33981 can be controlled by pulse-width modulation (PWM) with a frequency up to 60 kHz. It is designed for harsh environments, and it includes self-recovery features.

The 33981 is suitable for loads with high inrush current, as well as motors and all types of resistive and inductive loads. A dedicated parallel input is available for an external low side control with protection features and cross-conduction management.

### **FUNCTIONAL PIN DESCRIPTIONS**

### **OUTPUT CURRENT MONITORING (CSNS)**

This pin is used to output a current proportional to the high side OUT current and is used externally to generate a ground-referenced voltage for the microcontroller (MCU) to monitor OUT current.

### **TEMPERATURE FEEDBACK (TEMP)**

This pin reports an analog value proportional to the temperature of the GND flag (pin 13). It is used by the MCU to monitor board temperature.

### **ENABLE [ACTIVE HIGH] (EN)**

This is an input used to place the device in a low-current Sleep Mode. This pin has an active passive internal pull-down.

### **INPUT HIGH SIDE (INHS)**

The input pin is used to directly control the OUT. This input has an active internal pull-down current source and requires CMOS logic levels.

### FAULT STATUS (FS)

This pin is an open drain-configured output requiring an external pull-up resistor to  $V_{DD}$  (5.0 V) for fault reporting. When a device fault condition is detected, this pin is active LOW.

### **INPUT LOW SIDE (INLS)**

This input pin is used to directly control an external low side N-channel MOSFET and has an active internal pull-down current source and requires CMOS logic levels. It can be controlled independently of the INHS depending of CONF pin.

### **CONFIGURATION INPUT (CONF)**

This input pin is used to manage the cross-conduction between the internal high side N-channel MOSFET and the external low side N-channel MOSFET. The pin has an active internal pull-up current source. When CONF is at 0 V, the

two MOSFETs are controlled independently. When CONF is at  $V_{DD}$  5.0 V, the two MOSFETs cannot be on at the same time.

### **LOW SIDE OVERLOAD (OCLS)**

This pin sets the  $V_{DS}$  protection level of the external low side MOSFET. This pin has an active internal pull-up current source. It must be connected to an external resistor.

### **DRAIN LOW SIDE (DLS)**

This pin is the drain of the external low side N-channel MOSFET. Its monitoring allows protection features: low side short protection and  $V_{\text{PWR}}$  short protection.

### **LOW SIDE GATE (GLS)**

This pin is an output used to drive the gate of the external low side N-channel MOSFET.

### **SLEW RATE CONTROL (SR)**

A capacitor connected between this pin and ground is used to control the output slew rate.

### **BOOTSTRAP CAPACITOR (CBOOT)**

A capacitor connected between this pin and OUT is used to switch the OUT in PWM mode.

### **GROUND (GND)**

This pin is the ground for the logic and analog circuitry of the device.

### **POSITIVE POWER SUPPLY (VPWR)**

This pin connects to the positive power supply and is the source input of operational power for the device. The VPWR pin is a backside surface mount tab of the package.

### **OUTPUT (OUT)**

Protected high side power output to the load. Output pins must be connected in parallel for operation.

### **FUNCTIONAL DEVICE OPERATION**

### **OPERATIONAL MODES**

The 33981 has 2 operating modes: Sleep and Normal depending on EN input.

### **SLEEP MODE**

Sleep Mode is the state of the 33981 when the EN is logic [0]. In this mode, OUT, the gate driver for the external MOSFET, and all unused internal circuitry are off to minimize current draw.

### NORMAL MODE

The 33981 will go to the Normal operating mode when the EN pin is logic [1]. The INHS and INLS commands will be disabled  $t_{\rm ON}$  after the EN transitions to logic [1] to enable the charge of the bootstrap capacitor.

**Table 6. Operating Modes**

| Condition | CONF | INHS | INLS | OUT | GLS     | FS | EN | Comments                                                                                                       |

|-----------|------|------|------|-----|---------|----|----|----------------------------------------------------------------------------------------------------------------|

| Sleep     | х    | х    | х    | х   | х       | Н  | L  | Device is in Sleep Mode. The OUT and low side gate are OFF.                                                    |

| Normal    | L    | Н    | Н    | Н   | Н       | Н  | Н  | Normal mode. High side and low side are controlled independently. The high side and the low side are both on.  |

| Normal    | L    | L    | L    | L   | L       | Н  | Н  | Normal mode. High side and low side are controlled independently. The high side and the low side are both off. |

| Normal    | L    | L    | Н    | L   | Н       | Н  | Н  | Normal mode. Half-bridge configuration. The high side is off and the low side is on.                           |

| Normal    | L    | Н    | L    | Н   | L       | Н  | Н  | Normal mode. Half-bridge configuration. The high side is on and the low side is off.                           |

| Normal    | Н    | PWM  | Н    | PWM | PWM_bar | Н  | Н  | Normal mode. Cross-conduction management is activated. Half-bridge configuration.                              |

H = High level

### PROTECTION AND DIAGNOSTIC FEATURES

### **UNDER-VOLTAGE**

The 33981 incorporates under-voltage protection. In case of  $V_{PWR} < V_{PWR(UV)},$  the OUT is switched OFF until the power supply rises to  $V_{PWR(UV)} + V_{PWR(UVHYS)}.$  The latched fault are reset below  $V_{PWR(UV)}.$  The FS output pin reports the under-voltage fault in real time.

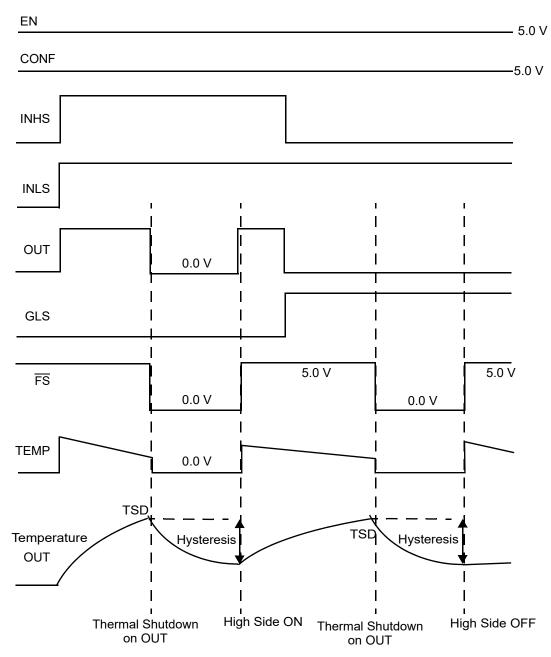

### **OVER-TEMPERATURE FAULT**

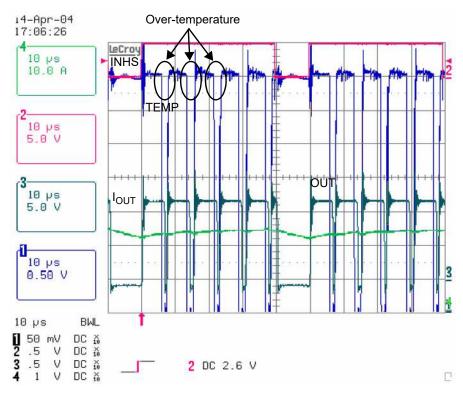

The 33981 incorporates over-temperature detection and shutdown circuitry on OUT. Over-temperature detection also protects the low side gate driver (GLS pin). Over-temperature detection occurs when OUT is in the ON or OFF state and GLS is at high or low level.

For OUT, an over-temperature fault condition results in OUT turning OFF until the temperature falls below  $T_{SD}$ . This cycle will continue indefinitely until the offending load is removed. Figure 12 and Figure 18 show an over-temperature on OUT.

An over-temperature fault on the low side gate drive results in OUT turning OFF and the GLS going to 0V until the

temperature falls below  $T_{SD}$ . This cycle will continue until the offending load is removed. FS pin transition to logic [1] will be disabled typically  $t_{ON}$  after to enable the charge of the bootstrap capacitor.

Over-temperature faults force the TEMP pin to 0 V.

### **OVER-CURRENT FAULT ON HIGH SIDE**

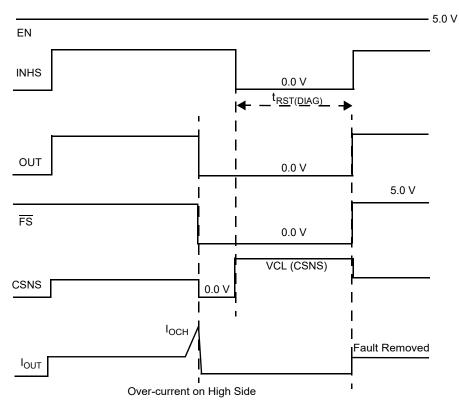

The OUT pin has an over-current high-detection level called I $_{\rm OCH}$  for maximum device protection. If at any time the current reaches this level, OUT will stay OFF and the CSNS pin will go to 0V. The OUT pin is reset (and the fault is delatched) by a logic [0] at the INHS pin for at least  $t_{\rm RST(DIAG)}$ . When INHS goes to 0 V, CSNS goes to 5.0 V.

In <u>Figure 15</u>, the OUT pin is short-circuited to 0V. When the current reaches  $I_{OCH}$ , OUT is turned OFF within  $t_{OCH}$  owing to internal logic circuit.

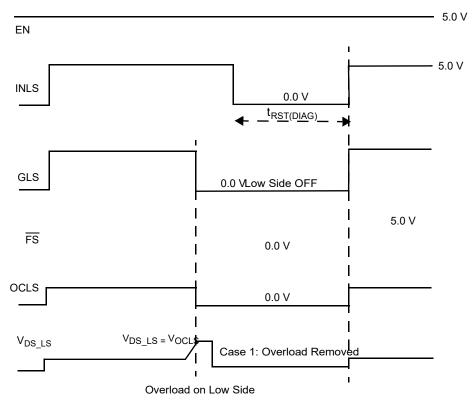

### **OVER-LOAD FAULT ON LOW SIDE**

This fault detection is active when INLS is logic [1]. Low side overload protection does not measure the current

33981

L = Low level

x = Don't care

PWM\_bar = Opposite of pulse-width modulation signal.

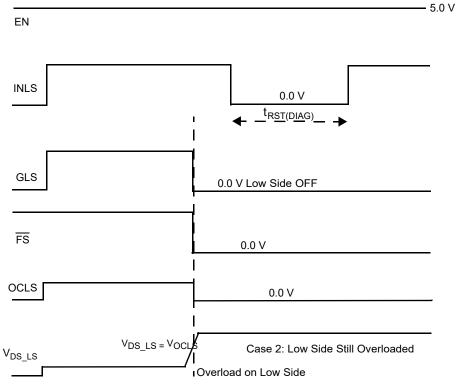

directly but rather its effects on the low side MOSFET. When  $V_{DLS} > V_{OCLS}$ , the GLS pin goes to 0 V and the OCLS internal current source is disconnected and OCLS goes to 0 V. The GLS pin and the OCLS pin are reset (and the fault is delatched) by a logic [0] at the INLS pin for at least  $t_{RST(DIAG)}$ . Figure 13 and Figure 14 illustrate the behavior in case of overload on the low side gate driver.

When connected to an external resistor, the OCLS pin with its internal current source sets the V<sub>OCLS</sub> level. By changing the external resistance, the protection level can be adjusted depending on low side characteristics. A 33 k $\Omega$  resistor gives a V<sub>DS</sub> level of 3.3 V typical.

This protection circuitry measures the voltage between the drain of the low side (DLS pin) and the 33981 ground (GND pin). For this reason it is key that the low side source, the 33981 ground, and the external resistance ground connection are connected together in order to prevent false error detection due to ground shifts.

The maximum OCLS voltage being 4.0 V, a resistor bridge on DLS must be used to detect a higher voltage across the low side.

### **CONFIGURATION**

The CONF pin manages the cross-conduction between the internal MOSFET and the external low side MOSFET. With the CONF pin at 0 V, the two MOSFETs can be independently controlled. A load can be placed between the high side and the low side.

With the CONF pin at 5.0 V, the two MOSFETs cannot be on at the same time. They are in half-bridge configuration as shown in the 33981 Simplified Application Diagram. If INHS and INLS are at 5.0 V at the same time, INHS has priority and OUT will be at  $\rm V_{PWR}.$  If INHS changes from 5.0 V to 0 V with INLS at 5.0 V, GLS will go to high state as soon as the  $\rm V_{GS}$  of the internal MOSFET is lower than 2.0 V typically. A half-bridge application could consist in sending PWM signal to the INHS pin and 5.0 V to the INLS pin with the CONF pin at 5.0 V.

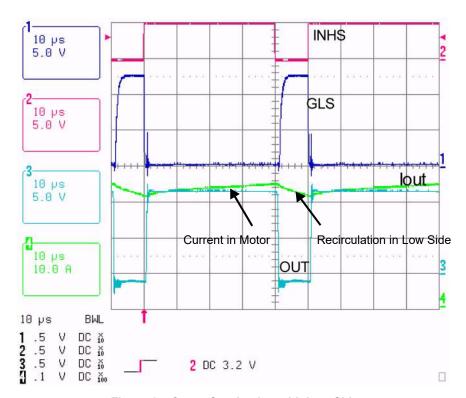

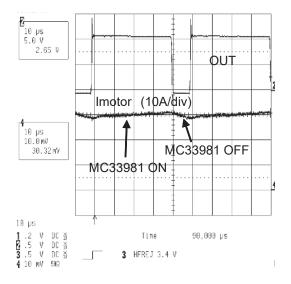

<u>Figure 20</u>, illustrates the simplified application diagram in the 33981 Simplified Application Diagram with a DC motor and external low side. The CONF and INLS pins are at 5.0 V. When INHS is at 5.0 V, current is flowing in the motor. When INHS goes to 0 V, the load current recirculates in the external low side.

### **BOOTSTRAP SUPPLY**

Bootstrap supply provides current to charge the bootstrap capacitor through the VPWR pin. A short time is required after the application of power to the device to charge the bootstrap capacitor. A typical value for this capacitor is 100 nF. An internal charge pump allows continuous MOSFET drive.

When the device is in the sleep mode, this bootstrap supply is off to minimize current consumption.

### **HIGH SIDE GATE DRIVER**

The high side gate driver switches the bootstrap capacitor voltage to the gate of the MOSFET. The driver circuit has a low-impedance drive to ensure that the MOSFET remains OFF in the presence of fast falling dV/dt transients on the OUT pin.

This bootstrap capacitor connected between the power supply and the  $C_{BOOT}$  pin provides the high pulse current to drive the device. The voltage across this capacitor is limited to about 13 V typical.

An external capacitor connected between pins SR and GND is used to control the slew rate at the OUT pin. Figure 9 and Figure 10 give V<sub>OUT</sub> rise and fall time versus different SR capacitors.

### LOW SIDE GATE DRIVER

The low side control circuitry is PWM capable. It can drive a standard MOSFET with an  $R_{DS(ON)}$  as low as 10.0  $\mbox{m}\Omega$  at a frequency up to 60 kHz. The  $\mbox{V}_{GS}$  is internally clamped at 12 V typically to protect the gate of the MOSFET. The GLS pin is protected against short by a local over-temperature sensor.

### THERMAL FEEDBACK

The 33981 has an analog feedback output (TEMP pin) that provides a value in inverse proportion to the temperature of the GND flag (pin 13). The controlling microcontroller can "read" the temperature proportional voltage with its analog-to-digital converter (ADC). This can be used to provide real-time monitoring of the PC board temperature to optimize the motor speed and to protect the whole electronic system. TEMP pin value is  $V_{\mathsf{TFEED}}$  with a negative temperature coefficient of  $\mathsf{DT}_{\mathsf{FFED}}$ .

### **REVERSE BATTERY**

The 33981 survives the application of reverse battery voltage as low as -16 V. Under these conditions, the output's gate is enhanced to decrease device power dissipation. No additional passive components are required. The 33981 survives these conditions until the maximum junction rating is reached.

In the case of reverse battery in a half-bridge application, a direct current passes through the external freewheeling diode and the internal high side.

As <u>Figure 11</u> shows, it is essential to protect this power line. The proposed solution is an external N-channel low side with its gate tied to battery voltage through a resistor. A high side in the  $V_{PWR}$  line could be another solution.

Figure 11. Reverse Battery Protection

### **GROUND (GND) DISCONNECT PROTECTION**

If the DC motor module ground is disconnected from load ground, the device protects itself and safely turns OFF the output regardless of the output state at the time of disconnection. A 10 k resistor needs to be added between the EN pin and the rest of the circuitry in order to ensure the device turns off in case of ground disconnect and to prevent exceeding this pin's maximum ratings.

### **FAULT REPORTING**

This  $339\underline{81}$  indicates the faults below as they occur by driving the  $\overline{FS}$  pin to logic [0]:

- · Over-temperature fault

- · Over-current fault on OUT

- · Overload fault on the external low side MOSFET

The  $\overline{\text{FS}}$  pin will return to logic [1] when the over temperature fault condition is removed. The two other faults are latched.

Table 7. Functional Truth Table in Fault Mode

| Conditions                                 | CONF | INHS | INLS | OUT | GLS | FS | EN | TEMP | CSNS | ocls | Comments                                                                                                                                                                                                                                                       |

|--------------------------------------------|------|------|------|-----|-----|----|----|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Over-temperature on OUT                    | х    | х    | х    | L   | Н   | L  | Н  | L    | х    | х    | The 33981 is currently in Fault mode. The OUT is OFF. TEMP at 0V indicates this fault. Once the fault is removed 33981 recovers its normal mode.                                                                                                               |

| Over-temperature on GLS                    | х    | х    | х    | L   | L   | L  | Н  | L    | х    | х    | The 33981 is currently in Fault mode. The OUT is OFF and GLS is at 0V. TEMP at 0V indicates this fault. Once the fault is removed 33981 recovers its Normal Mode.                                                                                              |

| Over-current<br>on OUT                     | х    | Н    | L    | L   | х   | L  | Н  | х    | L    | х    | The 33981 is currently in Fault mode. The OUT is OFF. It is reset by a logic [0] at INHS for at least t <sub>RST(DIAG)</sub> . When INHS goes to 0V, CSNS goes to 5.0 V.                                                                                       |

| Overload<br>on External Low<br>Side MOSFET | L    | L    | Н    | х   | L   | L  | Н  | х    | х    | L    | The 33981 is currently in Fault mode. GLS is at 0 V and OCLS internal current source is off. The external resistance connected between OCLS and GND pin will pull OCLS pin to 0V. The fault is reset by a logic [0] at INLS for at least $t_{\rm RST(DIAG)}$ . |

H = High level L = Low level

x = Don't care

Figure 12. Over-temperature on Output

Figure 13. Overload on Low Side Gate Drive, Case 1

Figure 14. Overload on Low Side Gate Drive, Case 2

Figure 15. Over-current on Output

Figure 16. High Side Over-current

Figure 17. Cross-Conduction with Low Side

Figure 18. Over-temperature on OUT

Figure 19. Maximum Operating Frequency for SR Capacitor of 4.7 nF

### TYPICAL APPLICATIONS

### INTRODUCTION

<u>Figure 20</u> shows a typical application for the 33981. A brush DC motor is connected to the output. A low side gate driver is used for the freewheeling phase. Typical values for external capacitors and resistors are given.

Figure 20. 33981 Typical Application Diagram

### **EMC AND EMI RECOMMENDATIONS**

### INTRODUCTION

This section relates the EMC capability for 33981, high frequency high-current high side switch. This device is a self-protected silicon switch used to replace electromechanical relays, fuses, and discrete circuits in power management applications.

This section presents the key features of the device and its targeted applications. The automotive standard to measure conducted and radiated emissions is provided. Concrete measurements on the 33981 and improvements to reduce electromagnetic emission are described.

### **DEVICE FEATURES**

This 33981 is a 4.0 m $\Omega$  self-protected, high side switch digitally controlled from a microcontroller (MCU) with extended diagnostics, able to drive DC motors up to 60 kHz.

A bootstrap architecture has been used to provide fast transient gate voltage in order to reach 4.0 m $\Omega$  R<sub>DS(ON)</sub> maximum at room temperature. In parallel, a charge pump is implemented to offer continuous on-state capability. This dual current supply of the high side MOSFET allows a duty cycle from 5% to 100%. An external capacitor connected between pins SR and GND is used to control the slew rate at

the output and, therefore, reduce electromagnetic perturbations.

In standard configuration, the motor current recirculation is handled by an external freewheeling diode. To reduce global power dissipation, the freewheeling diode can be replaced by an external discrete MOSFET in low side configuration. The IC integrates a gate driver that controls and protects this external MOSFET in the event of short-circuit to battery. The product manages the cross conduction between the internal high side and the external low side when used in a half-bridge configuration. The two MOSFETs can be controlled independently when the CONF pin is at 0 V. To eliminates fuses, the device is self-protected from severe short-circuits (100 A typical) with an innovative over-current strategy.

The 33981 has a current feedback for real-time monitoring of the load current through an MCU analog/digital converter to facilitate closed-loop operation for motor speed control.

The 33981 has an analog thermal feedback that can be used by the MCU to monitor PC board temperature to optimize the motor control and to protect the entire electronic system. Therefore, an over-temperature shutdown feature protects the IC against high overload condition.

Figure 21 illustrates the typical application diagram.

Figure 21. Typical Application Diagram

### **APPLICATION**

Engine cooling, air conditioning, and fuel pump are the targeted automotive applications for the 33981. Conventional solutions are designed with discrete components that are not optimized in terms of component board size, protection, and diagnostics. The 33981 is the right candidate to develop lighter and more compact units.

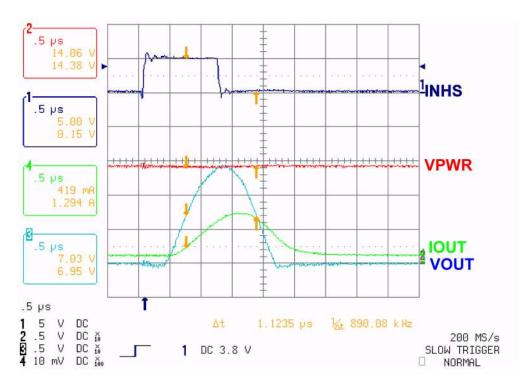

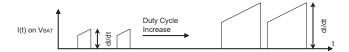

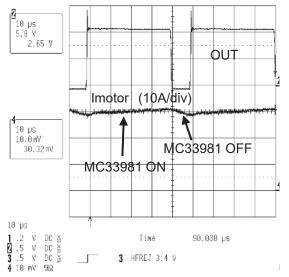

DC motor speed adjustment allows optimization of energy consumption by reducing supply voltage, hence the mean voltage applied to the motor. The commonly used control technique is pulse wide modulation (PWM) where the average voltage is proportional to the duty cycle. Most applications require a PWM frequency of at least 20 kHz to avoid audible noise. Figure 22 illustrates typical waveforms when switching the 33981 at 20 kHz with a duty cycle of 80%. The output voltage (OUT) and current in the motor (I<sub>MOTOR</sub>) waveforms are represented.

Figure 22. Current and Voltage waveforms

# HOW TO MEASURE ELECTROMAGNETIC EMISSION ACCORDING TO THE CISPR25

One EMC standard in the automotive world (at system level) is the CISPR25, edited by the International Electrotechnical Commission. This standard describes the measurement method to measure both conducted and radiated emission.

### CONDUCTED EMISSION MEASUREMENT

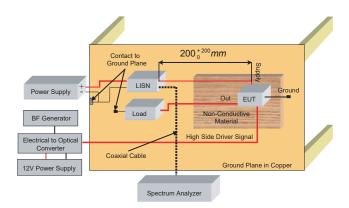

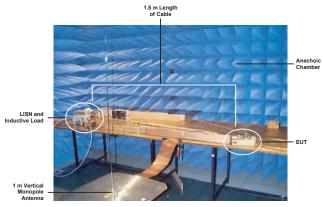

Conducted emission is the emission produced by the device on the battery cable. The test bench is described by CISPR25 (see Figure 23).

The Line Impedance Stabilization Network (LISN), also called artificial network (AN), in a given frequency range (150 kHz to 108 MHz), provides a specified load impedance for the measurement of disturbance voltages and isolates the equipment under test (EUT) from the supply in that frequency range.

Figure 23. Test Bench for Conducted Emission

The EUT must operate under typical loading and other conditions just as it must in the vehicle so maximum emission state occurs. These operating conditions must be clearly defined in the test plan to ensure that both supplier and customer are performing identical tests.

For the testing described in this application note, the out pin of the 33981 was connected to an inductive load (0.47  $\Omega$  + 1.0  $\mu H)$  switching at 20 kHz with a duty cycle of 80%. The output current was 17 A continuous.

The ground return of the EUT to the chassis must be as short as possible. The power supply is 13.5 V.

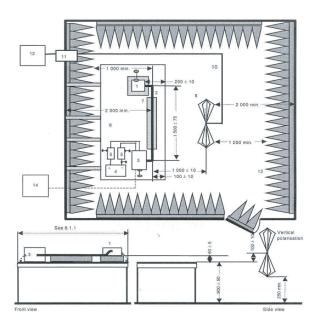

### RADIATED EMISSION MEASUREMENT

The radiated emission measurement consists of measuring the electromagnetic radiation produced by the equipment under test. CISPR 25 gives the schematic test bench described in Figure .

To measure radiated emission over all frequency ranges, several antenna types must be used:

- 0.15 MHz to 30 MHz: 1.0 m vertical monopole in vertical polarization.

- 30 MHz to 200 MHz: a biconical antenna used in vertical and horizontal polarization.

- 200 MHz to 1,000 MHz: a log-periodic antenna used in vertical and horizontal polarization.

### Key

- 1 EUT (grounded locally if required in test plan)

- 2 Test harness

- 3 Load simulator (placement and ground connection)

- 4 Power supply (location optional)

- 5 Artificial Network (AN)

- 6 Ground plane (bonded to shielded enclosure)

- 7 Low relative permittivity support  $(\epsilon \rho \le 1.4)$

- 8 Biconical antenna

- 10 High quality doubleshielded coaxial cab

- shielded coaxial cable  $(50 \Omega)$

- 11 Bulkhead connector

- 12 Measuring instrument

- 13 RF absorber material

- 14 Stimulation and monitoring system

Figure 24. Test Bench for Radiated Emission

### **EMC RESULTS AND IMPROVEMENTS**

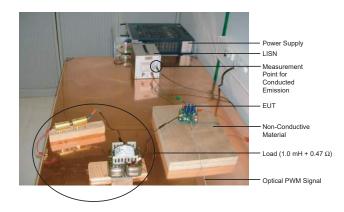

The 33981 OUT is connected to an inductive load (0.47  $\Omega$  + 1.0mH) switching at 20 kHz with duty = 80%. The current in the load was 17 A continuous.

### **BOARD SETUP**

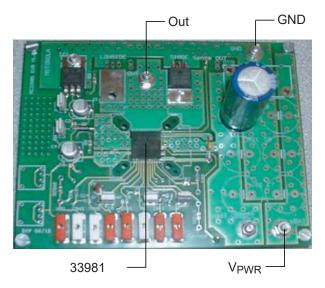

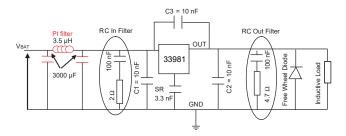

The initial configuration of our 33981 board is represented in Figure 25.

No SR capacitor is used. Therefore, the obtained switching times are the maximum values. A capacitor of 1000  $\mu F$  is connected between VPWR and GND.

Figure 25. 33981 Initial Configuration

### **CONDUCTED MEASUREMENTS**

### **TEST SETUP**

To perform a conducted emission measurement in accordance with the CISPR 25 standard, the test bench in <u>Figure 26</u> was developed.

Figure 26. Conducted Emission Test Setup

### **EFFECTS OF SOME PARAMETERS**

The conducted emissions level rise with the duty cycle. When the duty increases the di/dt on the VPWR line is higher. The device has to deliver more current and provide more energy. Figure 27 describes the effect of duty cycle increase on the  $V_{PWR}$  current waveform. The conducted emission level rises with the output frequency. This is due to the increasing number of commutations.

Figure 27. VPWR Current

### **HOW TO REDUCE ELECTROMAGNETIC EMISSION**

By adjusting the slew rate of the device during turn ON and turn OFF with SR capacitor, the electromagnetic emissions can be reduced.

Conductive emission tests were performed (taking care of the board filtering and routing that have a big impact on EMC performances).

An optimized solution was found by adding the following external components to the initial board:

- PI filter on the  $V_{PWR}\!:2~x~3~\mu F$  and  $3.5\mu H$

- RC IN filter between  $V_{PWR}$  and GND: a 2.0  $\Omega$  resistor in series with a 100 nF capacitor

- RC Out filter between OUT and GND: a 4.7 Ω resistor in series with a 100 nF capacitor

- Capacitor C1 of 10 nF between V<sub>PWR</sub> and GND

- Capacitor C2 of 10 nF between OUT and GND

- Capacitor C3 of 10 nF between OUT and V<sub>PWR</sub>

- · Capacitor SR of 3.3 nF

Figure 28. 33981 with Filter

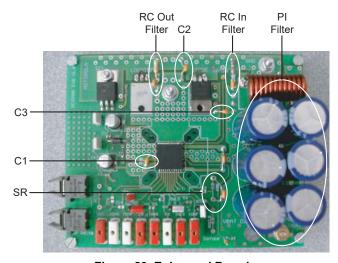

The EMC enhanced board with adapted value filter is represented in <u>Figure 29</u>.

Figure 29. Enhanced Board

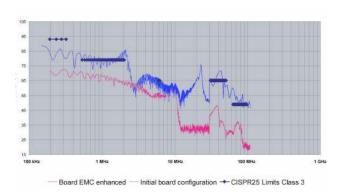

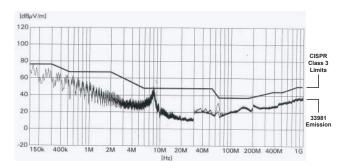

The chart in Figure 30 shows the spectrum of the enhanced board and the initial board. The improvement is appreciatively 15 dB to 20 dB in the all frequency range. The enhanced board is now in accordance with the Class 3 limits of the CISPR25 standard for conducted emission.

Figure 30. Conducted Emission Spectrum for 33981

### RADIATED MEASUREMENTS

This test was performed in order to evaluate the characteristic of the device relating to radiated emission. Measurements have been done in accordance with the CISPR 25 standard as shown in Figure 31. The tested board was the EMC enhanced board.

Figure 31. Radiated Emission Test Set-up

The results of these measurements are represented in Figure 32. The enhanced board is in accordance with the Class 3 limits of the CISPR25 standard for radiated emission.

Figure 32. Radiated Emission Spectrum for 33981

### CONCLUSION

This document explains how to measure conducted and radiated emission in accordance with the automotive CISPR25 standard. Measurements were performed on the 33981 in real application conditions, when driving an inductive load. An optimized filtering solution was put in place to have the tested system in accordance with the Class 3 limits. The same method can be used with other PC boards.

### **POWER DISSIPATION**

### INTRODUCTION

This section relates to the power dissipation capability for 33981, high frequency high-current high side switch. This device is a self-protected silicon switch used to replace electromechanical relays, fuses, and discrete circuits in power management applications.

This section presents the key features of the device and its targeted applications. The theoretical calculations for power dissipation and die junction temperatures are determined in this document for inductive loads. A concrete example with DC motor driven by the 33981 is analyzed in DC Motor 200W.

### **DEVICE FEATURES**

This 33981 is a 4.0 m $\Omega$  self-protected, high side switch digitally controlled from a microcontroller (MCU) with extended diagnostics, able to drive DC motors up to 60 kHz.

A bootstrap architecture has been used to provide fast transient gate voltage in order to reach 4.0 m $\Omega$   $R_{DS(ON)}$  maximum at room temperature. In parallel, a charge pump is implemented to offer continuous on-state capability. This dual current supply of the high side MOSFET allows a duty cycle from 5% to 100%. An external capacitor connected between pins SR and GND is used to control the slew rate at the output and, therefore, reduce electromagnetic perturbations.

In standard configuration, the motor current recirculation is handled by an external freewheeling diode. To reduce global power dissipation, the freewheeling diode can be replaced by an external discrete MOSFET in low side configuration. The IC integrates a gate driver that controls and protects this external MOSFET in the event of short-circuit to battery. The

product manages the cross conduction between the internal high side and the external low side when used in a half-bridge configuration. The two MOSFETs can be controlled independently when the CONF pin is at 0 V. To eliminates fuses, the device is self-protected from severe short-circuits (100 A typical) with an innovative over-current strategy.

The 33981 has a current feedback for real-time monitoring of the load current through an MCU analog/digital converter to facilitate closed-loop operation for motor speed control.

The 33981 has an analog thermal feedback that can be used by the MCU to monitor PC board temperature to optimize the motor control and to protect the entire electronic system. Therefore, an over-temperature shutdown feature protects the IC against high overload condition.

Figure 33 illustrates the typical application diagram.

Figure 33. Typical Application Diagram

### **APPLICATION**

Engine cooling, air conditioning, and fuel pump are the targeted automotive applications for the 33981. Conventional solutions are designed with discrete components that are not optimized in terms of component board size, protection, and diagnostics. The 33981 is the right candidate to develop lighter and more compact units.

The adjustment of the DC motor speed allows optimizing of energy consumption. It is realized by chopping the supply voltage, hence the mean voltage, applied to the motor. The commonly used control technique is pulse wide modulation (PWM) where the average voltage is proportional to the duty cycle. Most applications require a PWM frequency of at least 20 kHz to avoid audible noise. Figure 34 illustrates typical waveforms when switching the 33981 at 20 kHz with a duty cycle of 80%. The output voltage (OUT) and current in the motor ( $I_{\rm MOTOR}$ ) waveforms are represented.

Figure 34. Current and Voltage waveforms

### POWER DISSIPATION

The 33981 power dissipation is the sum of two kinds of losses:

- · On-State losses when device is fully ON,

- Switching losses when the device switches ON and OFF.

The analysis that follows assumes an inductive load and assumes that the current is constant in the load.

The case being considered in this paper is inductive load and the hypothesis is that the current is constant in the load.

### ON-STATE LOSSES

The mean on-state loss periods in the 33981 can be calculated as follows:

Pon\_state =  $a \cdot R_{DS(ON)} \cdot I_{OUT}^2$  where 'a' is the duty cycle.

The critical parameter is the on resistance ( $R_{DS(ON)}$ ) that increases with temperature. The 33981 has a maximum  $R_{DS(ON)}$  at 25 °C of 4.0 m $\Omega$  and its deviation with temperature is only 1.7 as shown in Figure 35.

Figure 35. R<sub>DS(ON)</sub> vs. Temperature

### SWITCHING LOSSES

The mean switching losses in the 33981 can be calculated as follows:

Pswitching =  $(t_{ON} . F_{REQ} . V_{PWR} . I_{OUT}) / 2 + (t_{OFF} . F_{REQ} . V_{PWR} . I_{OUT}) / 2$

where  $t_{ON}/t_{OFF}$  is the turn on/off time.

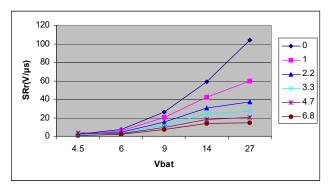

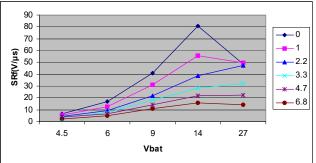

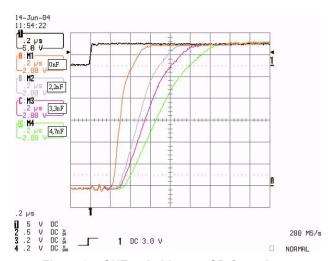

The switching time is a critical parameter. The 33981 provides adjustable slew rates through an external capacitor (SR) that slow down the rise and fall times to reduce the electromagnetic emissions. However, this adjustment will have an impact on power dissipation. Figure 36 gives the positive (SR<sub>R</sub>) and negative (SR<sub>F</sub>) slew rate versus different values of SR. This is illustrated in Figure 37.

Figure 36. Positive and Negative Slew Rate vs. SR Capacitor

Figure 37. OUT switching vs. SR Capacitor

### JUNCTION TEMPERATURE

The junction temperature of the 33981 can be calculated knowing the power dissipation and the thermal characteristics of the PC board with this formula:

$T_J = T_A + (Pon\_state + Pswitching). \ R_{THJA}$  where  $T_J$  is the junction temperature,  $T_A$  the ambient temperature, and  $R_{THJA}$  the thermal impedance junction to ambient.

### **RECIRCULATION PHASE**

In standard configuration, the motor current recirculation is handled by an external freewheeling diode. With the 33981, the freewheeling diode can be replaced by an external low-side discrete MOSFET.

The power dissipation during the recirculation phase is calculated as follows for the diode and the low-side MOSFET respectively:

where 'a' is the duty cycle

Pmosfet\_ls =

$$(1-a)$$

.  $R_{DS(ON)_ls}$  .  $I_{OUT}^2$

where  $R_{DS(ON)\_ls}$  is the on resistance of the low side.

### **APPLICATIONS EXAMPLES**

### **EXCEL TOOL**

An excel tool has been created with all the above formulas to calculate the dissipated power and the junction temperature knowing the application conditions. An example of the interface is given in Figure 38. The parameters to enter concern the load, the high side device, the recirculation, and the board. They are  $V_{PWR},\,DC$  current in the load (Imax for 100% of duty cycle), PWM frequency, 33981  $R_{DS(ON)}$  at 150 °C, SR capacitor, low side  $R_{DS(ON)}$  at 150 °C, ambient temperature, and thermal impedance.

| INPUTS                   |                             |          |  |  |  |  |  |

|--------------------------|-----------------------------|----------|--|--|--|--|--|

|                          | Vpwr                        | 12 V     |  |  |  |  |  |

| Load                     | Imax                        | 20 A     |  |  |  |  |  |

|                          | Frequency                   | 20 KHz   |  |  |  |  |  |

| High Side<br>Device (HS) | R <sub>DSON</sub><br>@150°C | 6.8 mOhm |  |  |  |  |  |

|                          | SR<br>Capacitor             | 0 nF     |  |  |  |  |  |

|                          | Low Side Characteristics    |          |  |  |  |  |  |

| Recirculation            | R <sub>DSON</sub><br>@150°C | 20 mOhm  |  |  |  |  |  |

| Board                    | Rthja                       | 15°C/W   |  |  |  |  |  |

|                          | T ambiant                   | 85°C     |  |  |  |  |  |

Figure 38. Excel Tool

The calculations are done with the maximum  $R_{DS(ON)}$  for the 33981 and the low side. The current is also considered constant in the load. The model taken for the  $V_F$  of the diode is  $(0.4\,+\,0.01$ .  $I_{OUT})$  Volts.

The listed conditions in Figure 38 are the ones chosen for the entire document.

### DC MOTOR 200W

A concrete example is the 33981. A 200 W DC motor, a frequency of 20 kHz, and an ambient temperature of 85  $^{\circ}$ C are chosen. The 33981 is evaluated using the following board. The thermal impedance of the board is in the range of 15  $^{\circ}$ C/W.

Figure 39. 33981 Evaluation Board

### **POWER DISSIPATION**

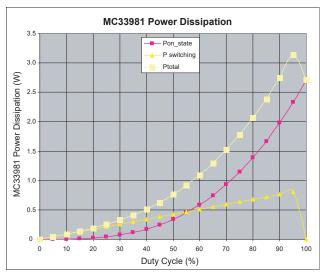

<u>Figure 40</u> illustrates the power dissipation in the 33981. The conditions are listed in <u>Figure 38</u>. Maximum power dissipation of 3.1 W is obtained with a duty of 95%.

Figure 40. Power Dissipation (Pon and Pswitching) vs.

Duty Cycle

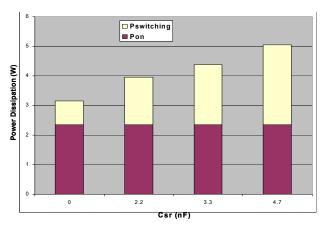

### INFLUENCE OF SR CAPACITOR

The SR capacitor value has an impact on these switching losses. Figure 41 illustrates the percentage of the switching losses versus the total power dissipation for the same load conditions as Figure 38. The higher the SR capacitor value, the higher the switching losses. They can be more than 50% of the total power dissipation in the 33981 with a 4.7 nF capacitor and is a basic applications trade-off. A compromise should be found between the power dissipation and the electromagnetic capability (EMC) performance.

Figure 41. Power Switching vs. SR Capacitor

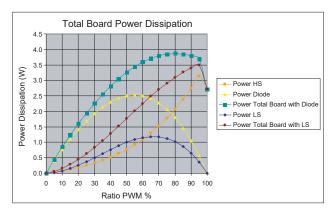

### **RECIRCULATION PHASE**

<u>Figure 42</u> illustrates the power dissipation for the two recirculation approaches, diode or low side MOSFET. The power dissipation gain for the entire system when using the low side instead of the diode can reach up to 1.5 W with a duty cycle of 50%.

Figure 42. Total Board Power Dissipation

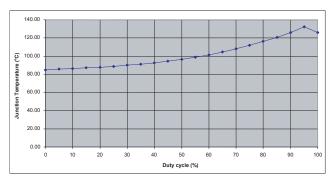

### **JUNCTION TEMPERATURE**

The junction temperature of the 33981 versus duty cycle for the condition listed in <u>Figure 38</u>, is given in <u>Figure 43</u>. The maximum obtained junction temperature is 132 °C with a duty cycle of 95%. This value is far from the 150°C maximum guaranteed junction.

Figure 43. Junction Temperature vs. Duty Cycle

### **CONCLUSION**

Knowing the application conditions, this document explained how to calculate power dissipation during on-state and switching phases and the junction temperature for the 33981 when controlling a DC motor. A concrete example with a 200 W DC motor was given in DC Motor 200W. The same principle can be used for other DC motors and other environmental conditions.

### **PACKAGING**

### **SOLDERING INFORMATION**

The 33981 is packaged in a surface mount power package (PQFN), intended to be soldered directly on the printed circuit board. The AN2467 provides guidelines for Printed Circuit Board design and assembly.

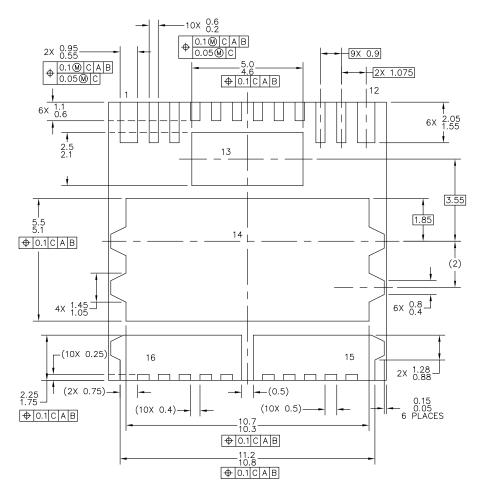

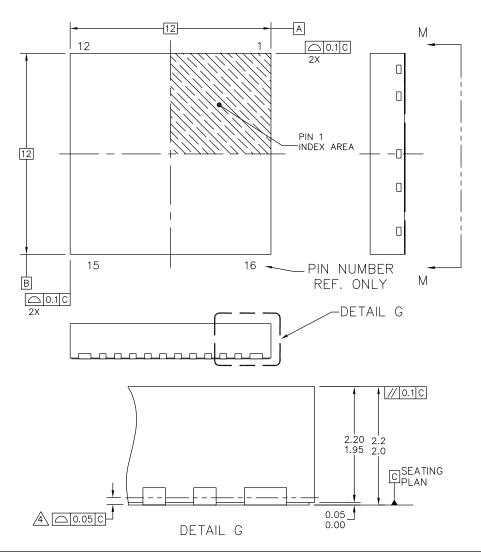

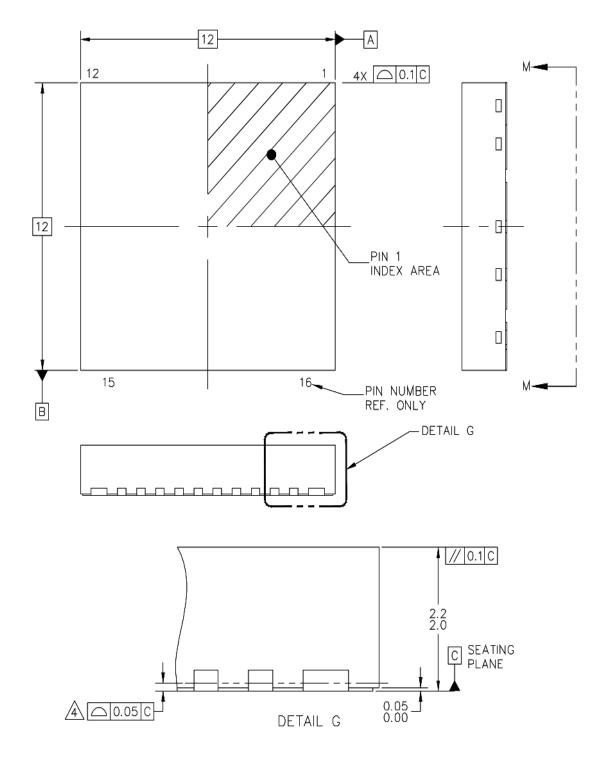

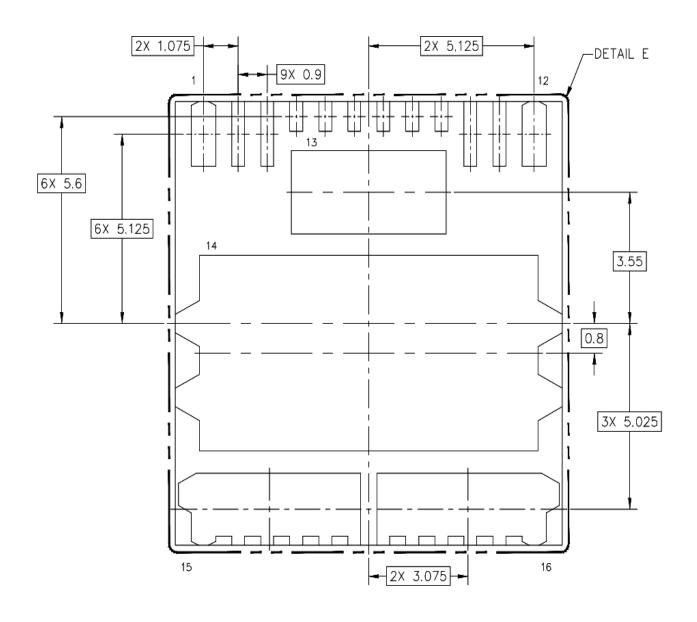

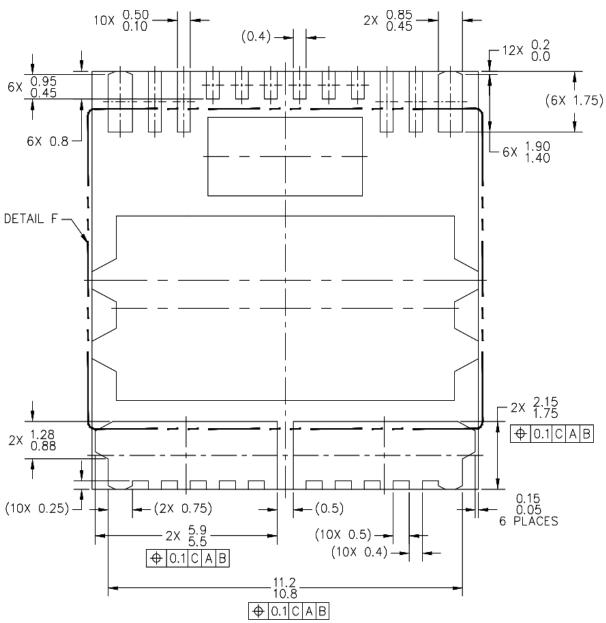

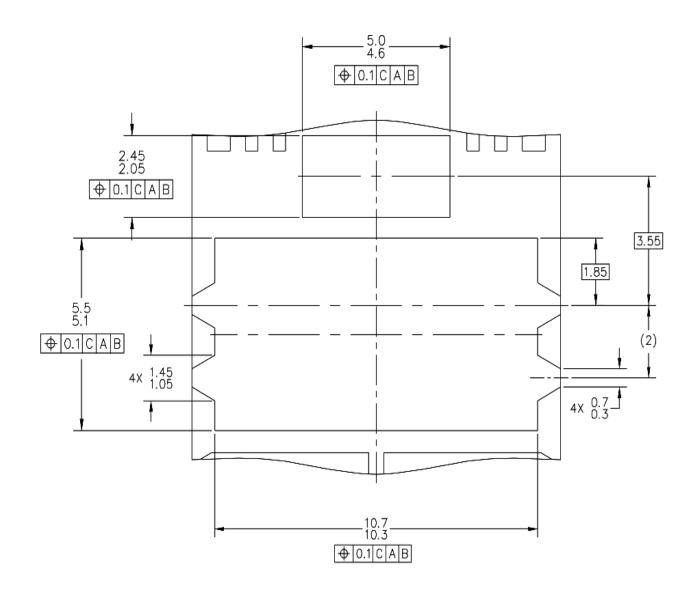

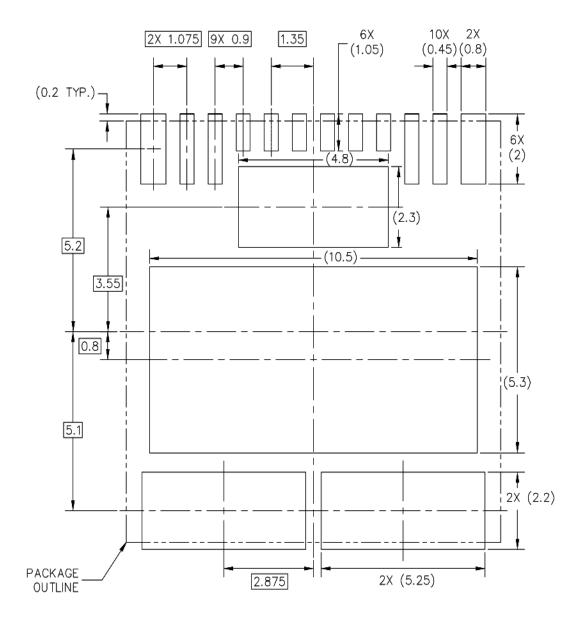

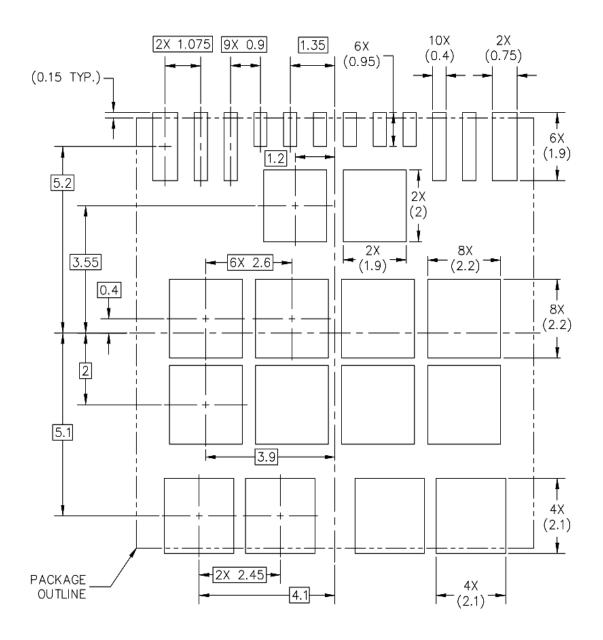

### **PACKAGING DIMENSIONS**

For the most current package revision, visit <u>www.nxp.com</u> and perform a keyword search using "98ARL10521D" and "98ASA00815D". Dimensions shown are provided for reference ONLY.

Table 8. Part keywords

| Suffix         | Package outline drawing number |

|----------------|--------------------------------|

| BHFK AND ABHFK | 98ARL10521D                    |

| ADHFK          | 98ASA00815D                    |

$VIEW\ M-M$

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                | PRINT VERSION NOT TO SCALE |        |  |  |

|------------------------------------------------------|-----------|--------------------------|----------------------------|--------|--|--|

| TITLE: POWER QUAD FLA                                | Т         | DOCUMENT NO: 98ARL10521D |                            | REV: C |  |  |

| NON-LEADED PACKAGE (F                                | PWR QFN)  | CASE NUMBER              | 27 APR 2005                |        |  |  |

| 16 TERMINAL, 0.9 PITCH(1                             | 2X12X2.1) | STANDARD: NON-JEDEC      |                            |        |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICA |           | L OUTLINE    | PRINT VERSION NO | T TO SCALE |

|-----------------------------------------------------------------|-----------|--------------|------------------|------------|

| TITLE: POWER QUAD FLA                                           | T         | DOCUMENT NO  | ): 98ARL10521D   | REV: C     |

| NON-LEADED PACKAGE (F                                           |           |              | 27 APR 2005      |            |

| 16 TERMINAL, 0.9 PITCH(1                                        | 2X12X2.1) | STANDARD: NO | N-JEDEC          |            |

| © NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED   | MECHANICAL OUTL | LINE     | PRINT VERSION N   | OT TO SC | ALE  |

|----------------------------------------------------|-----------------|----------|-------------------|----------|------|

| PQFN, 12 X 12 X 2.1 PKG,<br>0.9 PITCH, 16 TERMINAL |                 | DOCUMENT | Г NO: 98ASA00815D | RE       | V: B |

|                                                    |                 | STANDARD | : NON-JEDEC       |          |      |

|                                                    |                 | S0T1630- | 2                 | 22 MAY   | 2018 |

VIEW M-M

| 0      | NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE    | PRINT VERSION NO   | T TO SCALE  |

|--------|------------------------------------------------|---------------|----------|--------------------|-------------|

| TITLE: | PQFN. 12 X 12 X 2.1 PKG.                       |               | DOCUMEN  | NT NO: 98ASA00815D | REV: B      |

|        |                                                |               | STANDAR  | D: NON-JEDEC       |             |

|        | 0.0 111011, 10 121                             |               | S0T1630- | -2                 | 22 MAY 2018 |

UNLESS OTHERWISE SPECIFIED POSITIONAL TOLERANCE FOR ALL LEADS SHALL BE AS FOLLOWS

0.1 M C A B 0.05 M C

DETAIL E

| ©      | NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED     | MECHANICAL OU | TLINE   | PRINT VERSION     | NOT TO SCALE | =  |

|--------|----------------------------------------------------|---------------|---------|-------------------|--------------|----|

| TITLE: | DOEN 10 V 10 V 0                                   | I             |         | NT NO: 98ASA00815 | D REV:       | В  |

|        | PQFN, 12 X 12 X 2.1 PKG,<br>0.9 PITCH. 16 TERMINAL |               | STANDAR | D: NON-JEDEC      |              |    |

|        | 0.0 111011, 10 121                                 | (WIII V/ \C   | S0T1630 | -2                | 22 MAY 20    | 18 |

DETAIL F

| © N    | IXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED | MECHANICAL OU | TLINE    | PRINT VERSION NO   | OT TO SCALE |

|--------|------------------------------------------------|---------------|----------|--------------------|-------------|

| TITLE: | POFN. 12 X 12 X 2.1 PKG.                       |               | DOCUMEN  | IT NO: 98ASA00815D | REV: B      |

|        |                                                |               | STANDAR  | D: NON-JEDEC       |             |

|        | 0.5 111011, 10 1210                            | WIII 47 (C    | S0T1630- | -2                 | 22 MAY 2018 |

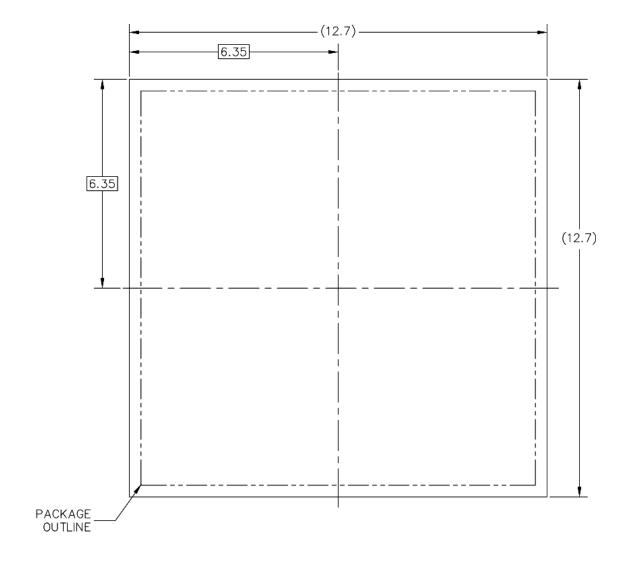

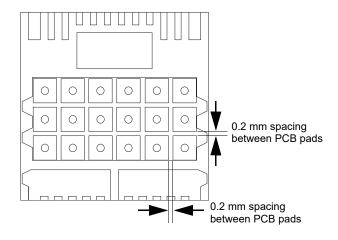

# PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN 1

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL / SPECIFIC REQUIREMENTS.

| NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED        | MECHANICAL OU | TLINE   | PRINT VERSION NOT  | TO SCALE |

|----------------------------------------------------|---------------|---------|--------------------|----------|

| PQFN, 12 X 12 X 2.1 PKG,<br>0.9 PITCH, 16 TERMINAL |               | DOCUMEN | NT NO: 98ASA00815D | REV: B   |

|                                                    |               | STANDAR | RD: NON-JEDEC      |          |

|                                                    |               | SOT1630 | -2 22              | MAY 2018 |

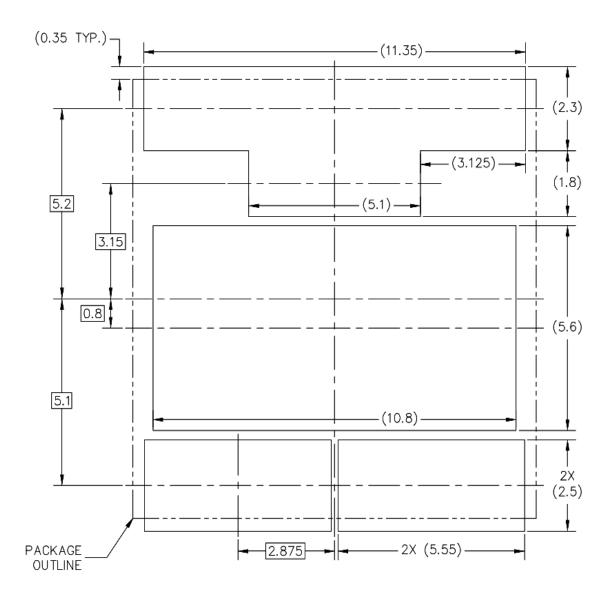

# PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN 2

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL / SPECIFIC REQUIREMENTS.

| © NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED | MECHANICAL OU                                      | TLINE   | PRINT VERSION NOT  | TO SCALE    |

|--------------------------------------------------|----------------------------------------------------|---------|--------------------|-------------|

|                                                  |                                                    | DOCUMEN | NT NO: 98ASA00815D | REV: B      |

|                                                  | PQFN, 12 X 12 X 2.1 PKG,<br>0.9 PITCH, 16 TERMINAL |         | RD: NON-JEDEC      |             |

| 0.5 111011, 10                                   | TEI (WIII TY VE                                    | S0T1630 | -2 2               | 22 MAY 2018 |

PCB CU GUIDELINES - I/O PADS & SOLDERABLE AREAS

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL / SPECIFIC REQUIREMENTS.

| NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED        | MECHANICAL OU  | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|----------------------------------------------------|----------------|---------|--------------------|-------------|

| TITLE:                                             |                |         | NT NO: 98ASA00815D | REV: B      |

| PQFN, 12 X 12 X 2.1 PKG,<br>0.9 PITCH, 16 TERMINAL |                | STANDAR | RD: NON-JEDEC      |             |

| 0.0 111011, 10 12                                  | 1 (IIII) 47 (C | S0T1630 | -2                 | 22 MAY 2018 |

# SOLDER PASTE STENCIL GUIDELINES

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL / SPECIFIC REQUIREMENTS.

| NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED | MECHANICAL OUT                                     | LINE     | PRINT     | VERSION NOT | TO SC | ALE |   |

|---------------------------------------------|----------------------------------------------------|----------|-----------|-------------|-------|-----|---|

|                                             |                                                    | DOCUMEN  | T NO: 98  | ASA00815D   | RE'   | V:  | В |

|                                             | PQFN, 12 X 12 X 2.1 PKG,<br>0.9 PITCH. 16 TERMINAL |          | D: NON-JE | EDEC        |       |     |   |

| 0.0 111011, 10 1210                         |                                                    | SOT1630- | -2        | 2.          | 2 MAY | 201 | 8 |

# NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS NON-JEDEC REGISTERED PACKAGE.

- 4. COPLANARITY APPLIES TO LEADS AND CORNER LEADS.

- 5. MINIMUM METAL GAP IS GUARANTEED TO BE 0.25 MM.

| NXP SEMICONDUCTORS N.V. ALL RIGHTS RESERVED | MECHANICAL OUT | LINE     | PRINT VERSION NOT | TO SCALE   |

|---------------------------------------------|----------------|----------|-------------------|------------|