www.ti.com

# PROGRAMMABLE 27-BIT SERIAL-TO-PARALLEL RECEIVER

#### **FEATURES**

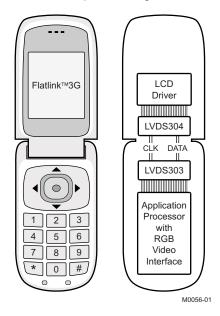

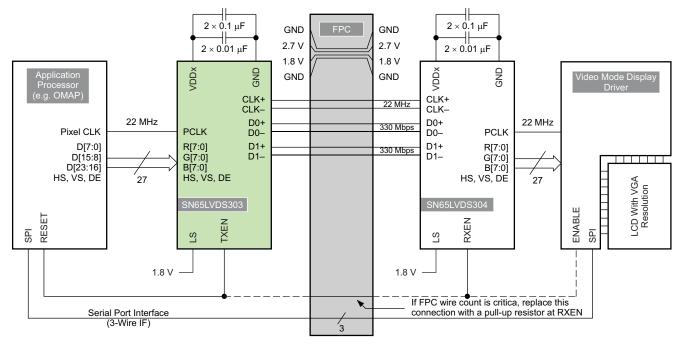

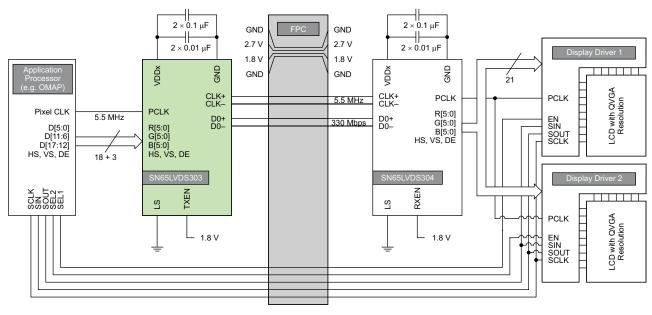

- Serial Interface Technology

- Compatible With FlatLink™3G Such as SN65LVDS303

- Supports Video Interfaces up to 24-Bit RGB Data and 3 Control Bits Received Over 1 or 2 SubLVDS Differential Lines

- SubLVDS Differential Voltage Levels

- Up to 810-Mbps Data Throughput

- Three Operating Modes to Conserve Power

- Active mode QVGA: 17 mW

- Typical Shutdown: 0.7 μW

- Typical Standby Mode: 27 μW Typical

- Bus-Swap Function for PCB-Layout Flexibility

- ESD Rating > 4 kV (HBM)

- Pixel Clock Range of 4 MHz–30 MHz

- Failsafe on all CMOS Inputs

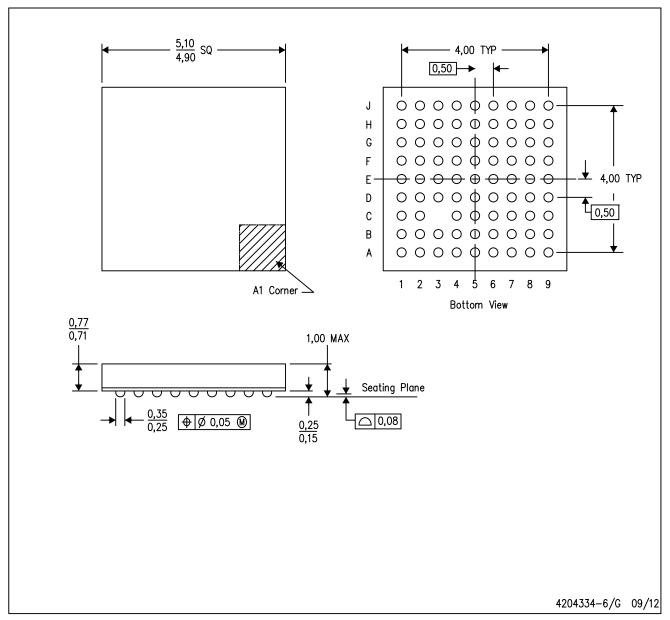

- Packaged in 5-mm × 5-mm MicroStar Junior μBGA<sup>®</sup> With 0,5-mm Ball Pitch

- Very Low EMI Meets SAE J1752/3 'Kh'-Spec

#### **APPLICATIONS**

- Small Low-Emission Interface Between Graphics Controller and LCD Display

- Mobile Phones and Smart Phones

- Portable Multimedia Players

#### **DESCRIPTION**

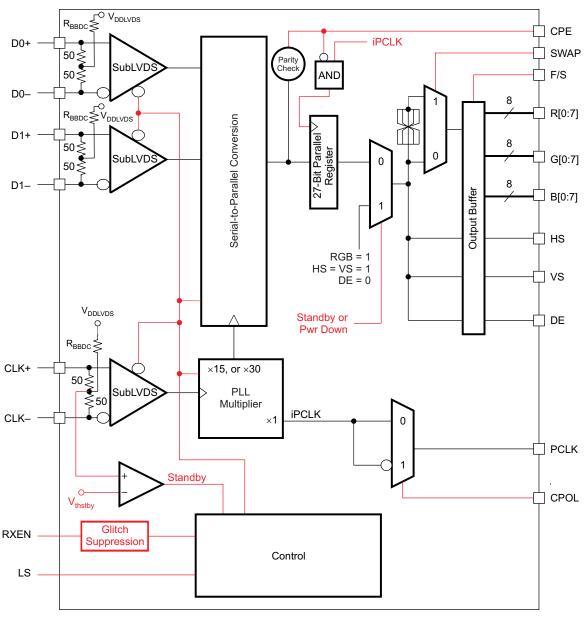

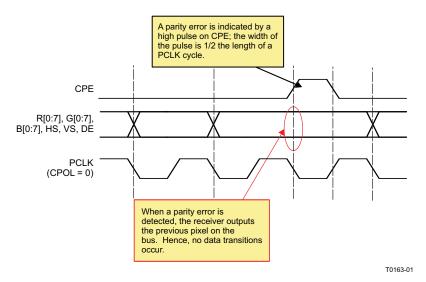

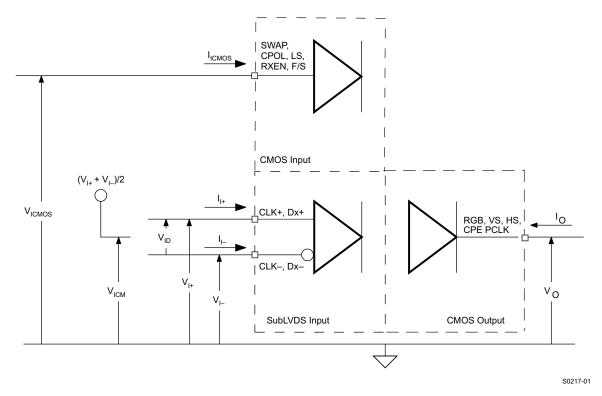

The SN65LVDS304 receiver deserializes FlatLink™3G-compliant serial input data to 27 parallel data outputs. The SN65LVDS304 receiver contains one shift register to load 30 bits from 1 or 2 serial inputs and latches the 24 pixel bits and 3 control bits out to the parallel CMOS outputs after checking the parity bit. If the parity check confirms correct parity, the channel parity error (CPE) output remains low. If a parity error is detected, the CPE output generates a high pulse while the data output bus disregards the newly-received pixel. Instead, the last data word is held on the output bus for another clock cycle.

The serial data and clock are received via sub-low-voltage differential signalling (SubLVDS) lines. The SN65LVDS304 supports three operating power modes (shutdown, standby, and active) to conserve power.

When receiving, the PLL locks to the incoming clock CLK and generates an internal high-speed clock at the line rate of the data lines. The data is serially loaded into a shift register using the internal high-speed clock. The deserialized data is presented on the parallel output bus with a recreation of the pixel clock, PCLK, generated from the internal high-speed clock. If no input CLK signal is present, the output bus is held static with PCLK and DE held low, while all other parallel outputs are pulled high.

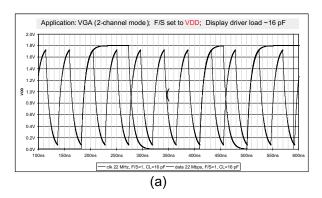

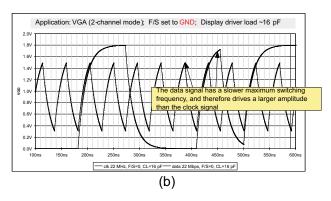

The parallel (CMOS) output bus offers a bus-swap feature. The SWAP control pin controls the output pin order of the output pixel data to be either R[7:0]. G[7:0], B[7:0], VS, HS, DE or B[0:7], G[0:7], R[0:7], VS, HS, DE. This gives a PCB designer the flexibility to better match the bus to the LCD driver pinout or to put the receiver device on the top side or the bottom side of the PCB. The F/S control input selects between a slow CMOS bus output rise time for best EMI and power consumption and a fast CMOS output for increased speed or higher-load designs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

FlatLink is a trademark of Texas Instruments. µBGA is a registered trademark of Tessera, Inc.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **DESCRIPTION (CONTINUED)**

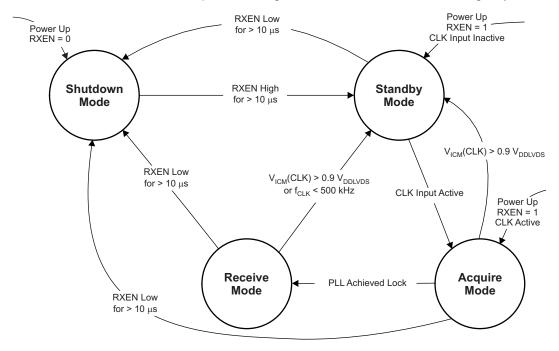

The link select line, LS, selects whether 1 or 2 serial links are used. The RXEN input can be used to put the SN65LVDS304 in a shutdown mode. The SN65LVDS304 enters an active standby mode if the common mode voltage of the CLK input becomes shifted to  $V_{DDLVDS}$  (e.g., transmitter releases CLK output into high-impedance). This minimizes power consumption without the need of switching an external control pin. The SN65LVDS304 is characterized for operation over ambient air temperatures of  $-40^{\circ}$ C to  $85^{\circ}$ C. All CMOS and SubLVDS signals are 2-V tolerant with  $V_{DD} = 0$  V. This feature allows signal powerup before  $V_{CC}$  is stabilized.

#### **FUNCTIONAL BLOCK DIAGRAM**

B0177-01

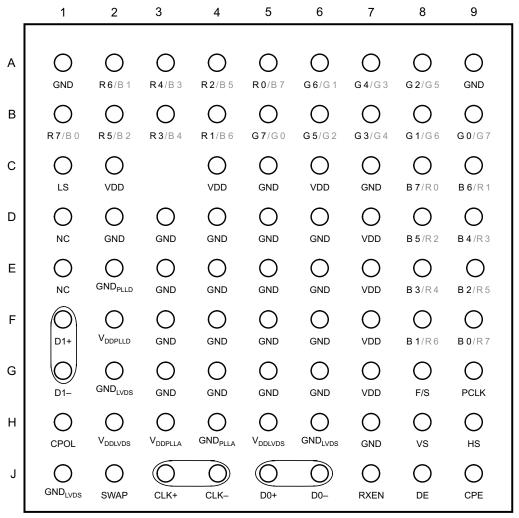

#### **PINOUT - TOP VIEW**

#### ZQE PACKAGE (TOP VIEW)

RGB Output pin assignment based on SWAP pin setting: SWAP = 0 / SWAP = 1

P0049-01

#### PINOUT - TOP VIEW (continued)

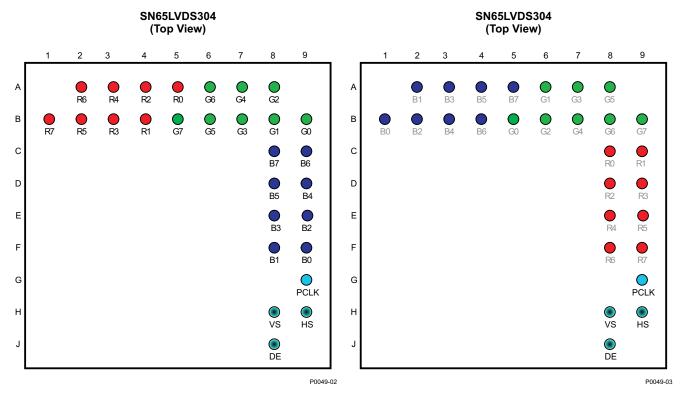

#### **SWAP PIN FUNCTIONALITY**

The SWAP pin allows the pcb designer to reverse the RGB bus, minimizing potential signal crossovers due to signal routing. The two drawings beneath show the RGB signal pin assignment based on the SWAP-pin setting.

Figure 1. Pinout With SWAP PIN = GND

Figure 2. Pinout With SWAP PIN = V<sub>DD</sub>

# PINOUT - TOP VIEW (continued)

# **Table 1. Pin Description**

| PIN | SWAP | SIGNAL | PIN      | SWAP . | SIGNAL              | PIN | SWAP | SIGNAL              |

|-----|------|--------|----------|--------|---------------------|-----|------|---------------------|

| A1  | -    | GND    | C1       | -      | LS                  | F1  | -    | D1+                 |

| 4.0 | L    | R6     | C2       | -      | $V_{DD}$            | F2  | -    | V <sub>DDPLLD</sub> |

| A2  | Н    | B1     | C3       | unpo   | pulated             | F3  | _    | GND                 |

| 4.0 | L    | R4     | C4       | _      | $V_{DD}$            | F4  | _    | GND                 |

| A3  | Н    | В3     | C5       | _      | GND                 | F5  | _    | GND                 |

| A 4 | L    | R2     | C6       | _      | $V_{DD}$            | F6  | _    | GND                 |

| A4  | Н    | B5     | C7       | _      | GND                 | F7  | _    | $V_{DD}$            |

| 4.5 | L    | R0     | 00       | L      | B7                  | F0  | L    | B1                  |

| A5  | Н    | B7     | C8       | Н      | R0                  | F8  | Н    | R6                  |

| 4.0 | L    | G6     | 00       | L      | В6                  | F0  | L    | В0                  |

| A6  | Н    | G1     | C9       | Н      | R1                  | F9  | Н    | R7                  |

|     | L    | G4     | D1       | _      | NC                  | G1  | _    | D1-                 |

| A7  | Н    | G3     | D2       | _      | GND                 | G2  | _    | GND <sub>LVDS</sub> |

|     | L    | G2     | D3       | _      | GND                 | G3  | _    | GND                 |

| A8  | Н    | G5     | D4       | _      | GND                 | G4  | _    | GND                 |

| A9  | _    | GND    | D5       | _      | GND                 | G5  | _    | GND                 |

|     | L    | R7     | D6       | _      | GND                 | G6  | _    | GND                 |

| B1  | Н    | В0     | D7       | _      | V <sub>DD</sub>     | G7  | _    | V <sub>DD</sub>     |

|     | L    | R5     |          | L      | B5                  | G8  | _    | F/S                 |

| B2  | Н    | B2     | D8       | Н      | R2                  | G9  | _    | PCLK                |

| _   | L    | R3     | _        | L      | B4                  | H1  | _    | CPOL                |

| В3  | Н    | B4     | D9       | Н      | R3                  | H2  | _    | V <sub>DDLVDS</sub> |

|     | L    | R1     | E1       | _      | NC                  | НЗ  | _    | V <sub>DDPLLA</sub> |

| B4  | Н    | B6     | E2       | _      | GND <sub>PLLD</sub> | H4  | _    | GND <sub>PLLA</sub> |

|     | L    | G7     | E3       | _      | GND                 | H5  | _    | V <sub>DDLVDS</sub> |

| B5  | Н    | G0     | E4       | _      | GND                 | H6  | _    | GND <sub>LVDS</sub> |

| _   | L    | G5     | E5       | _      | GND                 | H7  | _    | GND                 |

| B6  | Н    | G2     | E6       | _      | GND                 | H8  | _    | VS                  |

|     | L    | G3     | E7       | _      | $V_{DD}$            | H9  | _    | HS                  |

| B7  | Н    | G4     |          | L      | B3                  | J1  | _    | GND <sub>LVDS</sub> |

| _   | L    | G1     | E8       | Н      | R4                  | J2  | _    | SWAP                |

| B8  | Н    | G6     | _        | L      | B2                  | J3  | _    | CLK+                |

|     | L    | G0     | E9       | Н      | R5                  | J4  | _    | CLK-                |

| B9  | Н    | G7     | <u>L</u> | i      |                     | J5  | _    | D0+                 |

|     | 1    |        |          |        |                     | J6  | _    | D0-                 |

|     |      |        |          |        |                     | J7  | _    | RXEN                |

|     |      |        |          |        |                     | J8  | _    | DE                  |

|     |      |        |          |        |                     | J9  | _    | CPE                 |

#### **Table 2. TERMINAL FUNCTIONS**

| NAME                | I/O           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0+, D0-            |               | SubLVDS data link (active during normal operation)                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D1+, D1–            | SubLVDS in    | SubLVDS data link (active during normal operation when LS = high, high-impedance if LS = low); input can be left open if unused.                                                                                                                                                                                                                                                                                                                                                |

| CLK+, CLK-          |               | SubLVDS input pixel clock; polarity is fixed.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R0-R7               |               | Red-pixel data (8); pin assignment depends on SWAP pin setting.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G0-G7               |               | Green-pixel data (8); pin assignment depends on SWAP pin setting.                                                                                                                                                                                                                                                                                                                                                                                                               |

| B0-B7               |               | Blue-pixel data (8); pin assignment depends on SWAP pin setting.                                                                                                                                                                                                                                                                                                                                                                                                                |

| HS                  |               | Horizontal sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VS                  |               | Vertical sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DE                  |               | Data enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCLK                |               | Output pixel clock; rising or falling clock polarity is selected by control input CPOL.                                                                                                                                                                                                                                                                                                                                                                                         |

| LS                  |               | Link select (determines active SubLVDS data links and PLL range); see Table 3.                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     |               | Disables the CMOS Drivers and Turns Off the PLL, putting device in shutdown mode                                                                                                                                                                                                                                                                                                                                                                                                |

|                     |               | 1 – Receiver enabled<br>0 – Receiver disabled (shutdown)                                                                                                                                                                                                                                                                                                                                                                                                                        |

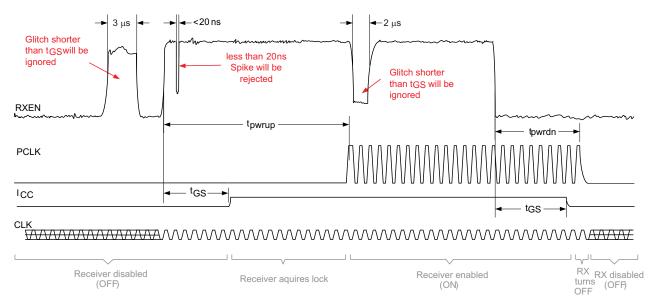

| RXEN                |               | Note: The RXEN input incorporates glitch suppression logic to avoid unwanted switching. The input must be pulled low for longer than 10 $\mu$ s continuously to force the receiver to enter shutdown. The input must be pulled high for at least 10 $\mu$ s continuously to activate the receiver. An input pulse shorter than 5 $\mu$ s is interpreted as a glitch and becomes ignored. At power up, the receiver is enabled immediately if RXEN = H and disabled if RXEN = L. |

|                     | CMOS In       | Output clock polarity selection                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CPOL                |               | 0 – rising edge clocking<br>1 – falling edge clocking                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SWAP                |               | Bus swap swaps the bus pins to allow device placement on top or bottom of PCB. See pinout drawing for pin assignments.                                                                                                                                                                                                                                                                                                                                                          |

| SWAI                |               | 0 – data output from R7B0<br>1 – data output from B0R7                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |               | CMOS bus rise time select                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F/S                 |               | 1 – fast-output rise time<br>0 – slow-output rise time                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPE                 | CMOS out      | Channel parity error This output indicates the detection of a parity error by generating an output high-pulse for half of a PCLK clock cycle; this allows counting parity errors with a simple counter.                                                                                                                                                                                                                                                                         |

|                     |               | 0 – no error<br>high-pulse – bit error detected                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $V_{DD}$            |               | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GND                 |               | Supply ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DDLVDS</sub> |               | SubLVDS I/O supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND <sub>LVDS</sub> | Dower augusti | SubLVDS ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DDPLLA</sub> | Power supply  | PLL analog supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND <sub>PLLA</sub> |               | PLL analog GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{DDPLLD}$        |               | PLL digital supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND <sub>PLLD</sub> |               | PLL digital GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### **FUNCTIONAL DESCRIPTION**

#### **Deserialization Modes**

The SN65LVDS304 receiver has two modes of operation controlled by link-select pin LS. Table 3 shows the deserializer modes of operation.

**Table 3. Logic Table: Link Select Operating Modes**

| LS |      | MODE OF OPERATION                          | DATA LINKS STATUS |

|----|------|--------------------------------------------|-------------------|

| 0  | 1ChM | 1-channel mode (30-bit serialization rate) | D0 active         |

| 1  | 2ChM | 2-channel mode (15-bit serialization rate) | D0, D1 active     |

#### 1-Channel Mode

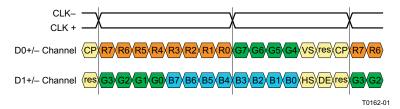

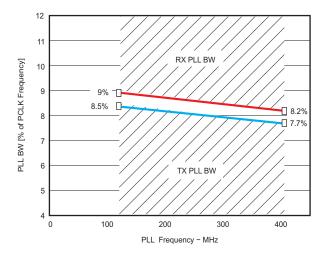

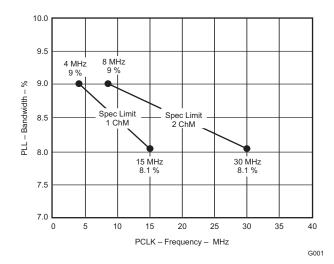

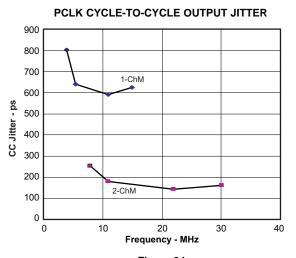

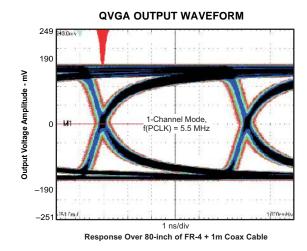

While LS is held low, the SN65LVDS304 receives payload data over a single SubLVDS data pair, D0. The PLL locks to the SubLVDS clock input and internally multiplies the clock by a factor of 30. The internal high-speed clock is used to shift in the data payload on D0 and to deserialize 30 bits of data. Figure 3 illustrates the timing and the mapping of the data payload into the 30-bit frame. The internal high-speed clock is divided by a factor of 30 to recreate the pixel clock, and the data payload with the pixel clock is presented on the output bus. The reserved bits and parity bit are not output. While in this mode, the PLL can lock to a clock that is in the range of 4 MHz through 15 MHz. This mode is intended for smaller video display formats that do not need the full bandwidth capabilities of the SN65LVDS304.

Figure 3. Data and Clock Input in 1-ChM (LS = low)

#### 2-Channel Mode

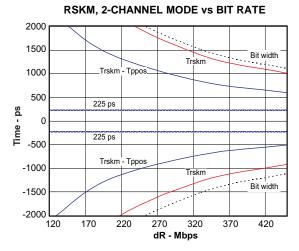

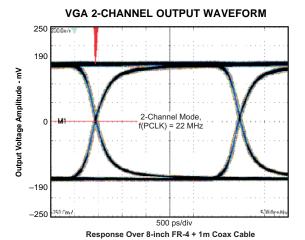

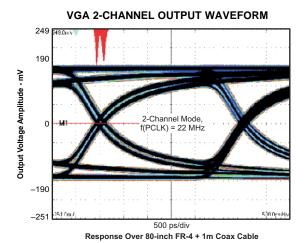

While LS is held high, the SN65LVDS304 receives payload data over two SubLVDS data pairs, D0 and D1. The PLL locks to the SubLVDS clock input and internally multiplies the clock by a factor of 15. The internal high-speed clock is used to shift in the data payload on D0 and D1 and to deserialize 15 bits of data from each pair. Figure 4 illustrates the timing and the mapping of the data payload into the 30-bit frame. The internal high-speed clock is divided by a factor of 15 to recreate the pixel clock, and the data payload with pixel clock is presented on the output bus. The reserved bits and parity bit are not output. While in this mode, the PLL can lock to a clock that is in the range of 8 MHz through 30 MHz.

Figure 4. Data and Clock Input in 2-ChM (LS = high)

#### **POWER-DOWN MODES**

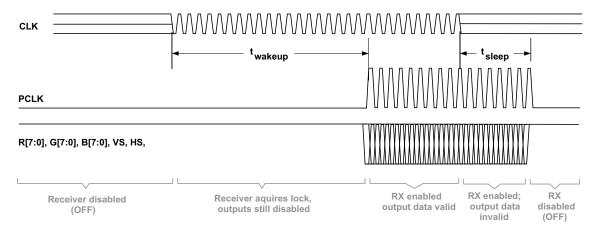

The SN65LVDS304 receiver has two power-down modes to facilitate efficient power management.

#### **SHUTDOWN MODE**

A low input signal on the RXEN pin puts the SN65LVDS304 into shutdown mode. This turns off most of the receiver circuitry including the SubLVDS receivers, PLL, and deserializers. The SubLVDS differential-input resistance remains  $100~\Omega$ , and any input signal is ignored. All outputs hold a static output pattern:

$$R[0:7] = G[0:7] = B[0:7] = VS = HS = high; DE = PCLK = low.$$

The current draw in shutdown mode is nearly zero if the SubLVDS inputs are left open or pulled high.

#### STANDBY MODE

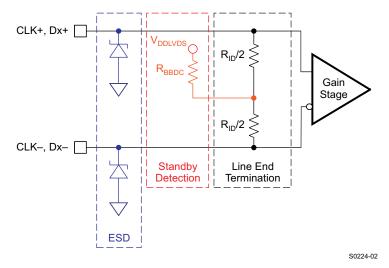

The SN65LVDS304 enters the standby mode when the SN65LVDS304 is not in shutdown mode but the SubLVDS clock-input common-mode voltage is above  $0.9 \times V_{DDLVDS}$ . The CLK input incorporates a pullup circuit to shift the SubLVDS clock-input common-mode voltage to  $V_{DDLVDS}$  in the absence of an input signal. All circuitry except the SubLVDS clock-input standby monitor is shut down. The SN65LVDS304 also enters the standby mode when the input clock frequency on the CLK input is less than 500 kHz. The SubLVDS input resistance remains 100  $\Omega$ , and any input signal on the data inputs D0 and D1 is ignored. All outputs will hold a static output pattern:

$$R[0:7] = G[0:7] = B[0:7] = VS = HS = high; DE = PCLK = low.$$

The current drawn in standby mode is very low.

#### **ACTIVE MODES**

A high input signal on RXEN combined with a CLK input signal switching faster than 3 MHz and  $V_{\text{ICM}}$  smaller than 1.3 V forces the SN65LVDS304 into the active mode. Current consumption in the active mode depends on operating frequency and the number of data transitions in the data payload. CLK-input frequencies between 3 MHz and 4 MHz activate the device, but proper PLL functionality is not assured. It is not recommended to operate the SN65LVDS304 in active mode at CLK frequencies below 4 MHz.

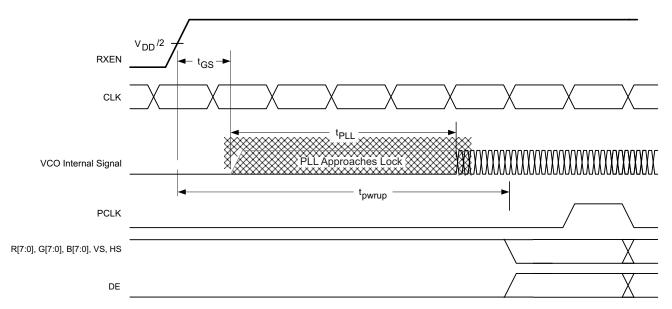

#### **ACQUIRE MODE (PLL Approaches Lock)**

When the SN65LVDS304 is enabled and a SubLVDS clock input present, the PLL pursues lock to the input clock. While the PLL pursues lock, the output data bus holds a static output pattern:

$$R[0:7] = G[0:7] = B[0:7] = VS = HS = high; DE = PCLK = low.$$

For proper device operation, the pixel clock frequency must fall within the valid  $f_{PCLK}$  range specified under recommended operating conditions. If the pixel clock frequency is larger than 3 MHz but smaller than  $f_{PCLK(min)}$ , the SN65LVDS304 PLL is enabled. Under such conditions, it is possible for the PLL to lock temporarily to the pixel clock, causing the PLL monitor to release the device into active receive mode. If this happens, the PLL may or may not be properly locked to the pixel clock input, potentially causing data errors, frequency oscillation, and PLL deadlock (loss of VCO oscillation).

#### **RECEIVE MODE**

After the PLL achieves lock the device enters the normal receive mode. The output data bus presents the deserialized data. The PCLK output pin outputs the recovered pixel clock.

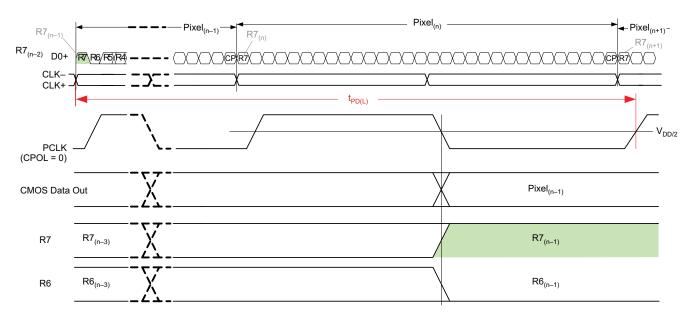

#### PARITY ERROR DETECTION AND HANDLING

The SN65LVDS304 receiver performs error checking on the basis of a parity bit that is transmitted across the SubLVDS interface from the transmitting device. Once the SN65LVDS304 detects the presence of the clock and the PLL has locked onto PCLK, then the parity is checked. Parity-error detection ensures detection of all single-bit errors in one pixel and 50% of all multibit errors.

The parity bit covers the 27-bit data payload consisting of 24 bits of pixel data plus VS, HS, and DE. Odd-parity bit signalling is used. The parity error is output on the CPE pin. If the sum of the 27 data bits and the parity bit result in an odd number, the receive data are assumed to be valid. The CPE output is held low. If the sum equals an even number, parity error is declared. The CPE output indicates high for half a PCLK period. The CPE output is set with the data bit transition and cleared after 1/2 the data-bit time. This allows counting every detected parity error with a simple counter connected to CPE.

If a parity error is detected, then the data on that PCLK cycle is not output. Instead, the last valid data from a previous PCLK cycle is repeated on the output bus. This is to prevent any bit error that occurs on the LVDS link from causing perturbations in VS, HS, or DE that might be visually disruptive to a display.

The reserved bits are not covered in the parity calculations.

Figure 5. Parity Error Detection

#### STATUS-DETECT AND OPERATING-MODES FLOW DIAGRAM

The SN65LVDS304 switches between the power saving and active modes in the following way:

F0017-01

#### **Table 4. Status Detect and Operating Modes Descriptions**

| MODE          | CHARACTERISTICS                                                                                                                                                                  | CONDITIONS                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shutdown mode | Least amount of power consumption (most circuitry turned off); all outputs held static:  R[0:7] = G[0:7] = B[0:7] = VS = HS = high; DE = PCLK = low                              | RXEN is set low for longer than 10 µs. (1)(2)                                                                                                                 |

| Standby mode  | Low power consumption (standby monitor circuit active; PLL is shutdown to conserve power); All outputs held static: $R[0:7] = G[0:7] = B[0:7] = VS = HS = high; DE = PCLK = low$ | RXEN is high for longer than 10 $\mu$ s and CLK inputs are common-mode, $V_{ICM(CLK)}$ is above $0.9 \times V_{DDLVDS}$ , or CLK inputs are floating $^{(2)}$ |

| Acquire mode  | PLL pursues lock; all outputs held static:<br>R[0:7] = G[0:7] = B[0:7] = VS = HS = high; DE = PCLK = low                                                                         | RXEN is high; CLK input monitor detected clock input common mode and woke up receiver from standby mode.                                                      |

| Receive mode  | Data transfer (normal operation);<br>receiver deserializes data and provides data on parallel<br>output                                                                          | RXEN is high and PLL is locked to incoming clock.                                                                                                             |

<sup>(1)</sup> In shutdown mode, all SN65LVDS304 internal switching circuits (e.g., PLL, serializer, etc.) are turned off to minimize power consumption. The input stage of any input pin remains active.

#### **Table 5. Operating Mode Transitions**

| MODE TRANSITION                        | USE CASE                                                                     | TRANSITION SPECIFICS                                                                                                                                         |

|----------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Shutdown \to standby$                 | Drive RXEN high to enable                                                    | 1. RXEN high > 10 μs                                                                                                                                         |

|                                        | receiver.                                                                    | 2. Receiver enters standby mode.                                                                                                                             |

|                                        |                                                                              | a. $R[0:7] = G[0:7] = B[0:7] = VS = HS$ remain high and DE = PCLK low                                                                                        |

|                                        |                                                                              | b. Receiver activates clock input monitor.                                                                                                                   |

| Standby → acquire                      | Transmitter activity                                                         | CLK input monitor detects clock input activity.                                                                                                              |

|                                        | detected                                                                     | 2. Outputs remain static.                                                                                                                                    |

|                                        |                                                                              | 3. PLL circuit is enabled.                                                                                                                                   |

| Acquire → receive                      | Link is ready to receive                                                     | PLL is active and approaches lock.                                                                                                                           |

|                                        | data.                                                                        | 2. PLL achieves lock within t <sub>wakeup</sub> .                                                                                                            |

|                                        |                                                                              | 3. Input D0 or D1 becomes active, depending on LS selection.                                                                                                 |

|                                        |                                                                              | First data word is recovered.                                                                                                                                |

|                                        |                                                                              | <ol><li>Parallel output bus turns on switching from a static output pattern to output the<br/>first valid data word.</li></ol>                               |

| Receive → standby                      | Transmitter requested to                                                     | Receiver disables outputs within t <sub>sleep</sub> .                                                                                                        |

|                                        | enter standby mode by input common mode                                      | 2. RX Input monitor detects $V_{ICM} > 0.9 V_{DDLVDS}$ within $t_{sleep}$ .                                                                                  |

|                                        | voltage V <sub>ICM</sub> > 0.9 V <sub>DDLVDS</sub> (e.g., transmitter output | 3. R[0:7] = G[0:7] = B[0:7] = VS = HS transition to high and DE = PCLK to low on next falling PLL clock edge                                                 |

|                                        | clock stops or enters high-impedance state)                                  | 4. PLL shuts down. Clock activity input monitor remains active.                                                                                              |

| $\textbf{Receive/standby} \rightarrow$ | Turn off receiver.                                                           | <ol> <li>RXEN pulled low for &gt; t<sub>pwrdn</sub>.</li> </ol>                                                                                              |

| shutdown                               |                                                                              | <ol> <li>R[0:7] = G[0:7] = B[0:7] = VS = HS remain static high or transition to static high<br/>and DE = PCLK remain or transition to static low.</li> </ol> |

|                                        |                                                                              | 3. Most IC circuitry is shut down for least power consumption.                                                                                               |

<sup>(2)</sup> Leaving CMOS control inputs unconnected can cause random noise to toggle the input stage and potentially harm the device. All CMOS inputs must be tied to a valid logic level, V<sub>IL</sub> or V<sub>IH</sub>, during shutdown or standby Mode. Exceptions are the SubLVDS inputs CLK and Dx, which can be left unconnected while not in use.

# **ABSOLUTE MAXIMUM RATINGS**(1)

|                                                                                                                                                                                                                     |                                                                                 | VALUE                  | UNIT    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------|---------|

| Supply voltage range, V <sub>DD</sub> (2                                                                                                                                                                            | <sup>2)</sup> , V <sub>DDPLLA</sub> , V <sub>DDPLLD</sub> , V <sub>DDLVDS</sub> | -0.3 to 2.175          | V       |

| $ \begin{array}{c c} \mbox{Voltage range at any input} & \mbox{When $V_{DDx} > 0$ V} \\ \mbox{or output terminal} & \mbox{When $V_{DDx} \le 0$ V} \\ \mbox{Human body model} \mbox{(3) (all pins)} \\ \end{array} $ | When V <sub>DDx</sub> > 0 V                                                     | -0.5 to 2.175          | V       |

|                                                                                                                                                                                                                     | -0.5 to V <sub>DD</sub> + 2.175                                                 | V                      |         |

|                                                                                                                                                                                                                     | Human body model (3) (all pins)                                                 | ±4                     | kV      |

| Electrostatic discharge                                                                                                                                                                                             | Charged-device model (4) (all pins)                                             | ±1500                  | V       |

|                                                                                                                                                                                                                     |                                                                                 | V                      |         |

| Continuous power dissipation See I                                                                                                                                                                                  |                                                                                 | See Dissipation Rating | s Table |

| Ouput current, I <sub>O</sub> ±5                                                                                                                                                                                    |                                                                                 | mA                     |         |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to the GND terminals.

- (3) In accordance with JEDEC Standard 22, Test Method A114-B

(4) In accordance with JEDEC Standard 22, Test Method C101

(5) In accordance with JEDEC Standard 22, Test Method A115-A

#### **DISSIPATION RATINGS**

| PACKAGE | PACKAGE CIRCUIT BOARD MODEL |        | DERATING FACTOR <sup>(1)</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |  |

|---------|-----------------------------|--------|---------------------------------------------------------------|---------------------------------------|--|

| ZQE     | Low-K <sup>(2)</sup>        | 592 mW | 7.407 mW/°C                                                   | 148 mW                                |  |

- (1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

- In accordance with the low-K thermal metric definitions of EIA/JESD51-2.

#### **DEVICE POWER DISSIPATION**

|                | PARAMETER TEST CONDITIONS |                                                                                                                | TYP                                                                                       | MAX | UNIT |    |

|----------------|---------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|------|----|

|                | Device power              | $V_{DDx} = 1.8 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , all outputs terminated with 10 pF, $f_{CLK}$ at 4 MHz | 16.8                                                                                      |     | m\// |    |

| P <sub>D</sub> | P <sub>D</sub>            |                                                                                                                | $V_{DDx}$ = 1.95 V, $T_A$ = -40°C, all outputs terminated with 10 pF, $f_{CLK}$ at 30 MHz |     | 72.2 | mW |

# RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>

|                                                                                      |                                                                         |                                                                                                 | MIN                        | TYP | MAX                 | UNIT  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------|-----|---------------------|-------|

| V <sub>DD</sub><br>V <sub>DDPLLA</sub><br>V <sub>DDPLLD</sub><br>V <sub>DDLVDS</sub> | Supply voltages                                                         |                                                                                                 | 1.65                       | 1.8 | 1.95                | V     |

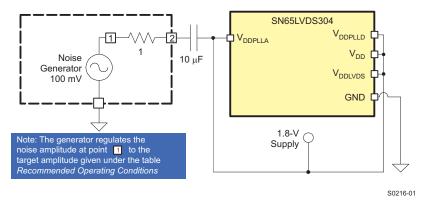

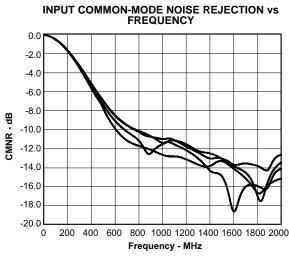

| V <sub>DDn(PP)</sub>                                                                 | Supply voltage noise magnitude                                          | Test set-up shown in Figure 7;<br>f <sub>CLK</sub> ≤ 50MHz; f(noise) = 1Hz to 2 GHz             |                            |     | 100                 | mV    |

|                                                                                      |                                                                         | f <sub>CLK</sub> > 50MHz; f(noise) = 1Hz to 1MHz                                                |                            |     | 100                 |       |

|                                                                                      |                                                                         | f <sub>CLK</sub> > 50 MHz; f(noise) > 1MHz                                                      |                            |     | 40                  |       |

| $T_A$                                                                                | Operating free-air temperature                                          |                                                                                                 | -40                        |     | 85                  | °C    |

| CLK+ and                                                                             | I CLK-                                                                  |                                                                                                 |                            |     |                     |       |

|                                                                                      |                                                                         | 1-channel transmit mode, see Figure 3                                                           | 4                          |     | 15                  | MHz   |

| $f_{CLK\pm}$                                                                         | Input pixel clock frequency                                             | 2-channel transmit mode, see Figure 4                                                           | 8                          |     | 30                  | IVI⊓∠ |

|                                                                                      |                                                                         | Standby mode <sup>(2)</sup> , see Figure 16                                                     |                            |     | 500                 | kHz   |

| t <sub>DUTCLK</sub>                                                                  | CLK input duty cycle                                                    |                                                                                                 | 35                         |     | 65                  | %     |

| D0+, D0-,                                                                            | , D1+, D1-, CLK+, and CLK-                                              |                                                                                                 |                            |     |                     |       |

| V <sub>ID</sub>                                                                      | Magnitude of differential input voltage                                 | $ V_{D0+} - V_{D0-} $ , $ V_{D1+} - V_{D1-} $ , $ V_{CLK+} - V_{CLK-} $ during normal operation | 70                         |     | 200                 | mV    |

|                                                                                      |                                                                         | Receive or acquire mode                                                                         | 0.6                        |     | 1.2                 |       |

| V <sub>ICM</sub>                                                                     | Input voltage common mode range                                         | Standby mode                                                                                    | 0.9<br>V <sub>DDLVDS</sub> |     |                     | V     |

| $\Delta V_{ICM}$                                                                     | Input voltage common mode variation among all SubLVDS inputs            | $V_{ICM(n)} - V_{ICM(m)}$ with n = D0, D1, or CLK and m = D0, D1, or CLK                        | -100                       |     | 100                 | mV    |

| $\Delta V_{ID}$                                                                      | Differential input voltage amplitude variation among all SubLVDS inputs | $V_{\text{ID}(n)} - V_{\text{ID}(m)}$ with n = D0, D1, or CLK and m = D0, D1, or CLK            | -10                        |     | 10                  | %     |

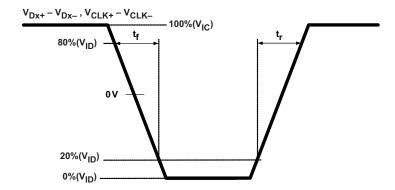

| t <sub>r/f</sub>                                                                     | Input rise and fall times                                               | RXEN at V <sub>DD</sub> ; see Figure 10                                                         |                            |     | 800                 | ps    |

| $\Delta t_{r/f}$                                                                     | Input rise or fall time mismatch among all SubLVDS inputs               | $t_{r(n)}-t_{r(m)}$ and $t_{f(n)}-t_{f(m)}$ with $n=D0,D1,or$ CLK and $m=D0,D1,or$ CLK          | -100                       |     | 100                 | ps    |

| LS, CPOL                                                                             | ., SWAP, RXEN, F/S                                                      |                                                                                                 |                            |     |                     |       |

| V <sub>ICMOSH</sub>                                                                  | High-level input voltage                                                |                                                                                                 | 0.7 V <sub>DD</sub>        |     | $V_{DD}$            | V     |

| V <sub>ICMOSL</sub>                                                                  | Low-level input voltage                                                 |                                                                                                 | 0                          |     | 0.3 V <sub>DD</sub> | V     |

| t <sub>inRXEN</sub>                                                                  | RXEN input pulse duration                                               |                                                                                                 | 10                         |     |                     | μs    |

| R[7:0], G[                                                                           | [7:0], B[7:0], VS, HS, PCLK, CPE                                        |                                                                                                 | •                          |     |                     |       |

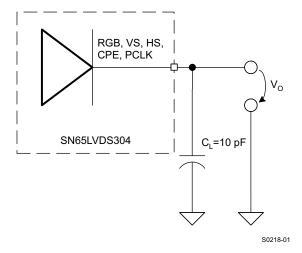

| C <sub>L</sub>                                                                       | Output load capacitance                                                 |                                                                                                 |                            | 10  |                     | pF    |

|                                                                                      |                                                                         |                                                                                                 |                            |     |                     |       |

<sup>(1)</sup> Unused single-ended inputs must be held high or low to prevent them from floating.

(2) PCLK input frequencies lower than 500 kHz force the SN65LVDS304 into standby mode. Input frequencies between 500 kHz and 3 MHz may or may not activate the SN65LVDS304. Input frequencies between 500 kHz and 4 MHz are not recommended, and can cause PLL malfunction.

#### **DEVICE ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

| PARAMETER               |                                                                                                                                                                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                             |                                             | MIN TYP(1) | MAX  | UNIT |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|------|------|

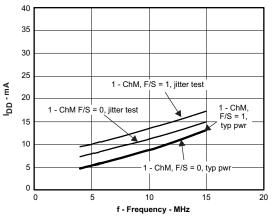

|                         |                                                                                                                                                                                       | Alternating 1010 test pattern (see Table 9); all CMOS outputs                                                                                                                                                                                                                                                                                                               | f <sub>PCLK</sub> = 4 MHz                   | 9.8        | 14   |      |

|                         |                                                                                                                                                                                       | terminated with 10 pF; F/S and RXEN at $V_{DD}$ ; $V_{IH} = V_{DD}$ , $V_{IL} = 0$ V; $V_{DD}$<br>= $V_{DDPLLA} = V_{DDPLD} = V_{DDLVDS}$                                                                                                                                                                                                                                   | f <sub>PCLK</sub> = 6 MHz                   | 11.7       | 15.9 | mA   |

|                         | 1ChM                                                                                                                                                                                  | - DDFLEA - DDFLED - DDLVDS                                                                                                                                                                                                                                                                                                                                                  | f <sub>PCLK</sub> = 15 MHz                  | 19.3       | 25   |      |

|                         | ICITIVI                                                                                                                                                                               | Typical power test pattern (see Table 7); V <sub>ID</sub> = 70 mV, all CMOS                                                                                                                                                                                                                                                                                                 | f <sub>PCLK</sub> = 4 MHz                   | 4.7        |      |      |

|                         |                                                                                                                                                                                       | outputs terminated with 10 pF; F/S at GND and RXEN at $V_{DD}$ ; $V_{IH} = V_{DD}$ , $V_{IL} = 0$ V; $V_{DD} = V_{DDPLLA} = V_{DDPLLD} = V_{DDIVDS}$                                                                                                                                                                                                                        | f <sub>PCLK</sub> = 6 MHz                   | 6          |      | mA   |

|                         |                                                                                                                                                                                       | VDD, VIL - VV, VDD - VDDPLLA - VDDPLLD - VDDLVDS                                                                                                                                                                                                                                                                                                                            | f <sub>PCLK</sub> = 15 MHz                  | 13.2       |      |      |

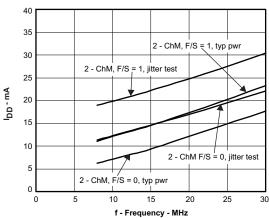

|                         |                                                                                                                                                                                       | Alternating 1010 test pattern (see <b>Table 9</b> ); all CMOS outputs terminated with 10 pF; F/S and RXEN at $V_{DD}$ ; $V_{IH} = V_{DD}$ , $V_{IL} = 0$ V; $V_{DD} = V_{DDPLLA} = V_{DDPLLD} = V_{DDLVDS}$                                                                                                                                                                 | f <sub>PCLK</sub> = 8 MHz                   | 14.3       | 19.4 |      |

| , RMS supply            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                             | f <sub>PCLK</sub> = 22 MHz                  | 25         | 33   | mA   |

| I <sub>DD</sub> current | 2ChM                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                             | f <sub>PCLK</sub> = 30 MHz                  | 26.8       | 37   |      |

|                         | ZCITIVI                                                                                                                                                                               | Typical power test pattern (see Table 8); V <sub>ID</sub> = 70 mV, all CMOS outputs terminated with 10 pF; F/S at GND and RXEN at V <sub>DD</sub> ; V <sub>IH</sub> = V <sub>DD</sub> , V <sub>IL</sub> = 0 V; V <sub>DD</sub> = V <sub>DDPLLA</sub> = V <sub>DDPLLD</sub> = V <sub>DDLVDS</sub> LK and D inputs are left open; all control inputs held static high or low; | f <sub>PCLK</sub> = 8 MHz                   | 6.4        |      |      |

|                         |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                             | f <sub>PCLK</sub> = 22 MHz                  | 13.7       |      | mA   |

|                         |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                             | f <sub>PCLK</sub> = 30 MHz                  | 18.3       |      |      |

|                         | CLK and                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                             | Standby mode;<br>RXEN = V <sub>IH</sub>     | 15         | 100  |      |

|                         | All CMOS outputs terminated with 10 pF;  V <sub>IH</sub> = V <sub>DD</sub> , V <sub>IL</sub> = 0 V; V <sub>DD</sub> = V <sub>DDPLLA</sub> = V <sub>DDPLLD</sub> = V <sub>DDLVDS</sub> |                                                                                                                                                                                                                                                                                                                                                                             | Shutdown<br>mode;<br>RXEN = V <sub>IL</sub> | 0.4        | 10   | μA   |

<sup>(1)</sup> All typical values are at 25°C and with 1.8-V supply, unless otherwise noted.

#### INPUT ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                                   | PARAMETER                                                                                   | TEST CONDITIONS                                                                                           | MIN                 | TYP <sup>(1)</sup> | MAX                     | UNIT |

|-----------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|--------------------|-------------------------|------|

| D0+, D                            | 0-, D1+, D1-, CLK+, and CLK-                                                                |                                                                                                           |                     |                    |                         |      |

| V <sub>thstby</sub>               | Input voltage common mode threshold to switch between receive/acquire mode and standby mode | RXEN at V <sub>DD</sub>                                                                                   | 1.3                 |                    | 0.9 V <sub>DDLVDS</sub> | V    |

| $V_{THL}$                         | Low-level differential input voltage threshold                                              | $V_{D0+} - V_{D0-}, V_{D1+} - V_{D1}, V_{CLK+} - V_{CLK-}$                                                | -40                 |                    |                         | mV   |

| $V_{THH}$                         | High-level differential input voltage threshold                                             |                                                                                                           |                     |                    | 40                      | mV   |

| I <sub>I+</sub> , I <sub>I-</sub> | Input leakage current                                                                       | $V_{DD} = 1.95 \text{ V}; V_{I+} = V_{I-};$<br>$V_{I} = 0.4 \text{ V} \text{ and } V_{I} = 1.5 \text{ V}$ |                     |                    | 75                      | μΑ   |

| I <sub>IOFF</sub>                 | Power-off input current                                                                     | $V_{DD} = GND; V_I = 1.5 V$                                                                               |                     |                    | <b>–75</b>              | μΑ   |

| R <sub>ID</sub>                   | Differential input termination resistor value                                               |                                                                                                           | 78                  | 100                | 122                     | Ω    |

| C <sub>IN</sub>                   | Input capacitance                                                                           | Measured between input terminal and GND                                                                   |                     | 1                  |                         | pF   |

| ΔC <sub>IN</sub>                  | Input capacitance variation                                                                 | Within one signal pair<br>Between all signals                                                             |                     |                    | 0.2<br>1                | pF   |

| R <sub>BBDC</sub>                 | Pullup resistor for standby detection                                                       |                                                                                                           | 21                  | 30                 | 39                      | kΩ   |

| LS, CP                            | OL, SWAP, RXEN, F/S                                                                         |                                                                                                           |                     |                    |                         |      |

| $V_{IK}$                          | Input clamp voltage                                                                         | $I_I = -18 \text{ mA}, V_{DD} = V_{DD}(\text{min})$                                                       |                     |                    | -1.2                    | V    |

| I <sub>ICMOS</sub>                | Input current <sup>(2)</sup>                                                                | $0 \text{ V} \le \text{V}_{DD} \le 1.95 \text{ V}; \text{ V}_{I} = \text{GND or V}_{I}$<br>= 1.95 V       |                     |                    | 100                     | nA   |

| C <sub>IN</sub>                   | Input capacitance                                                                           |                                                                                                           |                     | 2                  |                         | pF   |

| I <sub>IH</sub>                   | High-level input current                                                                    | $V_{IN} = 0.7 V_{DD}$                                                                                     | -200                |                    | 200                     | nA   |

| I <sub>IL</sub>                   | Low-level input current                                                                     | $V_{IN} = 0.3 V_{DD}$                                                                                     | -200                |                    | 200                     | IIA  |

| $V_{IH}$                          | High-level input voltage                                                                    |                                                                                                           | 0.7 V <sub>DD</sub> |                    | $V_{DD}$                | V    |

| V <sub>IL</sub>                   | Low-level input voltage                                                                     |                                                                                                           | 0                   |                    | 0.3 V <sub>DD</sub>     | V    |

<sup>(1)</sup> All typical values are at 25°C and with 1.8-V supply unless otherwise noted.

#### **OUTPUT ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                             | TEST CONDITIONS                          | MIN                 | TYP | MAX                 | UNIT |

|-----------------|---------------------------------------|------------------------------------------|---------------------|-----|---------------------|------|

| R[0:7           | 7], G[0:7], B[0:7], VS, HS, PCLK, CPI | E                                        |                     |     | ,                   |      |

|                 |                                       | 1-ChM, F/S = L, $I_{OH} = -250 \mu A$    |                     |     |                     |      |

| .,              | High lavel autout august              | 2-ChM, F/S = L, $I_{OH} = -500 \mu A$    | 0.01/               |     | .,                  | V    |

| V <sub>OH</sub> | High-level output current             | 1-ChM, F/S = H, $I_{OH} = -500 \mu A$    | 0.8 V <sub>DD</sub> |     | V <sub>DD</sub>     | V    |

|                 |                                       | 2-ChM, F/S = H, $I_{OH} = -2 \text{ mA}$ |                     |     | 0.2 V <sub>DD</sub> |      |

|                 |                                       | 1-ChM, F/S = L, I <sub>OL</sub> = 250 μA |                     |     | 0.2 V <sub>DD</sub> |      |

| \ /             | Low-level output current              | 2-ChM, F/S = L, $I_{OL}$ = 500 $\mu$ A   | 0                   | 0.  |                     | V    |

| V <sub>OL</sub> |                                       | 1-ChM, F/S = H, $I_{OL}$ = 500 $\mu$ A   | 0                   |     |                     | V    |

|                 |                                       | 2-ChM, F/S = H, I <sub>OL</sub> = 2 mA   |                     |     |                     |      |

| I <sub>OH</sub> | High-level output current             | 1-ChM, F/S = L                           | -250                |     |                     |      |

|                 |                                       | 2-ChM, F/S = L; 1-ChM, F/S = H           | -500                |     |                     |      |

|                 |                                       | 2-ChM, F/S = H                           | -2000               |     |                     |      |

| $I_{OL}$        | Low-level output current              | 1-ChM, F/S = L                           |                     |     | 250                 | μΑ   |

|                 |                                       | 2-ChM, F/S = L; 1-ChM, F/S = H           |                     |     | 500                 |      |

|                 |                                       | 2-ChM, F/S = H                           |                     |     | 2000                |      |

<sup>(2)</sup> Do not leave any CMOS input unconnected or floating to minimize leakage currents. Every input must be connected to a valid logic level, V<sub>IH</sub> or V<sub>OL</sub>, while power is supplied to V<sub>DD</sub>.

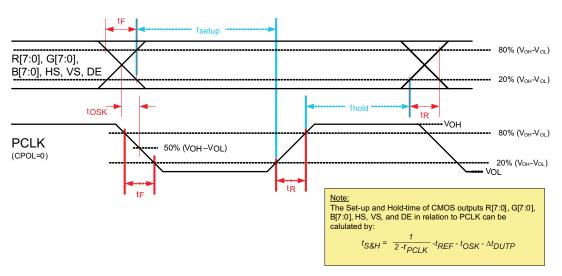

#### **SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                          | TEST CO                                                                                                                                                                                         | NDITIONS                                                                               | MIN                     | TYP(1)                | MAX                   | UNIT |

|---------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------|-----------------------|-----------------------|------|

| D0+, D0-            | -, D1+, D1-, CLK+, and CLK-                                        |                                                                                                                                                                                                 |                                                                                        |                         |                       |                       |      |

| t <sub>r/f</sub>    | Input rise and fall times                                          | RXEN at V <sub>DD</sub> ; see Figure 10                                                                                                                                                         |                                                                                        |                         |                       | 800                   | ps   |

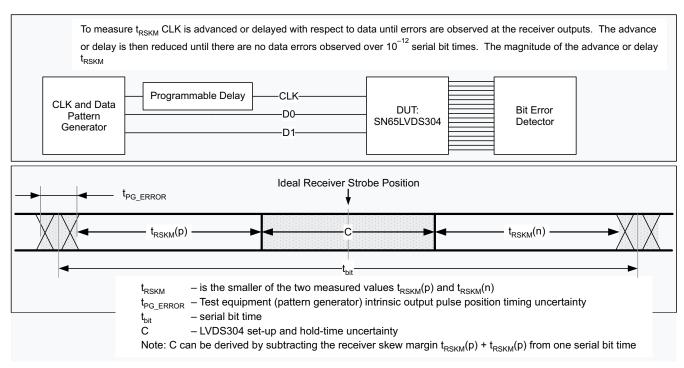

| $\Delta t_{r/f}$    | Input rise or fall time<br>mismatch between all<br>SubLVDS inputs  | $t_R(n) - t_R(m)$ and $t_F(n) - t_F(m)$<br>and m = D0, D1, or CLK                                                                                                                               | ) with n = D0, D1 or CLK                                                               | -100                    |                       | 100                   | ps   |