#### **MAX11212**

### 18-Bit, Single-Channel, Ultra-Low Power, Delta-Sigma ADC with 2-Wire Serial Interface

### **General Description**

The MAX11212 is an ultra-low power (< 300µA max active current), high-resolution, serial-output ADC. This device provides the highest resolution per unit power in the industry, and is optimized for applications that require very high dynamic range with low power such as sensors on a 4mA to 20mA industrial control loop. The MAX11212 provides a high-accuracy internal oscillator that requires no external components.

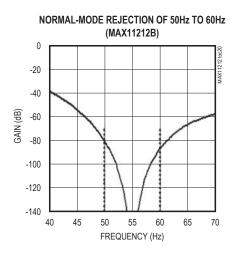

When used with the specified data rates, the internal digital filter provides more than 80dB rejection of 50Hz or 60Hz line noise. The MAX11212 provides a simple 2-wire serial interface in the space-saving, 10-pin  $\mu$ MAX® package. The MAX11212 operates over the -40°C to +85°C temperature range.

### **Applications**

- Sensor Measurement (Temperature and Pressure)

- Portable Instrumentation

- Battery Applications

- Weigh Scales

Ordering Information appears at end of data sheet.

μΜΑΧ is a registered trademark of Maxim Integrated Products, Inc.

#### **Features**

- 18-Bit Full-Scale Resolution

- 720nV<sub>RMS</sub> Noise (MAX11212B)

- 3ppm INL

- No Missing Codes

- Ultra-Low-Power Dissipation

- Operating-Mode Current Drain < 300µA (max)

- Sleep-Mode Current Drain < 0.1µA

- 2.7V to 3.6V Analog Supply Voltage Range

- 1.7V to 3.6V Digital and I/O Supply Voltage Range

- · Fully Differential Signal Inputs

- Fully Differential Reference Inputs

- Internal System Clock

- 2.4576MHz (MAX11212A)

- 2.2528MHz (MAX11212B)

- External Clock

- Serial 2-Wire Interface (Clock Input and Data Output)

- On-Demand Offset and Gain Self-Calibration

- -40°C to +85°C Operating Temperature Range

- ±2kV ESD Protection

- Lead(Pb)-Free and RoHS-Compliant μMAX Package

### **Absolute Maximum Ratings**

| Any Pin to GND0.3V to +3.9                          | V Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|-----------------------------------------------------|---------------------------------------------------------|

| AVDD to GND0.3V to +3.9                             | V 10-Pin μMAX (derate 5.6mW/°C above +70°C)444mW        |

| DVDD to GND0.3V to +3.9                             | Operating Temperature Range40°C to +85°C                |

| Analog Inputs (AINP, AINN, REFP, REFN)              | Junction Temperature+150°C                              |

| to GND0.3V to (V <sub>AVDD</sub> + 0.3V             | V) Storage Temperature Range55°C to +150°C              |

| Digital Inputs and Digital Outputs                  | Lead Temperature (soldering, 10s)+300°C                 |

| to GND0.3V to (V <sub>DVDD</sub> + 0.3V             | V) Soldering Temperature (reflow)+260°C                 |

| ESDHB (AVDD, AINP, AINN, REFP, REFN, DVDD, CLK, SCL | K,                                                      |

| RDY/DOUT, GND)±2kV (Note                            | 1)                                                      |

Note 1: Human Body Model to specification MIL-STD-883 Method 3015.7.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| PACKAGE TYPE: 10 μMAX |                |  |

|-----------------------|----------------|--|

| Package Code          | U10+2          |  |

| Outline Number        | <u>21-0061</u> |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

#### **Electrical Characteristics**

$(V_{AVDD} = +3.6V, V_{DVDD} = +1.8V, V_{REFP} - V_{REFN} = V_{AVDD})$ ; internal clock,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C under normal conditions, unless otherwise noted.)

| PARAMETER                     | SYMBOL           | CONDITIONS                                                               | MIN | TYP  | MAX | UNITS             |

|-------------------------------|------------------|--------------------------------------------------------------------------|-----|------|-----|-------------------|

| ADC PERFORMANCE               |                  |                                                                          |     |      |     |                   |

| Noise-Free Resolution         | NFR              | (Notes 2, 3)                                                             |     | 18   |     | Bits              |

| Thermal Naise (Natas 2, 2)    | \                | MAX11212A                                                                |     | 2.1  |     | μV <sub>RMS</sub> |

| Thermal Noise (Notes 2, 3)    | V <sub>N</sub>   | MAX11212B                                                                |     | 0.72 |     |                   |

| Integral Nonlinearity         | INL              | (Note 4)                                                                 | -10 |      | +10 | ppmFSR            |

| Zero Error                    | V <sub>OFF</sub> | After calibration, V <sub>REFP</sub> - V <sub>REFN</sub> = 2.5V          | -20 | 1    | +20 | ppmFSR            |

| Zero Drift                    |                  |                                                                          |     | 50   |     | nV/°C             |

| Full-Scale Error              |                  | After calibration, V <sub>REFP</sub> - V <sub>REFN</sub> = 2.5V (Note 5) | -35 | 3    | +35 | ppmFSR            |

| Full-Scale Error Drift        |                  |                                                                          |     | 0.05 |     | ppmFSR/°C         |

| Danier Committee Datie attack |                  | AVDD DC rejection                                                        | 70  | 80   |     | 40                |

| Power-Supply Rejection        |                  | DVDD DC rejection                                                        | 90  | 100  |     | - dB              |

### **Electrical Characteristics (continued)**

$(V_{AVDD}$  = +3.6V,  $V_{DVDD}$  = +1.8V,  $V_{REFP}$  -  $V_{REFN}$  =  $V_{AVDD}$ ; internal clock,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A$  = +25°C under normal conditions, unless otherwise noted.)

| PARAMETER                         | SYMBOL            | CONDITIONS                                                      | MIN                        | TYP                         | MAX                                   | UNITS |  |

|-----------------------------------|-------------------|-----------------------------------------------------------------|----------------------------|-----------------------------|---------------------------------------|-------|--|

| ANALOG INPUTS/REFERENCE I         | NPUTS             |                                                                 |                            |                             |                                       |       |  |

|                                   |                   | DC rejection                                                    | 90                         | 123                         |                                       |       |  |

| Common-Mode Rejection             | CMR               | 50Hz/60Hz rejection MAX11212A                                   | 90                         |                             |                                       | dB    |  |

|                                   |                   | 50Hz/60Hz rejection MAX11212B                                   | 144                        |                             |                                       |       |  |

| Normal-Mode 50Hz Rejection        | NMR <sub>50</sub> | MAX11212B (Note 6)                                              | 65                         | 80.5                        |                                       | dB    |  |

| Normal-Mode 60Hz Rejection        | NMR <sub>60</sub> | MAX11212B (Note 6)                                              | 73                         | 87                          |                                       | dB    |  |

| Common-Mode Voltage Range         |                   |                                                                 | GND                        |                             | V <sub>AVDD</sub>                     | V     |  |

| Absolute Input Voltage            |                   | Low input voltage GND - 30mV                                    |                            |                             | · · · · · · · · · · · · · · · · · · · |       |  |

| Absolute input voltage            |                   | High input voltage                                              |                            | V <sub>AVDD</sub> +<br>30mV |                                       | V     |  |

| DC Input Leakage                  |                   | Sleep mode (Note 2)                                             |                            | ±1                          |                                       | μΑ    |  |

| AIN Dynamic Input Current         |                   |                                                                 |                            | 5                           |                                       | μΑ    |  |

| REF Dynamic Input Current         |                   |                                                                 |                            | 7.5                         |                                       | μA    |  |

| AIN Input Capacitance             |                   |                                                                 |                            | 10                          |                                       | pF    |  |

| REF Input Capacitance             |                   |                                                                 |                            | 15                          |                                       | pF    |  |

| AIN Voltage Range                 |                   | VAINP - VAINN                                                   | -V <sub>REF</sub>          |                             | +V <sub>REF</sub>                     | V     |  |

| REF Voltage Range                 |                   |                                                                 |                            |                             | V <sub>AVDD</sub>                     | V     |  |

| lament Camardia a Data            |                   | MAX11212A                                                       |                            | 246                         |                                       | 1.11= |  |

| Input Sampling Rate               | f <sub>S</sub>    | MAX11212B                                                       |                            | 225                         |                                       | kHz   |  |

| DEE Committee Dete                |                   | MAX11212A                                                       |                            | 246                         |                                       | 1.11- |  |

| REF Sampling Rate                 |                   | MAX11212B                                                       |                            | 225                         |                                       | kHz   |  |

| LOGIC INPUTS (SCLK, CLK)          | •                 |                                                                 |                            |                             |                                       |       |  |

| Input Current                     |                   | Input leakage current                                           |                            | ±1                          |                                       | μA    |  |

| Input Low Voltage                 | V <sub>IL</sub>   |                                                                 |                            |                             | 0.3 x<br>V <sub>DVDD</sub>            | V     |  |

| Input High Voltage                | V <sub>IH</sub>   |                                                                 | 0.7 x<br>V <sub>DVDD</sub> |                             |                                       | V     |  |

| nput Hysteresis                   | V <sub>HYS</sub>  |                                                                 |                            | 200                         |                                       | mV    |  |

| External Clock                    |                   | MAX11212A                                                       |                            | 2.4576                      |                                       | MHz   |  |

| External Clock                    |                   | MAX11212B                                                       |                            | 2.2528                      |                                       |       |  |

| LOGIC OUTPUTS (RDY/DOUT)          |                   |                                                                 |                            | _                           |                                       |       |  |

| Output Low Level                  | V <sub>OL</sub>   | I <sub>OL</sub> = 1mA; also tested for V <sub>DVDD</sub> = 3.6V |                            |                             | 0.4                                   | V     |  |

| Output High Level                 | V <sub>OH</sub>   | I <sub>OH</sub> = 1mA; also tested for V <sub>DVDD</sub> = 3.6V | 0.9 x<br>V <sub>DVDD</sub> |                             |                                       | V     |  |

| Floating State Leakage Current    |                   | Output leakage current                                          |                            | ±10                         |                                       | μA    |  |

| Floating State Output Capacitance |                   |                                                                 |                            | 9                           |                                       | pF    |  |

# **Electrical Characteristics (continued)**

$(V_{AVDD}$  = +3.6V,  $V_{DVDD}$  = +1.8V,  $V_{REFP}$  -  $V_{REFN}$  =  $V_{AVDD}$ ; internal clock,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A$  = +25°C under normal conditions, unless otherwise noted.)

| PARAMETER                                                 | SYMBOL            | CONDITIONS                         | MIN | TYP   | MAX | UNITS |  |

|-----------------------------------------------------------|-------------------|------------------------------------|-----|-------|-----|-------|--|

| POWER REQUIREMENTS                                        |                   |                                    | '   |       |     |       |  |

| Analog Supply Voltage                                     | AVDD              |                                    | 2.7 |       | 3.6 | V     |  |

| Digital Supply Voltage                                    | DVDD              |                                    | 1.7 |       | 3.6 | V     |  |

| Total Operating Current                                   |                   | AVDD + DVDD                        |     | 230   | 300 | μA    |  |

| DVDD Operating Current                                    |                   |                                    |     | 45    | 60  | μA    |  |

| AVDD Operating Current                                    |                   |                                    |     | 185   | 245 | μA    |  |

| AVDD Sleep Current                                        |                   |                                    |     | 0.4   | 2   | μA    |  |

| DVDD Sleep Current                                        |                   |                                    |     | 0.35  | 2   | μA    |  |

| 2-WIRE SERIAL-INTERFACE TIM                               | ING CHAR          | ACTERISITCS                        |     |       |     |       |  |

| SCLK Frequency                                            | f <sub>SCLK</sub> |                                    |     |       | 5   | MHz   |  |

| SCLK Pulse Width Low                                      | t <sub>1</sub>    | 60/40 duty cycle 5MHz clock        | 80  |       |     | ns    |  |

| SCLK Pulse Width High                                     | t <sub>2</sub>    | 40/60 duty cycle 5MHz clock        | 80  |       |     | ns    |  |

| SCLK Rising Edge to Data Valid<br>Transition Time         | t <sub>3</sub>    |                                    |     |       | 40  | ns    |  |

| SCLK Rising Edge Data Hold Time                           | t <sub>4</sub>    | Allows for positive edge data read | 3   |       |     | ns    |  |

| RDY/DOUT Fall to SCLK Rising Edge                         | t <sub>5</sub>    |                                    | 0   |       |     | ns    |  |

| Next Data Update Time; No Read                            | 'a   te           | MAX11212A                          |     | 155   |     |       |  |

| Allowed                                                   |                   | MAX11212B                          |     | 169   |     | μs    |  |

| Data Cananaian Tima                                       | 4                 | MAX11212A                          |     | 8.6   |     |       |  |

| Data Conversion Time                                      | t <sub>7</sub>    | MAX11212B                          |     | 73    |     | ms    |  |

| Data Ready Time After Calibration                         |                   | MAX11212A                          |     | 208.3 |     |       |  |

| Starts (CAL + CNV)                                        | t <sub>8</sub>    | MAX11212B                          |     | 256.1 |     | ms    |  |

| SCLK High After RDY/DOUT                                  | 4                 | MAX11212A                          | 0   |       | 8.6 | mo    |  |

| Goes Low to Activate Sleep Mode                           | tg                | MAX11212B                          | 0   |       | 73  | ms    |  |

| Time From RDY/DOUT Low to SCLK High for Sleep Mode        | <b>.</b>          | MAX11212A                          | 0   |       | 8.6 | mo    |  |

| Activation                                                | t <sub>10</sub>   | MAX11212B                          | 0   |       | 73  | ms    |  |

| Data Ready Time After Wake-Up                             | 4                 | MAX11212A                          |     | 8.6   |     | ma    |  |

| from Sleep Mode                                           | t <sub>11</sub>   | MAX11212B                          |     | 73    |     | ms    |  |

| Data Ready Time After Calibration from Sleep Mode Wake-Up | tuo               | MAX11212A                          |     | 208.4 |     |       |  |

| (CAL + CNV)                                               | t <sub>12</sub>   | MAX11212B                          |     | 256.2 |     | ms    |  |

Note 2: These specifications are not fully tested and are guaranteed by design and/or characterization.

**Note 3:**  $V_{AINP} = V_{AINN}$ .

Note 4: ppmFSR is parts per million of full-scale range.

Note 5: Positive full-scale error includes zero-scale errors.

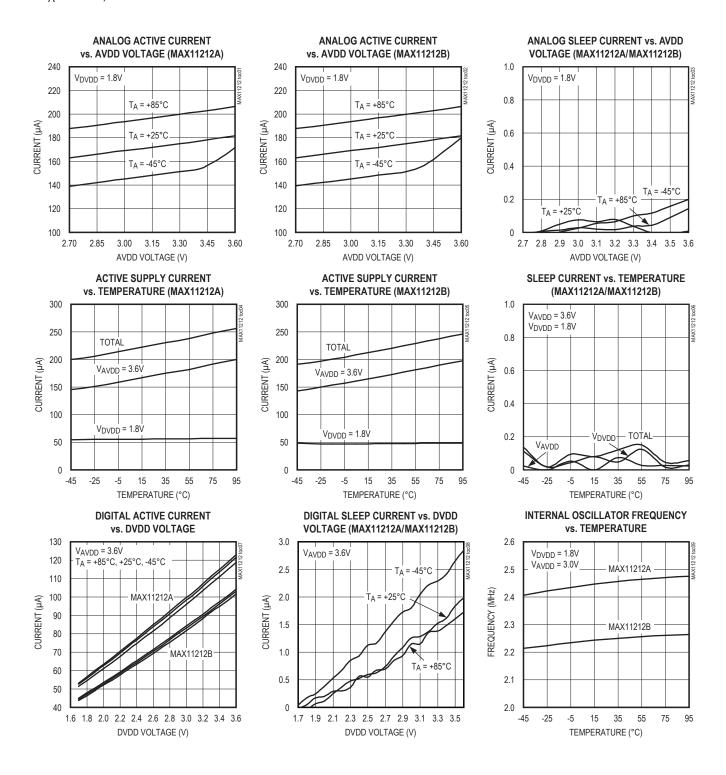

### **Typical Operating Characteristics**

$(V_{AVDD} = 3.6V, V_{DVDD} = 1.8V, V_{REFP} - V_{REFN} = V_{AVDD}$ ; internal clock;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

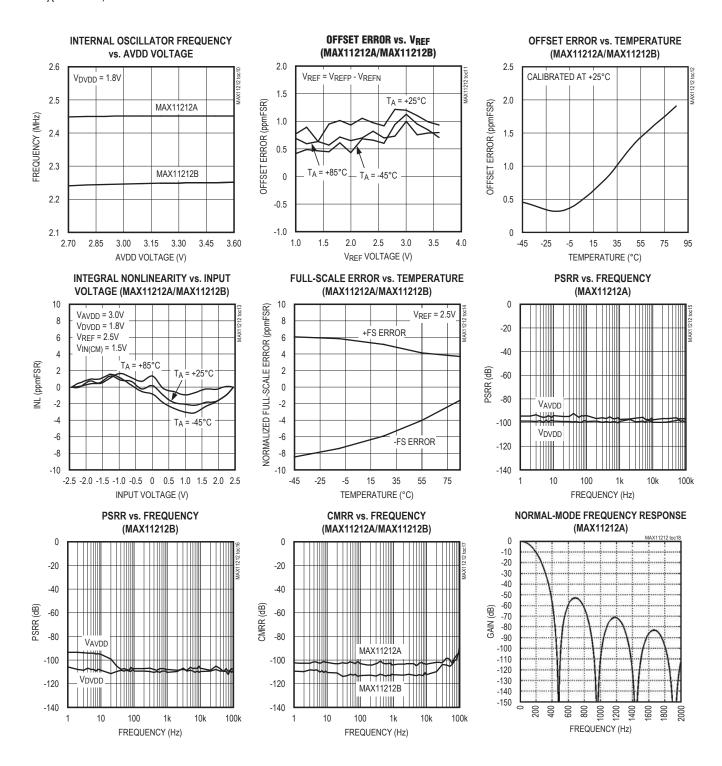

### **Typical Operating Characteristics (continued)**

$(V_{AVDD} = 3.6V, V_{DVDD} = 1.8V, V_{REFP} - V_{REFN} = V_{AVDD}$ ; internal clock;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

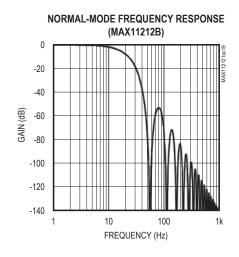

# **Typical Operating Characteristics (continued)**

$(V_{AVDD} = 3.6V, V_{DVDD} = 1.8V, V_{REFP} - V_{REFN} = V_{AVDD};$  internal clock;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

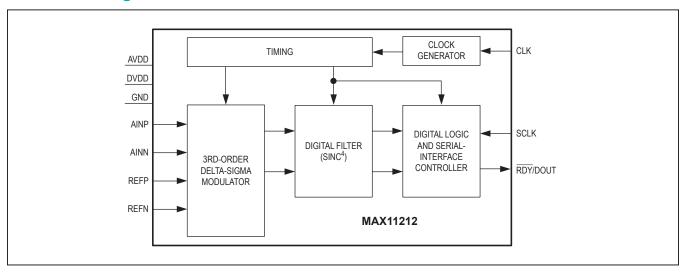

### **Functional Diagram**

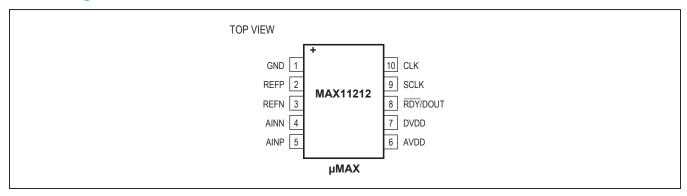

# **Pin Configuration**

# **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                        |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND      | Ground. Ground reference for analog and digital circuitry.                                                                                                                                                                                                                                                                      |

| 2   | REFP     | Differential Reference Positive Input. REFP must be more positive than REFN. Connect REFP to a voltage between AVDD and GND.                                                                                                                                                                                                    |

| 3   | REFN     | Differential Reference Negative Input. REFN must be more negative than REFP. Connect REFN to a voltage between AVDD and GND.                                                                                                                                                                                                    |

| 4   | AINN     | Negative Fully Differential Analog Input                                                                                                                                                                                                                                                                                        |

| 5   | AINP     | Positive Fully Differential Analog Input                                                                                                                                                                                                                                                                                        |

| 6   | AVDD     | Analog Supply Voltage. Connect a supply voltage between +2.7V to +3.6V with respect to GND.                                                                                                                                                                                                                                     |

| 7   | DVDD     | Digital Supply Voltage. Connect a digital supply voltage between +1.7V to +3.6V with respect to GND.                                                                                                                                                                                                                            |

| 8   | RDY/DOUT | Data-Ready Output/Serial-Data Output. This output serves a dual function. In addition to the serial-data output function, the $\overline{\text{RDY}}/\text{DOUT}$ also indicates that the data is ready when the $\overline{\text{RDY}}$ is logic-low. $\overline{\text{RDY}}/\text{DOUT}$ changes on the falling edge of SCLK. |

| 9   | SCLK     | Serial-Clock Input. Apply an external serial clock to SCLK.                                                                                                                                                                                                                                                                     |

| 10  | CLK      | External Clock Signal Input. The internal clock shuts down when CLK is driven by an external clock. Use a 2.4576MHz oscillator (MAX11212A) or a 2.2528MHz oscillator (MAX11212B).                                                                                                                                               |

### **Detailed Description**

The MAX11212 is an ultra-low-power (<  $240\mu A$  active), high-resolution, low-speed, serial-output ADC. This device provides the highest resolution per unit power in the industry, and is optimized for applications that require very high dynamic range with low power such as sensors on a 4mA to 20mA industrial control loop. The MAX11212 provides a high-accuracy internal oscillator, which requires no external components. When used with the specified data rates, the internal digital filter provides more than 80dB rejection of 50Hz or 60Hz line noise. The MAX11212 provides a simple, system-friendly, 2-wire serial interface in the space-saving, 10-pin  $\mu$ MAX package.

#### Power-On Reset (POR)

The MAX11212 utilizes power-on reset (POR) supplymonitoring circuitry on both the digital supply (DVDD) and the analog supply (AVDD). The POR circuitry ensures proper device default conditions after either a digital or analog power-sequencing event.

The MAX11212 performs a self-calibration operation as part of the startup initialization sequence whenever a digital POR is triggered. It is important to have a stable reference voltage available at the REFP and REFN pins to ensure an accurate calibration cycle. If the reference voltage is not stable during a POR event, the part should be calibrated once the reference has stabilized. The part can be programmed for calibration by using 26 SCLKs as shown in Figure 3.

The digital POR trigger threshold is approximately 1.2V and has 100mV of hysteresis. The analog POR trigger threshold is approximately 1.25V and has 100mV of hysteresis. Both POR circuits have lowpass filters that prevent high-frequency supply glitches from triggering the POR. The analog supply (AVDD) and the digital supply (DVDD) pins should be bypassed using 0.1µF capacitors placed as close as possible to the package pin.

#### **Analog Inputs**

The MAX11212 accepts two analog inputs (AINP and AINN). The modulator input range is bipolar (- $V_{REF}$  to + $V_{REF}$ ).

#### **Internal Oscillator**

The MAX11212 incorporates a highly stable internal oscillator that provides the system clock. The system clock runs the internal state machine and is trimmed to

2.4576MHz (MAX11212A) or 2.2528MHz (MAX11212B). The internal oscillator clock is divided down to run the digital and analog timing.

#### Reference

The MAX11212 provides differential inputs REFP and REFN for an external reference voltage. Connect the external reference directly across REFP and REFN to obtain the differential reference voltage. The commonmode voltage range for  $V_{REFP}$  and  $V_{REFN}$  is between 0 and  $V_{AVDD}$ . The differential voltage range for REFP and REFN is 1V to  $V_{AVDD}$ .

#### **Digital Filter**

The MAX11212 contains an on-chip, digital lowpass filter that processes the 1-bit data stream from the modulator using a SINC<sup>4</sup> (sinx/x)<sup>4</sup> response. When the device is operating in single-cycle conversion mode, the filter is reset at the end of the conversion cycle. When operating in continuous conversion latent mode, the filter is not reset. The SINC<sup>4</sup> filter has a -3dB frequency equal to 24% of the data rate.

#### **Serial-Digital Interface**

The MAX11212 communicates through a 2-wire serial interface with a clock input and data output. The output rate is predetermined based on the package option (MAX11212A at 120sps and MAX11212B at 13.75sps).

#### 2-Wire Interface

The MAX11212 is compatible with the 2-wire interface and uses SCLK and  $\overline{RDY}/DOUT$  for serial communications. In this mode, all controls are implemented by timing the high or low phase of the SCLK. The 2-wire serial interface only allows for data to be read out through the  $\overline{RDY}/DOUT$  output. Supply the serial clock to SCLK to shift the conversion data out.

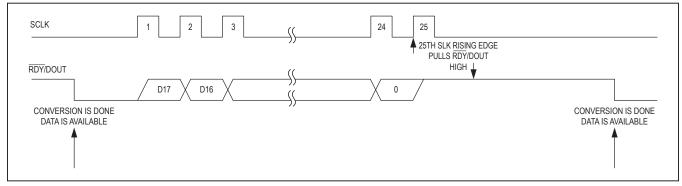

The RDY/DOUT is used to signal data ready, as well as reading the data out when SCLK pulses are applied. RDY/DOUT is high by default. The MAX11212 pulls RDY/DOUT low when data is available at the end of conversion, and stays low until clock pulses are applied at SCLK input; on applying the clock pulses at SCLK, the RDY/DOUT outputs the conversion data on every SCLK positive edge. To monitor data availability, pull RDY/DOUT high after reading the 18 bits of data by supplying a 25th SCLK pulse.

The different operational modes using this 2-wire interface are described in the following sections.

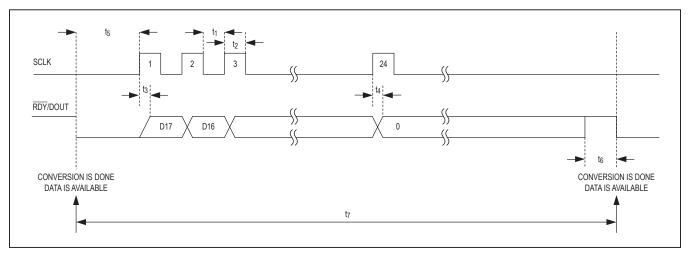

### **Data Read Following Every Conversion**

The MAX11212 indicates conversion data availability as well as allows the retrieval of data through the  $\overline{RDY}/DOUT$  output. The  $\overline{RDY}/DOUT$  output idles at the value of the last bit read unless a 25th SCLK pulse is provided, causing  $\overline{RDY}/DOUT$  to idle high.  $\overline{RDY}/DOUT$  is pulled low when the conversion data is available.

Figure 1 shows the timing diagram for the data read. Once a low is detected on RDY/DOUT, clock pulses at SCLK clock out the data. Data is shifted out MSB first and is in binary two's complement format. Once all the data has been shifted out, a 25th SCLK is required to pull the RDY/DOUT output back to the idle high state. See Figure 2.

If the data is not read before the next conversion data is updated, the old data is lost, as the new data overwrites the old value.

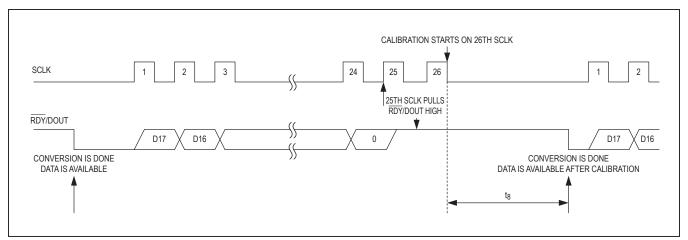

#### **Data Read Followed by Self-Calibration**

To initiate self-calibration at the end of a data read, provide a 26th SCLK pulse. After reading the 16 bits of conversion data, a 25th positive edge on SCLK pulls the  $\overline{RDY}/DOUT$  output back high, indicating end of data read. Provide a 26th SCLK pulse to initiate a self-calibration routine starting on the falling edge of the 26th SCLK. A subsequent falling edge of  $\overline{RDY}/DOUT$  indicates data availability at the end of calibration. The timing is illustrated in Figure 3.

Figure 1. Timing Diagram for Data Read After Conversion

Figure 2. Timing Diagram for Data Read Followed by RDY/DOUT Being Asserted High Using 25th SCLK

Figure 3. Timing Diagram for Data Read Followed by Two Extra Clock Cycles for Self-Calibration

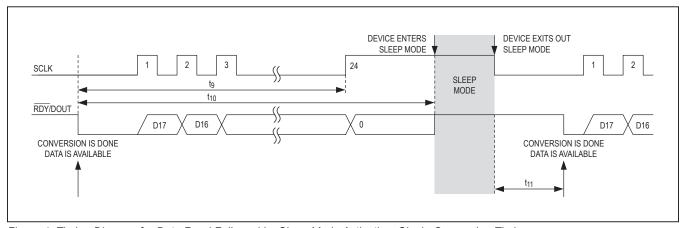

Figure 4. Timing Diagram for Data Read Followed by Sleep Mode Activation; Single-Conversion Timing

#### Data Read Followed by Sleep Mode

The MAX11212 can be put into sleep mode to save power between conversions. To activate the sleep mode, idle the SCLK high any time after the  $\overline{\text{RDY}}/\text{DOUT}$  output goes low (that is, after conversion data is available). It is not required to read out all 18 bits before putting the part in sleep mode. Sleep mode is activated after the SCLK is held high (see  $\overline{\text{Figure 4}}$ ). The  $\overline{\text{RDY}}/\text{DOUT}$  output is pulled high once the device enters sleep mode. To come out of sleep mode, pull SCLK low. After the sleep mode

is deactivated (when the device wakes up), conversion starts again and  $\overline{RDY}/DOUT$  goes low, indicating the next conversion data is available. See Figure 4.

#### **Single-Conversion Mode**

For operating the MAX11212 in single-conversion mode, activate and deactivate sleep mode between conversions as described in the *Data Read Followed by Sleep Mode* section). Single-conversion mode reduces power consumption by shutting down the device when idle between conversions. See Figure 4.

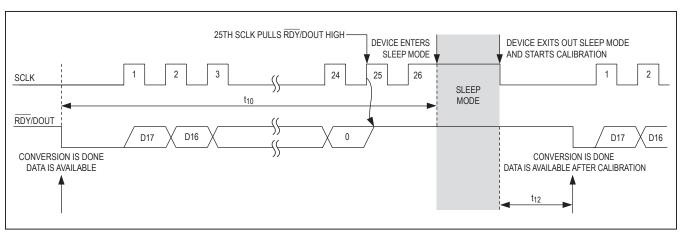

# Single-Conversion Mode with Self-Calibration at Wake-Up

The MAX11212 can be put in self-calibration mode immediately after wake-up from sleep mode. Self-calibration at wake-up helps to compensate for temperature or supply changes if the device is shut down for extensive periods. To automatically start self-calibration at the end of sleep mode, all the data bits must be shifted out followed by 25th SCLK edge to pull  $\overline{RDY}/DOUT$  high, and then on the 26th SCLK keep it high for as long as shutdown is

desired. Once SCLK is pulled back low, the device automatically performs a self-calibration and, when the data is ready, the RDY/DOUT output goes low. See Figure 5. This also achieves the purpose of single conversions with self-calibration.

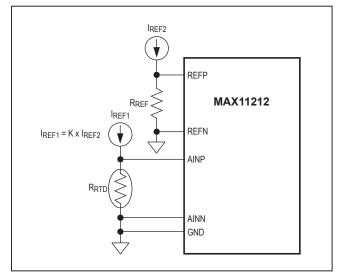

### **Applications Information**

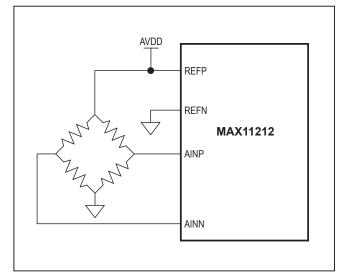

See <u>Figure 6</u> for the RTD temperature measurement circuit and <u>Figure 7</u> for a resistive bridge measurement circuit

Figure 5. Timing Diagram for Sleep Mode Activation Followed by Self-Calibration at Wake-Up

Figure 6. RTD Temperature Measurement Circuit

Figure 7. Resistive Bridge Measurement Circuit

### **Selector Guide**

| RESOLUTION<br>(BITS) | 4-WIRE SPI, 16-PIN QSOP,<br>PROGRAMMABLE GAIN | 4-WIRE SPI,<br>16-PIN QSOP | 2-WIRE SERIAL,<br>10-PIN μΜΑΧ                      |

|----------------------|-----------------------------------------------|----------------------------|----------------------------------------------------|

| 24                   | MAX11210                                      | MAX11200                   | MAX11201 (with buffers) MAX11202 (without buffers) |

| 20                   | MAX11206                                      | MAX11207                   | MAX11208                                           |

| 18                   | MAX11209                                      | MAX11211                   | MAX11212                                           |

| 16                   | MAX11213                                      | MAX11203                   | MAX11205                                           |

### **Ordering Information**

| PART           | PIN-PACKAGE | OUTPUT RATE<br>(sps) |

|----------------|-------------|----------------------|

| MAX11212AEUB+* | 10 μMAX     | 120                  |

| MAX11212BEUB+  | 10 μMAX     | 13.75                |

**Note:** All devices are specified over the -40°C to +85°C operating temperature range.

### **Chip Information**

PROCESS: BICMOS

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>Future product—contact factory for availability.

### MAX11212

# 18-Bit, Single-Channel, Ultra-Low Power, Delta-Sigma ADC with 2-Wire Serial Interface

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 4/10             | Initial release | _                |

| 1                  | 8/18             | Replaced TOC18  | 6                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.