SLUS565F - JULY 2003 - REVISED DECEMBER 2004

### OCTAL POWER SOURCING EQUIPMENT POWER MANAGER

### FEATURES

- Compliant to Power Over Ethernet IEEE 802.3af Standard

- Two-Point 25-kΩ Resistor Discovery

- Capacitive Detection for Non-Compliant Legacy Loads

- Power Classification

- Controlled di/dt Ramp Power-Up and Power-Down for EMI Reduction

- Current Management for Charging Powered Device Bulk Capacitance

- Electronic Circuit Breaker

- Fault detection

- Input Undervoltage Lockout (UVLO)

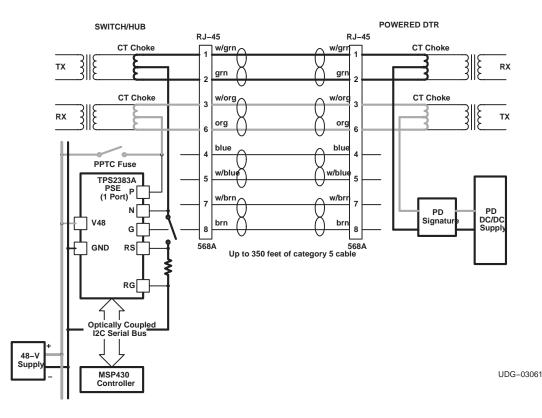

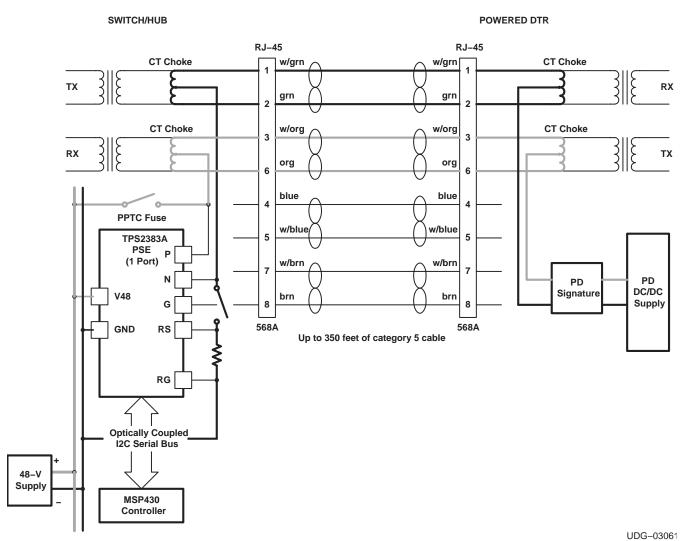

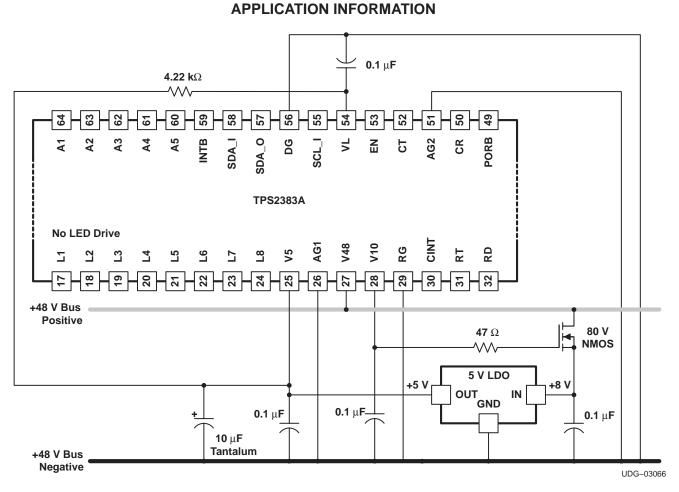

### **APPLICATION DIAGRAM**

- Load Overcurrent and Undercurrent Detection

- 12-Bit Port Current and Voltage Acquisition

- Standard Slave I<sup>2</sup>C Serial Interface

- 5-Bit Serial Address Selectability

- Discovery and/or Classification Bypass Modes Selectable Via Register

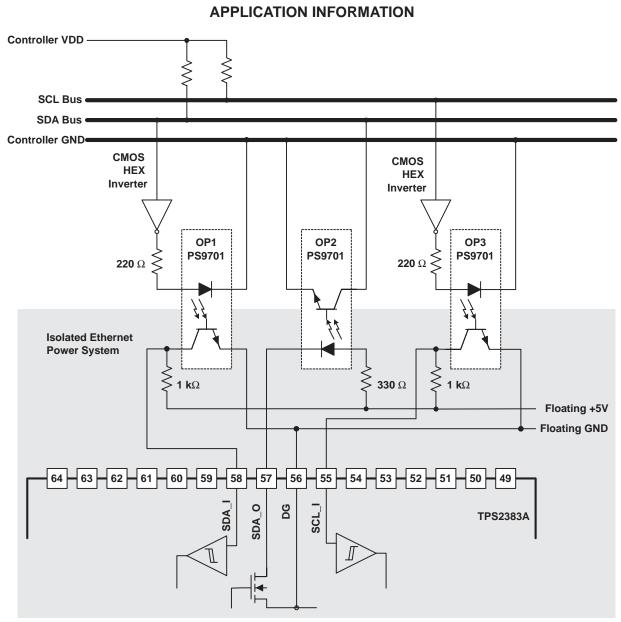

- Opto-Coupler Compatible SDA and SCL Lines for System Ground Isolation

- Dual Color LED Driver for Port Status

- Hardware FAULT Interrupt

### **APPLICATIONS**

- PoE Switches

- Mid-Span Injectors

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999 - 2008, Texas Instruments Incorporated

### DESCRIPTION

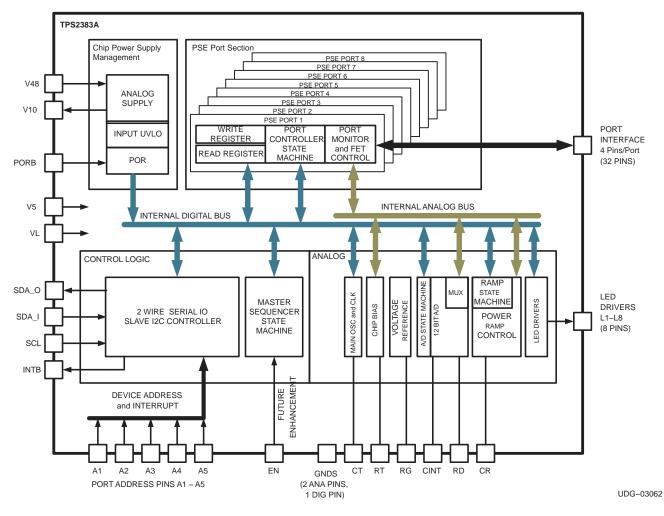

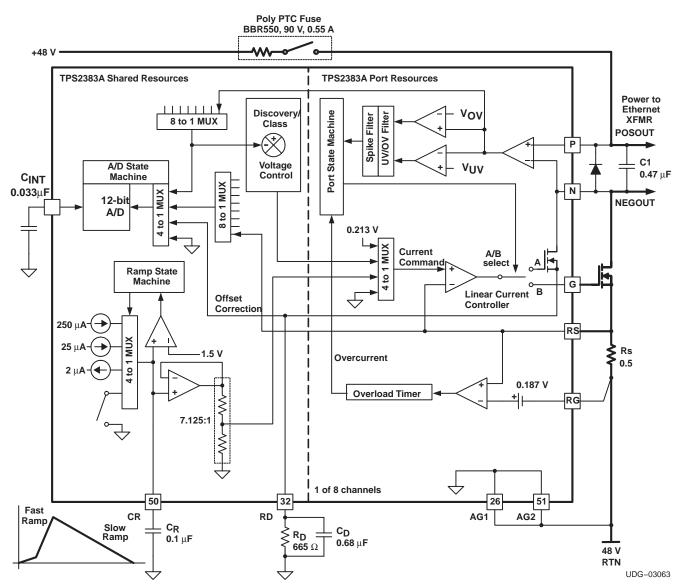

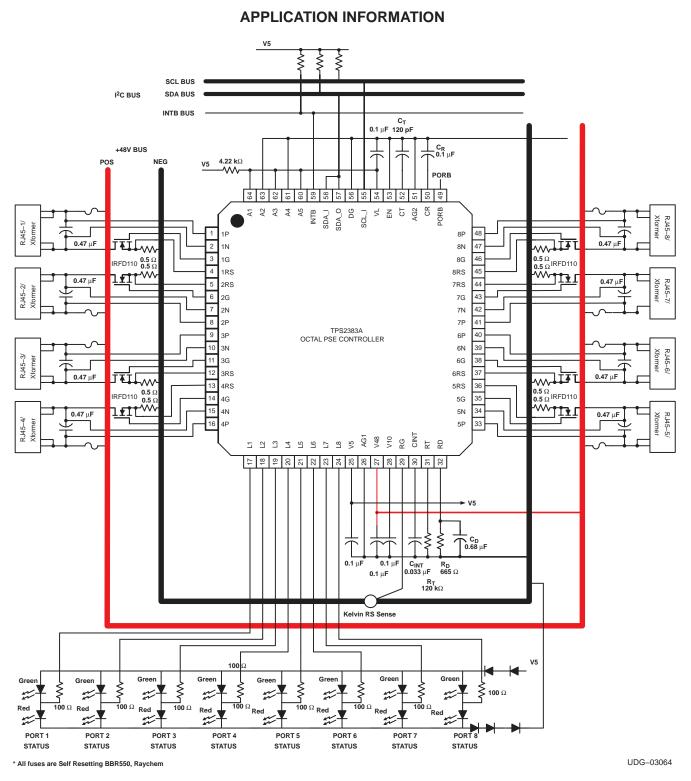

The TPS2383A and TPS2383B family of products are power sourcing equipment power managers (PSEPM) that are compliant to the power-over-ethernet (PoE) IEEE 802.3af Standard. The TPS2383A and the TPS2383B are pin-for-pin functionally equivalent products. A PSEPM port can discover, classify and deliver power to a powered device (PD) capable of accepting PoE twisted pair cable. The TPS2383A/B is fully programmable by the user. This allows for the detection and powering of both fully compliant 802.3 devices as well as custom detection of legacy devices.

The TPS2383A/B PSEPM can individually manage power for up to eight ethernet ports. All operations of the TPS2383A/B are controlled through register read and write operations over a standard (slave) I<sup>2</sup>C serial interface. The TPS2383A/B has dual SDA lines to allow easy application of opto-coupler circuitry to maintain ethernet port isolation when a ground based controller is used. Each TPS2383A/B has five selection pins making it possible to address up to 32 devices on the I<sup>2</sup>C bus and allows individual control and monitoring of up to 256 ethernet ports from a single master I<sup>2</sup>C controller. Per-port write registers initiate and manipulate the flow of the discovery, classification, and power-up states while the read registers contain status information of the enable process, faults, classification value, and real time port operating current and voltage. Per-port status LED drivers are provided which can be manually controlled through the serial I/O.

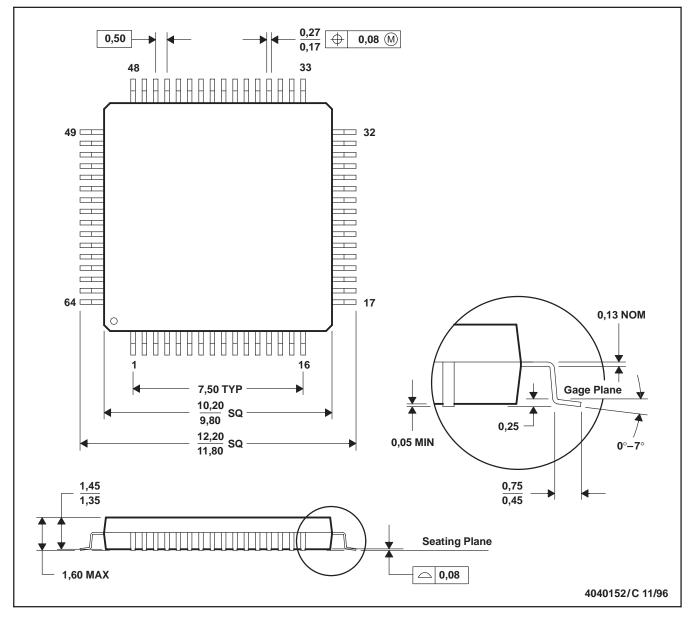

The TPS2383A/B is available in a full function 64-pin LQFP.

External N-channel MOSFETs switch port power. High-voltage (HV) gate drive ensures that these FETs are fully enhanced, resulting in lower power dissipation and enabling the use of lower costs FETs. The TPS2383A/B generates its HV gate supply from the 48-V port power, simplifying system power supply design. An external 3.3-V digital supply is also used. This supply can be active when 48-V power is not present which allows the user to access the part through the serial I/O in this case. A 5-V analog supply is used to power port LEDs and internal analog functions. Due to the very low quiescent current, both the 3.3-V and 5-V supply can be generated from the 48-V power bus with minimal external components. An internal power-on-reset (POR) circuit with an ORed external input pin resets all registers positions to a known safe state upon power up.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                               |                                                                                  | TPS2383A/B  | UNIT |  |

|-----------------------------------------------|----------------------------------------------------------------------------------|-------------|------|--|

|                                               | V48, 1P, 2P, 3P, 4P, 5P, 6P, 7P, 8P, 1N, 2N, 3N, 4N, 5N, 6N, 7N, 8N              | -0.5 to 80  |      |  |

|                                               | 1RS, 2RS, 3RS, 4RS, 5RS, 6RS, 7RS, 8RS, 1G, 2G, 3G, 4G, 5G, 6G, 7G, 8G, V10      | -0.5 to 12  | V    |  |

| Input voltage range, V <sub>CC</sub>          | VL                                                                               | -0.5 to 3.9 |      |  |

|                                               | V5                                                                               | -0.5 to 6   |      |  |

|                                               | SCL_I, SDA_I, SDA_O, INTB, A1, A2, A3, A4, A5, EN, PORB                          | -0.5 to 6   |      |  |

| Storage temperature, T <sub>Stg</sub>         | -55 to 150                                                                       |             |      |  |

| Operating temperature, TJ                     | -40 to 125                                                                       | °C          |      |  |

| Lead temperature, T <sub>SOI</sub> , 1,6 mm ( | Lead temperature, T <sub>SOI</sub> , 1,6 mm (1/16 inch) from case for 10 seconds |             |      |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into and negative out of, the specified terminal.

### **RECOMMENDED OPERATING CONDITIONS**

|                                   | MIN | NOM | MAX | UNIT |

|-----------------------------------|-----|-----|-----|------|

| Input voltage, V <sub>V48</sub>   | 44  | 48  | 57  | V    |

| Operating ambient temperature, Ta | -40 |     | 85  | °C   |

### **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                  | MAX | UNIT |

|------------------|-----|------|

| Human body model | 1.5 |      |

| CDM              | 1   | kV   |

| Machine model    | 0.2 |      |

### **ORDERING INFORMATION**

|               | PACKAGED DEVICES <sup>(2)</sup> |

|---------------|---------------------------------|

| TA            | LQFP–64<br>(PM)                 |

| 1000 10 0500  | TPS2383APM                      |

| –40°C to 85°C | TPS2383BPM                      |

(2) The PM package is available taped and reeled. Add R suffix to device type (e.g.TPS2383APMR) to order quantities of 2,500 devices per reel.

### **OPERATING TEMPERATURE RANGE**

| PACKAGE | <sup>θ</sup> jc | <sup>θ</sup> ja | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING<br>FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|-----------------|-----------------|---------------------------------------|---------------------------------------------------|---------------------------------------|

| LQFD-64 | 9°C/W           | 65°C/W          | 1.5 W                                 | 15.4 mW/°C                                        | 615<br>mW000000000000<br>000          |

SLUS565F - JULY 2003 - REVISED DECEMBER 2004

### **ELECTRICAL CHARACTERISTICS**

$V_{V48}\text{=}$  48 V, RT = 120 kΩ, –40°C to 85°C, and TA = TJ (unless otherwise noted)

| PARAMETER                                               | TEST CONDITIONS                                                           | MIN   | TYP   | MAX   | UNIT |

|---------------------------------------------------------|---------------------------------------------------------------------------|-------|-------|-------|------|

| POWER SUPPLIES                                          |                                                                           |       |       |       | -    |

|                                                         | Off mode (all ports)                                                      |       | 3     | 5     |      |

| Quiescent current, V48                                  | Powered mode (all ports)                                                  |       | 5     | 10    |      |

| Quiescent current, V5                                   | Powered mode (all ports), $V_{V5} = 5 V$                                  |       | 3     | 15    | mA   |

| Quiescent current, VL                                   | Powered mode (all ports), $V_{VL} = 3.3 V$                                |       | 0.28  | 4     |      |

| Internal analog supply, V10                             |                                                                           | 9.75  | 10.50 | 11.50 |      |

| Internal reference <sup>(1)</sup>                       |                                                                           | 2.475 | 2.500 | 2.525 | V    |

| Input UVLO                                              |                                                                           |       | 30    | 38    |      |

| Internal POR timeout (I <sup>2</sup> C)                 | After all supplies are good (8 CLK periods)                               |       | 8     |       |      |

| Internal POR timeout (state machine)                    | After all supplies are good (65536 CLK periods)                           |       | 65536 |       | CLKs |

| LED OUTPUTS                                             | •                                                                         | -     |       |       |      |

| High-level output voltage, L1 through L8                | I <sub>SRC</sub> = 5 mA                                                   | 4     |       |       |      |

| Low-level output voltage, L1 through L8                 | I <sub>SINK</sub> = 5 mA                                                  |       |       | 0.75  | V    |

| Tri-state leakage <sup>(1)</sup>                        |                                                                           |       | 0.1   |       | μA   |

| ANALOG CIRCUITS - PORT VOLTAGE CONTROL                  | LOOP                                                                      |       |       |       |      |

| Input resistance, nP to nN                              |                                                                           | 480   | 800   | 1280  | kΩ   |

| Classification voltage                                  | A/B select = B                                                            | 15.5  | 17.5  | 20.5  |      |

| Discovery voltage, high                                 |                                                                           | 7.5   | 8.8   | 9.5   | V    |

| Discovery voltage, low                                  |                                                                           | 3.5   | 4.4   | 5.5   |      |

| Loop power supply feedthru loop control range $C^{(1)}$ |                                                                           |       | 1.5   |       | mV   |

| Discovery short-circuit current                         |                                                                           |       |       | 3     | mA   |

| Port output, undervoltage                               |                                                                           | 40    | 42    | 44    |      |

| Port output, overvoltage                                |                                                                           | 56.0  | 59.5  | 63.0  | V    |

|                                                         | ClassLimit1 = 0, ClassLimit2 = 0                                          |       | 160   |       |      |

|                                                         | ClassLimit1 = 1, ClassLimit2 = 0                                          |       | 80    |       |      |

| Classification current limit                            | ClassLimit1 = 0, ClassLimit2 = 1                                          |       | 40    |       | mA   |

|                                                         | ClassLimit1 = 1, ClassLimit2 = 1                                          |       | 20    |       |      |

| N-CHANNEL MOSFET GATE CONTROL                           | •                                                                         | -     |       |       |      |

| Gate turn-off MOSFET RDS(on)                            |                                                                           |       | 200   |       | Ω    |

| Maximum gate voltage                                    |                                                                           | 8     | 10    | 12    | V    |

| Gate turn-off timer from UV/OV fault                    | After port enabled and ramped up,<br>(1024 CLK periods)                   |       | 1024  |       |      |

| UV/OV spike timer, power quality warning <sup>(1)</sup> | IV/OV spike timer, power quality warning <sup>(1)</sup> (256 CLK periods) |       |       |       | CLKs |

| Gate turn-off timer from overload fault                 | (32768 CLK periods)                                                       |       | 32768 |       |      |

NOTE: (1) Ensured by design. Not production tested.

SLUS565F - JULY 2003 - REVISED DECEMBER 2004

### **ELECTRICAL CHARACTERISTICS**

$V_{V48}\text{=}$  48 V, RT = 120 kΩ, –40°C to 85°C, and TA = TJ (unless otherwise noted)

| PARAMETER                                                          | TEST CONDITIONS                                  | MIN | TYP  | MAX | UNIT     |  |

|--------------------------------------------------------------------|--------------------------------------------------|-----|------|-----|----------|--|

| LOW-SIDE CURRENT-SENSE                                             | •                                                | •   |      |     |          |  |

| Overload threshold voltage                                         |                                                  | 175 | 187  | 200 |          |  |

| Current limit threshold voltage                                    |                                                  | 200 | 213  | 225 | mV       |  |

| Maximum swing, CINT                                                |                                                  | 9   |      | 11  | V        |  |

| Reset voltage, CINT                                                |                                                  |     | 10   | 100 | mV       |  |

| Internal pull-up current, CINT                                     | V <sub>CINT</sub> < 1.25 V, A/D inputs = -100 mV |     | 850  |     | nA       |  |

| Maximum swing, CR                                                  |                                                  |     | 4.5  | 6.0 | V        |  |

| Input leakage, nRS                                                 |                                                  |     | 10   |     | μA       |  |

| ANALOG-TO-DIGITAL CONVERTER                                        | ÷                                                | •   |      |     | •        |  |

| A/D resistive scaling <sup>(1)</sup>                               | R <sub>RD</sub> = 1 kΩ                           |     | 72   |     | count/kΩ |  |

| Port-to-port resistance variation                                  | Referenced to port #1                            | -5% | 0%   | 5%  |          |  |

| A/D classificatin scaling <sup>(1)</sup>                           | $R_{RS} = 0.5 \Omega$                            |     | 35   |     |          |  |

| A/D load current scaling <sup>(1)</sup>                            | $R_{RS} = 0.5 \Omega$                            |     | 4.72 |     | count/m  |  |

| A/D load voltage scaling <sup>(1)</sup>                            |                                                  |     | 33.6 |     | count/V  |  |

|                                                                    | $I_{LOAD} = 50 \text{ mA},  R_{RS} = 0.5 \Omega$ |     | 236  |     |          |  |

| A/D load current conversion                                        | $I_{LOAD} = 300 \text{ mA}, R_{RS} = 0.5 \Omega$ |     | 1416 |     |          |  |

|                                                                    | V <sub>PORT</sub> = 5 V                          |     | 168  |     | count    |  |

| A/D port voltage conversion                                        | V <sub>PORT</sub> = 45 V                         |     | 1512 |     | 1        |  |

| DIGITAL I/O                                                        | •                                                | •   |      |     | •        |  |

| Logic input threshold voltage, SCL, SDA_I, A1 through A5, EN, PORB |                                                  |     | 1.5  |     | V        |  |

| Input hysteresis, SCL, SDA_I                                       |                                                  |     | 250  |     |          |  |

| Input hysteresis, EN, PORB                                         |                                                  |     | 150  |     | mV       |  |

| Input pull-down resistance, EN, PORB                               |                                                  |     | 50   |     | kΩ       |  |

| Pull-up current, A0, A1, A2, A3, A4, A5                            |                                                  |     | 10   | 25  |          |  |

| Logic high leakage, SDA_O                                          | Drain = 6 V                                      |     | 10   |     | μΑ       |  |

| Logic low output voltage, SDA_O                                    | ISINK = 3 mA                                     |     | 200  |     | mV       |  |

| Logic high leakage, INTB                                           | Drain = 6 V                                      |     | 10   |     | μΑ       |  |

| Logic low output voltage, INTB                                     | I <sub>SINK</sub> = 3 mA                         |     | 200  |     | mV       |  |

| DIGITAL I/O TIMING I <sup>2</sup> C CHARACTERISTICS                | 5                                                |     |      |     | -        |  |

| Clock frequency, SCL                                               |                                                  | 0   |      | 400 | kHz      |  |

|                                                                    | SCL high                                         | 1.3 |      |     |          |  |

| Pulse duration                                                     | SCL low                                          | 0.6 |      |     | μs       |  |

| Rise time, SCL, SDA <sup>(1)</sup>                                 |                                                  |     |      | 300 |          |  |

| Fall time, SCL, SDA <sup>(1)</sup>                                 |                                                  |     |      | 300 |          |  |

| Setup time SDA to SCL                                              |                                                  | 250 |      |     | ns       |  |

| Hold time SCL to SDA                                               |                                                  | 0   |      |     |          |  |

| Bus free time between startup and stop                             |                                                  | 1.3 |      |     |          |  |

| Setup time SCL to start condition                                  |                                                  | 0.6 |      |     |          |  |

| Hold time start condition to SCL                                   |                                                  | 0.6 |      |     | μs       |  |

| Setup time, SCL to stop condition                                  |                                                  | 0.6 |      |     | ]        |  |

NOTE: (1) Ensured by design. Not production tested.

### **TERMINAL FUNCTIONS**

| AG2     and v10     Analog ground 2. Analog ground, which ties to the substrate and ESD of the device. It should be externally tie to the common copper 48-V return plane. AG1 and AG2 must be tied together directly for lowest noise operation.       DG     56     1     Digital ground. It connects to the internal logic ground bus. It should be externally tied to the common copper 48-V return plane. In addition a 0.1 uF de-coupling capacitor should terminate as close to this node and the VI pin as possible.       RG     29     1     Reference ground. A precision sense of the external ground plane. It should also be used as the ground guar ing for the integration capacitor (CINT). It should be to common copper 48-V return plane.       V10     28     0     +10V analog supply.Connects to the internal analog power bus. This voltage is generated internally. This pin should not be ide to any external supplies. A 0.1-µF de-coupling capacitor should terminate as close to this node and the AG2 pin as possible. This pin can be used for external generation of V5.       V48     27     1     +48V input to the device. This supply can have a range of 44 V to 57 V. This pin should be de-coupled with a 0.1-µF de-coupling capacitor should terminate as close to the internal analog ground terminate as close to the internal analog ground terminate as close to the internal analog group by. Visiting in as possible.       V5     25     1     External +5V analog supply.Connects to the internal analog grower bus. This supplies the LED output drivers and internal analog ground terminate as close to the indevice as possible.       V5     25     1     External +3.3V logic supply. This pin connects to the internal logic p               | TERMIN   | AL               |        |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| AG1         26         I         Analog ground 1. Analog ground of the V5, V10 and V48 power systems. It should be externally tied to the common copper 48-V return plane. This pin should carry the low side of two de-coupling capacitors tied to V4 analog ground. Analog ground, which ties to the substrate and ESD of two de-coupling capacitors tied to V4           AG2         51         I         Analog ground 2. Analog ground, which ties to the substrate and ESD of two de-coupling capacitors to to the common copper 48-V return plane. AG1 and AG2 must be tied together directly for lowest noise operation.           DG         56         I         Analog ground. It connects to the internal logic ground bus. It should be externally tied to the common copper 48-V return plane. In addition a 0.10F de-coupling capacitor should terminate as close to this node and the V1 pin as possible.           PG         29         I         Reference ground. A precision sense of the external ground plane. It should also be used as the ground guar ring for the integration capacitor (CINT), it should be to common copper 48-V return plane.           V10         28         O         +10V analog supply.Connects to the internal analog power bus. This voltage is generated internally. This pin should not be tied to any external supplies. A 0.1-1/F de-coupling capacitor should terminate as close to this node and the AC2 placed as close to the device as possible.           V48         27         I         +42V input to the device. This supply can have a range of 44 V to 57V. This pin should be de-coupled with a 0.1-1/F de-coupling capacitor should terminate as close to this node and the AC2 placed as close to the device as to this nod | NAME     | PIN              | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| AG1       26       1       common copper 48-V return plane. This pin should carry the low side of two de-coupling capacitors tied to V4 and V10         AG2       51       1       Analog ground 2. Analog ground, which ties to the substrate and ESD of the device. It should be externally tie to the common copper 48-V return plane. AG1 and AG2 must be tied together directly for lowest noise operation.         DG       56       1       AdaV return plane. In addition a 0.10F de-coupling capacitor should terminate as close to this node and the V1 pin as possible.         RG       29       1       Reference ground. A precision sense of the external ground plane. It should also be used as the ground guar ming for the integration capacitor (CINT). It should be the closest ground to the low side of the 0.5-0 current sense resistors, as well as RD. CINT, and RT. It should the tocommon copper 48-V return plane.         V10       28       0       1       448V return plane. This is stored to the internal analog power bus. This voltage is generated internally. This pin should new side of the 0.5-0 current sense resistors, as well as RD. CINT, and RT. It should the to common copper 48-V return plane.         V10       28       0       1       448V return the ada C2 pin as possible. This pin canalog opwer bus. This solutage is generated internally. This pin should new internal analog circuits. A 0.1-uF de-coupling capacitor should terminate as close to this node and the AC pin as possible.         V48       27       1       448 to 0.1-uF capacitor from V48 to AS2 placed as close to the internal alog to power bus. This supplies the LED output                                                                                 | POWER A  | POWER AND GROUND |        |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| AG2         51         1         to the čommon copper 48-V return plane. AG1 and AG2 must be tied together directly for lowest noise operation.           DG         56         1         Digital ground. It connects to the internal logic ground bus. It should be externally tied to the common copper 48-V return plane. In addition a 0.10 de-coupling capacitor should terminate as close to this node and the VI pin as possible.           RG         29         1         Reference ground. A precision sense of the external ground plane. It should also be used as the ground guar ring for the integration capacitor (CINT), the should be the coupling capacitor should terminate as close to this node and the VI pin as possible.           V10         28         0         Reference ground. A precision sense of the external ground plane. It should also be used as the ground guar ring for the integration capacitor (CINT), its hould be the coupling capacitor should terminate as close to this node and the AG2 pin as possible.           V10         28         0         +10V analog supply.Connects to the internal analog power bus. This solutage is generated internally. This pin code and the AG2 pin as possible.           V48         27         1         +48V input to the device. This supply can have a range of 44 V to 57 V. This pin should be de-coupled with a 0.1-µF capacitor from V48 to AG2 placed as close to the device as possible.           V5         25         1         External +3/3 V logic supply. Connects to the internal analog group bus. This sing the supply voltage for the pin as possible.           VL         54         <                                                                                               | AG1      | 26               | Ι      | common copper 48-V return plane. This pin should carry the low side of two de-coupling capacitors tied to V48                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| DG       56       I       48V return plane. In addition a 0.1uF de-coupling capacitor should terminate as close to this node and the VL pin as possible.         RG       29       I       Reference ground. A precision sense of the external ground plane. It should also be used as the ground guar ring for the integration capacitor (CINT). It should be the closest ground to the low side of the 0.5-0 current sense resistors, as well as RD, CINT, and RT. It should the to common copper 48-V return plane.         V10       28       0       +10V analog supply.Connects to the internal analog power bus. This voltage is generated internally. This pin should be de-coupling capacitor should terminate as close to this node and the AG2 pin as possible. This pin can be used for external generated internally. This pin should be de-coupled with a 0.1µF capacitor should terminate as close to this node and the AG2 pin as possible. This pin can be used for external generated internally. This pin should be de-coupled with a 0.1µF capacitor should terminate as close to this node and the AG pin as possible.         V48       27       1       +48V input to the device. This supply can have a range of 44 V to 57 V. This pin should be de-coupled with a 0.1µF capacitor should terminate as close to this node and the AG pin as possible.         V5       25       1       and internal analog circuits. A 0.1µF de-coupling capacitor should terminate as close to this node and the AG pin as possible.         VL       54       1       External +3.3V logic supply. Connects to the internal analog power bus. This supply capacitor should terminate as close to this node and the AG pin as possible. This pin can be powered from V5 by using         | AG2      | 51               | I      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| RG       29       1       ring for the integration capacitor (CINT). It should be the closest ground to the low side of the 0.5-Ω current sense resistors, as well as RD, CINT, and RT. It should tie to common copper 48-V return plane.         V10       28       0       +10V analog supply.Connects to the internal analog power bus. This voltage is generated internally. This pin node and the AG2 pin as possible. This pin can be used for external generation of V5.         V48       27       1       +48V input to the device. This supply can have a range of 44 V to 57. U. This pin should be de-coupled with a 0.1-µF capacitor from V48 to AG2 placed as close to the device as possible.         V5       25       1       External +5V analog supply.Connects to the internal analog power bus. This supplies the LED output drivers and internal analog circuits. A 0.1-µF de-coupling capacitor should terminate as close to this node and the AC pin as possible.         VL       54       1       External +5V analog supply.Connects to the internal analog power bus. This is the supply voltage for th internal device logic. A 0.1-µF de-coupling capacitor should terminate as close to this node and the AC pin as possible.         VL       54       1       External +3.3V logic supply. This pin connects to the internal togic power bus. This is the supply voltage for th internal device logic. A 0.1-µF de-coupling capacitor should terminate as close to this node and the AC pin as possible.         1P       1       1       Port positive. +48V load sense pin. Terminal voltage is monitored and controlled differentially with respect to 0.1-µF de-coupling capacities the lose of                                                                | DG       | 56               | I      | 48V return plane. In addition a 0.1 uF de-coupling capacitor should terminate as close to this node and the VL                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| V10       28       O       should not be ited to any external supplies. A 0.1-µE de-coupling capacitor should terminate as close to this node and the AG2 pin as possible. This pin can be used for external generation of V5.         V48       27       1       +48V input to the device. This supply can have a range of 44 V to 57 V. This pin should be de-coupled with a 0.1-µE capacitor from V48 to AG2 placed as close to the device as possible.         V5       25       1       External +5V analog supply.Connects to the internal analog power bus. This supplies the LED output drivers and internal analog circuits. A 0.1-µE de-coupling capacitor should terminate as close to this node and the AG pin as possible.         VL       54       1       External +3.3V logic supply. This pin connects to the internal logic power bus. This is the supply voltage for the internal device logic. A 0.1-µE de-coupling capacitor should terminate as close to this node and the AG pin as possible.         VL       54       1       External +3.3V logic supply. This pin connects to the internal logic power bus. This is the supply voltage for the internal device logic. A 0.1-µE de-coupling capacitor should terminate as close to this node and the DG pin as possible.         1P       1       1       Port positive. +48V load sense pin. Terminal voltage is monitored and controlled differentially with respect to <i>i</i> optionally, if the application warrants it, this high-side path can be protected with the use of a self-resetting por fuse.         6P       40       1         7P       41       1         8P       48                                                                                                                               | RG       | 29               | I      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| V48       27       1       0.1-μF capacitor from V48 to AG2 placed as close to the device as possible.         V5       25       1       External +5V analog supply.Connects to the internal analog power bus. This supplies the LED output drivers and internal analog circuits. A 0.1-μF de-coupling capacitor should terminate as close to this node and the AC pin as possible.         VL       54       1       External +3.3V logic supply. This pin connects to the internal logic power bus. This is the supply voltage for the internal device logic. A 0.1-μF de-coupling capacitor should terminate as close to this node and the DG pin as possible. This pin can be powered from V5 by using a 4.22-kΩ resistor from V5 to VL         PORT ANALOG SIGNALS       I       External +3.3V logic supply. This pin connects to the internal logic power bus. This is the supply voltage for the possible. This pin can be powered from V5 by using a 4.22-kΩ resistor from V5 to VL         PORT ANALOG SIGNALS       I       Port positive. +48V load sense pin. Terminal voltage is monitored and controlled differentially with respect to <i>i</i> Optionally, if the application warrants it, this high-side path can be protected with the use of a self-resetting porture.         6P       40       I         7P       41       I         8P       48       I         1N       2       I         2N       7       I         3N       10       I         4N       15       I         For negative. </td <td>V10</td> <td>28</td> <td>0</td> <td>should not be tied to any external supplies. A 0.1-µF de-coupling capacitor should terminate as close to this</td>                                                                                                                  | V10      | 28               | 0      | should not be tied to any external supplies. A 0.1-µF de-coupling capacitor should terminate as close to this                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| V5       25       1       and intermal analog circuits. A 0.1-μF de-coupling capacitor should terminate as close to this node and the AC pin as possible.         VL       54       1       External +3.3V logic supply. This pin connects to the internal logic power bus. This is the supply voltage for this node and the DG pin as possible. This pin can be powered from V5 by using a 4.22-kΩ resistor from V5 to VL         PORT ANALOG SIGNALS       1       Image: Comparison of the terminate as close to this node and the DG pin as possible. This pin can be powered from V5 by using a 4.22-kΩ resistor from V5 to VL         PORT ANALOG SIGNALS       1       1       1         2P       8       1       1         3P       9       1       1         4P       16       1       0ptionalty, if the application warrants it, this high-side path can be protected with the use of a self-resetting porture.         6P       40       1         7P       41       1         8P       48       1         1N       2       1         2N       7       1         3N       10       1         4N       15       1         6N       39       1         7N       42       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V48      | 27               | I      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| VL       54       I       internal device logic. A 0.1-μF de-coupling capacitor should terminate as close to this node and the DG pin as possible. This pin can be powered from V5 by using a 4.22-kΩ resistor from V5 to VL         PORT ANALOG SIGNALS       I       I       I       I         1P       1       1       I       I       Image: Signal state of the powered from V5 by using a 4.22-kΩ resistor from V5 to VL         PORT ANALOG SIGNALS       I       I       I       I       Image: Signal state of the powered from V5 by using a 4.22-kΩ resistor from V5 to VL         1P       1       I       I       Image: Signal state of the powered from V5 by using a 4.22-kΩ resistor from V5 to VL         2P       8       I       Image: Signal state of the powered from V5 by using a 4.22-kΩ resistor from V5 to VL         3P       9       I       Image: Signal state of the powered from V5 by using a 4.22-kΩ resistor from V5 to VL         4P       16       I       Port positive. +48V load sense pin. Terminal voltage is monitored and controlled differentially with respect to respect to respect to the powered from V5 to VL         6P       40       I       Image: Signal state of the powered from V5 to VL         7P       41       I       Image: Signal state of the power                                                                                                                                                                                                                                                                                                    | V5       | 25               | I      | and internal analog circuits. A 0.1-µF de-coupling capacitor should terminate as close to this node and the AG1                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 1P112P813P914P1615P3316P4017P4118P4811N212N713N1014N1516N3917N421                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VL       | 54               | I      | External +3.3V logic supply. This pin connects to the internal logic power bus. This is the supply voltage for the internal device logic. A 0.1- $\mu$ F de-coupling capacitor should terminate as close to this node and the DG pin as possible. This pin can be powered from V5 by using a 4.22-k $\Omega$ resistor from V5 to VL |  |  |  |  |  |  |  |

| 2P813P914P1615P3316P4017P4118P4811N212N713N1014N1516N3917N421                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PORT ANA | LOG S            | SIGNAL | S                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 3P914P1614P1615P3316P4017P4118P4811N212N713N1014N1516N3917N421                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1P       | 1                | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 4P1615P3315P3316P4017P4118P4811N212N713N1014N1515N3416N3917N421                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2P       | 8                | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| InNoISP33ISP33IGP40ITP41I8P48I1N2I2N7I3N10I4N15I5N34I6N39I7N42I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3P       | 9                | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 5P       33       1         6P       40       1         7P       41       1         8P       48       1         1N       2       1         2N       7       1         3N       10       1         4N       15       1         5N       34       1         6N       39       1         7N       42       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4P       | 16               | Ι      | Port positive. +48V load sense pin. Terminal voltage is monitored and controlled differentially with respect to <i>n</i> N.                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 7P       41       1         8P       48       1         1N       2       1         2N       7       1         3N       10       1         4N       15       1         5N       34       1         6N       39       1         7N       42       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5P       | 33               | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 8P         48         I           1N         2         I           1N         2         I           2N         7         I           3N         10         I           4N         15         I           5N         34         I           6N         39         I           7N         42         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6P       | 40               | I      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 1N         2         1           1N         2         1           2N         7         1           3N         10         1           4N         15         1           5N         34         1           6N         39         1           7N         42         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7P       | 41               | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 2N       7       I         3N       10       I         4N       15       I         5N       34       I         6N       39       I         7N       42       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8P       | 48               | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 3N       10       I         4N       15       I         5N       34       I         6N       39       I         7N       42       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1N       | 2                | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 4N       15       I         5N       34       I         5N       34       I         6N       39       I         7N       42       I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2N       | 7                | I      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 5N         34         1           6N         39         1           7N         42         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3N       | 10               | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 5N         34         I           6N         39         I           7N         42         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4N       | 15               | Ι      | Port negative48V load return sense pin. The low side of the load is switched and protected with the external                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 7N 42 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5N       | 34               | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

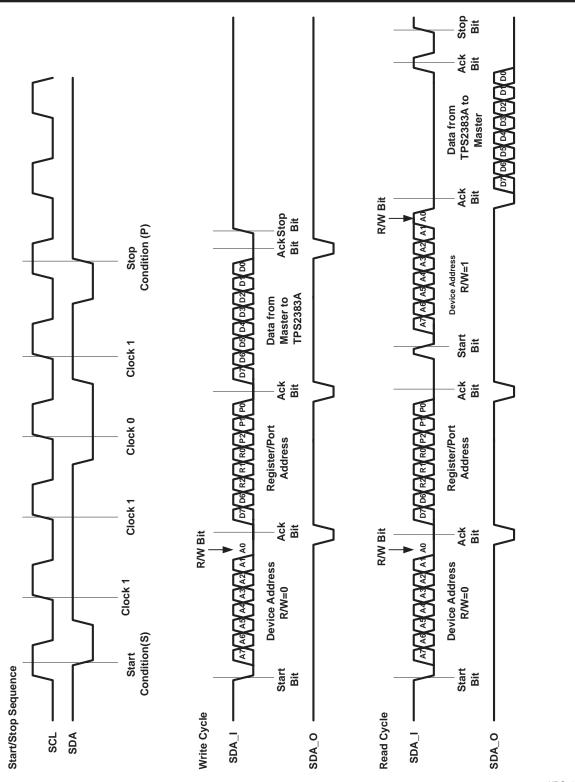

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6N       | 39               | Ι      |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |