### **Multichannel Integrated Power Management IC**

#### **General Description**

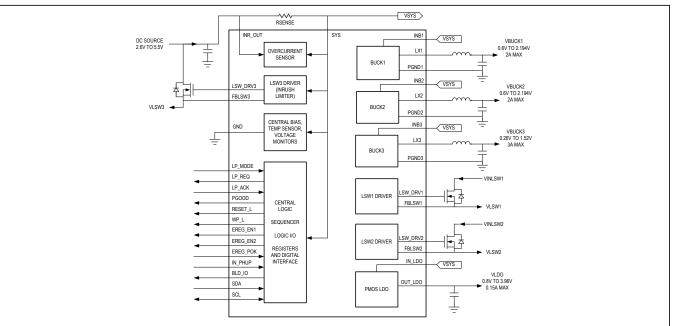

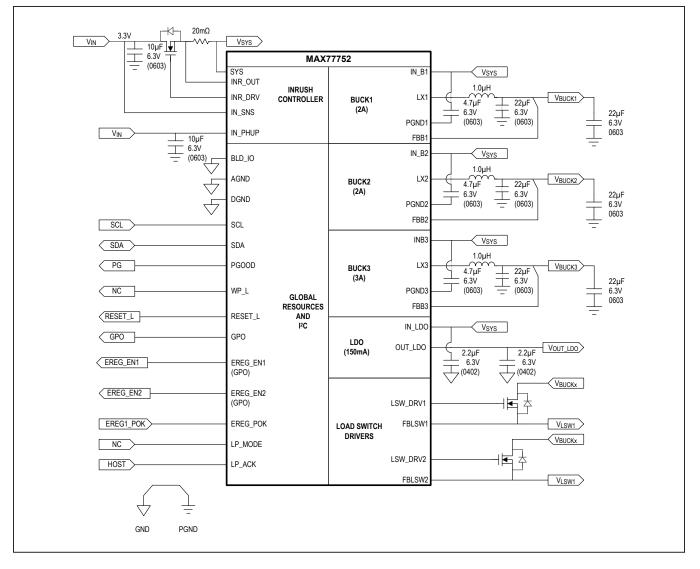

The MAX77752 is a highly-integrated power management solution including three step-down converters, a low-dropout linear regulator, two external regulators enable outputs, two dedicated load switch controllers, and an inrush-current limiter which can be configured as a third load switch controller using OTP. The MAX77752 provides a combination of high-performance power management components, high-accuracy monitoring, and a customized top-level controller that results in an efficient, size optimized solution.

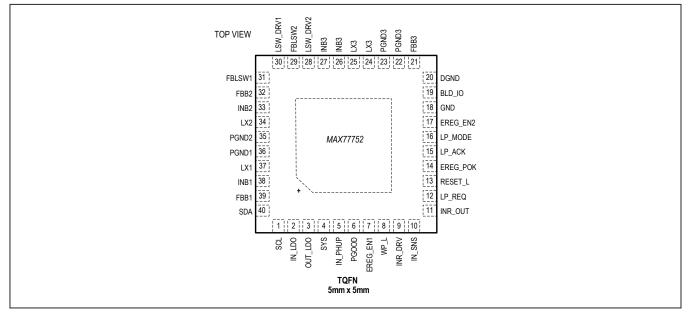

The 40-pin, 5mm x 5mm x 0.8mm, 0.4mm pitch TQFN package is ideal for space constrained applications.

Numerous factory programmable options allow the device to be tailored for many variations of the end application.

#### **Applications**

- Solid-State Drive Systems

- Handheld Devices

- Gaming Consoles

- Drones

- Automation Systems

- Cameras

#### Simplified Block Diagram

#### **Benefits and Features**

- Highly Integrated

- Three Buck Regulators

- Integrated High-Accuracy Brownout Comparators

- One Low-Dropout Linear Regulator

Low-Input Voltage

- Two Dedicated Load Switch Controllers

- One Inrush-Current Limiter, Configurable to be Load Switch 3 Controller Using OTP

- Two External Regulator Enable Outputs

- Voltage Monitor for Backup Power Control

- Highly Flexible and Configurable

- I<sup>2</sup>C-Compatible Interface

- Factory OTP Options Available

- Flexible Power Sequencer

- Configurable Sleep-State Control

- Small Size

- 40-Pin, 5mm x 5mm x 0.8mm, 0.4mm Pitch TQFN

- 70mm<sup>2</sup> Total Solution Size

Ordering Information appears at end of data sheet.

### Multichannel Integrated Power Management IC

#### **Absolute Maximum Ratings**

| Тор                      |                                |

|--------------------------|--------------------------------|

| IN_DRV to GND            | 0.3V to +16.0V                 |

| IN_SNS to GND (Note 1)   | 0.3V to +6.0V                  |

| INR_OUT to GND           | 0.3V to +6.0V                  |

| SYS to GND               | 0.3V to +6.0V                  |

| IN_PHUP to GND           | 0.3V to +6.0V                  |

| RESET_L to GND           | 0.3V to V <sub>SYS</sub> +0.3V |

| LP_REQ to GND            | 0.3V to V <sub>SYS</sub> +0.3V |

| LP_ACK to GND            | 0.3V to V <sub>SYS</sub> +0.3V |

| LP_MODE to GND           | 0.3V to V <sub>SYS</sub> +0.3V |

| WP_L to GND (Note 2)     | 0.3V to V <sub>H INT</sub>     |

| PGOOD to GND (Note 2)    | 0.3V to V <sub>H</sub> INT     |

| EREG_EN1 to GND (Note 2) | 0.3V to V <sub>H</sub> INT     |

| EREG_EN2 to GND          | 0.3V to 6.0V                   |

| EREG_POK to GND          | 0.3V to V <sub>SYS</sub> +0.3V |

| BLD_IO to GND (Note 2)   | 0.3V to +6.0V                  |

| WP_L Sink Current        | 35mA                           |

| RESET_L Sink Current     | 35mA                           |

| PGOOD Sink Current       | 35mA                           |

| EREG_EN1 Sink Current    | 35mA                           |

| EREG_EN2 Sink Current    | 35mA                           |

| LP_REQ Sink Current      | 35mA                           |

| DGND to GND              | 0.3V to +0.3V                  |

| LDO                      |                                |

| IN_LDO to GND            | 0.3V to +6.0V                  |

| OUT_LDO to GND           |                                |

| _                        |                                |

|                          |                                |

#### Buck

| BUCK                                                        |

|-------------------------------------------------------------|

| INB1, INB2, INB3 to SYS0.3V to +0.3V                        |

| INB1 to PGND10.3V to +6.0V                                  |

| INB2 to PGND20.3V to +6.0V                                  |

| INB3 to PGND30.3V to +6.0V                                  |

| LX1 to PGND1 (Note 3)0.3V to V <sub>INB1</sub> +0.3V        |

| LX2 to PGND2 (Note 3)0.3V to V <sub>INB2</sub> +0.3V        |

| LX3 to PGND3 (Note 3)0.3V to V <sub>INB3</sub> +0.3V        |

| LX1, LX2 RMS Current per pin (T <sub>J</sub> = +110°C)      |

| (RMS current per pin (T <sub>J</sub> = +110°C))1.7A         |

| LX3 RMS Current per pin (T <sub>J</sub> = +110°C)           |

| (RMS current per pin ( $T_J$ = +110°C))3.0A                 |

| FBB1, FBB2, FBB3 to GND0.3V to $V_{\mbox{SYS}}\mbox{+}0.3V$ |

| PGND1, PGND2, PGND3 to GND0.3V to +0.3V                     |

| 1 <sup>2</sup> C                                            |

| SDA, SCL to GND0.3V to V <sub>IN_VIO_I2C</sub> +0.3V        |

| SDA Sink Current                                            |

| Load Switch                                                 |

| LSW_DRV1 to GND0.3V to +16.0V                               |

| LSW_DRV2 to GND0.3V to +16.0V                               |

| FBLSW1 to GND0.3V to V <sub>SYS</sub> +0.3V                 |

| FBLSW2 to GND0.3V to V <sub>SYS</sub> +0.3V                 |

| Continuous Power Dissipation (Multilayer Board)             |

| T <sub>A</sub> = +70°C, derate 35.70mW/°C                   |

| above +70°C mW to 2857.1mW                                  |

| Operating Temperature Range40°C to +85°C                    |

| Junction Temperature+150°C                                  |

| Storage Temperature Range40°C to +150°C                     |

| Soldering Temperature (reflow)+260°C                        |

|                                                             |

Note 1: IN\_SNS voltage ramp rates greater than 2.8V/µs trigger the internal ESD device and should be avoided. The ESD device recovers if exposed to an excessive ramp rate.

Note 2:  $V_{H\_INT}$  is the maximum voltage of  $V_{SYS}$  and  $V_{IN\_PHUP}$ .

Note 3: The specified voltage limitation is for steady state conditions. Dead times of a few nano seconds exist during the dynamic BUCK regulator transitions from inductor charging to inductor discharging and vice versa. These dead times allow internal clamping diodes to PGNDx and INBx to forward bias (Vf~1V). When the LXx waveform is observed on a high-bandwidth oscilloscope (≥100MHz), the LXx transition edges are commonly seen with 1.5V spikes. These spikes are due to (1) the internal clamping diode forward voltage and (2) the high rate of current change through the current loop's inductance (V = L x di/dt). Designs must follow the recommended printed circuit board (PCB) layout in order to minimize this current loop's inductance.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### TQFN

| PACKAGE CODE                            | T4055+1C       |

|-----------------------------------------|----------------|

| Outline Number                          | 21-0140        |

| Land Pattern Number                     | <u>90-0016</u> |

| Thermal Resistance, Single-Layer Board: |                |

| Junction to Ambient $(\theta_{JA})$     | 45°C/W         |

| Junction to Case $(\theta_{JC})$        | 2°C/W          |

| Thermal Resistance, Four-Layer Board:   |                |

| Junction to Ambient $(\theta_{JA})$     | 28°C/W         |

| Junction to Case (θ <sub>JC</sub> )     | 2°C/W          |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

#### **Electrical Characteristics—Global Resources**

| PARAMETER                         | SYMBOL                    | CONDITIONS                                                                                                                                                                                                                        | MIN | ТҮР | MAX | UNITS |

|-----------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SUPPLY CURRENT                    |                           |                                                                                                                                                                                                                                   |     |     |     |       |

| OFF State Quiescent<br>Current    | IQSYS_OFF                 | V <sub>SYSUVLO</sub> < V <sub>SYS</sub> < V <sub>SYS_RESET</sub><br>(rising), OTP_INT_PU = 1, all regulators<br>are disabled. This includes any central<br>bias currents disabled (EREG_EN1<br>pulled to V <sub>SYS</sub> )       |     | 86  | 135 | μΑ    |

| DEVSLP State Quiescent<br>Current | I <sub>QSYS_</sub> DEVSLP | V <sub>SYS</sub> = 3.3V, V <sub>SYS</sub> > V <sub>SYS_RESET</sub> ,<br>OTP_INT_PU = 0, PMIC in DEVSLP<br>State, Buck2, Buck3, LDO enabled in<br>low-power mode. No load on all<br>regulators. All other regulators disabled      |     | 70  | 125 | - μΑ  |

|                                   |                           | V <sub>SYS</sub> = 5V, V <sub>SYS</sub> > V <sub>SYS</sub> <u>RESET</u> ,<br>OTP_INT_PU = 0, PMIC in DEVSLP<br>state, Buck2, Buck3, LDO enabled in<br>low-power mode. No load on all<br>regulators. All other regulators disabled |     | 90  | 155 |       |

| Buck Quiescent Supply<br>Current  | IQSYS_BUCK                | V <sub>SYS</sub> = 5V, V <sub>SYS</sub> > V <sub>SYS_RESET</sub> , all<br>bucks enabled in normal-power mode<br>and skip mode                                                                                                     |     | 233 | 420 | μΑ    |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                                 | SYMBOL                  | CONDITIONS                                        | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|-------------------------|---------------------------------------------------|------|------|------|-------|

| BIAS AND REFERENCE CU                     | RRENT GENER             | ATOR                                              |      |      |      |       |

| Operating Voltage Range                   | V <sub>SYS</sub>        |                                                   | 2.6  |      | 5.5  | V     |

| Quiescent Supply Current                  | I <sub>QCBRG</sub>      | $V_{SYS} > V_{SYSUVLO}$ (rising)                  |      | 25   |      | μA    |

| Shutdown Supply Current                   |                         | V <sub>SYS</sub> < V <sub>SYSUVLO</sub> (falling) |      | 0.1  |      | μA    |

| Bias Enable time                          | <sup>t</sup> BIASOK     |                                                   |      | 100  |      | μs    |

| POR COMPARATOR (INTER                     | RNAL)                   |                                                   |      |      |      |       |

| Quiescent Supply Current                  | I <sub>QSYS_POR</sub>   |                                                   |      | 1    |      | μA    |

| POR Undervoltage-Lockout<br>Threshold     | V <sub>POR</sub>        | V <sub>SYS</sub> falling                          |      | 1.33 |      | V     |

| POR Threshold Hysteresis                  | V <sub>HYS_POR</sub>    | V <sub>SYS</sub> rising                           |      | 160  |      | mV    |

| Response Time                             |                         | 100mV overdrive                                   |      | 300  |      | μs    |

| POR to UV/LO Delay                        | +                       | V <sub>SYS</sub> rising across POR (1V to 2V)     |      | 100  |      |       |

| POR to UVLO Delay                         | <sup>t</sup> PORUVLO    | V <sub>SYS</sub> falling across POR               |      | 50   |      | μs    |

| SYS UNDERVOLTAGE-LOC                      | KOUT COMPAR             | ATOR                                              |      |      |      |       |

| Quiescent Supply Current                  | IQSYS_UVLO              |                                                   |      | 1    |      | μA    |

| SYS Undervoltage-Lockout<br>Threshold     | V <sub>SYSUVLO</sub>    | V <sub>SYS</sub> falling                          | 2.00 | 2.10 | 2.25 | V     |

| SYS Undervoltage-Lockout<br>Hysteresis    | VINUVLO_HYS             |                                                   |      | 400  |      | mV    |

| SYS Undervoltage-Lockout<br>Response Time | <sup>t</sup> sysuvlo    | 100mV overdrive, falling edge                     |      | 150  |      | μs    |

| SYS RESET COMPARATOR                      | 2                       | ·                                                 |      |      |      |       |

| Quiescent Supply Current                  | I <sub>QSYS_RESET</sub> |                                                   |      | 3    |      | μA    |

| Reset Falling Threshold<br>Range          | V <sub>SYS_RESET</sub>  | Programmed by SYSRST[3:0]                         | 2650 |      | 4150 | mV    |

| Reset Threshold Step Size                 |                         |                                                   |      | 100  |      | mV    |

| Reset Threshold Hysteresis<br>Range       | V <sub>SYSRESET</sub> _ | Programmed by SYSRSTHYS[1:0]                      | 150  |      | 300  | mV    |

| Reset Threshold Hysteresis<br>Step Size   |                         |                                                   |      | 50   |      | mV    |

| Reset Comparator<br>Response Time         | <sup>t</sup> SYSRESET   |                                                   |      | 5    |      | μs    |

| Reset Comparator Accuracy                 |                         | SYSRSTTH[3:0] = 0x0, 0x1, 0x5,<br>0xA, 0xF        | -2.5 |      | +2.5 | %     |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                                     | SYMBOL                  | CONDITIONS                                                                                                                | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| SYS BROWNOUT COMPAR                           | ATOR                    |                                                                                                                           |      |      |      |       |

| Brownout Falling Threshold<br>Range           | V <sub>SYS_BO</sub>     | Programmed by SYSBOTH[3:0]                                                                                                | 2800 |      | 4300 | mV    |

| Brownout Threshold Step<br>Size               |                         |                                                                                                                           |      | 100  |      | mV    |

| Brownout Threshold<br>Hysteresis Range        | V <sub>SYS_BO_HYS</sub> | Programmed by SYSBOHYS[1:0]                                                                                               | 150  |      | 300  | mV    |

| Brownout Threshold<br>Hysteresis Step Size    |                         |                                                                                                                           |      | 50   |      | mV    |

|                                               |                         | SYS_BO_PR[1:0] = 0b00 (fast),<br>PMIC not in DEVSLP state, 100mV<br>under-drive with falling slew rate of<br>150mV/µs     |      | 1.04 |      |       |

| Brownout Comparator                           | <b>4</b>                | SYS_BO_PR[1:0] = 0b01 (med-fast),<br>PMIC not in DEVSLP state, 100mV<br>under-drive with falling slew rate of<br>150mV/µs |      | 1.14 |      |       |

| Response Time                                 | <sup>t</sup> sysbo      | SYS_BO_PR[1:0] = 0b10 (med-slow),<br>PMIC not in DEVSLP state, 100mV<br>under-drive with falling slew rate of<br>150mV/µs |      | 1.30 |      | - µs  |

|                                               |                         | SYS_BO_PR[1:0] = 0b11 (slow),<br>PMIC not in DEVSLP state, 100mV<br>under-drive with falling slew rate of<br>150mV/µs     |      | 1.68 |      |       |

| Brownout Comparator<br>Response Time (DEVSLP) | t <sub>SYSBO</sub>      | PMIC in DEVSLP state, 100mV under-<br>drive with falling slew rate of 150mV/µs                                            |      | 3.53 |      | μs    |

|                                               |                         | SYS_BO_PR[1:0] = 0b00 (fast), PMIC<br>not in DEVSLP state                                                                 |      | 13.4 |      |       |

| Quiescent Supply Current                      |                         | SYS_BO_PR[1:0] = 0b01 (med-fast),<br>PMIC not in DEVSLP state                                                             |      | 10.4 |      | μA    |

| Quescent Supply Surrent                       | I <sub>QSYS_BO</sub>    | SYS_BO_PR[1:0] = 0b10 (med-slow),<br>PMIC not in DEVSLP state                                                             |      | 7.4  |      |       |

|                                               |                         | SYS_BO_PR[1:0] = 0b11 (slow),<br>PMIC not in DEVSLP state                                                                 |      | 4.4  |      |       |

| Quiescent Supply Current (DEVSLP)             | I <sub>QSYS_BO</sub>    | PMIC in DEVSLP state                                                                                                      |      | 1.3  |      | μA    |

| Brownout Comparator<br>Accuracy               |                         | SYSBO[3:0] = 0x0, 0x1, 0x5, 0xA, 0xF,<br>PMIC is not in DEVSLP state                                                      | -2.5 |      | +2.5 | %     |

| Brownout Comparator<br>Accuracy (DEVSLP)      |                         | SYSBO[3:0] = 0x0, 0x1, 0x5, 0xA, 0xF,<br>PMIC is in DEVSLP state                                                          | -2.5 |      | +2.5 | %     |

| Brownout Timer Period                         | t <sub>BO</sub>         | T_BO_EN = 1                                                                                                               |      | 100  |      | ms    |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                        | SYMBOL               | CONDITIONS                                                                 | MIN | TYP   | MAX | UNITS |

|----------------------------------|----------------------|----------------------------------------------------------------------------|-----|-------|-----|-------|

| OSCILLATOR                       |                      |                                                                            |     |       |     |       |

| Clock Frequency                  | CLK32K               | V <sub>SYS</sub> = 5V                                                      |     | 31.5  |     | kHz   |

|                                  |                      | V <sub>SYS</sub> = 3.3V                                                    | -10 |       | +10 | 0/    |

| Oscillator Tolerance             |                      | V <sub>SYS</sub> = 5V                                                      | -10 |       | +10 | - %   |

| WP_L OUTPUT (OPEN DRA            | lN)                  |                                                                            |     |       |     |       |

| WP_L Output-Voltage Low          | V <sub>OL</sub>      | I <sub>SINK</sub> = 2mA                                                    |     |       | 0.4 | V     |

| WP_L Open Leakage                |                      | $V_{SYS} = V_{WP_L} = 5.5V, T_A = +25^{\circ}C,$<br>OTP_INT_PU[0] = 0b0    |     | 0.001 | 1   |       |

| Current                          |                      | $V_{SYS} = V_{WP_L} = 5.5V, T_A = +85^{\circ}C,$<br>OTP_INT_PU[0] = 0b0    |     | 0.01  |     | μA    |

| WP_L Falling Edge Time           |                      | $C_{WP_L} = 25pF, V_{WP_L} = 1.8V \ge 0$                                   |     | 25    |     | ns    |

|                                  |                      | WP_L_DLY[1:0] = 0b00<br>(based on an internal 31.5kHz clock)               |     | 0     |     |       |

| WP_L Output Deassert             | twpdly               | WP_L_DLY[1:0] = 0b01 (based on an internal 31.5kHz clock)                  |     | 254   |     |       |

| Delay Time                       |                      | WP_L_DLY[1:0] = 0b10<br>(based on an internal 31.5kHz clock)               |     | 508   |     | - µs  |

|                                  |                      | WP_L_DLY[1:0] = 0b11<br>(based on an internal 31.5kHz clock)               |     | 1016  |     |       |

| WP_L Output Assert<br>Delay Time |                      |                                                                            |     | 0     |     | μs    |

| WP_L Pullup Resistance           | R <sub>PU_WP_L</sub> | Pulled up to $V_{IN\_VIO}$ ,<br>OTP_INT_PU[0] = 0b1                        | 50  | 100   | 170 | kΩ    |

| RESET_L OUTPUT (OPEN I           | ORAIN)               |                                                                            |     |       |     |       |

| RESET_L Output-Voltage<br>Low    | V <sub>OL</sub>      | I <sub>SINK</sub> = 2mA                                                    |     |       | 0.4 | V     |

| RESET_L Open Leakage             |                      | $V_{SYS} = V_{RESET_L} = 5.5V, T_A = +25^{\circ}C,$<br>OTP_INT_PU[0] = 0b0 |     | 0.001 | 1   |       |

| Current                          |                      | $V_{SYS} = V_{RESET_L} = 5.5V, T_A = +85^{\circ}C,$<br>OTP_INT_PU[0] = 0b0 |     | 0.01  |     | μΑ    |

| RESET_L Falling Edge<br>Time     |                      | $C_{RESET_L} = 25pF, V_{RESET_L}$ falling from 1.8V $\ge 0$                |     | 25    |     | ns    |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                           | SYMBOL                  | CONDITIONS                                                                                   | MIN | ТҮР   | MAX | UNITS |

|-------------------------------------|-------------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| RESET L Output Deassert             |                         | RST_L_DLY[1:0] = 0b00<br>(based on an internal 31.5kHz clock)                                |     | 0     |     |       |

|                                     | <b>•</b>                | RST_L_DLY[1:0] = 0b01<br>(based on an internal 31.5kHz clock)                                |     | 254   |     |       |

| Delay Time                          | <sup>t</sup> RSTDLY     | RST_L_DLY[1:0] = 0b10<br>(based on an internal 31.5kHz clock)                                |     | 508   |     | μs    |

|                                     |                         | RST_L_DLY[1:0] = 0b11<br>(based on an internal 31.5kHz clock)                                |     | 1016  |     |       |

| RESET_L Output Assert<br>Delay Time |                         |                                                                                              |     | 0     |     | μs    |

| RESET_L Pullup<br>Resistance        | R <sub>PU_RESET_L</sub> | Pulled up to V <sub>IN_VIO,</sub><br>OTP_INT_PU[0] = 0b1                                     | 50  | 100   | 170 | kΩ    |

| PGOOD OUTPUT (OPEN DE               | RAIN)                   |                                                                                              |     |       |     |       |

| PGOOD Output-Voltage<br>Low         | V <sub>OL</sub>         | I <sub>SINK</sub> = 2mA                                                                      |     |       | 0.4 | V     |

| PGOOD Open Leakage                  |                         | V <sub>SYS</sub> = V <sub>PGOOD</sub> = 5.5V, T <sub>A</sub> = +25°C,<br>OTP_INT_PU[0] = 0b0 |     | 0.001 | 1   |       |

| Current                             |                         | V <sub>SYS</sub> = V <sub>PGOOD</sub> = 5.5V, T <sub>A</sub> = +85°C,<br>OTP_INT_PU[0] = 0b0 |     | 0.01  |     | μA    |

| PGOOD Falling Edge Time             |                         | $C_{PGOOD} = 25 pF, V_{PGOOD} = 1.8 V \ge 0$                                                 |     | 25    |     | ns    |

|                                     |                         | PG_DLY[1:0] = 0b00<br>(based on an internal 31.5kHz clock)                                   |     | 31.5  |     |       |

| PGOOD Output Assert                 |                         | PG_DLY[1:0] = 0b01<br>(based on an internal 31.5kHz clock)                                   |     | 254   |     |       |

| Delay Time                          | <sup>t</sup> pgooddly   | PG_DLY[1:0] = 0b10<br>(based on an internal 31.5kHz clock)                                   |     | 508   |     | μs    |

|                                     |                         | PG_DLY[1:0] = 0b11<br>(based on an internal 31.5kHz clock)                                   |     | 1016  |     |       |

| PGOOD Output Deassert<br>Delay Time |                         |                                                                                              |     | 0     |     | μs    |

| PGOOD Pullup Resistance             | R <sub>PU_PGOOD</sub>   | Pulled up to V <sub>IN_VIO</sub> , OTP_INT_PU[0]<br>= 0b1                                    | 50  | 100   | 170 | kΩ    |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                               | SYMBOL                 | CONDITIONS                                                                                                 | MIN | TYP   | MAX | UNITS |

|-----------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| LP_MODE INPUT                           |                        | 1                                                                                                          | 1   |       |     |       |

| LP_MODE I/O Pad<br>Operating Voltage    | V <sub>SYS</sub>       |                                                                                                            | 2.6 |       | 5.5 | V     |

| LP_MODE Input-Low<br>Voltage            | VIL                    |                                                                                                            |     |       | 0.4 | V     |

| LP_MODE Input-High<br>Voltage           | VIH                    |                                                                                                            | 1.4 |       |     | V     |

| LP_MODE Input Hysteresis                | V <sub>HYS</sub>       |                                                                                                            |     | 50    |     | mV    |

| LP_MODE Input Leakage                   |                        | $V_{SYS} = V_{IN_VIO} = 5.5V,$<br>$V_{LP_MODE} = 0V$ and 5.5V, $T_A = +25^{\circ}C$                        |     | 0.001 | 1   | μA    |

| Current                                 |                        | $V_{SYS} = V_{IN\_VIO} = 5.5V,$<br>$V_{LP\_MODE} = 0V$ and 5.5V, $T_A = +85^{\circ}C$                      |     | 0.01  |     | μΑ    |

| LP_MODE Debounce                        | <sup>t</sup> LPMD_DBNC | Debounce applies to rising and falling<br>edge. Does not account for oscillator<br>tolerance (Note 4)      |     | 95    | 127 | μs    |

| LP_MODE I/O Pad<br>Undervoltage Lockout | V <sub>SYSUVLO</sub>   | V <sub>SYS</sub> falling                                                                                   |     | 2.1   |     | V     |

| LP_MODE Mask<br>Deassertion Timer       | <sup>t</sup> LPMD_MSK  |                                                                                                            | 16  | 20    | 25  | ms    |

| LP_ACK INPUT                            | -                      | •                                                                                                          |     |       |     |       |

| I/O Pad Operating Voltage               | V <sub>SYS</sub>       |                                                                                                            | 2.6 |       | 5.5 | V     |

| Input Low Voltage                       | V <sub>IL</sub>        |                                                                                                            |     |       | 0.4 | V     |

| Input High Voltage                      | V <sub>IH</sub>        |                                                                                                            | 1.4 |       |     | V     |

| Input Hysteresis                        | V <sub>HYS</sub>       |                                                                                                            |     | 50    |     | mV    |

|                                         |                        | V <sub>SYS</sub> = 5.5V, V <sub>LP_ACK</sub> = 0V and 5.5V,<br>T <sub>A</sub> = +25°C, OTP_INT_PU[0] = 0b0 |     | 0.001 | 1   |       |

| Input Leakage Current                   |                        | V <sub>SYS</sub> = 5.5V, V <sub>LP_ACK</sub> = 0V and 5.5V,<br>T <sub>A</sub> = +85°C, OTP_INT_PU[0] = 0b0 |     | 0.01  |     | μA    |

| LP_ACK Pullup Resistance                | R <sub>PU_LP_ACK</sub> | Pulled up to V <sub>IN_VIO,</sub><br>OTP_INT_PU[0] = 0b1                                                   | 50  | 100   | 170 | kΩ    |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                      | SYMBOL                       | CONDITIONS                                                                                            | MIN | TYP   | MAX | UNITS |

|--------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| LP_REQ OUTPUT (OPEN D          | RAIN)                        | · · · · ·                                                                                             |     |       |     |       |

| LP_REQ Output Voltage<br>Low   | V <sub>OL</sub>              | I <sub>SINK</sub> = 2mA                                                                               |     |       | 0.4 | V     |

| LP_REQ Open Leakage            |                              | $V_{SYS} = V_{LP\_REQ} = 5.5V, T_A = +25^{\circ}C,$<br>OTP_INT_PU[0] = 0b0                            |     | 0.001 | 1   |       |

| Current                        |                              | V <sub>SYS</sub> = V <sub>LP_REQ</sub> = 5.5V, T <sub>A</sub> = +85°C,<br>OTP_INT_PU[0] = 0b0         |     | 0.01  |     | μA    |

| LP_REQ Falling Edge Time       |                              | $C_{LP\_REQ} = 25pF, V_{LP\_REQ} = 1.8V \ge 0$                                                        |     | 25    |     | ns    |

|                                |                              | LP_REQ_T_EN = 0, PMIC in master<br>mode (OTP_SLP_MSTRSLV = 0),<br>applies during DevSlp exit sequence |     | 31.75 |     | μs    |

| LP_REQ Delay                   | <sup>t</sup> LPREQ_LOW       | LP_REQ_T_EN = 1, PMIC in master<br>mode (OTP_SLP_MSTRSLV = 0),<br>applies during DevSlp exit sequence |     | 20    |     | ms    |

| LP_REQ Pullup Resistance       | R <sub>PU_LP_REQ</sub>       | Pulled up to V <sub>IN_VIO</sub> ,<br>OTP_INT_PU[0] = 0b1                                             | 50  | 100   | 170 | kΩ    |

| EREG_ENx OUTPUT (OPEN          | I DRAIN)                     |                                                                                                       |     |       |     |       |

| EREG_EN1 Output-Voltage<br>Low | V <sub>OL</sub>              | I <sub>SINK</sub> = 2mA                                                                               |     |       | 0.4 | V     |

| EREG_EN2 Output-Voltage<br>Low | V <sub>OL</sub>              | I <sub>SINK</sub> = 10mA                                                                              |     |       | 0.4 | V     |

| EREG_ENx Open                  |                              | $V_{SYS} = V_{EREG\_ENx} = 5.5V, T_A = +25^{\circ}C,$<br>OTP_INT_PU[0] = 0b0                          |     | 0.001 | 1   |       |

| Leakage Current                |                              | V <sub>SYS</sub> = V <sub>EREG_ENx</sub> = 5.5V, T <sub>A</sub> = +85°C,<br>OTP_INT_PU[0] = 0b0       |     | 0.01  |     | μA    |

| EREG_ENx Falling Edge<br>Time  |                              | C <sub>EREG_ENx</sub> = 25pF, V <sub>EREG_ENx</sub> = 1.8V<br>≥ 0                                     |     | 25    |     | ns    |

| EREG_EN1 Pullup<br>Resistance  | R <sub>PU_EREG_</sub><br>ENx | Pulled up to V <sub>H_INT</sub> , OTP_INT_PU[0]<br>= 0b1                                              | 50  | 100   | 170 | kΩ    |

| EREG_EN2 Pullup<br>Resistance  | R <sub>PU_EREG_</sub><br>ENx | Pulled up to V <sub>IN_VIO</sub> , OTP_INT_PU[0]<br>= 0b1                                             | 50  | 100   | 170 | kΩ    |

| EREG_POK INPUT                 |                              | · · ·                                                                                                 |     |       |     |       |

| I/O Pad Operating Voltage      | V <sub>SYS</sub>             |                                                                                                       | 2.6 |       | 5.5 | V     |

| Input Low Voltage              | V <sub>IL</sub>              |                                                                                                       |     |       | 0.4 | V     |

| Input High Voltage             | V <sub>IH</sub>              |                                                                                                       | 1.4 |       |     | V     |

| Input Hysteresis               | V <sub>HYS</sub>             |                                                                                                       |     | 50    |     | mV    |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

| PARAMETER                           | SYMBOL                       | CONDITIONS                                                                                      | MIN  | TYP    | MAX  | UNITS |

|-------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------|------|--------|------|-------|

| Input Leakage Current               |                              | $V_{SYS} = 5.5V, V_{EREG_POK} = 0V$<br>and 5.5V, T <sub>A</sub> = +25°C,<br>OTP_INT_PU[0] = 0b0 |      | 0.001  | 1    |       |

|                                     |                              | $V_{SYS} = 5.5V, V_{EREG_POK} = 0V$<br>and 5.5V, T <sub>A</sub> = +85°C,<br>OTP_INT_PU[0] = 0b0 |      | 0.01   |      | - μΑ  |

| EREG_POK Pullup<br>Resistance       | R <sub>PU_EREG_</sub><br>POK | Pulled up to V <sub>IN_VIO</sub> ,<br>OTP_INT_PU[0] = 0b1                                       | 50   | 100    | 170  | kΩ    |

| THERMAL MONITORS                    |                              |                                                                                                 |      |        |      |       |

| Quiescent Supply Current            | I <sub>QTM</sub>             |                                                                                                 |      | 1.5    |      | μA    |

| Shutdown Supply Current             |                              |                                                                                                 |      | 0.1    |      | μA    |

| Thermal Overload                    | T <sub>JOVLD</sub>           | T <sub>J</sub> rising, 15°C hysteresis                                                          |      | 165    |      | °C    |

| Response Time                       |                              | 5°C overdrive                                                                                   |      | 10     |      | μs    |

| FLEXIBLE POWER SEQUE                | NCER                         |                                                                                                 |      |        |      |       |

| Power-Up Sequence<br>Enable Delay   | <sup>t</sup> FPSDON          | Measured from internal FPSxEN =<br>1 to start of sequence<br>(based on a 31.5kHz clock)         |      | 63.492 |      | μs    |

| Power-Down Sequence<br>Enable Delay | <sup>t</sup> FPSDOFF         | Measured from internal FPSxEN =<br>0 to start of sequence<br>(based on a 31.5kHz clock)         |      | 95.240 |      | μs    |

|                                     |                              | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b000                                                        |      | 31     |      |       |

|                                     |                              | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b001                                                        |      | 63     |      |       |

|                                     |                              | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b010                                                        |      | 127    |      |       |

| Flexible Power Sequencer            | t <sub>FPS PU,</sub>         | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b011                                                        |      | 253    |      |       |

| Event Period                        | t <sub>FPS_PD</sub>          | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b100                                                        | 508  |        | - µs |       |

|                                     |                              | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b101                                                        |      | 984    |      |       |

|                                     |                              | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b110                                                        | 1936 |        |      |       |

|                                     |                              | MSTRxUPF[2:0] =<br>MSTRxDNF[2:0] = 0b111                                                        |      | 3904   |      |       |

### Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Global Resources (continued)**

$(V_{SYS} = 3.6V, V_{IO} = 1.8V, T_A = -40^{\circ}C$  to +85°C, limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER               | SYMBOL                 | CONDITIONS                                                                 | MIN | ТҮР   | MAX | UNITS  |

|-------------------------|------------------------|----------------------------------------------------------------------------|-----|-------|-----|--------|

|                         |                        | PD_DLY[1:0] = 0b00                                                         |     | 0     |     |        |

| Power-Down Sequence     |                        | PD_DLY[1:0] = 0b01                                                         |     | 1.0   |     |        |

| Delay                   | <sup>t</sup> PD_DLY    | PD_DLY[1:0] = 0b10                                                         |     | 1.5   |     | - ms   |

|                         |                        | PD_DLY[1:0] = 0b11                                                         |     | 2.0   |     |        |

| BLD_IO                  |                        |                                                                            |     |       |     |        |

| Maximum Bleed Time      | tBLEED_MAX             |                                                                            |     | 20    | 22  | ms     |

| Minimum Bleed Time      | t <sub>BLEED_MIN</sub> |                                                                            |     | 31.5  |     | μs     |

| Bleed Threshold         |                        | BLD_IO falling                                                             |     | 90    | 100 | mV     |

| Bleed Resistance        | R <sub>BLEED</sub>     | BLD_IO = 0.3V                                                              |     | 20    | 27  | Ω      |

| BLD_IO Input Leakage    |                        | $V_{\rm SYS}$ = 5.5V, $V_{\rm BLD\_IO}$ = 0V and 5.5V, $T_{\rm A}$ = +85°C |     | 0.01  |     |        |

| Current                 |                        | $V_{SYS}$ = 5.5V, $V_{BLD_{IO}}$ = 0V and 5.5V, $T_A$ = +25°C              |     | 0.001 | 1   | μA     |

| ON/OFF CONTROLLER       |                        |                                                                            |     |       |     |        |

| Hiccup Counter Limit    | HICCUP_<br>CNT_LIM     |                                                                            |     | 7     |     | counts |

| IN_PHUP                 |                        | ·                                                                          |     |       |     | •      |

| Operating Voltage Range | V <sub>IN_PHUP</sub>   |                                                                            | 2.4 |       | 5.5 | V      |

| IN_PHUP Supply Current  | I <sub>IN_PHUP</sub>   | $V_{SYS} = V_{IN_{PHUP}} = 5.5V, T_A = +25^{\circ}C$                       |     | 5.0   |     | μA     |

**Note 4:** The LP\_MODE debounce period has a variation due to the variability associated with quantizing an asynchronous input signal. Additionally, while measuring the period from a valid LP\_MODE edge to a subsequent event, such as LP\_REQ assertion, there is one more clock cycle (CLK32K) of delay observed in a real system.

### **Electrical Characteristics—Inrush Control**

$(V_{IN\_SNS} = 5.0V)$ , limits are 100% tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                | SYMBOL              |                                                  | CONDITIONS                                                                                                  | MIN  | TYP   | MAX  | UNITS |

|------------------------------------------|---------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| POWER SUPPLY                             | 1                   |                                                  |                                                                                                             |      |       |      |       |

| Supply Voltage Range                     | V <sub>IN</sub>     |                                                  |                                                                                                             | 2.1  |       | 5.5  | V     |

| IN Undervoltage-Lockout<br>Threshold     | V <sub>INUVLO</sub> | V <sub>IN</sub> rising                           |                                                                                                             |      | 2.3   | 2.55 | V     |

| IN Undervoltage-Lockout<br>Hysteresis    | VINUVLO_HYS         |                                                  |                                                                                                             |      | 200   |      | mV    |

| IN Undervoltage-Lockout<br>Response Time | <sup>t</sup> INUVLO | V <sub>IN</sub> rising                           | (V <sub>IN</sub> = V <sub>INUVLO</sub> + 100mV)                                                             |      | 39    |      | μs    |

| IN Overvoltage-Lockout<br>Threshold      | V <sub>INOVLO</sub> | V <sub>IN</sub> rising                           |                                                                                                             | 5.70 | 5.87  | 6.10 | V     |

| IN Overvoltage-Lockout<br>Hysteresis     | VINOVLO_HYS         |                                                  |                                                                                                             |      | 80    |      | mV    |

| IN Overvoltage-Lockout<br>Response Time  | <sup>t</sup> INOVLO | V <sub>IN</sub> rising                           | (V <sub>IN</sub> = V <sub>INOVLO</sub> + 50mV)                                                              |      | 8     |      | μs    |

| Leakage                                  |                     | V <sub>IN</sub> = 5.5V<br>T <sub>A</sub> = +25°( | , V <sub>IN_DRV</sub> = 0V and 11V,<br>C                                                                    |      | 0.001 | 1    | ıιΔ   |

|                                          | ILKG_VIN_DRV        | V <sub>IN</sub> = 5.5V<br>T <sub>A</sub> = +85°( | $V_{\rm IN_{DRV}} = 0V \text{ and } 11V$ ,                                                                  |      | 0.01  |      | μA    |

|                                          |                     | start state)                                     | /INR_OUT < V <sub>IN_SNS</sub> (soft-<br>), OTP_GDRV_FREQ =<br>)kHz), V <sub>IN_SNS</sub> = 3.3V            |      | 85    |      |       |

| Supply Current (Soft-Start)              | IQ_IN_SS            | (soft-start                                      | /INR_OUT < V <sub>IN_SNS</sub><br>state), OTP_GDRV_FREQ =<br>0kHz), V <sub>IN_SNS</sub> = 5V                |      | 138   |      | μA    |

| Supply Current (Steady-                  |                     | (steady sta                                      | /INR_OUT = V <sub>IN_SNS</sub><br>ate), t <sub>SS_DONE</sub> expired,<br>2.5kHz, V <sub>IN_SNS</sub> = 3.3V |      | 26    |      |       |

| State)                                   | I <sub>IN</sub>     | (steady sta                                      | /INR_OUT = V <sub>IN_SNS</sub><br>ate), t <sub>SS_DONE</sub> expired,<br>2.5kHz, V <sub>IN_SNS</sub> = 5V   |      | 37    |      | μΑ    |

| NMOS SWITCH DRIVER                       |                     |                                                  |                                                                                                             |      |       |      |       |

| Gate Drive ON Voltage                    | VIN_DRV_ON          | V <sub>IN</sub> = 5V                             | Voltage with respect to<br>ground when external<br>MOSFET is being driven to<br>it's fully ON state         | 8.5  | _     | 11   | V     |

| Gate Drive Current                       | IGDRV_INRUSH        | V <sub>IN</sub> = 3.3V<br>setting                | , 1X gate drive frequency                                                                                   | 1.8  | 3.0   | 4.2  | μA    |

| 4x Gate Drive Oscillator<br>Frequency    | fGDRV_4X            | OTP_INR_<br>V <sub>IN</sub> = 3.3V               | FREQ[2:0] = 0b111,<br>, V <sub>IN</sub> = 5V                                                                |      | 720   |      | kHz   |

## Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Inrush Control (continued)**

$(V_{IN\_SNS} = 5.0V)$ , limits are 100% tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                                                                                                                                                                                                                                                                                  | MIN | ТҮР   | MAX | UNITS                          |

|-----------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|--------------------------------|

| 2x Gate Drive Oscillator<br>Frequency         | fgdrv_2x               | OTP_INR_FREQ[2:0] = 0b110,<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                  |     | 360   |     | kHz                            |

| 1x Gate Drive Oscillator<br>Frequency         | fgdrv_1x               | OTP_INR_FREQ[2:0] = 0b101<br>(nominal gate drive strength),<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                 | 120 | 180   | 240 | kHz                            |

| 0.5x Gate Drive Oscillator<br>Frequency       | fGDRV_0.5X             | OTP_INR_FREQ[2:0] = 0b100,<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                  |     | 90    |     | kHz                            |

| 0.25x Gate Drive Oscillator<br>Frequency      | fgdrv_0.25X            | OTP_INR_FREQ[2:0] = 0b011,<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                  |     | 45    |     | kHz                            |

| 0.125x Gate Drive Oscillator<br>Frequency     | fGDRV_0.125X           | OTP_INR_FREQ[2:0] = 0b010,<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                  | 15  | 23    | 32  | kHz                            |

| 0.0625x Gate Drive Oscilla-<br>tor Frequency  | fGDRV_0.0625X          | OTP_INR_FREQ[2:0] = 0b001,<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                  |     | 11.25 |     | kHz                            |

| 0.03125x Gate Drive Oscil-<br>lator Frequency | fGDRV_0.03125X         | OTP_INR_FREQ[2:0] = 0b000,<br>V <sub>IN</sub> = 3.3V, V <sub>IN</sub> = 5V                                                                                                                                                                                                                                  |     | 5.625 |     | kHz                            |

| Gate Drive Discharge<br>Resistance            | 5                      | Resistance from INR_DRV to<br>INR_OUT, V <sub>INR_DRV-INR_OUT</sub> = 4V                                                                                                                                                                                                                                    |     | 74    |     |                                |

|                                               | R <sub>GDRV_DIS</sub>  | Resistance from INR_DRV to<br>INR_OUT, V <sub>INR_DRV-INR_OUT</sub> = 3.3V                                                                                                                                                                                                                                  |     | 100   |     | Ω                              |

| TIMING                                        |                        |                                                                                                                                                                                                                                                                                                             |     |       |     |                                |

| Start-Up Delay                                | <sup>t</sup> en_inrush | Time from V <sub>IN</sub> rising above V <sub>INUVLO</sub><br>to the internal charge pump being<br>enabled. Duration is based on the<br>gate drive oscillator frequency (f <sub>GDRV</sub> )<br>selected by OTP_INR_FREQ[2:0]                                                                               |     | 128   |     | cycles of<br><sup>f</sup> GDRV |

| Soft-Start Done Time                          | <sup>t</sup> ss_1      | Duration from MOSFET drive<br>circuit being enabled (subsequent to<br>startup delay) to the point when the<br>IN_SS_DONE (internal signal) is<br>asserted allowing a power-up<br>sequence to occur. Based on default<br>gate drive frequency (f <sub>GDRV</sub> ) selected<br>by OTP_INR_FREQ[2:0]          |     | 512   |     | cycles of<br><sup>f</sup> GDRV |

| Gate Drive Idle Time                          | <sup>t</sup> ss_done   | Duration from MOSFET drive circuit<br>being enabled (subsequent to the<br>startup delay) to the point when the<br>gate drive oscillator frequency folds<br>back to the 12.5kHz setting (idle gate<br>drive). Based on default gate drive<br>frequency (f <sub>GDRV</sub> ) selected by<br>OTP_INR_FREQ[2:0] |     | 1024  |     | cycles of<br><sup>f</sup> GDRV |

### Multichannel Integrated Power Management IC

#### **Electrical Characteristics—Current Sense Amplifier**

$(V_{SYS} = 3.3V, C_{LOAD} = 10pF, T_A = -40^{\circ}C$  to +85°C, limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                   | SYMBOL              | CONDITIONS                                 | MIN  | TYP | MAX  | UNITS |  |  |  |

|---------------------------------------------|---------------------|--------------------------------------------|------|-----|------|-------|--|--|--|

| INPUT OVERCURRENT                           |                     |                                            |      |     |      |       |  |  |  |

| Input Overcurrent Threshold                 |                     | 2.25A setting, V <sub>SYS</sub> = 3.3V     | -6.5 |     | +6.5 | %     |  |  |  |

| CSA Debounce Timer                          |                     | OTP_CSA_DBNC = 0                           |      | 100 |      |       |  |  |  |

|                                             |                     | OTP_CSA_DBNC = 1                           |      | 50  |      | μs    |  |  |  |

| Overcurrent-Sense<br>Comparator Threshold 1 | V <sub>OC_THR</sub> | Overcurrent limit,<br>CSTH_OPT[1:0] = 0b00 |      | 30  |      | mV    |  |  |  |

| Overcurrent-Sense<br>Comparator Threshold 2 | V <sub>OC_THR</sub> | Overcurrent limit,<br>CSTH_OPT[1:0] = 0b01 |      | 35  |      | mV    |  |  |  |

| Overcurrent-Sense<br>Comparator Threshold 3 | V <sub>OC_THR</sub> | Overcurrent-limit,<br>CSTH_OPT[1:0] = 0b10 |      | 40  |      | mV    |  |  |  |

| Overcurrent-Sense<br>Comparator Threshold 4 | V <sub>OC_THR</sub> | Overcurrent limit,<br>CSTH_OPT[1:0] = 0b11 |      | 45  |      | mV    |  |  |  |

#### Electrical Characteristics—Buck Regulators (BUCK1/2 - 2A Output)

| PARAMETER                | SYMBOL                        | CONDITIONS                                                                   | MIN | ТҮР | MAX | UNITS |

|--------------------------|-------------------------------|------------------------------------------------------------------------------|-----|-----|-----|-------|

| SUPPLY VOLTAGE AND CU    | IRRENT                        |                                                                              |     |     |     |       |

| Input Voltage Range      | V <sub>INBx</sub>             |                                                                              | 2.6 |     | 5.5 | V     |

| Shutdown Supply Current  | IQSHDN_BUCKx                  | (Note 5)                                                                     |     | 0.1 |     | μA    |

|                          | IQ SKIP NM                    | No switching, no load, (Note 6),<br>V <sub>SYS</sub> = 3.3V                  |     | 19  | 30  |       |

|                          | BUCKx                         | No switching, no load, (Note 6),<br>V <sub>SYS</sub> = 5V                    |     | 19  | 30  | μA    |

| Supply Quisseent Current | I <sub>Q_FPWM_</sub><br>BUCKx | FPWM mode (switching at fixed frequency), no load, V <sub>SYS</sub> = 3.3V   |     | 10  |     |       |

| Supply Quiescent Current |                               | FPWM mode (switching at fixed frequency), no load, V <sub>SYS</sub> = 5V     |     | 10  |     | mA    |

|                          | IQ_SKIP_LPM_<br>BUCKx         | Low-power mode (no switching),<br>no load, (Note 6), V <sub>SYS</sub> = 3.3V |     | 5   | 9   |       |

|                          |                               | Low-power mode (no switching),<br>no load, (Note 6), V <sub>SYS</sub> = 5V   |     | 5   | 9   | μA    |

## Multichannel Integrated Power Management IC

#### Electrical Characteristics—Buck Regulators (BUCK1/2 - 2A Output) (continued)

| PARAMETER                 | SYMBOL                             | CONDITIONS                                                                                                                                                                                                                   | MIN   | TYP   | MAX   | UNITS |

|---------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| OUTPUT VOLTAGE            |                                    |                                                                                                                                                                                                                              |       |       |       |       |

| Output Voltage Range      | V <sub>OUT_BUCKx</sub>             | Programmable in 6.25mV steps with<br>BUCK1VOUT[7:0] and<br>BUCK2VOUT[7:0]                                                                                                                                                    | 0.600 |       | 2.194 | V     |

|                           | V <sub>OUT_ACC_NM_</sub><br>BUCKx  | FPWM mode, normal mode,<br>no load, V <sub>OUT_BUCK1</sub> = 1.800V                                                                                                                                                          | -2    |       | +2    |       |

| Output Voltage Accuracy   | VOUT_ACC_<br>LPM_BUCKx             | Low-power mode, no load,<br>V <sub>OUT_BUCK1</sub> = 1.800V                                                                                                                                                                  | -4    |       | +4    | %     |

| Output voltage Accuracy   | V <sub>OUT_ACC_NM_</sub><br>BUCKx  | FPWM mode, normal mode,<br>no load, V <sub>OUT_BUCK2</sub> = 1.200V                                                                                                                                                          | -2    |       | +2    | 70    |

|                           | V <sub>OUT_ACC_</sub><br>LPM_BUCKx | Low-power mode, no load,<br>V <sub>OUT_BUCK2</sub> = 1.200V                                                                                                                                                                  | -4    |       | +4    |       |

| OUTPUT CURRENT            |                                    |                                                                                                                                                                                                                              |       |       |       |       |

| Maximum Output Current    | IOUT_MAX_<br>NM_BUCKx              | RMS, normal mode, L = 1µH                                                                                                                                                                                                    | 2000  |       |       | mA    |

|                           | I <sub>OUT_MAX_</sub><br>LPM_BUCKx | RMS, low-power mode, L = $1\mu$ H                                                                                                                                                                                            |       | 10    |       |       |

| PMOS Peak Current Limit   |                                    | V <sub>SYS</sub> = 3.6V                                                                                                                                                                                                      | 2300  | 2875  | 4200  | mA    |

|                           | I <sub>LIMP</sub>                  | V <sub>SYS</sub> = 5V                                                                                                                                                                                                        | 2300  | 2875  | 4200  |       |

| NMOS Valley Current Limit | h                                  | V <sub>SYS</sub> = 3.6V                                                                                                                                                                                                      |       | 2125  |       | mA    |

|                           | ILIMV                              | V <sub>SYS</sub> = 5V                                                                                                                                                                                                        |       | 2125  |       |       |

| NMOS Negative Current     |                                    | V <sub>SYS</sub> = 3.6V                                                                                                                                                                                                      |       | 800   |       | mA    |

| Limit                     | LIMN                               | V <sub>SYS</sub> = 5V                                                                                                                                                                                                        |       | 800   |       |       |

| PERFORMANCE PARAMET       | TERS                               |                                                                                                                                                                                                                              |       |       |       |       |

| Line Regulation           |                                    | $V_{SYS} = V_{INBx} = 2.6V$ to 5.5V                                                                                                                                                                                          |       | 0.2   |       | %/V   |

| Load Regulation           |                                    | Load = 0 to 1A, FPWM mode                                                                                                                                                                                                    |       | 0.125 |       | %/A   |

| Logd Transient Degenerate |                                    | $\begin{array}{l} \mbox{FPWM mode, V_{OUT\_BUCKx} = default,} \\ \mbox{L = 1}\mu\mbox{H, C}_{OUT} = 12\mu\mbox{F effective} \\ \mbox{\Delta I}_{OUT} = 0.2\mbox{A}_{-2}\mbox{A}, \mbox{\Delta t} = 3\mu\mbox{s} \end{array}$ |       | 88    |       | m)/   |

| Load Transient Response   |                                    | Skip mode, $V_{OUT\_BUCKx}$ = default,<br>L = 1µH, C <sub>OUT</sub> = 12µF effective<br>$\Delta I_{OUT}$ = 10mA to 0.7A, $\Delta t$ = 3µs,                                                                                   |       | 90    |       | mV    |

| Switching Frequency       | f <sub>SW</sub>                    | V <sub>SYS</sub> = 3.3V                                                                                                                                                                                                      | 1.8   | 2     | 2.2   | MHz   |

| Dead Time                 | t <sub>DEAD</sub>                  | V <sub>SYS</sub> = 3.3V                                                                                                                                                                                                      |       | 2.0   |       | ns    |

| Switching Frequency       | f <sub>SW</sub>                    | V <sub>SYS</sub> = 5V                                                                                                                                                                                                        | 1.8   | 2     | 2.2   | MHz   |

Multichannel Integrated Power Management IC

#### Electrical Characteristics—Buck Regulators (BUCK1/2 - 2A Output) (continued)

| PARAMETER                               | SYMBOL                         | CONDITIONS                                                                                                                                        | MIN | TYP | MAX | UNITS             |

|-----------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------------|

| Dead Time                               | t <sub>DEAD</sub>              | V <sub>SYS</sub> = 5V                                                                                                                             |     | 2.0 |     | ns                |

| Coff Start Slaw Data                    |                                | Fixed for buck 1                                                                                                                                  |     | 6.5 |     |                   |

| Soft-Start Slew Rate                    |                                | Fixed for buck 2                                                                                                                                  |     | 17  |     | mV/µs             |

| Output Voltage Ramp-Up<br>Slew Rate     |                                | Fixed for buckx (Notes 5, 8, 9),<br>C <sub>OUT</sub> = 22µF                                                                                       |     | 40  |     | mV/µs             |

| Output Voltage Ramp-Down<br>Slew Rate   |                                | Fixed for buck 1, 2 (Notes 5, 8),<br>$C_{OUT} = 22\mu$ F, BUCKxFPWMEN = 1<br>(x = 1, 2), no load                                                  |     | 18  |     | mV/µs             |

| DMOS ON Projetance                      | P                              | V <sub>SYS</sub> = V <sub>INBUCKx</sub> = 3.6V,<br>I <sub>OUT</sub> = 150mA                                                                       |     | 100 | 150 |                   |

| PMOS ON Resistance                      | R <sub>ON_PCH</sub>            | V <sub>SYS</sub> = V <sub>INBUCKx</sub> = 5V,<br>I <sub>OUT</sub> = 150mA                                                                         |     | 100 | 150 | mΩ                |

| NMOS ON Resistance                      | Barris                         | $V_{SYS} = V_{INBUCKx} = 3.6V,$<br>$I_{OUT} = 150mA$                                                                                              |     | 60  | 100 |                   |

|                                         | R <sub>ON_NCH</sub>            | $V_{SYS} = V_{INBUCKx} = 5V,$<br>$I_{OUT} = 150mA$                                                                                                |     | 60  | 100 | mΩ                |

| NMOS Zero-Crossing<br>Threshold         | I <sub>ZX</sub>                | Threshold to determine transition from<br>PWM to SKIP mode                                                                                        |     | 20  |     | mA                |

| Output Voltage Ripple in<br>Skip Mode   |                                | $V_{OUT_BUCKx}$ = 1.0V, L = 1µH,<br>C <sub>OUT</sub> = 12µF effective, no load<br>(Note 5)                                                        |     | 40  |     | mV <sub>P-P</sub> |

| Output Voltage Ripple in<br>PWM Mode    |                                | $V_{OUT\_BUCKx} = 1.0V, L = 1\mu H,$<br>$C_{OUT} = 12\mu F \text{ effective},$<br>$I_{LOAD} = 0.5 \text{ x } I_{OUT\_MAX\_BUCKx}$<br>(Note 5)     |     | 5   |     | mV <sub>P-P</sub> |

|                                         | IL_LX_25C                      | V <sub>LXx</sub> = 5.5V or 0V, T <sub>A</sub> = +25°C                                                                                             |     | 0.1 | 1   |                   |

| LX Leakage                              | IL_LX_85C                      | V <sub>LXx</sub> = 5.5V or 0V, T <sub>A</sub> = +85°C<br>(Note 5)                                                                                 |     | 1   |     | μA                |

| Output Active Discharge<br>Resistance   | R <sub>DISCHG</sub> _<br>BUCKx | Resistance from FBBx to PGNDx,<br>output disabled, (Note 7)                                                                                       |     | 100 |     | Ω                 |

| Nominal Output Inductance               | LNOM                           |                                                                                                                                                   |     | 1.0 |     | μH                |

| Minimum Effective Output<br>Capacitance | C <sub>OUT_EFF_MIN</sub>       | 0mA < I <sub>OUT</sub> < 2000mA                                                                                                                   | 18  |     |     | μF                |

| Light Load Efficiency                   | Eff <sub>LIGHT</sub>           | Low-power mode, $I_{OUT} = 0.5mA$ ,<br>$V_{OUT_BUCKx} = 1.0V$ , L = 1µH,<br>DCR <sub>L</sub> = 50m $\Omega$ , C <sub>OUT</sub> = 22µF<br>(Note 5) |     | 75  |     | %                 |

## Multichannel Integrated Power Management IC

#### Electrical Characteristics—Buck Regulators (BUCK1/2 - 2A Output) (continued)

| PARAMETER                                              | SYMBOL                             | CONDITIONS                                                                                                                                                                                    | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Typical Load Efficiency                                | Effiout_typ                        | $\begin{split} I_{OUT} &= 0.25 \text{ x } I_{OUT\_MAX\_BUCKx}, \\ V_{OUT\_BUCKx} &= 1.0V, L = 1 \mu H, \\ DCR_L &= 50 \text{m}\Omega, C_{OUT} = 22 \mu \text{F} \text{ (Note 5)} \end{split}$ |      | 85   |      | %     |

| Maximum Load Efficiency                                | EFF <sub>IOUT_MAX</sub>            | $\label{eq:out_constraints} \begin{array}{l} I_{OUT} = I_{OUT}\_MAX\_BUCKx, \\ V_{OUT} = 1.0V, L = 1\muH, \\ DCR_L = 50m\Omega, C_{OUT} = 22\muF \\ (Note \ 5) \end{array}$                   |      | 70   |      | %     |

| Turn-On Delay Time                                     | <sup>t</sup> ON_DLY_BUCKx          | EN signal to LX switching with bias ON                                                                                                                                                        |      | 30   |      | μs    |

| Maximum Duty Cycle                                     |                                    | V <sub>OUT_BUCKx</sub> / V <sub>IN_BUCKx</sub><br>expressed as %                                                                                                                              |      | 90   |      | %     |

| BROWNOUT COMPARATO                                     | R                                  |                                                                                                                                                                                               |      |      |      |       |

| Output Brownout                                        |                                    | Normal-power mode, falling threshold,<br>BUCKx_BO_THR[1:0] = 0b00                                                                                                                             |      | 75   |      |       |

|                                                        |                                    | Normal-power mode, falling threshold,<br>BUCKx_BO_THR[1:0] = 0b01                                                                                                                             |      | 80   |      |       |

| Threshold                                              | V <sub>BO_BUCKx</sub>              | Normal-power mode, falling threshold,<br>BUCKx_BO_THR[1:0] = 0b10                                                                                                                             |      | 85   |      | %     |

|                                                        |                                    | Normal-power mode, falling threshold,<br>BUCKx_BO_THR[1:0] = 0b11                                                                                                                             |      | 90.7 |      |       |

| Output Brownout<br>Accuracy                            |                                    | Normal-power mode.<br>V <sub>OUT_BUCKx</sub> = 1.0V<br>(VOUT_BUCKx[7:0] = 0 x 40)                                                                                                             | -4.0 |      | +4.0 | %     |

| Output Brownout Threshold<br>(Low-Power Mode)          | V <sub>BO_BUCKx</sub>              | Falling threshold, low-power mode                                                                                                                                                             |      | 86.0 |      | %     |