## CMOS 10- & 12-Bit Monolithic Multiplying D/A Converters

# AD7530, AD7531

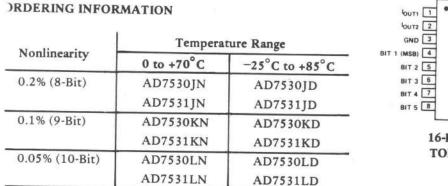

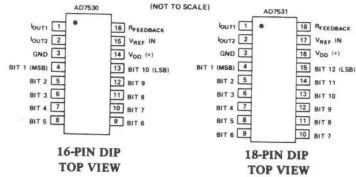

FEATURES AD7530, AD7531 FUNCTIONAL BLOCK DIAGRAM AD7530: 10-Bit Resolution AD7531: 12-Bit Resolution 10% 10% 10k VREF O 8-, 9- and 10-Bit End Point Linearity DTL/TTL/CMOS Compatible €20k 20k €20k €20k 20k Nonlinearity Tempco: 2ppm of FSR/°C Low Power Dissipation: 20mW S-1 S-2 S-3 S-N Current Settling Time: 500ns 0 0 0 Feedthrough Error: 10mV p-p @ 50kHz O OUT2 Low Cost O IOUTI AD7533 is Recommended for New 10-Bit Designs. Note: 10k AD7541A or AD7545 is Recommended for New O REEDBACK O O BIT 1 (MSB) BIT 2 Ċ 12-Bit Design BIT 3 BIT N (LSB) DIGITAL INPUTS (DTL/TTL/CMOS COMPATIBLE) AD7530: N = 10AD7531: N = 12**GENERAL DESCRIPTION** (Swit s shown in "High The AD7530 (AD7531) is a low cost, monolithic 10-bit (12-bit) multiplying digital-to-analog converter packaged in a 16-pin (18-pin) DIP. The device uses advanced CMOS PACKAGE IDENTIFICATION Suffix D: Ceramic DIP and thin film technologies providing up to 10-bit accuracy with DTL/TTL/CMOS compatibility. AD7530: (D16A) AD7531: (D18A) The AD7530 (AD7531) operates from a +5V to +15V Suffix N: Plastic DIP supply and dissipates only 20mW, including the ladder AD7530: (N16B) AD7531: (N18B) network.

<sup>1</sup>See Section 19 for package outline information.

#### **PIN CONFIGURATION**

Typical applications include: digital/analog multiplication, CRT character generation, programmable power supplies,

digitally controlled gain circuits, etc.

9

### **SPECIFICATIONS** ( $V_{DD} = +15$ , $V_{REF} = +10V$ , $T_A = +25^{\circ}C$ unless otherwise noted)

| PARAMETER                              | AD7530 AD7531                                                                                                   |         | TEST CONDITIONS                                        |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------|--|

| DC ACCURACY (Note 1)                   | 가 있습니다. "44 Content on Alian Content of States" (Source States) (Source States) (Source States) (Source States) |         |                                                        |  |

| Resolution                             | 10 Bits                                                                                                         | 12 Bits |                                                        |  |

| Relative Accuracy AD7530J              | 0.2% of FSR max (8 Bit)                                                                                         | *       |                                                        |  |

| AD7530K                                | 0.1% of FSR max (9 Bit)                                                                                         | *       |                                                        |  |

| AD7530L                                | 0.05% of FSR max (10 Bit)                                                                                       | *       |                                                        |  |

| Nonlinearity Tempco                    | 2ppm of FSR/°C max                                                                                              | *       | $-10V < V_{REF} < +10V$                                |  |

| Gain Error                             | 0.3% of FSR typ                                                                                                 | *       |                                                        |  |

| Gain Error Tempco                      | 10ppm of FSR/°C max                                                                                             | *       |                                                        |  |

|                                        | 300nA max                                                                                                       | *       | Over specified temperature                             |  |

| Output Leakage Current (Either Output) | Soona max                                                                                                       |         |                                                        |  |

| Power Supply Principa                  | 50mm of ESP /% tun                                                                                              | *       | range.                                                 |  |

| Power Supply Rejection                 | 50ppm of FSR/% typ                                                                                              |         |                                                        |  |

| AC ACCURACY                            |                                                                                                                 |         | To 0.05%                                               |  |

| Output Current Settling Time           | 500ns typ                                                                                                       | *       | All digital inputs low to high                         |  |

| $\frown$                               |                                                                                                                 |         | and high to low                                        |  |

| Feedthrough Error (Note 2)             | 10mV p-p max                                                                                                    | *       | $V_{REF} = 20V \text{ p-p}, 50\text{kHz}. \text{ All}$ |  |

|                                        |                                                                                                                 |         | digital inputs low                                     |  |

| REFERENCE INPUT                        | ±10V                                                                                                            | *       |                                                        |  |

| Input Range                            | (±kmA                                                                                                           | *       |                                                        |  |

| Input Resistance                       | (10KD the                                                                                                       | *       |                                                        |  |

|                                        |                                                                                                                 | $\sim$  |                                                        |  |

| ANALOG OUTPUT                          | $\neg > \rangle / / \rangle \rangle$                                                                            |         |                                                        |  |

| Output Current Range (Both Outputs)    | ±1mA                                                                                                            | / /.    |                                                        |  |

| Output Capacitance L <sub>OUT1</sub>   | 120pf typ                                                                                                       |         | All digital inputs high                                |  |

| I <sub>OUT2</sub>                      | 37pE typ                                                                                                        | / /*    |                                                        |  |

| I <sub>OUT1</sub>                      | 37pF typ                                                                                                        | *       |                                                        |  |

| LOUT2                                  | 120pF typ                                                                                                       |         | All digital input low                                  |  |

|                                        |                                                                                                                 | 1/      |                                                        |  |

| Output Noise (Both Outputs)            | Equivalent to $10k\Omega$                                                                                       |         |                                                        |  |

|                                        | Johnson noise typ                                                                                               |         |                                                        |  |

| DIGITAL INPUTS (Note 3)                |                                                                                                                 |         |                                                        |  |

| Low State Threshold                    | 0.8V max                                                                                                        | *       | Over specified temperature range                       |  |

| High State Threshold                   | 2.4V min                                                                                                        | *       | Over specified temperature range                       |  |

| ingli otate i ilesitota                | 2.17 mm                                                                                                         |         | over specified temperature range                       |  |

| Input Current (low to high state)      | 1μA typ                                                                                                         | *       |                                                        |  |

| Input Coding                           | Binary                                                                                                          | *       | See Tables I & II                                      |  |

| POWER REQUIREMENTS                     | -                                                                                                               |         |                                                        |  |

|                                        | 15V to 115V                                                                                                     | *       |                                                        |  |

| Power Supply Voltage Range             | +5V to +15V                                                                                                     | *       | All digital inputs at CND                              |  |

| I <sub>DD</sub>                        | 5nA typ                                                                                                         | *       | All digital inputs at GND                              |  |

| Total Dissipation                      | 2mA max<br>20mW typ                                                                                             | *       | All digital inputs high or low                         |  |

|                                        |                                                                                                                 |         |                                                        |  |

NOTES <sup>1</sup> Full scale range (FSR) is 10V for unipolar mode and ±10V for bipolar mode. <sup>2</sup> To minimize feedthrough with the ceramic package, the user must ground the metal lid. If the lid is not grounded, then the feedthrough is 10mV typical and 30mV maximum. <sup>3</sup> Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

\*Same specifications as for AD7530.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| V <sub>DD</sub> (to Gnd) +17V                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REF</sub> (to Gnd)                                                                                                               |

| Digital Input Voltage Range VDD to Gnd                                                                                                  |

| Voltage at Pin 1, Pin 2                                                                                                                 |

| Power Dissipation (package)<br>up to +75°C                                                                                              |

| Operating Temperature                                                                                                                   |

| JN, KN, LN Versions $\dots \dots \dots$ |

| JD, KD, LD Versions $\dots \dots \dots$ |

| Storage Temperature                                                                                                                     |

CAUTION:

| CAU <u>TION:</u>                                                      |

|-----------------------------------------------------------------------|

| 1. Do not apply voltages higher than V <sub>DD</sub> or less than GND |

| potential on any terminal except VREF.                                |

| 2. The digital control inputs are zener protected; however,           |

| permanent damage may occur on unconnected units                       |

| under high energy electrostatic fields. Keep unused units             |

| in conductive loath at all times.                                     |

|                                                                       |

| APPLICATIONS                                                          |

|                                                                       |

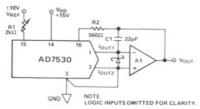

#### UNIPOLAR BINARY OPERATION (2-QUADRANT MULTIPLICATION)

Figure 1 shows the analog circuit connections required for unipolar binary (2-quadrant multiplication) operation. The logic inputs are omitted for clarity. With a dc reference voltage or current (positive or negative polarity) applied at pin 15, the circuit is a unipolar D/A converter. With an ac reference voltage or current the circuit provides 2-quadrant multiplication (digitally controlled attenuation). The input/output relationship is shown in Table I. Protection Schottky shown in Figure 1 is not required when using TRIFET output amplifiers such as the AD542 or AD544.

R1 provides full scale trim capability [i.e.—load the DAC register to 11 1111 1111, adjust R1 for  $V_{OUT} = -V_{REF}$  (1 – 2<sup>-10</sup>)]. Alternatively, Full Scale can be adjusted by omitting R1 and R2 and trimming the reference voltage magnitude.

C1 phase compensation (10 to 25pF) may be required for stability when using high speed amplifiers. (C1 is used to cancel the pole formed by the DAC internal feedback resistance and output capacitance at  $I_{OUT1}$ ).

Amplifier A1 should be selected or trimmed to provide  $V_{OS} \leq 10\%$  of the voltage resolution at  $V_{OUT}$ . Additionally, the amplifier should exhibit a bias current which is low over the temperature range of interest (bias current causes output offset at  $V_{OUT}$  equal to  $I_B$  times the DAC feedback resistance, nominally 15k $\Omega$ ).

| DIGITAL INPUT         | ANALOG OUTPUT                         |

|-----------------------|---------------------------------------|

| 1 1 1 1 1 1 1 1 1 1 1 | $-V_{\text{REF}} (1 - 2^{-10})$       |

| 1 0 0 0 0 0 0 0 0 1   | $-V_{\text{REF}} (1/2 + 2^{-10})$     |

| 10000000000           | -V <sub>REF</sub><br>2                |

| 0111111111            | $-V_{\rm REF} (1/2 - 2^{-10})$        |

| 0 0 0 0 0 0 0 0 0 0 1 | -V <sub>REF</sub> (2 <sup>-10</sup> ) |

| 00000000000           | 0                                     |

NOTE: 1 LSB =  $2^{-10}$  V<sub>REE</sub>

| Table I. | Code Table - | - Unipolar | Binary | Operation |

|----------|--------------|------------|--------|-----------|

|----------|--------------|------------|--------|-----------|

#### BIPOLAR OPERATION (4-QUADRANT MULTIPLICATION)

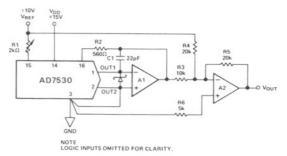

Figure 2 and Table II illustrate the circuitry and code relationship for bipolar operation. With a dc reference (positive or negative polarity) or an ac reference the circuit provides offset binary operation. Protection Schottky shown in Figure 2 is not required when using TRIFET output amplifiers such as the AD542 or AD544.

With the DAC register loaded to 10 0000 0000, adjust R1 fq = 0V (alternatively, one can omit R1 and R2 and OU st the ratio of R3 to R4 for VOUT = OV). Full Scale ng can be ac complished by adjusting the amplitude nmi REF or by varying the value of R5. of unipolar op eration, A1 must be chosen for lo os and must be selected for matching low IB. R3, R4 and R5 and tracking. Mismatch of 2R3 to R4 causes both offset and Full Scale error. Mismatch of R5 to R4 or 2R3 causes Full Scale error. C1 phase compensation (10pF to 25pF) may quired for stability.

Figure 2. Bipolar Operation (4-Quadrant Multiplication)

| DIGITAL INPUT         | ANALOG OUTPUT                        |  |  |

|-----------------------|--------------------------------------|--|--|

| 1 1 1 1 1 1 1 1 1 1 1 | $-V_{\text{REF}} (1 - 2^{-9})$       |  |  |

| 1000000001            | -V <sub>REF</sub> (2 <sup>-9</sup> ) |  |  |

| 10000000000           | 0                                    |  |  |

| 01111111111           | V <sub>REF</sub> (2 <sup>-9</sup> )  |  |  |

| 0000000001            | $V_{\text{REF}} (1 - 2^{-9})$        |  |  |

| 00000000000           | V <sub>REF</sub>                     |  |  |

NOTE: 1 LSB =  $2^{-9}$  V<sub>REF</sub>

Table II Code Table – Bipolar (Offset Binary) Operation

#### TERMINOLOGY

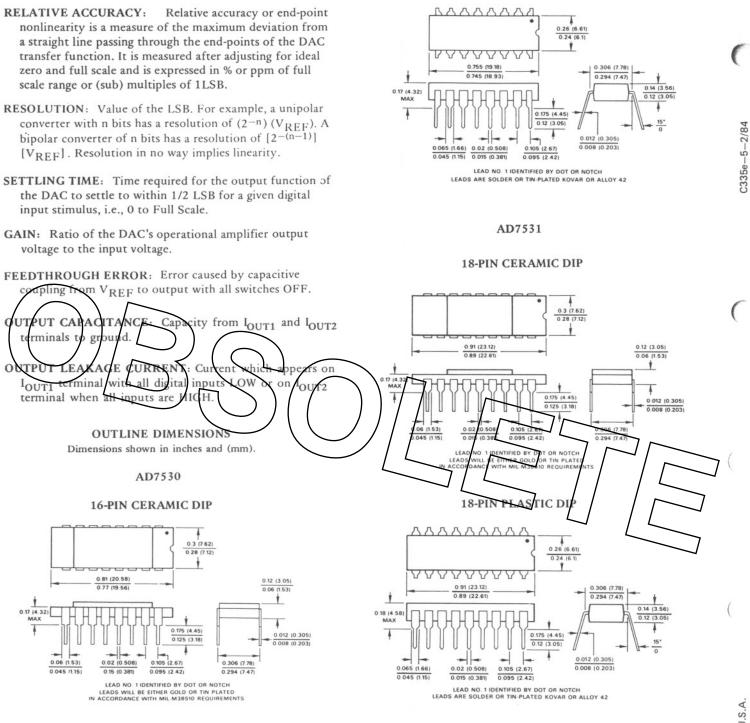

**16-PIN PLASTIC DIP**

PRINTED IN U.S.A