# RICHTEK

## Host-Side Single Cell Lithium Battery Gauge

## **General Description**

The RT9428 is a compact, host-side fuel gauge IC for lithium-ion (Li+) battery-powered systems.

For the embedded Fuel Gauge function, the state-ofcharge (SOC) calculation is based on the battery voltage information and the dynamic difference between battery voltage and relaxed OCV, by using iteration to estimate the increasing or decreasing SOC.

Voltage-based algorithm can support smoothly SOC and does not accumulate error with time and current. That is an advantage compared to coulomb counter which suffer from SOC drift caused by current-sense error and battery self-discharge. The disadvantage of voltage-based fuel gauge, it can report incremental SOC (%), but can't report capacity (mAh).

A quick sensing operation provides a good initial estimate of the battery's SOC. This feature allows the IC to be located on system side, reducing cost and supply chain constraints on the battery. Measurement and estimated capacity data sets are accessed through an  $I^2C$  interface.

The RT9428 is available in the WL-CSP-8B 1.6x1.52 (BSC) package.

### Features

- Host-Side Fuel Gauging

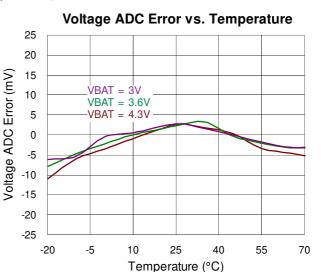

- Precision Voltage Measurement ±7.5mV Accuracy

- Accurate Relative Capacity (RSOC) Calculated from Voltaic Gauge Algorithm with Temperature Compensation

- No Accumulation Error on Capacity Calculation

- No Battery Relearning Necessary

- No Current Sense Resistor Required

- External Alarm/Interrupt for Low Battery Alert

- I<sup>2</sup>C Compatible Interface

- Low Power Consumption

- RoHS Compliant and Halogen Free

## **Applications**

- Smartphones

- Tablet PC

- Digital Still Cameras

- Digital Video Cameras

- Handheld and Portable Applications

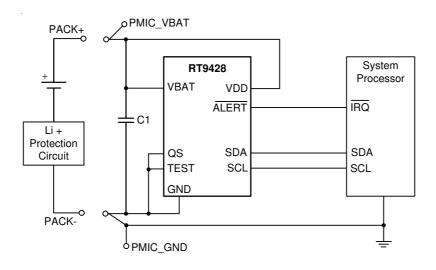

## **Simplified Application Circuit**

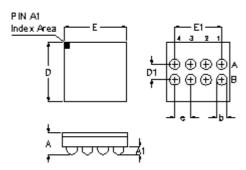

**Pin Configuration**

(TOP VIEW)

TEST VBAT VDD GND

A) A2 A3 A4 B) B2 B3 B4

SDA SCL QS

WL-CSP-8B 1.6x1.52 (BSC)

ALERT

## **Ordering Information**

RT9428 🖵

Package Type WSC : WL-CSP-8B 1.6x1.52 (BSC)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

1SW

1S : Product Code W : Date Code

### **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                            |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | TEST     | Test pin. Connect to GND pin during normal operation.                                                                                                                   |

| A2      | VBAT     | Battery voltage measurement input.                                                                                                                                      |

| A3      | VDD      | Processor power input. Decouple with a 10nF capacitor.                                                                                                                  |

| A4      | GND      | Ground.                                                                                                                                                                 |

| B1      | SDA      | Serial data input. Slave $I^2C$ data line for communication with system. Open-drain I/O.                                                                                |

| B2      | SCL      | Serial clock input. Slave I <sup>2</sup> C clock line for communication with system.                                                                                    |

| B3      | QS       | Quick sensing input. Active high to restart the calculation. Pull low to GND during normal operation.                                                                   |

| B4      | ALERT    | Alert output. When SOCLow condition is detected, It outputs low as interrupt signal.<br>Connect to interrupt input of the system processor. Connect to GND if not used. |

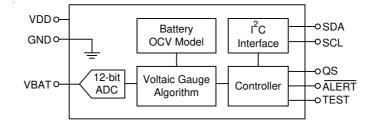

## **Functional Block Diagram**

## Operation

#### 12-bit ADC

Analog-to-Digital Converter. It converts the voltage input from VBAT pin to target value.

#### **Battery OCV Model**

Parameters for battery characteristics.

#### **Voltaic Gauge Algorithm**

The RT9428 calculates and determines that the embedded Fuel Gauge calculates and determines the Li+ battery SOC according to battery voltage only.

The algorithm estimates the increasing or decreasing SOC by an iteration model according to the difference between battery voltage and the battery OCV. The dynamic voltaic information can effectively emulate the Li+ battery behavior and determines the SOC (%), but can't report capacity (mAh).

#### Controller

The controller takes care of the control flow of system routine, ADC measurement flow, algorithm calculation and alert determined.

#### I<sup>2</sup>C Interface

The fuel gauge registers can be accessed through the  $\mathsf{I}^2\mathsf{C}$  Interface.

## Absolute Maximum Ratings (Note 1)

| Voltage on TEST Pin Relative to GND            | –0.3V to 5.5V  |

|------------------------------------------------|----------------|

| Voltage on VBAT Pin Relative to GND            | –0.3V to 5.5V  |

| Voltage on All Other Pins Relative to GND      | –0.3V to 6V    |

| • SCL, SDA, QS, ALERT to GND                   | -0.3V to 5.5V  |

| VBAT to GND                                    | –0.3V to 5V    |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                |

| WL-CSP-8B 1.6x1.52 (BSC)                       | 0.87W          |

| Package Thermal Resistance (Note 2)            |                |

| WL-CSP-8B 1.6x1.52 (BSC), θ <sub>JA</sub>      | 114.4°C/W      |

| Lead Temperature (Soldering, 10 sec.)          | 260°C          |

| Junction Temperature Range                     | 150°C          |

| Storage Temperature Range                      | –65°C to 150°C |

## Recommended Operating Conditions (Note 3)

| Supply Voltage, VDD        | - 2.5V to 4.5V  |

|----------------------------|-----------------|

| Junction Temperature Range | - 40°C to 125°C |

| Ambient Temperature Range  | - −40°C to 85°C |

## **Electrical Characteristics**

$(2.5V \leq V_{\text{DD}} \leq 4.5V, \ T_{\text{A}} = 25^{\circ}\text{C} \ \text{unless otherwise specified}) \quad (\text{Note 4})$

| Parameter                 |               | Symbol                | Test Conditions                                                     | Min  | Тур | Max | Unit |  |

|---------------------------|---------------|-----------------------|---------------------------------------------------------------------|------|-----|-----|------|--|

| DC Section                |               |                       |                                                                     |      |     |     |      |  |

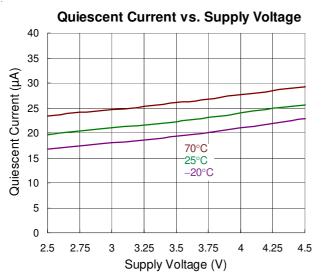

| Active Current            |               | IACTIVE               |                                                                     |      | 22  | 40  | μA   |  |

| Sloop Mode Cur            | (Niata E)     |                       | V <sub>DD</sub> = 2.5V                                              |      | 0.5 | 1   |      |  |

| Sleep-Mode Curi           | rent (Note 5) | ISLEEP                |                                                                     |      | 1   | 3   | μA   |  |

| Time-Base Accu            | racy          | terr                  | $T_A = -20^{\circ}C \text{ to } 70^{\circ}C \qquad (\text{Note 4})$ | -3.5 | ±1  | 3.5 | %    |  |

| Voltage Measurement Error |               | Vocas                 | $V_{BAT} = 4V$                                                      | -7.5 |     | 7.5 | mV   |  |

| voltage measure           |               | V <sub>GERR</sub>     | $T_A = -20^{\circ}C \text{ to } 70^{\circ}C \qquad (\text{Note 4})$ | -20  |     | 20  | IIIV |  |

| VBAT Pin Input I          | mpedance      | R <sub>VBAT</sub>     |                                                                     | 15   |     |     | MΩ   |  |

| SCL, SDA, QS              | Logic-High    |                       | All voltage reference to GND                                        | 1.4  |     |     | v    |  |

| Input Voltage             | Logic-Low     |                       | All voltage reference to GND                                        |      |     | 0.5 | v    |  |

| SDA Output Logic-Low      |               | V <sub>OL_SDA</sub>   | I <sub>OL_SDA</sub> = 4mA, All voltage reference to GND             |      |     | 0.4 | V    |  |

| ALERT Output Logic-Low    |               | V <sub>OL_ALERT</sub> | IOL_ALERT = 2mA, All voltage reference to GND                       |      |     | 0.4 | V    |  |

| SCL, SDA Pull-D           | own Current   | IPD                   | $V_{DD} = 4.5V$ , $V_{SCL} = V_{SDA} = 0.4V$                        |      | 0.2 | 0.4 | μA   |  |

| Bus Low Timeou            | t             | <b>t</b> SLEEP        | (Note 6)                                                            | 2    |     | 3   | S    |  |

## RICHTEK

| Parameter                                        | Symbol           | Test Conditions  | Min | Тур | Max | Unit |

|--------------------------------------------------|------------------|------------------|-----|-----|-----|------|

| I <sup>2</sup> C Interface                       |                  |                  |     |     |     |      |

| Clock Operating Frequency                        | fscl             | (Note 7)         | 10  |     | 250 | kHz  |

| Bus Free Time Between a STOP and START Condition | t <sub>BUF</sub> |                  | 1.3 |     |     | μs   |

| Hold Time After START<br>Condition               | thd_sta          | (Note 7)         | 0.6 |     |     | μs   |

| Low Period of the SCL Clock                      | t∟ow             |                  | 1.3 |     |     | μs   |

| High Period of the SCL Clock                     | tнідн            |                  | 0.6 |     |     | μs   |

| Setup Time for a Repeated START Condition        | tsu_sta          |                  | 0.6 |     |     | μs   |

| Data Hold Time                                   | thd_dat          | (Note 8, Note 9) | 0.2 |     | 0.9 | ms   |

| Data Setup Time                                  | tsu_dat          | (Note 8)         | 100 |     |     | ns   |

| Clock Data Rising Time                           | t <sub>R</sub>   |                  | 20  |     | 300 | ns   |

| Clock Data Falling Time                          | tF               |                  | 20  |     | 300 | ns   |

| Set-Up Time for STOP<br>Condition                | tsu_sto          |                  | 0.6 |     |     | μs   |

| Spike Pulse Widths<br>Suppressed by Input Filter | t <sub>SP</sub>  | (Note 10)        | 0   |     | 50  | ns   |

| Capacitive Load for Each Bus Line                | CB               | (Note 11)        | 400 |     |     | pF   |

| SCL, SDA Input Capacitance                       | CBIN             |                  |     |     | 60  | pF   |

Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. The device is not guaranteed to function outside its operating conditions.

- **Note 4.** Specifications are 100% tested at  $T_A = 25$ °C. Limits over the operating range are guaranteed by design and characterization.

- Note 5. SDA, SCL = GND; QS, ALERT idle.

- Note 6. The RT9428 enter sleep mode after SCL and SDA low for longer than 3s.

- Note 7. f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall time.

- Note 8. The maximum  $t_{HD_DAT}$  has only to be met if the device does not stretch the low period ( $t_{LOW}$ ) of the SCL signal.

- Note 9. This device internally provides a hold time of at least 75ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

- Note 10. Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

- Note 11. C<sub>B</sub> total capacitance of one bus line in pF.

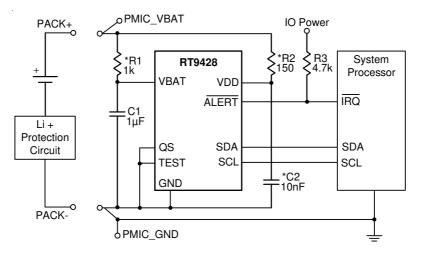

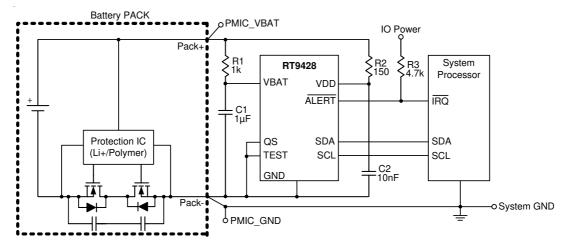

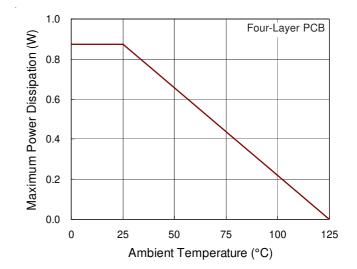

## **Typical Application Circuit**

$^{\ast}$  : For better noise reduction performance and improve measurement accuracy, add R1 R2 C2 are optional and recommended.

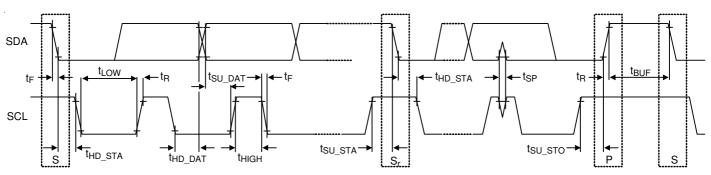

## **Timing Diagram**

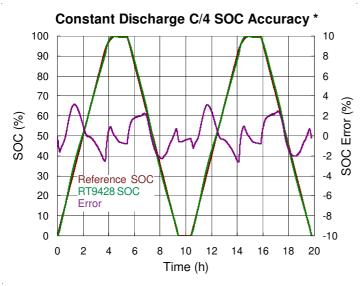

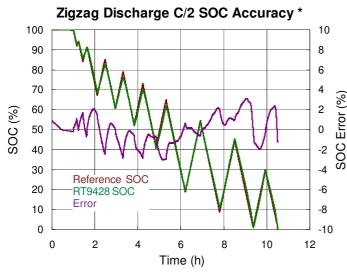

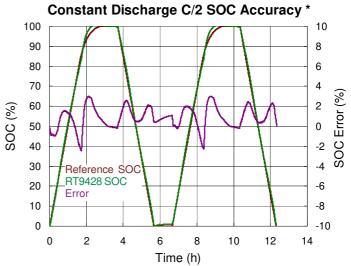

## **Typical Operating Characteristics**

(T<sub>A</sub> = 25°C, battery is Sanyo UF534553F, unless otherwise specified.)

\* : Sample accuracy with custom parameters into the IC.

## **Application Information**

#### Voltaic Gauge Theory and Performance

The embedded Fuel Gauge calculates and determines the Li+ battery SOC according to battery voltage only.

The algorithm estimates the increasing or decreasing SOC by an iteration model according to the difference between battery voltage and the battery OCV. The dynamic voltaic information can effectively emulate the Li+ battery behavior and determines the SOC (%), but can't report capacity (mAh).

The calculation is based on the battery voltage information and the dynamic difference between battery voltage and relaxed OCV, by using iteration algorithm to estimate the increasing or decreasing SOC to calculate SOC. Comparing to coulomb counter based fuel gauge solution; voltaic gauge does not accumulate error with time and current. The coulomb counter based fuel gauge suffers from SOC drift due to current-sense error and cell selfdischarge. Even there is a very small current sensing error, the coulomb counter accumulates the error from time to time. The accumulated error can be eliminated by only full charged or full discharged. The VoltaicGauge estimates battery SOC by only voltage information and will not accumulate error because it does not rely on battery current information.

#### **Power On**

When the IC is powered on by the battery insertion, the IC measures the battery voltage quickly and predicts the first SOC according to the voltage. The first SOC would be accurate if the battery has been well relaxed for over 30 min. Otherwise, the initial SOC error occurs.

However, the initial SOC error will be convergent and the SOC will be adjusted gradually and finally approach to the accurate SOC without accumulation error.

#### **Quick Sensing**

A Quick Sensing operation allows the RT9428 to restart sensing and SOC calculation. It has the same behavior as power on. The operation is used to reduce the initial SOC error caused by unwell power-on sequence. A Quick Sensing operation could be performed by either a rising edge on the QS pin or  $I^2C$  Quick Sensing command to the Control register. QS pin active high to restart the SOC calculation, and pull low to GND during normal operation.

#### **Temperature Compensation**

To maximize the SOC performance, the host must measure battery temperature periodically, and compensate the VGCOMP Voltaic-Gauge parameter at least once per minute.

Contact Richtek for instructions for temperature compensation.

#### **ALERT Interrupt**

The RT9428 monitors the SOC and reports the alert condition if the SOC change over 1% or if the SOC falls below the SOCLow which is in the Config (0Dh) register.

When alert condition occurs, the RT9428 outputs logiclow to the ALERT pin and sets 1 to the [Alert] bit in the Config register and sets 1 to the corresponding alert flag in the Status register. The only three ways to recover the alert condition is writing 0 to clear [Alert] bit or writing 0 to clear both [SL] and [SC] bit or power on reset. Before the recovery, the [Alert] bit will keep 1 and the ALERT pin will keep logic-low. It can't recover the alert condition by entering sleep mode.

Please note that the SOC low alert detection function is enable when power on.

#### Sleep Mode

RT9428 will enter sleep mode if host pulls low both SDA and SCL to logic-low at least 2.5s. All operation such as voltage measurement and SOC calculation are halted and power consumption is reduced under  $3\mu$ A in sleep mode. Any rising edge of SDA or SCL will transfer IC back to active mode immediately.

The other way to enter sleep mode is write [Sleep] bit in the Config register to 1 through  $I^2C$  communication, and the only way to exit sleep mode is to write [Sleep] bit to logic 0 or power on reset the IC.

Copyright ©2020 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

www.richtek.com

#### Initialization

The RT9428 can be reset by writing an initialization command to MFA resister. The behavior of initialization is the same as power on reset.

#### I<sup>2</sup>C Register

The RT9428 supports the following 16-bit I<sup>2</sup>C registers: VBAT, SOC, Control, Device ID, Config and MFA.

The register writing is valid when all of 16 bits data are transferred; otherwise, the write data will be ignored. The valid register addresses are defined in Table 1. Other remaining addresses are reserved.

| Address<br>(Hex) | Register  | Description                                                                                                                                 | Read/<br>Write | Default<br>(Hex) |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|

| 02h-03h          | VBAT      | It reports voltage measured from the input of VBAT pin.                                                                                     | R              |                  |

| 04h-05h          | SOC       | It reports the SOC result calculated by voltaic-gauge algorithm.                                                                            | R              |                  |

| 06h-07h          | Control   | It's the command interface for special function such as Quick Sensing.                                                                      | W              |                  |

| 08h-09h          | Device ID | It reports the device ID.                                                                                                                   | R              |                  |

| 0Ah              | Status    | It reports alert status.                                                                                                                    |                | 01h              |

| 0Bh              | dSOC      | It reports approximately incremental SOC in unit of 1% per hour.                                                                            |                |                  |

| 0Ch-0Dh          | Config    | The Config register includes the parameter of compensation, setting of sleep mode and SOCLow threshold. It also indicates the alert status. | R/W            | 321Ch            |

| 0Eh-0Fh          | OCV       | It reports Open Circuit Voltage corresponding to present SOC in unit of 1.25mV.                                                             |                |                  |

| FEh-FFh          | MFA       | Manufacturer Access. Sends special commands to the IC for the manufacturing.                                                                | W              |                  |

#### Table 1. I<sup>2</sup>C Register

#### VBAT

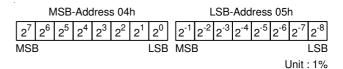

SOC

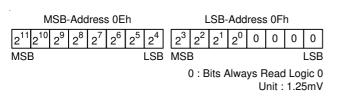

The VBAT register is a read only register that reports the measured voltage at VBAT pin. The VBAT is reported in units of 1.25mV. The first report is made after chip POR with 250ms delay and then updates 1s periodically. Figure 1 shows the VBAT register format.

|                 | Ν               | ISB            | -Ado           | dres           | s 02           | h              |                |                | L              | SB             | Add            | Iress | s 03l | h |     |

|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|-------|---|-----|

| 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | 0     | 0     | 0 | 0   |

| MSE             | 3               |                |                |                |                |                | LSB            | MSE            | 3              |                |                |       |       |   | LSB |

| ЛSE | 3 |  |  | l | LSB | MSE | 3     |       |      |      |      |       | LSB   |  |

|-----|---|--|--|---|-----|-----|-------|-------|------|------|------|-------|-------|--|

|     |   |  |  |   |     | (   | ) : B | its A | Alwa | ys F | Read | l Log | gic O |  |

Unit : 1.25mV

#### Figure 1. VBAT Register

The SOC register is a read only register that returns the relative state of charge of the cell as calculated by the voltaic gauge algorithm. The result is displayed as a percentage of the cell's full capacity. The high byte is reported in units of %. The low byte is reported in units of 1/256%. Figure 2 shows the SOC register format.

Figure 2. SOC Register

#### Control

The Control register allows the host processor to send special commands to the IC (Table2). Valid Control register write values are listed as follows. All other Control register values are reserved.

| Table 2. | Control | Register | Commands |

|----------|---------|----------|----------|

|----------|---------|----------|----------|

| Value | Command          | Description                            |

|-------|------------------|----------------------------------------|

| 4000h | Quick<br>Sensing | Restart sensing and<br>SOC calculation |

## **RT9428**

#### **Device ID**

The Device ID register is a read only register that contains a value indicating the production ID of the RT9428.

#### dSOC

The dSOC register is a read only registert that reports the approximately incremetal SOC in unit of 1% per hour.

#### Config

The Config register includes the parameter of compensation, setting of sleep mode and SOCLow threshold. It also indicates the alert status. The format of Config is shown in Figure 3.

VGCOMP is the setting to optimize IC performance for different cell chemistries or temperatures. Contact Richtek for instructions for optimization. The power on reset value for VGCOMP is 32h.

| Register | Bit | Description |

|----------|-----|-------------|

| 0x0C     | 7:0 | VGCOMP      |

|          | 7   | Sleep       |

| 0x0D     | 6   | SCEN        |

| 0x0D     | 5   | Alert       |

|          | 4:0 | SOCLow      |

Figure 3. Config Register

#### [Sleep]

Writing [Sleep] to logic 1 forces the IC to enter Sleep mode. Writing [Sleep] to logic 0 forces the IC to exit Sleep mode. The power on reset value for [Sleep] is logic 0.

#### [SCEN]

Writing [SCEN] to logic 1 to enable SOC Change Alert. When SOC Change Alert is enabled, the [SC] flag is set to 1 if SOC is changed at least 1%. The power on reset value for [SCEN] is logic 0.

#### [Alert]

The [Alert] bit is set by the IC when the alert condition occurs. The [Alert] bit is cleared by either host writing 0 to clear or a reset condition occurs.

The power on reset value for [Alert] is logic 0.

#### [SOCLow]

The SOCLow is a 5-bit value for setting the low battery alert threshold and defined as 2's-complement form. The programming unit is 1% and range is 32% to 1%. (00000 = 32%, 10001 = 15%, 11100 = 4%, 11111 = 1%). The power on reset value for SOCLow is 4% or 1Ch.

#### MFA

The MFA register allows the host processor to send special commands to the chip for manufacturing. Valid MFA register write values are listed as follows. All other MFA register values are reserved. Table 3 shows MFA register commands.

| Value | Command        | Description  |

|-------|----------------|--------------|

| 5400h | Initialization | Reset the IC |

#### Status

The Status register reports the alert status of RT9428. When any alert flag of Status register is set, the [Alert] flag of Config register will be set.

#### [SC]

The [SC] flag is set when SOC changes at least 1%. The [SC] flag is cleared by either host writing 0 to clear or a reset condition occurs. The power on reset value of [SC] is logic 0.

#### [SL]

The [SL] flag is set when SOC is lower than SOC threshold set by [SOCLow] bits. The [SL] flag is cleared by either host writing 0 to clear or a reset condition occurs. The power on reset value of [SL] is logic 0.

#### [RI]

The [RI] flag is set at POR and could be cleared after configuration. The power on reset value of [RI] is logic 1.

#### OCV

The OCV register reports Open Circuit Voltage corresponding to present SOC in unit of 1.25mV.

Figure 4. OCV Register

| Register | Bit | Description |  |  |

|----------|-----|-------------|--|--|

| 0x0A     | 7:6 | Reserved    |  |  |

|          | 5   | SC          |  |  |

|          | 4   | SL          |  |  |

|          | 3:1 | Reserved    |  |  |

|          | 0   | RI          |  |  |

Figure 5. Status Register

Figure 6. RT9428 Application Example with Alert Interrupt

Figure 6 presents a single cell battery-powered system application. The RT9428 is used on system side and direct powered from the battery.

The RC filter saves the noise for IC power supply and voltage measurement on VBAT pin.

To reduce the I-R drop effect, make the connection of VBAT as close as possible to the battery pack.

The ALERT pin provides a battery low interrupt signal to system processor when capacity low is detected.

The QS pin is unused in this configuration, so it needs to be tied to GND.

#### I<sup>2</sup>C Bus Interface

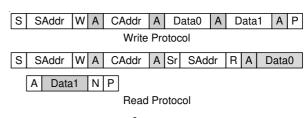

Figure 7 shows the timing diagram of the I<sup>2</sup>C interface.

The RT9428 communicates with a host (master) by using the standard  $I^2C$  2-wire interface. After the START condition, the  $I^2C$  master sends 8-bit data, consisting of 7-bit slave address and a following data direction bit (R/W).

A byte of data consists of 8 bits ordered MSB first and the LSB followed by the Acknowledge bit.

The RT9428 address is 0110110 (6Ch) and is a receive only (slave) device. The second word selects the register to which the data will be written. The third word contains data to write to the selected register.

Table 4 applies to the transaction formats.

| Symbol | Description                          | Symbol                               | Description                     |

|--------|--------------------------------------|--------------------------------------|---------------------------------|

| S      | START bit                            | Sr                                   | Repeated START                  |

| SAddr  | Slave address (7bit)                 | R/W                                  | Read : R/W = 1; Write : R/W = 0 |

| CAddr  | Command address (byte)               | Р                                    | STOP bit                        |

| Data   | Data byte written by master          | Data Data byte returned by slave     |                                 |

| А      | Acknowledge bit written by master    | A Acknowledge bit returned by slave  |                                 |

| Ν      | No acknowledge bit written by master | No acknowledge bit returned by slave |                                 |

#### Table4. 2-Wire Protocol

#### **Thermal Considerations**

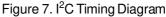

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

$P_{D(MAX)} = \left(T_{J(MAX)} - T_A\right) / \theta_{JA}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. For WL-CSP-8B 1.6x1.52 (BSC) package, the thermal resistance,  $\theta_{JA}$  is 114.4°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula :

$$\label{eq:PDMAX} \begin{split} P_{D(MAX)} &= (125^{\circ}C - 25^{\circ}C) \ / \ (114.4^{\circ}C/W) = 0.87W \ \text{for} \\ WL\text{-}CSP\text{-}8B \ 1.6x1.52 \ (BSC) \ \text{package} \end{split}$$

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 8 allow the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 8. Derating Curve of Maximum Power Dissipation

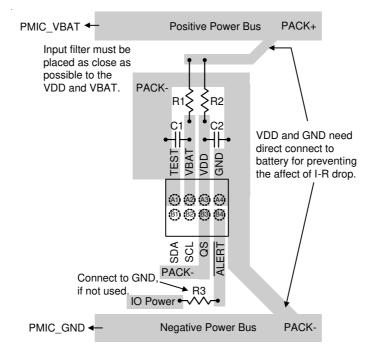

#### Layout Considerations

Figure 9. PCB Layout Guide

## **Outline Dimension**

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |  |

|--------|---------------------------|-------|----------------------|-------|--|

|        | Min                       | Max   | Min                  | Мах   |  |

| A      | 0.500                     | 0.600 | 0.020                | 0.024 |  |

| A1     | 0.170                     | 0.230 | 0.007                | 0.009 |  |

| b      | 0.240                     | 0.300 | 0.009                | 0.012 |  |

| D      | 1.470                     | 1.570 | 0.058                | 0.062 |  |

| D1     | 0.400                     |       | 0.016                |       |  |

| E      | 1.550                     | 1.650 | 0.061                | 0.065 |  |

| E1     | 1.200                     |       | 0.047                |       |  |

| е      | 0.400                     |       | 0.016                |       |  |

8B WL-CSP 1.6x1.52 Package (BSC)

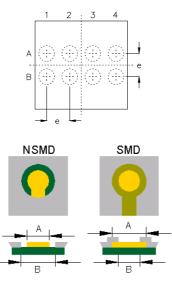

## **Footprint Information**

| Package               | Number of<br>Pin | Туре | Footprint Dimension (mm) |       |       | Tolerance  |

|-----------------------|------------------|------|--------------------------|-------|-------|------------|

|                       |                  |      | е                        | А     | В     | TOIETAILCE |

| WL-CSP1.6x1.52-8(BSC) | 8                | NSMD | 0.400                    | 0.240 | 0.340 | ±0.025     |

|                       |                  | SMD  |                          | 0.270 | 0.240 |            |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.