# Product Document

# **AS7261N**

# **XYZ Tri-Stimulus and NIR Sensor with Electronic Shutter**

# **General Description**

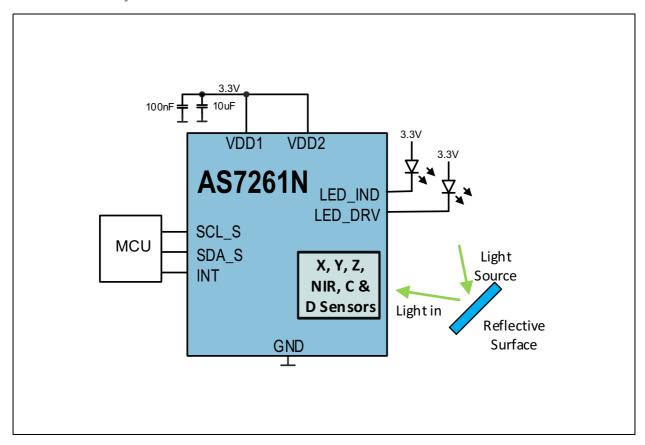

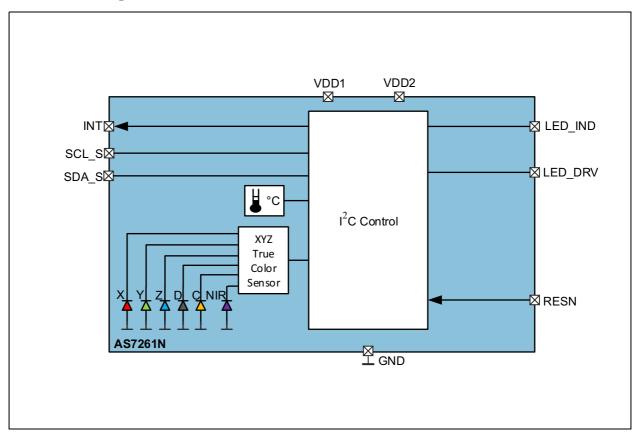

The AS7261N provides direct XYZ sensor data which conforms to the tri-stimulus standard observer color response of the human eye. A near-IR channel enables additional application flexibility. LED drivers with programmable currents are provided for electronic shutter applications.

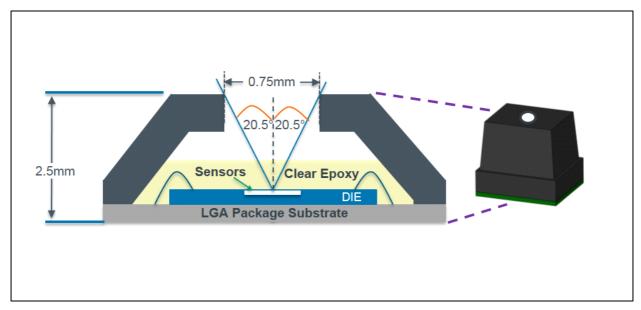

The AS7261N integrates Gaussian filters into standard CMOS silicon via nano-optic deposited interference filter technology and is packaged in an LGA package that provides a built in aperture to control the light entering the sensor array.

Control and spectral data access is implemented through an I<sup>2</sup>C register set.

Ordering Information and Content Guide appear at end of datasheet.

# **Key Benefits & Features**

The benefits and features of AS7261N, XYZ Tri-Stimulus and NIR Sensor with Electronic Shutter are listed below:

Figure 1: **AS7261N Benefits and Features**

| Benefits                                                               | Features                                                                      |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| XYZ channel data conforming to human eye response to color information | XYZ tri-stimulus standard observer filter set                                 |

| High accuracy ambient light measurements                               | Ambient light sensing (photopic response)                                     |

| Direct register read and write with interrupt on sensor ready          | I <sup>2</sup> C slave digital Interface with optional interrupt operation    |

| High stability over lifetime with minimal drift over temperature       | Filter set realized by silicon interference filters                           |

| No additional signal conditioning required                             | 16-bit ADC with digital access                                                |

| Direct register read and write with interrupt on sensor ready          | I <sup>2</sup> C slave digital Interface with optional interrupt<br>operation |

| Benefits                                      | Features                                                                      |

|-----------------------------------------------|-------------------------------------------------------------------------------|

| Electronic shutter control/synchronization    | Programmable LED drivers                                                      |

| Low voltage operation                         | • 2.7V to 3.6V with I <sup>2</sup> C interface                                |

| Small, robust package, with built-in aperture | • 20-pin LGA package 4.5mm x 4.7mm x 2.5mm<br>-40°C to 85°C temperature range |

# **Application**

The AS7261N applications include:

- Color measurement and absorbance

- Color matching and identification

- Precision color tuning/calibration

# **System Block Diagram**

Figure 2: AS7261N Sensor System

Page 2

Document Feedback

[v1-02] 2017-Feb-27

# **Pin Assignments**

The device pin assignments are described below.

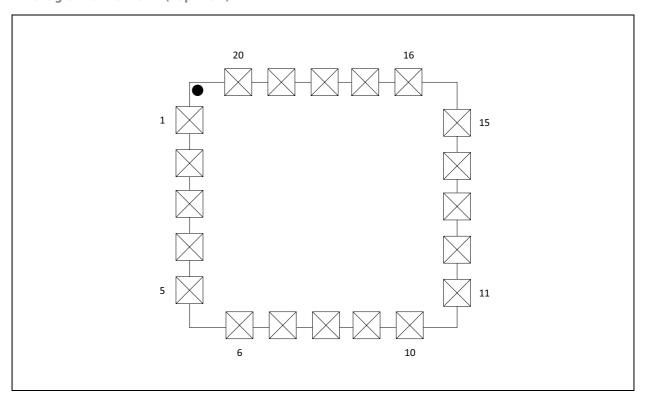

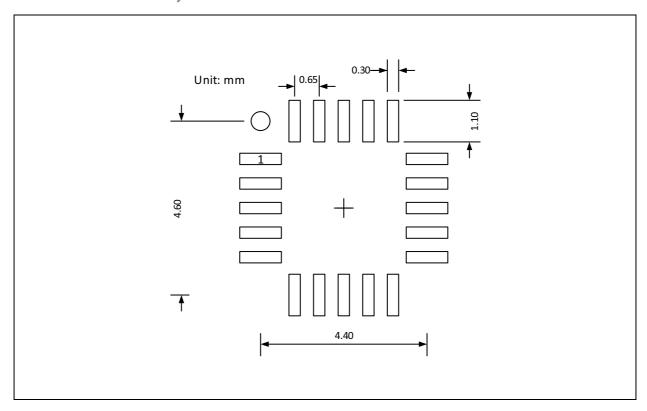

Figure 3: Pin Diagram of AS7261N (Top View)

# **Pin Description**

Figure 4: Pin Description of AS7261N

| Pin Number | Pin Name | Description                      |

|------------|----------|----------------------------------|

| 1          | NF       | Not Functional. Do not connect.  |

| 2          | RESN     | Reset, Active LOW                |

| 3          | NF       | Not Functional. Do not connect.  |

| 4          | NF       | Not Functional. Do not connect.  |

| 5          | NF       | Not Functional. Do not connect.  |

| 6          | NF       | Not Functional. Do not connect.  |

| 7          | NF       | Not Functional. Do not connect.  |

| 8          | NF       | Not Functional. Do not connect.  |

| 9          | SCL_S    | I <sup>2</sup> C Slave Clock pin |

| 10         | SDA_S    | I <sup>2</sup> C Slave Data pin  |

| 11         | NF       | Not Functional. Do not connect.  |

ams Datasheet Page 3

[v1-02] 2017-Feb-27

Document Feedback

| Pin Number | Pin Name | Description                                      |

|------------|----------|--------------------------------------------------|

| 12         | NF       | Not Functional. Do not connect.                  |

| 13         | INT      | Interrupt, active high                           |

| 14         | VDD2     | Voltage Supply                                   |

| 15         | LED_DRV  | LED Driver Output for Driving LED Current Sink   |

| 16         | GND      | Ground                                           |

| 17         | VDD1     | Voltage Supply                                   |

| 18         | LED_IND  | LED Driver Output for Indicator LED Current Sink |

| 19         | NF       | Not Functional. Do not connect.                  |

| 20         | NF       | Not Functional. Do not connect.                  |

Page 4ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

# **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The device is not designed for high energy UV (ultraviolet) environments, including upward looking outdoor applications, which could affect long term optical performance.

Figure 5: Absolute Maximum Ratings

| Symbol              | Parameter                             | Min          | Max          | Units     | Comments                                                                                                                                                                                                                 |  |  |  |  |

|---------------------|---------------------------------------|--------------|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     |                                       | Electrica    | l Parameters |           |                                                                                                                                                                                                                          |  |  |  |  |

| V <sub>DD_MAX</sub> | Supply Voltages VDD1,<br>VDD2         | -0.3         | 5            | V         | Pins VDD1 & VDD2 must be sourced from the same supply voltage                                                                                                                                                            |  |  |  |  |

| V <sub>DD_IO</sub>  | Input/Output Pin<br>Voltage           | -0.3         | VDD+0.3      | V         | Input/Output Pin to GND                                                                                                                                                                                                  |  |  |  |  |

| I <sub>SCR</sub>    | Input Current<br>(latch-up immunity)  | ±100 mA      |              |           | JESD78D                                                                                                                                                                                                                  |  |  |  |  |

|                     | Electrostatic Discharge               |              |              |           |                                                                                                                                                                                                                          |  |  |  |  |

| ESD <sub>HBM</sub>  | Electrostatic Discharge<br>HBM        | ±1           | 000          | V         | JS-001-2014                                                                                                                                                                                                              |  |  |  |  |

| ESD <sub>CDM</sub>  | Electrostatic Discharge<br>CDM        | ±500         |              | V         | JSD22-C101F                                                                                                                                                                                                              |  |  |  |  |

|                     | Temper                                | ature Ranges | and Storage  | Condition | s                                                                                                                                                                                                                        |  |  |  |  |

| T <sub>STRG</sub>   | Storage Temperature                   | -40          | 85           | °C        |                                                                                                                                                                                                                          |  |  |  |  |

| T <sub>BODY</sub>   | Package Body<br>Temperature           |              | 260          | °C        | IPC/JEDEC J-STD-020. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices" |  |  |  |  |

| RH <sub>NC</sub>    | Relative Humidity<br>(non-condensing) | 5            | 85           | %         |                                                                                                                                                                                                                          |  |  |  |  |

| MSL                 | Moisture Sensitivity<br>Level         | 3            |              |           | Maximum floor life time of 168 hours                                                                                                                                                                                     |  |  |  |  |

ams Datasheet Page 5

[v1-02] 2017-Feb-27

Document Feedback

# **Electrical Characteristics**

All limits are guaranteed with VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB} = 25^{\circ}\text{C}$ . The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. VDD1 and VDD2 must be sourced from the same power supply.

Figure 6: Electrical Characteristics of AS7261N

| Symbol                       | Parameter                                                       | Conditions                 | Min            | Тур | Max  | Unit |  |  |  |

|------------------------------|-----------------------------------------------------------------|----------------------------|----------------|-----|------|------|--|--|--|

| General Operating Conditions |                                                                 |                            |                |     |      |      |  |  |  |

| VDD                          | Voltage Operating<br>Supply                                     | I <sup>2</sup> C Interface | ce 2.7 3.3 3.6 |     | V    |      |  |  |  |

| T <sub>AMB</sub>             | Operating Temperature                                           |                            | -40            | 25  | 85   | °C   |  |  |  |

| I <sub>VDD</sub>             | Operating Current                                               |                            |                |     | 5    | mA   |  |  |  |

| I <sub>STANDBY</sub> (1)     | Standby Current                                                 |                            |                | 12  |      | μΑ   |  |  |  |

|                              |                                                                 | Internal RC Oscillator     | 1              | 1   | •    |      |  |  |  |

| F <sub>OSC</sub>             | Internal RC Oscillator<br>Frequency                             |                            | 15.7           | 16  | 16.3 | MHz  |  |  |  |

| t <sub>JITTER</sub> (2)      | Internal Clock Jitter                                           | @25°C                      |                |     | 1.2  | ns   |  |  |  |

|                              |                                                                 | Temperature Sensor         | 1              |     | l    | l    |  |  |  |

| D <sub>TEMP</sub>            | Absolute Accuracy of the<br>Internal Temperature<br>Measurement |                            | -8.5           |     | 8.5  | °C   |  |  |  |

|                              |                                                                 | Indicator LED              | ı              |     |      |      |  |  |  |

| I <sub>IND</sub>             | LED Current                                                     | 1, 2, 4 or 8               | 1              |     | 8    | mA   |  |  |  |

| I <sub>ACC</sub>             | Accuracy of Current                                             |                            | -30            |     | 30   | %    |  |  |  |

| V <sub>LED</sub>             | Voltage Range of<br>Connected LED                               | Vds of current sink        | 0.3            |     | VDD  | V    |  |  |  |

| LED_DRV                      |                                                                 |                            |                |     |      |      |  |  |  |

| I <sub>LED1</sub>            | LED Current                                                     | 12.5, 25, 50 or 100        | 12.5           |     | 100  | mA   |  |  |  |

| I <sub>ACC</sub>             | Accuracy of Current                                             |                            | -10            |     | 10   | %    |  |  |  |

| V <sub>LED</sub>             | Voltage Range of<br>Connected LED                               | Vds of current sink        | 0.3            |     | VDD  | V    |  |  |  |

Page 6ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

| Symbol                            | Parameter                         | Conditions    | Min      | Тур | Max          | Unit |  |  |  |

|-----------------------------------|-----------------------------------|---------------|----------|-----|--------------|------|--|--|--|

|                                   | Digital Inputs and Outputs        |               |          |     |              |      |  |  |  |

| I <sub>IH</sub> , I <sub>IL</sub> | Logic Input Current               | Vin=0V or VDD | -1       |     | 1            | μΑ   |  |  |  |

| I <sub>IL RESN</sub>              | Logic Input Current<br>(RESN pin) | Vin=0V        | -1       |     | -0.2         | mA   |  |  |  |

| V <sub>IH</sub>                   | CMOS Logic High Input             |               | 0.7* VDD |     | VDD          | V    |  |  |  |

| V <sub>IL</sub>                   | CMOS Logic Low Input              |               | 0        |     | 0.3*<br>VDD  | V    |  |  |  |

| V <sub>OH</sub>                   | CMOS Logic High Output            | I=1mA         |          |     | VDD -<br>0.4 | V    |  |  |  |

| V <sub>OL</sub>                   | CMOS Logic Low Output             | I=1mA         |          |     | 0.4          | V    |  |  |  |

| t <sub>RISE</sub> (2)             | Current Rise Time                 | C(Pad)=30pF   |          |     | 5            | ns   |  |  |  |

| t <sub>FALL</sub> (2)             | Current Fall Time                 | C(Pad)=30pF   |          |     | 5            | ns   |  |  |  |

## Note(s):

- $1.\,15\mu A$  over temperature

- 2. Guaranteed, not tested in production

# **Timing Characteristics**

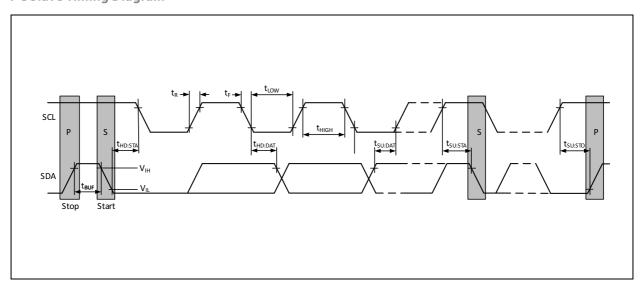

Figure 7: AS7261N I<sup>2</sup>C Slave Timing Characteristics

| Symbol                     | Parameter                              | Conditions                                   | Min | Тур | Max | Unit |  |

|----------------------------|----------------------------------------|----------------------------------------------|-----|-----|-----|------|--|

| I <sup>2</sup> C Interface |                                        |                                              |     |     |     |      |  |

| f <sub>SCLK</sub>          | SCL Clock Frequency                    |                                              | 0   |     | 400 | kHz  |  |

| t <sub>BUF</sub>           | Bus Free Time Between a STOP and START |                                              | 1.3 |     |     | μs   |  |

| t <sub>HS:STA</sub>        | Hold Time (Repeated) START             |                                              | 0.6 |     |     | μs   |  |

| t <sub>LOW</sub>           | LOW Period of SCL Clock                |                                              | 1.3 |     |     | μs   |  |

| t <sub>HIGH</sub>          | HIGH Period of SCL Clock               |                                              | 0.6 |     |     | μs   |  |

| t <sub>SU:STA</sub>        | Setup Time for a Repeated START        |                                              | 0.6 |     |     | μs   |  |

| t <sub>HS:DAT</sub>        | Data Hold Time                         |                                              | 0   |     | 0.9 | μs   |  |

| t <sub>SU:DAT</sub>        | Data Setup Time                        |                                              | 100 |     |     | ns   |  |

| t <sub>R</sub>             | Rise Time of Both SDA and SCL          |                                              | 20  |     | 300 | ns   |  |

| t <sub>F</sub>             | Fall Time of Both SDA and SCL          |                                              | 20  |     | 300 | ns   |  |

| t <sub>SU:STO</sub>        | Setup Time for STOP Condition          |                                              | 0.6 |     |     | μs   |  |

| C <sub>B</sub>             | Capacitive Load for Each Bus Line      | CB — total capacitance of one bus line in pF |     |     | 400 | pF   |  |

| C <sub>I/O</sub>           | I/O Capacitance (SDA, SCL)             |                                              |     |     | 10  | pF   |  |

Figure 8: I<sup>2</sup>C Slave Timing Diagram

Page 8ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

# **Operation Characteristics**

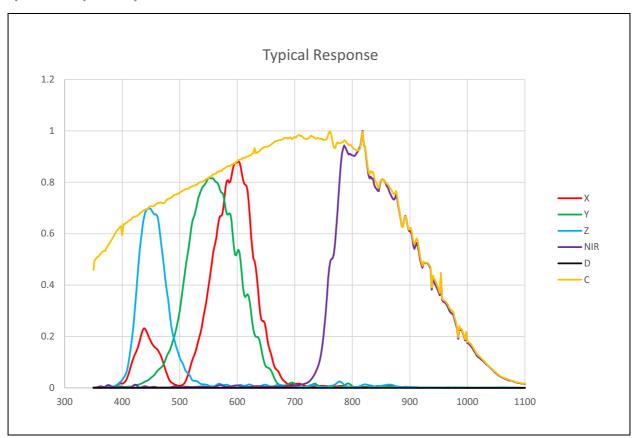

Figure 9: Spectral Responsivity

Figure 10: AS7261N Optical Characteristics (Pass Band)

| Symbol  | Parameter   | Test Conditions                                     | Min | Тур  | Max | Unit                             |

|---------|-------------|-----------------------------------------------------|-----|------|-----|----------------------------------|

| Х       | Channel X   | White LED 5700K source, Ee=116μW/cm <sup>2</sup>    |     | 7.7  |     | counts/<br>(μW/cm <sup>2</sup> ) |

| Y       | Channel Y   | White LED 5700K source, Ee=116μW/cm <sup>2</sup>    |     | 8.6  |     | counts/<br>(μW/cm <sup>2</sup> ) |

| Z       | Channel Z   | White LED 5700K source, Ee=116μW/cm <sup>2</sup>    |     | 4.7  |     | counts/<br>(μW/cm <sup>2</sup> ) |

| NIR     | Channel NIR | Incandescent light source, Ee=465µW/cm <sup>2</sup> |     | 14.0 |     | counts/<br>(μW/cm <sup>2</sup> ) |

| С       | Channel C   | White LED 5700K source, Ee=116μW/cm <sup>2</sup>    |     | 18.1 |     | counts/<br>(μW/cm <sup>2</sup> ) |

| D_LED   | Channel D   | White LED 5700K source, Ee=116μW/cm <sup>2</sup>    |     | 0    | 15  | counts                           |

| D_INCAN | Channel D   | Incandescent light source, Ee=465μW/cm <sup>2</sup> |     |      | 15  | counts                           |

ams Datasheet Page 9

[v1-02] 2017-Feb-27

Document Feedback

| Symbol | Parameter                | Test Conditions | Min | Тур   | Max | Unit |

|--------|--------------------------|-----------------|-----|-------|-----|------|

| PFOV   | Package Field<br>of View |                 |     | ±20.5 |     | deg  |

## Note(s):

- 1. Each channel is tested with GAIN = 3.7x, Integration Time (INT\_T) = 166ms and  $T_{AMB}$ =25°C

- 2. The accuracy of each channel count is  $\pm 25\%$

Figure 11: AS7261N LGA Package Field of View

Page 10ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

# **Detailed Descriptions**

Figure 12: Internal Block Diagram

# **XYZ Sensor**

The AS7261N XYZ sensor is a next-generation digital color sensor device. It senses X, Y, Z standard observer filters compliant with the CIE 1931 standard observer color response in addition to near IR (NIR), Clear (C) and Dark (D) spectrum filters.

The sensor contains analog-to-digital converters (16-bit resolution ADC), which integrate current from each channel's photodiode. Upon completion of conversion cycle, the integrated result is transferred to the corresponding data register. Transfers are double-buffered to ensure integrity of the data is maintained.

Interference filters realize all filter responses and enable minimal life-time drift and very high temperature stability. Filter accuracy is affected by the optical angle of incidence which itself is limited by an integrated aperture and an internal micro-lens structure in the AS7261N. The package field of view (PFOV) is  $\pm 20.5^{\circ}$  to deliver the specified accuracy. External optics can be used as needed to expand or reduce this built in PFOV.

ams Datasheet Page 11

[v1-02] 2017-Feb-27

Document Feedback

#### **Data Conversion**

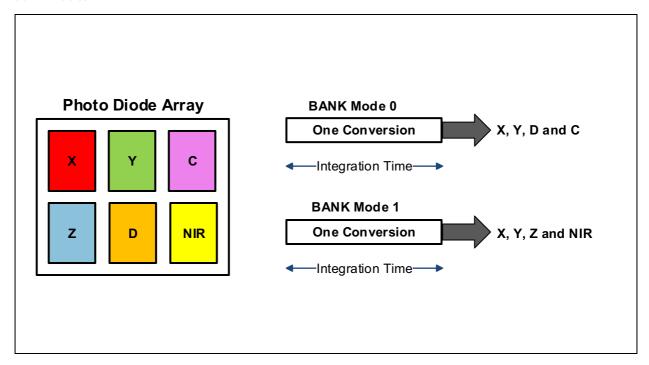

AS7261N spectral conversion is implemented via two photodiode banks. The first bank provides data from the X, Y, Z and NIR (near-IR) photodiodes. The second bank provides data from the same X and Y photodiodes as well as D (Dark) and C (Clear) photodiodes.

The spectral conversion process is controlled with two BANK Mode settings. Bank Mode 0 uses I<sup>2</sup>C registers for X, Y, D and C data. Bank Mode 1 uses I<sup>2</sup>C registers for X, Y, Z and NIR data. Sensor data is available in four I<sup>2</sup>C registers (NDATAL/NDATAH, XDATAL/XDATAH, YDATAL/YDATAH and ZDATAL/ZDATAH) as shown in the figures below.

Figure 13: Bank Modes

Figure 14:

AS7261N Sensor Data I<sup>2</sup>C Registers

| I <sup>2</sup> C Register | Bank Mode 0 | Bank Mode 1 |

|---------------------------|-------------|-------------|

| NDATAL/NDATAH             | С           | NIR         |

| XDATAL/XDATAH             | Х           | Х           |

| YDATAL/YDATAH             | Y           | Y           |

| ZDATAL/ZDATAH             | D           | Z           |

Page 12

Document Feedback

[v1-02] 2017-Feb-27

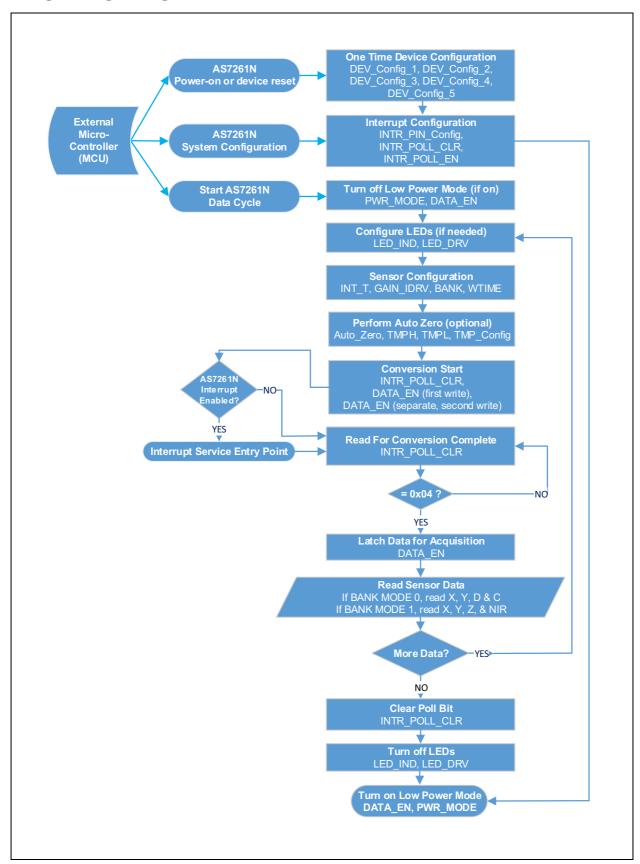

# **Spectral Conversion and Data Acquisition**

Spectral conversion uses a register set for integration time (register INT\_T). If both photodiode banks are required to complete the conversion, the second bank requires an additional integration time. Minimum conversion time for a single bank is 2.8 milliseconds. If data is required from all 6 photodiodes the device must perform 2 full conversions (2 x integration time). The user has control of gain for the photodiode current, programmed into bits 0 and 1 of the GAIN\_IDRV register where gain can be set to 1x, 3.7x, 16x or 64x. A wait time between integration cycles can be programmed into register WTIME using the same units as the INT\_T register.

An auto zero function is automatically performed before the first data conversion after a power-on or reset, in order to achieve the best data quality. Auto zero corrects for internal device temperature. But since it's automatically done only once, it can also be manually run. Typically, if the temperature changes by 15 degrees C or more the auto zero should be manually run by writing to the Auto\_Zero register (temperature is user calculated based on TMPL & TMPH registers values). But auto zero can also be manually done before every conversion. When auto zero function is complete the DONE bit (bit7) of Auto\_Zero register will be set to 1.

The BANK bit (bit7) in the BANK register can be changed as needed before data conversion to acquire the desired channels. While conversion is continuous, timing is done using registers. Both polling and interrupt operation are then supported for "conversion complete" timing. Both require programming the INTR\_POLL\_EN register bit 2 to a 1. The conversion process is started by writing a 0x01 to the DATA\_EN register followed by clearing any previous Data Valid bit in the INTR\_POLL\_CLR register. This is followed by a separate write of 0x03 to the DATA\_EN register.

If the AS7261N interrupt output is to be used for data conversion timing the INTR\_PIN\_Config register should be programmed to 0xCA. The INT pin will then be asserted high at the completion of the conversion cycle. A 0x04 should be written to the INTR\_POLL\_CLR register to clear this interrupt which also clears polling bit 2 in the register.

If only polling is to be used for conversion timing, an external interrupt is not required and the INTR\_PIN\_Config register should be programmed to 0x00. Polling of bit 2 in the INTR\_POLL\_CLR register will return 0x00 if the conversion is not complete, and 0x04 if complete. Once complete a 0x04 should be written to the INTR\_POLL\_CLR register to clear bit 2, the polled bit.

For acquisition, done after conversion, data needs to be latched by writing 0x83 to the DATA\_EN register. The purpose of latching the data by the user is to provide a mechanism for data to be coherent and under user control. Now, the data bank register can be read (one bank per single conversion-acquisition cycle). The CLR bit (bit2) should be

ams Datasheet Page 13

[v1-02] 2017-Feb-27 Document Feedback

cleared by writing a 1 to the CLR bit (bit2) of the INTR\_POLL\_ CLR register (0xF8) after each conversion-acquisition cycle is completed.

# **Temperature Sensor**

The Temperature Sensor measures on-chip temperature on demand, and enables temperature compensation procedures. The basic equation for calculating the internal temperature of the device is:

(EQ1)

$$\frac{0.7604 - \frac{TMP_{-} VALUE \bullet 2.048}{1024}}{2.046 \bullet 10^{-3}} - 40$$

TMP\_VALUE is the derived from TMPL & TMPH (0xD2 [1:0] and 0xD1 [7:0]) register data. Temperature conversions are performed by writing 0x24 to the TMP\_Config register. Polling the TMP\_Config register will indicate data acquisition is complete upon reading 0x84. After reading 0x84 the TMP\_Config register should be written to either 0x00 for idle or 0x24 to perform another temperature measurement. The result of the calculation is the device temperature in degree Celsius (°C).

# Electronic Shutter with LED\_IND or LED\_DRV Driver Control

Under user control there are two LED driver outputs that can be used to control LEDs on the two driver pins. This allows different wavelength light sources to be used in the same system. The LED output sink currents are programmable and can drive external LED sources. After programming for current the sources can be turned off and on via registers to provide the AS7261N with an electronic shutter capability. If turning LEDs on, they should be fully on optically before a conversion begins and not shut off until after the conversion-acquisition cycle completes

The LED\_IND pin can be turned on/off via the LED\_IND register with values 0x01, 0x05, 0x09 and 0x0D for sink currents of 1mA, 2mA, 4mA and 8mA respectively.

For the LED\_DRV pin, the GAIN\_IDRV Register (0xB9) bits 7 and 6 control the drive strength of the pin for current values 12.5mA, 25mA, 50mA and 100mA. This register also controls the gain of all light acquisitions so care should be taken when writing to it. The LED\_DRV pin can be turned on/off via the LED\_DRV register bit 2.

Page 14

Document Feedback [v1-02] 2017-Feb-27

#### Low Power Mode

AS7261N can be put into the low power mode by writing 0x02 to the POWER MODE Register (0x73). Write 0x00 to set it back to normal mode. Wait at least 50µs before doing further AS7261N operations after powering back to normal.

The sequence to configure AS7261N into low power mode:

- Write 0x00 to Register 0xFA

- Write 0x02 to Register 0x73

- AS7261N is in low power mode

The sequence to configure AS7261N out of low power mode:

- Write 0x00 to Register 0x73

- Wait for at least 50μS

- Write 0x03 to Register 0xFA

- AS7261N is in normal mode

# **Device Initialization and Pin Assignment**

On power up device needs to be initialized as follows before programming registers to do data conversion and acquisition:

- Device Config 1 register: 0x70 written to 0x8A

- Device Config 2 register: 0x71 written to 0x02

- Device Config 3 register: 0xB0 written to 0x02

- Device Config 4 register: 0x88 written to 0x00

- Device Config 5 register: 0x9A written to 0x02

- Interrupt Operation: The only user defined pin functionality is whether to use pin 13 as an interrupt signal at the completion of data conversion. This is done by programming the INTR\_PIN\_Config register (0x22) to 0xCA. To disable interrupt function the INTR\_PIN\_Config register should be programmed to 0x00, which is the power-on and reset default.

# **RC Oscillator**

An internal on-chip timing generation circuit provides a 16MHz temperature compensated oscillator for the AS7261N master clock.

ams Datasheet Page 15

[v1-02] 2017-Feb-27 Document Feedback

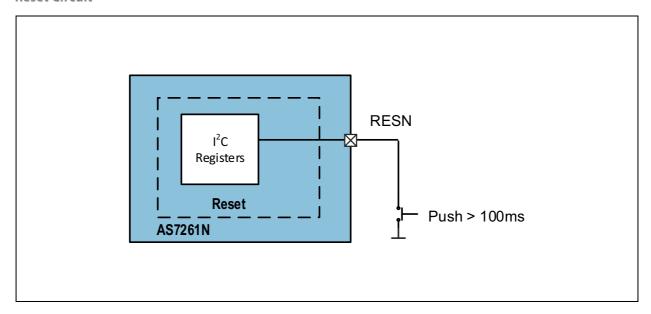

## Reset

Pulling down the RESN pin for longer than 100ms resets the AS7261N.

Figure 15: Reset Circuit

Page 16ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

Figure 16: I<sup>2</sup>C Register Programming Flow Chart

#### Note(s):

$1. When using shuttered \ LEDs, the \ LED \ source(s) \ should \ be \ at \ desired \ brightness \ before \ conversion \ starts.$

ams Datasheet Page 17

[v1-02] 2017-Feb-27 Document Feedback

# I<sup>2</sup>C Slave Interface

Interface, control and reading sensor data is accomplished through an I<sup>2</sup>C compatible slave interface via a set of registers.

#### I<sup>2</sup>C Feature List

• Fast mode (400 kHz) and standard mode (100 kHz) support

• 7+1-bit addressing mode

Write format: ByteRead format: Byte

# I<sup>2</sup>C Register Set

The 7-bit  $I^2C$  slave address of AS7261N is 0x49 plus one bit for read/write. When reading from  $I^2C$  registers, the 7 + 1-bit address should be 0x93. When writing to  $I^2C$  registers, the 7+1-bit address should be 0x92.

The figure below provides a summary of the AS7261N I<sup>2</sup>C register set. Figures after that provide additional details. All register data is hex, and all multi-byte entities are Big Endian (most significant byte is situated at the lower register address).

I<sup>2</sup>C register addresses not listed should be treated as reserved and not used.

Figure 17: I<sup>2</sup>C Register Set Overview

| Addr | Name                           | <d7></d7>              | <d6></d6> | <d5></d5>   | <d4></d4>  | <d3></d3>    | <d2></d2> | <d1></d1> | <d0></d0> |

|------|--------------------------------|------------------------|-----------|-------------|------------|--------------|-----------|-----------|-----------|

|      |                                |                        | Device    | e Version F | Registers  |              |           |           |           |

| 0x10 | DEV_ID                         |                        |           |             | Device Ide | entification | 1         |           |           |

| 0x11 | DEV_VER                        |                        |           |             | Device     | Version      |           |           |           |

|      | Device Configuration Registers |                        |           |             |            |              |           |           |           |

| 0x70 | DEV_Config_1                   |                        |           |             | Device Cor | nfiguration  | 1         |           |           |

| 0x71 | DEV_Config_2                   |                        |           |             | Device Cor | nfiguration  | 2         |           |           |

| 0xB0 | DEV_Config_3                   |                        |           |             | Device Cor | nfiguration  | 3         |           |           |

| 0x88 | DEV_Config_4                   |                        |           |             | Device Cor | nfiguration  | 4         |           |           |

| 0x9A | DEV_Config_5                   | Device Configuration 5 |           |             |            |              |           |           |           |

|      | Power Mode Register            |                        |           |             |            |              |           |           |           |

| 0x73 | PWR_MODE                       |                        |           | RE          | SV         |              |           | PM        | RESV      |

Page 18

Document Feedback

[v1-02] 2017-Feb-27

| Addr                                    | Name                  | <d7></d7>           | <d6></d6>  | <d5></d5>   | <d4></d4>    | <d3></d3>    | <d2></d2>    | <d1></d1> | <d0></d0> |

|-----------------------------------------|-----------------------|---------------------|------------|-------------|--------------|--------------|--------------|-----------|-----------|

| Interrupt and Polling Control Registers |                       |                     |            |             |              |              |              |           |           |

| 0x22                                    | INTR_PIN_Config       | ОР                  | IN         |             |              | Fl           | JNCT         |           |           |

| 0xF8                                    | INTR_POLL_CLR         |                     |            | RESV        |              |              | CLR          | RESV      |           |

| 0xF9                                    | INTR_POLL_EN          |                     |            | RESV        |              |              | EN           | R         | ESV       |

|                                         | LED Control Registers |                     |            |             |              |              |              |           |           |

| 0xEA                                    | LED_DRV               |                     |            | RESV        |              |              | ON_OFF       | R         | ESV       |

| 0x84                                    | LED_IND               |                     | RE:        | SV          |              | CUI          | RRENT        | RESV      | ON_OFF    |

|                                         |                       | Auto Z              | ero and Te | emperatur   | e Control    | Registers    |              |           |           |

| 0xBA                                    | Auto_Zero             |                     | RE:        | SV          |              | C_EN         | X_EN         | Y_EN      | Z_EN      |

| 0xD1                                    | TMPH                  |                     | Most       | Significant | bits (9:2) c | of Tempera   | ture Measure | ement     |           |

| 0xD2                                    | TMPL                  |                     |            | RE          | SV           |              |              | TI        | MPL       |

| 0xD3                                    | TMP_Config            | ISTAT               | RESV       | STRT        | RESV         |              | SF           | RC        |           |

|                                         |                       |                     | Senso      | r Control F | Registers    |              |              |           |           |

| 0xDB                                    | BANK                  | BANK                |            |             |              | RESV         |              |           |           |

| 0xB9                                    | GAIN_IDRV             | IDI                 | RV         |             | R            | ESV          | GAIN         |           | AIN       |

| 0xD9                                    | INT_T                 |                     |            |             | Integra      | tion Time    |              |           |           |

| 0xDA                                    | WTIME                 |                     |            |             | Wai          | t Time       |              |           |           |

| 0xFA                                    | DATA_EN               | DL                  |            | RESV        |              | WAIT         | RESV         | CON       | PON       |

|                                         |                       |                     | Sens       | or Data Re  | gisters      | l            |              |           |           |

| 0xDC                                    | NDATA_L               |                     |            |             | N Chann      | el Low Byte  | 9            |           |           |

| 0xDD                                    | NDATA_H               |                     |            |             | N Channe     | el High Byt  | e            |           |           |

| 0xDE                                    | YDATA_L               | Y Channel Low Byte  |            |             |              |              |              |           |           |

| 0xDF                                    | YDATA_H               | Y Channel High Byte |            |             |              |              |              |           |           |

| 0xEC                                    | ZDATA_L               | Z Channel Low Byte  |            |             |              |              |              |           |           |

| 0xED                                    | ZDATA_H               | Z Channel High Byte |            |             |              |              |              |           |           |

| 0xEE                                    | XDATA_L               |                     |            |             | X Channe     | el Low Byte  | <u></u>      |           |           |

| 0xEF                                    | XDATA_H               |                     |            |             | X Channe     | el High Byte | e            |           |           |

ams Datasheet Page 19

[v1-02] 2017-Feb-27 Document Feedback

# **Detailed Register Description**

Figure 18: Device ID and Version Registers

| Addr: 0x01 |                       | Device Identification |        |                                 |  |

|------------|-----------------------|-----------------------|--------|---------------------------------|--|

| Bit        | Bit Name              | Default               | Access | Bit Description                 |  |

| 7:0        | DEV_ID                | 01110010              | R      | Device identification number    |  |

| Addr: 0x11 |                       | Device Version        |        |                                 |  |

| A          | ddr: 0x11             |                       |        | Device Version                  |  |

| Bit        | ddr: 0x11<br>Bit Name | Default               | Access | Device Version  Bit Description |  |

Figure 19: Device Configuration Registers

| Ac  | ldr: 0x70    |                        | Device Configuration 1 |                                                                     |  |  |

|-----|--------------|------------------------|------------------------|---------------------------------------------------------------------|--|--|

| Bit | Bit Name     | Default                | Access                 | Bit Description                                                     |  |  |

| 7:0 | DEV_Config_1 |                        | R/W                    | Device Configuration 1, must be initialized to 0x8A by external MCU |  |  |

| Ac  | ldr: 0x71    |                        |                        | Device Configuration 2                                              |  |  |

| Bit | Bit Name     | Default                | Access                 | Bit Description                                                     |  |  |

| 7:0 | DEV_Config_2 |                        | R/W                    | Device Configuration 1, must be initialized to 0x02 by external MCU |  |  |

| Ad  | Addr: 0xB0   |                        | Device Configuration 3 |                                                                     |  |  |

| Bit | Bit Name     | Default                | Access                 | Bit Description                                                     |  |  |

| 7:0 | DEV_Config_3 |                        | R/W                    | Device Configuration 1, must be initialized to 0x02 by external MCU |  |  |

| Ac  | ldr: 0x88    | Device Configuration 4 |                        |                                                                     |  |  |

| Bit | Bit Name     | Default                | Access                 | Bit Description                                                     |  |  |

| 7:0 | DEV_Config_4 |                        | R/W                    | Device Configuration 1, must be initialized to 0x00 by external MCU |  |  |

| Ad  | Addr: 0x9A   |                        | Device Configuration 5 |                                                                     |  |  |

| Bit | Bit Name     | Default                | Access                 | Bit Description                                                     |  |  |

| 7:0 | DEV_Config_5 |                        | R/W                    | Device Configuration 1, must be initialized to 0x02 by external MCU |  |  |

Page 20ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

Figure 20: **Power Mode Register**

| Addr: 0x04/0x84 |          | PWR_MODE |        |                                                     |  |

|-----------------|----------|----------|--------|-----------------------------------------------------|--|

| Bit             | Bit Name | Default  | Access | Bit Description                                     |  |

| 7:2             | RESV     | 0        | R/W    | Reserved, set to 000000 if writing the register     |  |

| 1               | PM       | 1        | R/W    | 1= Normal Operation Power Mode<br>0= Low Power Mode |  |

| 0               | RSVD     | 0        | R/W    | Reserved, set to 0 if writing the register          |  |

Figure 21: **Interrupt Pin Configuration Register**

| A   | Addr: 0x22      |         | INTR_PIN_Config |                                                   |  |  |

|-----|-----------------|---------|-----------------|---------------------------------------------------|--|--|

| Bit | Bit Name        | Default | Access          | Bit Description                                   |  |  |

| 7:0 | INTR_PIN_Config | 0x00    | R/W             | 0x00 = INT pin disabled<br>0xCA = INT pin enabled |  |  |

Figure 22: **Interrupt and Polling Clear Register**

| Addr: 0xF8 |          | INTR_POLL_CLR |        |                                                                                                                                                                   |  |

|------------|----------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default       | Access | Bit Description                                                                                                                                                   |  |

| 7:3        | RESV     | 00000         | R/W    | Reserved, set to 00000 if writing the register                                                                                                                    |  |

| 2          | CLR      | 0             | R/W    | Set to 1 to clear any asserted interrupt pin INT (the interrupt channel ready must be enabled). If the interrupt channel ready is enabled this bit will read a 1. |  |

| 1:0        | RSVD     | 00            | R/W    | Reserved, set to 00 if writing the register                                                                                                                       |  |

Figure 23: **Interrupt and Polling Enable Register**

| Addr: 0xF9 |          | INT_POLL_EN |        |                                                                     |  |

|------------|----------|-------------|--------|---------------------------------------------------------------------|--|

| Bit        | Bit Name | Default     | Access | Bit Description                                                     |  |

| 7:3        | RESV     | 0           | R/W    | Reserved, set to 00000 if writing the register                      |  |

| 2:1        | EN       | 0           | R/W    | Set to 1 to enable the channel data ready for polling or interrupt. |  |

| 0          | RSVD     | 0           | R/W    | Reserved, set to 0 if writing the register                          |  |

ams Datasheet Page 21 [v1-02] 2017-Feb-27 Document Feedback

Figure 24: LED Driver Register

| Addr: 0xEA |          | LED_DRV |        |                                                                                                                           |  |

|------------|----------|---------|--------|---------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                                                                           |  |

| 7:3        | RESV     | 0       | R/W    | Reserved, set to 00000 if writing the register                                                                            |  |

| 2          | ON_OFF   | 0       | R/W    | Set to 1 to enable the LED_DRV pin to the current level specified by the register GAIN_IDRV (0xB9). Set to 0 to turn off. |  |

| 0:1        | RSVD     | 0       | R/W    | Reserved, set to 00 if writing the register                                                                               |  |

Figure 25: LED Indicator Register

| Addr: 0x84 |          | LED_IND |        |                                                                                                              |  |

|------------|----------|---------|--------|--------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                                                              |  |

| 7:4        | RESV     | 0       | R/W    | Reserved, set to 0 if writing the register                                                                   |  |

| 3:2        | CURRENT  | 00      | R/W    | For LED_IND pin current value (when on). Set to: 'b00=1mA; 'b01=2mA; 'b10=4mA; 'b11=8mA;                     |  |

| 1          | RSVD     | 0       | R/W    | Reserved, set to 0 if writing the register                                                                   |  |

| 0          | ON_OFF   | 0       | R/W    | Set to 1 to enable the LED_DRV pin to the current level specified by the CURRENT bits. Set to 0 to turn off. |  |

Page 22ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

Figure 26: Auto Zero Register

| Ad  | Addr: 0xBA |         | Auto_Zero |                                                                                                           |  |  |

|-----|------------|---------|-----------|-----------------------------------------------------------------------------------------------------------|--|--|

| Bit | Bit Name   | Default | Access    | Bit Description                                                                                           |  |  |

| 7   | DONE       | 0       | R/W       | Will be set to 1 when any auto zero function is completed. Set to 0 if writing to the register.           |  |  |

| 6:4 | RESV       | 0       | R/W       | Reserved, set to 000 if writing the register                                                              |  |  |

| 3   | C_EN       | 0       | R/W       | Set to 1 to manually run auto zero on the C channel. Will be automatically set to 0 when DONE bit is set. |  |  |

| 2   | X_EN       | 0       | R/W       | Set to 1 to manually run auto zero on the X channel. Will be automatically set to 0 when DONE bit is set. |  |  |

| 1   | Y_EN       | 0       | R/W       | Set to 1 to manually run auto zero on the Y channel. Will be automatically set to 0 when DONE bit is set. |  |  |

| 0   | Z_EN       | 0       | R/W       | Set to 1 to manually run auto zero on the Z channel. Will be automatically set to 0 when DONE bit is set. |  |  |

ams Datasheet Page 23

[v1-02] 2017-Feb-27

Document Feedback

# Temperature Measurement High Register (bits 9:2)

TMP\_VALUE is the value from TMPL & TMPH (0xD2 [1:0] and 0xD1 [7:0]) registers (see the Temperature Sensor section of this datasheet). Temperature conversion controlled by the TEMP\_Config register.

Figure 27: Temperature Measurement High Register

| Addr: 0xD1 |          | ТМРН    |        |                                                                  |  |

|------------|----------|---------|--------|------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                  |  |

| 7:0        | TMPH     |         | R      | Most significant 8 bits (9:2) of the Temperature<br>Measurement. |  |

# Temperature Measurement Low Register (bits 1:0)

TMP\_VALUE is the value from TMPL & TMPH (0xD2 [1:0] and 0xD1 [7:0]) registers (see the Temperature Sensor section of this datasheet). Temperature conversion controlled by the TEMP\_Config register.

Figure 28: Temperature Measurement Low Register

| Addr: 0xD2 |          | TMPL    |        |                                                                |  |

|------------|----------|---------|--------|----------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                |  |

| 7:0        | TMPL     |         | R      | Least significant 2 bits (1:0) of the Temperature Measurement. |  |

Figure 29: Temperature Configure Register

| Addr: 0xD3 |          | TEMP_Config |                                                                                                        |                                                                                  |  |  |

|------------|----------|-------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| Bit        | Bit Name | Default     | Default Access Bit Description                                                                         |                                                                                  |  |  |

| 7          | ISTAT    | 0           | R/W Will be set to 1 when internal temperature measu is complete. Set to 0 if writing to the register. |                                                                                  |  |  |

| 6          | RESV     | 0           | R/W                                                                                                    | Reserved, set to 0 if writing the register                                       |  |  |

| 5          | START    | 0           | R/W Set to 1 to start a temperature conversion cycle. Se for IDLE state.                               |                                                                                  |  |  |

| 4          | RESV     | 0           | R/W                                                                                                    | Reserved, set to 0 if writing the register                                       |  |  |

| 3:0        | SRC      | 0           | R/W                                                                                                    | Set to 0100 to start a temperature conversion cycle. Set to 0000 for IDLE state. |  |  |

Page 24ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

Figure 30: Bank Register

| Addr: 0xDB |          | BANK    |                                |                                                                                                                                |  |

|------------|----------|---------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Default Access Bit Description |                                                                                                                                |  |

| 7          | BANK     | 0       | R/W                            | Sets Bank mode for sensor channel selection: 0= Mode 0 for X, Y, D and D sensor data 1= Mode 1 for X, Y, Z and NIR sensor data |  |

| 6:0        | RESV     | 0       | R/W                            | Reserved, set to 0000000 if writing the register                                                                               |  |

Figure 31: Sensor Gain and LED\_DRV Current Drive Register

| Addr: 0xB9 |          | GAIN_IDRV      |     |                                                                                                 |  |

|------------|----------|----------------|-----|-------------------------------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default Access |     | Bit Description                                                                                 |  |

| 7:6        | IDRV     | 0              | R/W | For LED_DRV pin current limit (when on). Set to: 'b00=100mA; 'b01=50mA; 'b10=25mA; 'b11=12.5mA; |  |

| 5:2        | RESV     | 0              | R/W | Reserved, set to 0000 if writing the register                                                   |  |

| 1:0        | GAIN     | 0              | R/W | Sensor Channel Gain Setting (all channels)<br>'b00=1x; 'b01=3.7x; 'b10=16x; 'b11=64x;           |  |

Figure 32: **Integration Time Register**

| Addr: 0xD9 |          | INT_T   |        |                                                                          |  |

|------------|----------|---------|--------|--------------------------------------------------------------------------|--|

| Bit        | Bit Name | Default | Access | Bit Description                                                          |  |

| 7:0        | INT_T    | 0xFF    | R/W    | Sets sensor integration time<br>Integration time = (256 - value) * 2.8ms |  |

Page 25 ams Datasheet Document Feedback

Figure 33: Integration Wait Time Register

| Addr: 0xDA |          | INT_WT  |        |                                                                                        |

|------------|----------|---------|--------|----------------------------------------------------------------------------------------|

| Bit        | Bit Name | Default | Access | Bit Description                                                                        |

| 7:0        | INT_WT   | 0xFF    | R/W    | Sets time between sensor integrations<br>Integration wait time = (256 - value) * 2.8ms |

Figure 34: Data Enable Register

| Addr: 0xFA |          | DATA_EN |                                                                      |                                                                    |  |  |

|------------|----------|---------|----------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| Bit        | Bit Name | Default | Default Access Bit Description                                       |                                                                    |  |  |

| 7          | DL       | 0       | R/W                                                                  | Data Latch. Set to 1 to latch the data after acquisition completes |  |  |

| 6:4        | RESV     | 0       | R/W                                                                  | Reserved, set to 000 if writing the register                       |  |  |

| 3          | WAIT     | 0       | R/W Set to 1 to enable the wait timer between data chan acquisitions |                                                                    |  |  |

| 2          | RESV     | 0       | R/W                                                                  | Reserved, set to 0 if writing the register                         |  |  |

| 1          | CON      | 0       | R/W Set to 1 to enable data channel acquisitions                     |                                                                    |  |  |

| 0          | PON      | 0       | R/W Set to 1 if writing the register                                 |                                                                    |  |  |

Page 26ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

Figure 35: Sensor Data Registers

| Addr: 0xDC |            | NDATA_L |        | NDATA_L                  |

|------------|------------|---------|--------|--------------------------|

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | NDATA_L    |         | R      | Channel N Low Data Byte  |

| Ad         | ldr: 0xDD  |         |        | NDATA_H                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | NDATA_H    |         | R      | Channel N High Data Byte |

| Ac         | ldr: 0xDE  |         |        | YDATA_L                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | YDATA_L    |         | R      | Channel Y Low Data Byte  |

| Ac         | ldr: 0xDF  |         |        | YDATA_H                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | YDATA_H    |         | R      | Channel Y High Data Byte |

| Addr: 0xEC |            |         |        | ZDATA_L                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | ZDATA_L    |         | R      | Channel Z Low Data Byte  |

| Ac         | ldr: 0xED  |         |        | ZDATA_H                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | ZDATA_H    |         | R      | Channel Z High Data Byte |

| Ac         | Addr: 0xEE |         |        | XDATA_L                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | XDATA_L    |         | R      | Channel X Low Data Byte  |

| Ac         | Addr: 0xEF |         |        | XDATA_H                  |

| Bit        | Bit Name   | Default | Access | Bit Description          |

| 7:0        | XDATA_H    |         | R      | Channel X High Data Byte |

ams DatasheetPage 27[v1-02] 2017-Feb-27Document Feedback

# **Application Information**

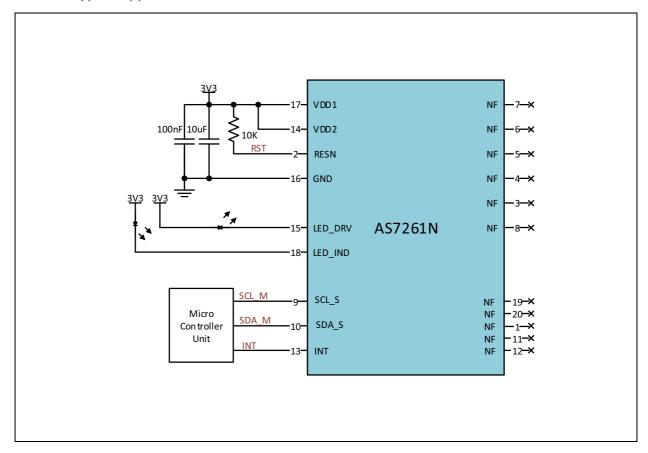

# **Schematic**

Figure 36: AS7261N Typical Application Circuit

Page 28ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

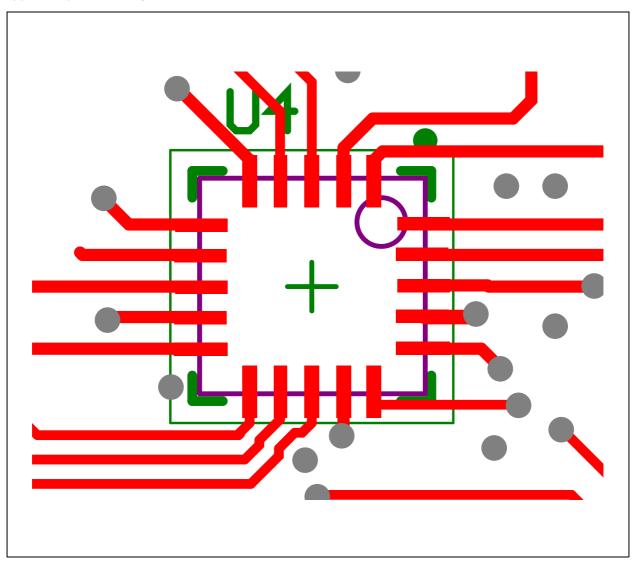

# **PCB Layout**

Figure 37: Typical Layout Routing

In order to prevent interference, avoid trace routing feedthroughs with exposure directly under the AS7261N. An example routing is illustrated in the diagram.

ams Datasheet Page 29

[v1-02] 2017-Feb-27 Document Feedback

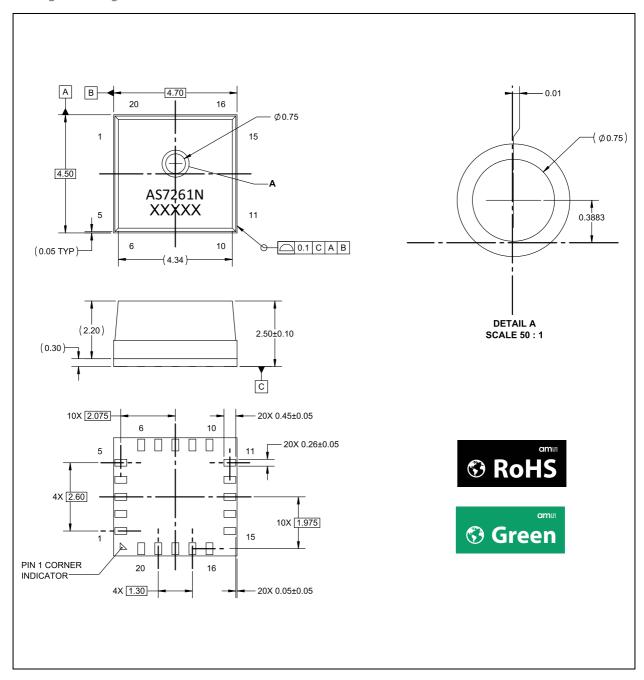

# **Package Drawings & Markings**

Figure 38: **Package Drawing**

#### Note(s):

- 1. All linear dimensions are in millimeters

- 2. XXXXX = tracecode

Page 30 ams Datasheet [v1-02] 2017-Feb-27

# **PCB Pad Layout**

Suggested PCB pad layout guidelines for the LGA device are shown.

Figure 39: Recommended PCB Pad Layout

#### Note(s):

- 1. Unless otherwise specified, all dimensions are in millimeters.

- 2. Dimensional tolerances are  $\pm 0.05$ mm unless otherwise noted.

- 3. This drawing is subject to change without notice.

ams DatasheetPage 31[v1-02] 2017-Feb-27Document Feedback

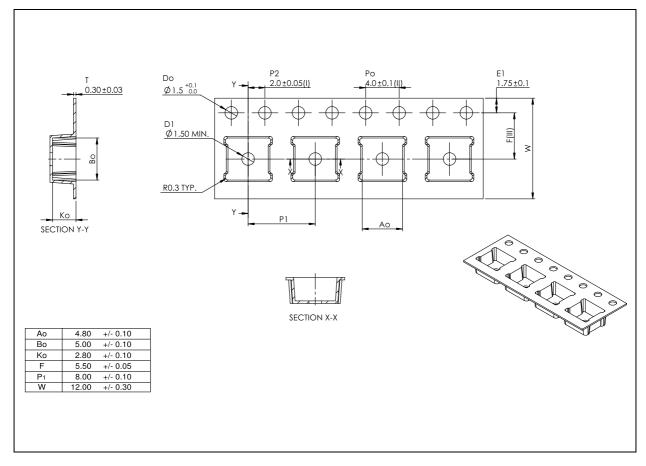

# **Mechanical Data**

Figure 40: Tape & Reel Information

#### Note(s):

- 1. All dimensions in millimeters unless of otherwise stated.

- 2. Measured from centreline of sprocket hole to centreline of pocket.

- 3. Cumulative tolerance of 10 sprocket holes is  $\pm 0.20$ .

- ${\bf 4.}\ Measured\ from\ centreline\ of\ sprocket\ hole\ to\ centreline\ of\ pocket.}$

- 5. Other material available.

Page 32ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

# Soldering & Storage Information

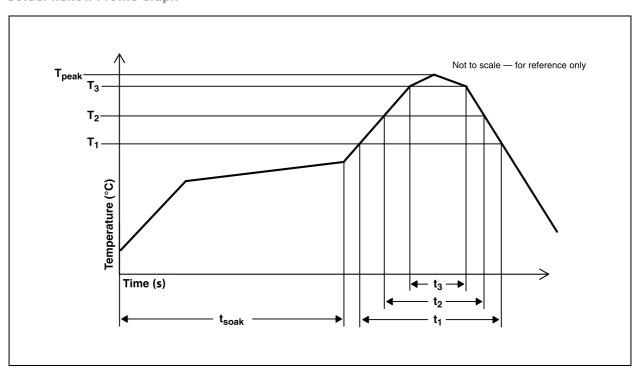

# **Soldering Information**

The module has been tested and has demonstrated an ability to be reflow soldered to a PCB substrate. The solder reflow profile describes the expected maximum heat exposure of components during the solder reflow process of product on a PCB. Temperature is measured on top of component. The components should be limited to a maximum of three passes through this solder reflow profile.

Figure 41: Solder Reflow Profile

| Parameter                                            | Reference         | Device         |

|------------------------------------------------------|-------------------|----------------|

| Average temperature gradient in preheating           |                   | 2.5°C/s        |

| Soak time                                            | t <sub>SOAK</sub> | 2 to 3 minutes |

| Time above 217°C(T <sub>1</sub> )                    | t <sub>1</sub>    | Max 60s        |

| Time above 230°C(T <sub>2</sub> )                    | t <sub>2</sub>    | Max 50s        |

| Time above T <sub>peak</sub> - 10°C(T <sub>3</sub> ) | t <sub>3</sub>    | Max 10s        |

| Peak temperature in reflow                           | T <sub>peak</sub> | 260°C          |

| Temperature gradient in cooling                      |                   | Max -5°C/s     |

Figure 42: Solder Reflow Profile Graph

ams Datasheet Page 33

[v1-02] 2017-Feb-27 Document Feedback

# **Manufacturing Process Considerations**

The AS7261N package is compatible with standard reflow no-clean and cleaning processes including aqueous, solvent or ultrasonic techniques. However, as an open-aperture device, precautions must be taken to avoid particulate or solvent contamination as a result of any manufacturing processes, including pick and place, reflow, cleaning, integration assembly and/or testing. Temporary covering of the aperture is allowed. To avoid degradation of accuracy or performance in the end product, care should be taken that any temporary covering and associated sealants/debris are thoroughly removed prior to any optical testing or final packaging.

# **Storage Information**

# **Moisture Sensitivity**

Optical characteristics of the device can be adversely affected during the soldering process by the release and vaporization of moisture that has been previously absorbed into the package. To ensure the package contains the smallest amount of absorbed moisture possible, each device is baked prior to being dry packed for shipping.

Devices are dry packed in a sealed aluminized envelope called a moisture-barrier bag with silica gel to protect them from ambient moisture during shipping, handling, and storage before use.

#### **Shelf Life**

The calculated shelf life of the device in an unopened moisture barrier bag is 12 months from the date code on the bag when stored under the following conditions:

· Shelf Life: 12 months

Ambient Temperature: <40°C</li>

• Relative Humidity: <90%

Rebaking of the devices will be required if the devices exceed the 12 month shelf life or the Humidity Indicator Card shows that the devices were exposed to conditions beyond the allowable moisture region.

Page 34

Document Feedback

[v1-02] 2017-Feb-27

#### Floor Life

The module has been assigned a moisture sensitivity level of MSL 3. As a result, the floor life of devices removed from the moisture barrier bag is 168 hours from the time the bag was opened, provided that the devices are stored under the following conditions:

• Floor Life: 168 hours

• Ambient Temperature: <30°C

• Relative Humidity: <60%

If the floor life or the temperature/humidity conditions have been exceeded, the devices must be rebaked prior to solder reflow or dry packing.

# **Rebaking Instructions**

When the shelf life or floor life limits have been exceeded, rebake at 50°C for 12 hours.

ams Datasheet Page 35

[v1-02] 2017-Feb-27 Document Feedback

# **Ordering & Contact Information**

Figure 43: Ordering Information

| Ordering<br>Code | Package    | Marking | Description                                   | Delivery<br>Form | Delivery<br>Quantity |

|------------------|------------|---------|-----------------------------------------------|------------------|----------------------|

| AS7261N-BLGT     | 20-pin LGA | AS7261N | XYZ and NIR Sensor with<br>Electronic Shutter | Tape & Reel      | 2000 pcs/reel        |

Buy our products or get free samples online at:

www.ams.com/ICdirect

Technical Support is available at:

www.ams.com/Technical-Support

Provide feedback about this document at:

www.ams.com/Document-Feedback

For further information and requests, e-mail us at:

ams\_sales@ams.com

$For \ sales \ of fices, \ distributors \ and \ representatives, \ please \ visit:$

www.ams.com/contact

# Headquarters

ams AG Tobelbader Strasse 30 8141 Premstaetten Austria, Europe

Tel: +43 (0) 3136 500 0 Website: www.ams.com

Page 36

Document Feedback

[v1-02] 2017-Feb-27

# **RoHS Compliant & ams Green** Statement

**RoHS:** The term RoHS compliant means that ams AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

ams Green (RoHS compliant and no Sb/Br): ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams AG knowledge and belief as of the date that it is provided. ams AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams AG and ams AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

ams Datasheet Page 37 **Document Feedback**

# **Copyrights & Disclaimer**

Copyright ams AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. This product is provided by ams AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

Page 38

Document Feedback

[v1-02] 2017-Feb-27

# **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                         |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                           |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the design, validation or qualification phase of development. The performance and parameters shown in this document are preliminary without any warranty and are subject to change without notice            |

| Datasheet                | Production      | Information in this datasheet is based on products in ramp-up to full production or full production which conform to specifications in accordance with the terms of ams AG standard warranty as given in the General Terms of Trade                                |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which conform to specifications in accordance with the terms of ams AG standard warranty as given in the General Terms of Trade, but these products have been superseded and should not be used for new designs |

Page 39 ams Datasheet **Document Feedback**

# **Revision Information**

| Changes from 1-01 (2017-Feb-08) to current revision 1-02 (2017-Feb-27) | Page |

|------------------------------------------------------------------------|------|

| Updated Figure 10                                                      | 9    |

#### Note(s):

- 1. Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

- $2. \, Correction \, of \, typographical \, errors \, is \, not \, explicitly \, mentioned.$

Page 40ams DatasheetDocument Feedback[v1-02] 2017-Feb-27

#### **Content Guide**

#### 1 General Description

- 1 Key Benefits & Features

- 2 Application

- 2 System Block Diagram

#### 3 Pin Assignments

- 3 Pin Description

- 5 Absolute Maximum Ratings

- **6 Electrical Characteristics**

- 8 Timing Characteristics

- 9 Operation Characteristics

# 11 Detailed Descriptions

- 11 XYZ Chromatic White Color Sensor

- 12 Data Conversion

- 13 Spectral Conversion and Data Acquisition

- 14 Temperature Sensor

- 14 Electronic Shutter with LED\_IND or LED\_DRV Driver Control

- 15 Low Power Mode

- 15 Device Initialization and Pin Assignment

- 15 RC Oscillator

- 15 Reset

- 18 I<sup>2</sup>C Slave Interface

- 18 I<sup>2</sup>C Feature List

- 18 I<sup>2</sup>C Register Set

- 20 Detailed Register Description

- 22 Temperature Measurement High Register (bits 9:2)

- 22 Temperature Measurement Low Register (bits 1:0)

## 27 Application Information

- 27 Schematic

- 27 PCB Layout

- 28 Package Drawings & Markings

- 29 PCB Pad Layout

- 30 Mechanical Data

## 31 Soldering & Storage Information

- 31 Soldering Information

- 32 Manufacturing Process Considerations

- 32 Storage Information

- 32 Moisture Sensitivity

- 32 Shelf Life

- 32 Floor Life

- 33 Rebaking Instructions

## 34 Ordering & Contact Information

ams Datasheet Page 41

[v1-02] 2017-Feb-27 Document Feedback

- 35 RoHS Compliant & ams Green Statement

- 36 Copyrights & Disclaimer

- 37 Document Status

- 38 Revision Information

Page 42ams DatasheetDocument Feedback[v1-02] 2017-Feb-27