#### **MAX5712**

## **General Description**

The MAX5712 is a small footprint, low-power, 12-bit digital-to-analog converter (DAC) that operates from a single +2.7V to +5.5V supply. The MAX5712 on-chip precision output amplifier provides rail-to-rail output swing. Drawing only  $85\mu A$  supply current at +3V, the MAX5712 is ideally suited for portable battery-operated equipment.

The MAX5712 utilizes a 3-wire serial-interface that is compatible with SPI/QSPI™/MICROWIRE® and DSP-interface standards. All logic inputs are CMOS-logic compatible and buffered with Schmitt triggers to allow direct interfacing to optocouplers. The MAX5712 incorporates a power-on reset (POR) circuit that ensures the DAC begins in a zero-volt-state upon power-up. A power-down mode that reduces current consumption to 0.3μA may be initiated through a software command.

The MAX5712 is available in a small 6-pin SOT23 package. For dual and quad 12-bit versions, see the MAX5722 and MAX5742 data sheets. For single, dual, and quad 10-bit versions, see the MAX5711, MAX5721 and MAX5741 data sheets. The MAX5712 is specified over the automotive temperature range of -40°C to +125°C.

## **Applications**

- Automatic Tuning

- · Gain and Offset Adjustment

- Power Amplifier Control

- Process Control I/O Boards

- Battery-Powered Equipment

- VCO Control

QSPI is a trademark of Motorola, Inc.

MICROWIRE is a registered trademark of National Semiconductor, Corp.

## **Functional Diagram**

#### $V_{\text{DD}}$ GND MAX5712 RFF+ RFF DAC OUTPUT 12-RIT OUT REGISTER **BUFFER** DAC 100kΩ INPUT POWER-DOWN CONTROL CONTROL LOGIC LOGIC POWER-ON RESET CS SCLK

## Low-Power, 12-Bit, Rail to Rail Voltage-Output Serial DAC in SOT23

#### **Features**

- Wide -40°C to +125°C Operating Temperature Range

- Low 85µA Supply Current

- Ultra Low 0.3µA Power-Down Supply Current

- Single +2.7V to +5.5V Supply Voltage

- Fast 20MHz 3-Wire SPI/QSPI/MICROWIRE and DSP-Compatible Serial Interface

- Schmitt-Triggered Inputs for Direct Interfacing to Optocouplers

- Rail-to-Rail Output Buffer

- Tiny 6-Pin SOT23 Package

- Power-On Reset to 0V

- Three Software-Selectable Power-Down Output Impedances (100kΩ, 1kΩ, Hi-Z)

## **Ordering Information**

| PART        | TEMP RANGE        | PIN-<br>PACKAGE | TOP<br>MARK |

|-------------|-------------------|-----------------|-------------|

| MAX5712EUT+ | T -40°C to +85°C  | 6 SOT23         | ABCQ/ACST   |

| MAX5712AUT+ | T -40°C to +125°C | 6 SOT23         | AAUD/ACST   |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<u>Pin Configuration</u> appears at end of data sheet.

## Low-Power, 12-Bit, Rail to Rail Voltage-Output Serial DAC in SOT23

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +6V                                    | Operating Temperature Range40°C to +125°C |

|----------------------------------------------------------------------|-------------------------------------------|

| OUT, SCLK, DIN, <del>CS</del> to GND0.3V to (V <sub>DD</sub> + 0.3V) | Maximum Junction Temperature+150°C        |

| Maximum Current into Any Pin±50mA                                    | Storage Temperature Range65°C to +150°C   |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                | Lead Temperature (soldering, 10s)+300°C   |

| 6-Pin SOT23 (derate 9.1mW/°C above +70°C)727mW                       | Soldering Temperature (reflow)+260°C      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

SOT23

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )...134.40°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......39°C/W

#### **Electrical Characteristics**

$(V_{DD}$  = +2.7V to +5.5V, GND = 0,  $R_L$  = 5k $\Omega$ ,  $C_L$  = 200pF,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD}$  = +5V.  $T_A$  = +25°C)

| PARAMETER                       | SYMBOL          | CONDITIONS                                            | MIN                   | TYP  | MAX                   | UNITS   |

|---------------------------------|-----------------|-------------------------------------------------------|-----------------------|------|-----------------------|---------|

| STATIC ACCURACY (NOTE 1         | )               |                                                       |                       |      |                       |         |

| Resolution                      | N               |                                                       | 12                    |      |                       | Bits    |

| Differential Nonlinearity Error | DNL             | Guaranteed monotonic (Note 2)                         |                       |      | ±1                    | LSB     |

| Integral Nonlinearity Error     | INL             | (Note 2)                                              |                       | ±2   | ±16                   | LSB     |

| Zero-Code Error                 | OE              | Code = 000                                            |                       | 0.4  | 1.5                   | % of FS |

| Zero-Code Error Tempco          |                 |                                                       |                       | 2.3  |                       | ppm/°C  |

| Gain Error                      | GE              | Code = FFF hex                                        |                       |      | -3                    | % of FS |

| Gain-Error Tempco               |                 | Integral                                              |                       | 0.26 |                       | ppm/°C  |

| DAC OUTPUT                      |                 |                                                       |                       |      |                       |         |

| Output Voltage Range            |                 | No-load (Note 3)                                      | 0                     |      | $V_{DD}$              | V       |

| DC Output Impedance             |                 | Code = 800 hex                                        |                       | 0.8  |                       | Ω       |

| Short Circuit Current           |                 | V <sub>DD</sub> = +3V                                 |                       | 15   |                       | mA      |

| Short Circuit Current           |                 | V <sub>DD</sub> = +5V                                 |                       | 48   |                       | IIIA    |

| Weke Un Time                    |                 | V <sub>DD</sub> = +3V                                 |                       | 8    |                       |         |

| Wake-Up Time                    |                 | V <sub>DD</sub> = +5V                                 |                       | 8    |                       | μs      |

| Output Leakage Current          |                 | Power-down mode = output high-impedance               |                       | ±18  | ±33                   | nA      |

| DIGITAL INPUTS (SCLK, DIN,      | CS)             |                                                       |                       |      |                       |         |

| Input High Voltage              | V <sub>IH</sub> | V <sub>DD</sub> = +3V, +5V                            | 0.7 x V <sub>DD</sub> |      |                       | V       |

| Input Low Voltage               | V <sub>IL</sub> | V <sub>DD</sub> = +3V, +5V                            |                       |      | 0.3 x V <sub>DD</sub> | V       |

| Input Leakage Current           | I <sub>IN</sub> | Digital Inputs = 0 or V <sub>DD</sub>                 |                       | ±0.1 | ±1                    | μA      |

| Input Capacitance               | C <sub>IN</sub> |                                                       |                       | 5    |                       | pF      |

| DYNAMIC PERFORMANCE             |                 |                                                       |                       |      |                       |         |

| Voltage-Output Slew Rate        | SR              |                                                       |                       | 0.5  |                       | V/µs    |

| Voltage-Output Settling Time    |                 | 400 hex to C00 hex (Note 4)                           |                       | 4    | 10                    | μs      |

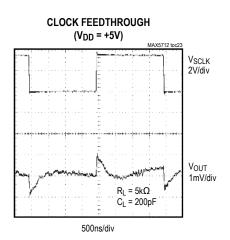

| Digital Feedthrough             |                 | Any digital inputs from 0 to V <sub>DD</sub>          |                       | 0.2  |                       | nV-s    |

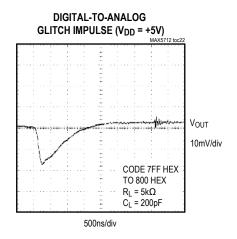

| Digital-Analog Glitch Impulse   |                 | Major carry transition (code 7FF hex to code 800 hex) |                       | 12   |                       | nV-s    |

#### **Electrical Characteristics (continued)**

$(V_{DD}$  = +2.7V to +5.5V, GND = 0,  $R_L$  = 5k $\Omega$ ,  $C_L$  = 200pF,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD}$  = +5V.  $T_A$  = +25°C)

| PARAMETER                              | SYMBOL            | CONDITIONS                                                           | MIN | TYP  | MAX | UNITS |

|----------------------------------------|-------------------|----------------------------------------------------------------------|-----|------|-----|-------|

| POWER REQUIREMENTS                     | •                 |                                                                      | •   |      |     |       |

| Supply Voltage Range                   | V <sub>DD</sub>   |                                                                      | 2.7 |      | 5.5 | V     |

| Cumply Cumpent with No Load            |                   | All digital inputs at 0 or V <sub>DD</sub> , V <sub>DD</sub> = +3.6V |     | 85   | 150 |       |

| Supply Current with No-Load            | I <sub>DD</sub>   | All digital inputs at 0 or V <sub>DD</sub> , V <sub>DD</sub> = +5.5V |     | 105  | 187 | μA    |

| Power-Down Supply Current              | I <sub>DDPD</sub> | All digital inputs at 0 or V <sub>DD</sub> , V <sub>DD</sub> = +5.5V |     | 0.29 | 1   | μA    |

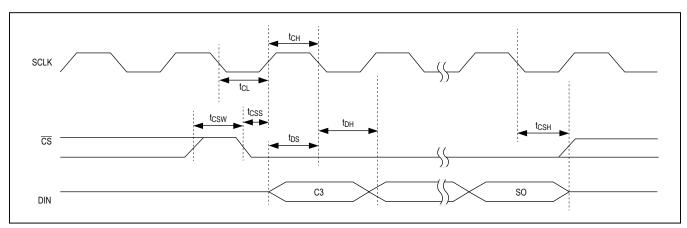

| TIMING CHARACTERISTICS                 | FIGURE 1) (       | TIMING IS TESTED WITH NO-LOAD)                                       |     |      |     |       |

| SCLK Clock Frequency                   | fsclk             |                                                                      | 0   |      | 20  | MHz   |

| SCLK Pulse Width High                  | t <sub>CH</sub>   |                                                                      | 20  |      |     | ns    |

| SCLK Pulse Width Low                   | t <sub>CL</sub>   |                                                                      | 20  |      |     | ns    |

| CS Fall-to-SLCK Rise Setup             | t <sub>CSS</sub>  |                                                                      | 15  |      |     | ns    |

| DIN Setup Time                         | t <sub>DS</sub>   |                                                                      | 15  |      |     | ns    |

| DIN Hold Time                          | t <sub>DH</sub>   |                                                                      | 0   |      |     | ns    |

| SCLK Falling Edge-to-CS<br>Rising Edge | tcsH              |                                                                      | 10  |      |     | ns    |

| CS Pulse Width High                    | t <sub>CSW</sub>  |                                                                      | 80  |      |     | ns    |

Note 1: DC Specifications are tested without output loads.

Note 2: Linearity guaranteed from code 115 to code 3981.

Note 3: Offset and gain error limit the FSR.

Note 4: Guaranteed by design.

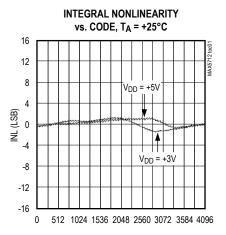

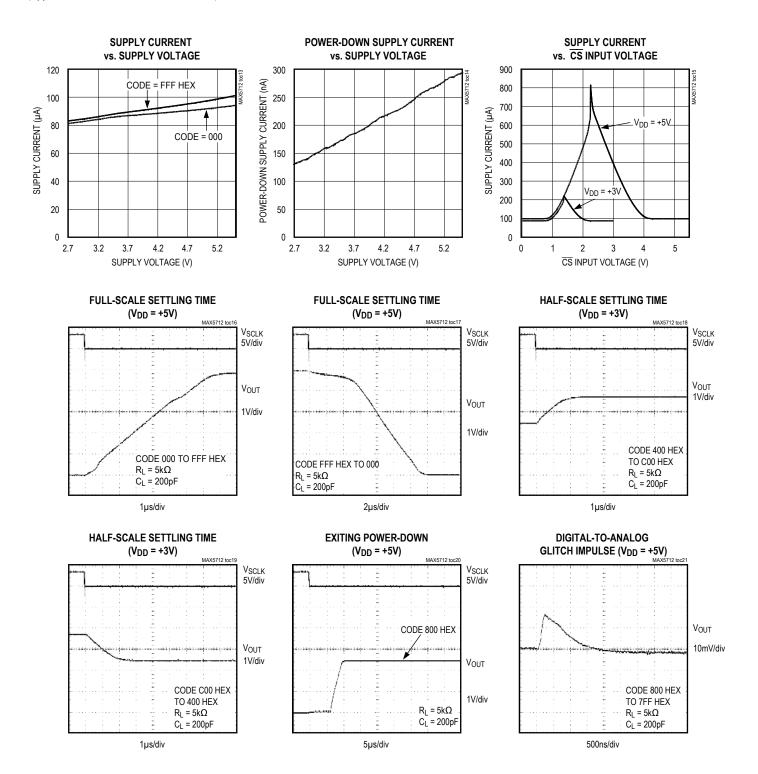

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

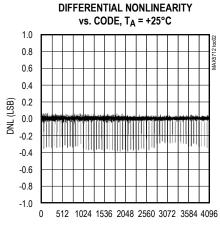

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

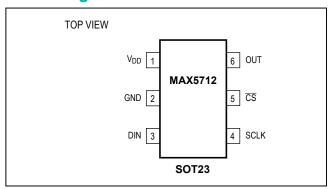

## **Pin Description**

| PIN | NAME          | FUNCTION                     |

|-----|---------------|------------------------------|

| 1   | $V_{DD}$      | Power-Supply Input           |

| 2   | GND           | Ground                       |

| 3   | DIN           | Serial-Data Input            |

| 4   | SCLK          | Serial-Clock Input           |

| 5   | <del>CS</del> | Active Low Chip-Select Input |

| 6   | OUT           | DAC Output Voltage           |

## Low-Power, 12-Bit, Rail to Rail Voltage-Output Serial DAC in SOT23

#### **Detailed Description**

The MAX5712 voltage output, 12-bit DAC, offers a full 12-bit performance in a small 6-pin SOT23 package. The SOT23 footprint is less than 9mm². The MAX5712 has less than 1LSB differential nonlinearity error, ensuring monotonic performance. The device uses a simple 3-wire, SPI/QSPI/MICROWIRE and DSP-compatible serial interface that operates up to 20MHz. The MAX5712 incorporates three shutdown modes, making it ideal for low-power.

#### **Analog Section**

The MAX5712 consists of a resistor string, an output buffer, and a POR circuit. Monotonic digital to analog conversion is achieved using a resistor string architecture. Since  $V_{DD}$  is the reference for the MAX5712, the accuracy of the DAC depends on the accuracy of  $V_{DD}$ . The low bias current of the MAX5712 allows its power to be supplied by a voltage reference such as the MAX6030. The 12-bit DAC code is binary-unipolar with 1LSB =  $V_{DD}/4096$ .

#### **Output Buffer**

The DAC output buffer has a rail-to-rail output and is capable of driving a  $5k\Omega$  resistive load in parallel with a 200pF capacitive load. With a capacitive load of 200pF, the output buffer slews  $0.5V/\mu s$ . With a 1/4FS to 3/4FS output transition, the amplifier output settles to 1/2LSB in less than  $10\mu s$  when loaded with  $5k\Omega$  in parallel with 200pF. The buffer amplifier is stable with any combination of resistive loads greater than  $5k\Omega$  and capacitive loads less than 200pF.

Program the input register bits to power-down the device. The DAC registers are preserved during power-down

and upon wake-up, the DAC output is restored to its prepower-down voltage.

#### **Power-On Reset**

The MAX5712 has a POR circuit to set the DACs output to zero when  $V_{DD}$  is first applied. This ensures that unwanted DAC output voltages will not occur immediately following a system start-up, such as after a loss of power. Upon initial power-up, an internal power-on-reset circuit ensures that all DAC registers are cleared, the DAC is powered-down, and its output is terminated to GND by a  $100k\Omega$  resistor. An  $8\mu s$  recovery time after issuing a wake-up command is needed before writing to the DAC registers.

## **Digital Section**

#### 3-Wire Serial Interface

The MAX5712 digital interface is a standard 3-wire connection compatible with SPI/QSPI/MICROWIRE/DSP interfaces. The chip-select input (CS) frames the serial data loading at DIN. Immediately following CS high-to-low transition, the data is shifted synchronously and latched into the input register on the falling edge of the serial clock input (SCLK). After 16 bits have been loaded into the serial input register, it transfers its contents to the DAC latch. CS may then either be held low or brought high. CS must be brought high for a minimum of 80ns before the next write sequence, since a write sequence is initiated on a falling edge of  $\overline{CS}$ . Not keeping  $\overline{CS}$  low during the first 15 SCLK cycles discards input data. The serial clock (SCLK) can idle either high or low between transitions. Figure 1 shows the complete 3-wire serial interface transmission. Table 1 lists serial-interface mapping.

Figure 1. Timing Diagram

|     |    |    |    |     |     | 16-B | IT SEI | RIAL | WOR   | D     |      |     |     |     |     |                    |                                                   |

|-----|----|----|----|-----|-----|------|--------|------|-------|-------|------|-----|-----|-----|-----|--------------------|---------------------------------------------------|

| MSB |    |    |    |     |     |      |        |      |       |       |      |     |     |     | LSB | MODE               | OUTPUT                                            |

| СЗ  | C2 | C1 | C0 | D11 | D10 | D09  | D08    | D07  | D06   | D05   | D04  | D03 | D02 | D01 | D00 |                    |                                                   |

| 0   | 0  | 0  | 0  |     |     |      |        | 1    | 2-Bit | DAC ( | Code |     |     |     |     | Set and update DAC | V <sub>OUT</sub> = V <sub>DD</sub> x<br>CODE/4096 |

| 1   | 1  | 1  | 1  | х   | Х   | Х    | Х      | Х    | Х     | Х     | Х    | Х   | Х   | 0   | 0   | Wake-Up            | Current DAC setting (initially 0)                 |

| 1   | 1  | 1  | 1  | Х   | Х   | Х    | Х      | Х    | Х     | Х     | Х    | Х   | Х   | 0   | 1   | Power-Down         | Floating                                          |

| 1   | 1  | 1  | 1  | Х   | Х   | Х    | Х      | Х    | Х     | Х     | Х    | Х   | Х   | 1   | 0   | Power-Down         | 1kΩ to GND                                        |

| 1   | 1  | 1  | 1  | Х   | Х   | Х    | Х      | Х    | Х     | Х     | Х    | Х   | Х   | 1   | 1   | Power-Down         | 100kΩ to GND                                      |

**Table 1. Serial Interface Mapping**

#### **Shutdown Modes**

The MAX5712 includes three software-controlled shutdown modes that reduce the supply current to below 1 $\mu$ A. In two of the three shutdown modes, OUT is connected to GND through a resistor. Table 1 lists the three shutdown modes of operation.

## **Applications Information**

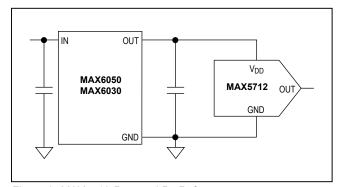

## Device Powered by an External Reference

The MAX5712 generates an output voltage proportional to  $V_{DD}$ , coupling power supply noise to the output. The circuit in <u>Figure 2</u> rejects this power-supply noise by powering the device directly with a precision voltage reference, improving overall system accuracy. The MAX6030 (+3V, 75ppm) or the MAX6050 (+5V, 75ppm) precision voltage references are ideal choices due to the low-power requirements of the MAX5712. This solution is also useful when the required full-scale output voltage is less than the available supply voltages.

Figure 2. MAX5712 Powered By Reference

#### **Digital Inputs and Interface Logic**

The 3-wire digital interface for the MAX5712 is compatible with SPI, QSPI, MICROWIRE, and DSP. The three digital inputs ( $\overline{CS}$ , DIN, and SCLK) load the digital input serially into the DAC. All of the digital inputs include Schmitt-trigger buffers to accept slow-transition interfaces. This allows optocouplers to interface directly to the MAX5712 without additional external logic. The digital inputs are compatible with CMOS-logic levels.

#### **Power-Supply Bypassing and Layout**

Careful PC board layout is important for optimal system performance. Keep analog and digital signals separate to reduce noise injection and digital feedthrough. Use a ground plane to ensure that the ground return from GND to the supply ground is short and low impedance. Bypass  $V_{DD}$  with a  $0.1\mu F$  capacitor to ground as close as possible to the device.

## **Pin Configuration**

## **Chip Information**

PROCESS: BICMOS

# Low-Power, 12-Bit, Rail to Rail Voltage-Output Serial DAC in SOT23

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO. | LAND PATTERN NO. |

|--------------|--------------|-------------|------------------|

| 6 SOT23      | U6F-6        | 21-0058     | 90-0175          |

## MAX5712

## Low-Power, 12-Bit, Rail to Rail Voltage-Output Serial DAC in SOT23

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                  | PAGES<br>CHANGED |

|--------------------|---------------|----------------------------------------------|------------------|

| 0                  | 8/01          | Initial release                              | _                |

| 1                  | 10/01         | Updated Electrical Characteristics           | 2                |

| 2                  | 11/04         | Updated Package Information                  | 9                |

| 3                  | 8/13          | Updated Ordering Information                 | 1                |

| 4                  | 9/16          | Added top mark to Ordering Information table | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.