## **Product Data Sheet**

3M<sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+FDR Applications

## **REVISION HISTORY**

| 27/01/2014 |

|------------|

|            |

|            |

|            |

|            |

|            |

|            |

|            |

|            |

**3M Electronic Solutions Division**

6801 River Place Blvd. Austin, TX 78726-9000 http://www.3Mconnectors.com

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 1 of 15                |

#### Description

The 3M Active Optical Cable (AOC) Assembly for QSFP+ FDR (fourteen data rate) Applications extends the performance and benefits of its light engine technology to 14 Gbps per channel. This AOC provides an aggregate throughput of 56 Gbps in each direction over 100 meters of multimode fiber for applications in the new generation of 14 Gbps InfiniBand<sup>TM</sup> switches and servers. Using industry leading VCSEL technology and an advanced light-engine design, the 3M AOC assembly provides exceptional cost/performance value.

#### **Features**

- Low power

- Four channels each operating up to 14.0625 Gbps

- Fiber link up to 100m

- Reliable 850nm VCSEL technology

- 0 to +70 degree Celsius operating temperature range

- Hot pluggable

- Bend-insensitive fiber

- Includes digital diagnostic features

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 2 of 15                |

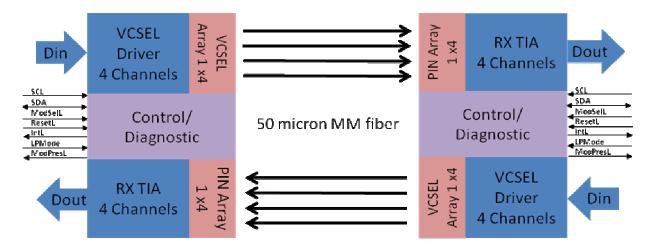

### **AOC** block diagram

**Absolute Maximum Rating**

| Parameters                 | Min  | Тур | Max  | Units           |

|----------------------------|------|-----|------|-----------------|

| Storage temperature        | -20  |     | +70  | Deg.<br>Celsius |

|                            |      |     |      | Celsius         |

| Relative humidity          | 5    |     | 85   | %               |

| Supply voltage             | 3.10 |     | 3.65 | V               |

| Operating case temperature | 0    |     | +70  | Deg.            |

| _                          |      |     |      | Deg.<br>Celsius |

Note: if product is exposed to conditions beyond the levels indicated, the reliability of the product is likely to be negatively affected.

**Recommended Operating Conditions**

| Parameter                             | Min   | Тур | Max     | Units   |

|---------------------------------------|-------|-----|---------|---------|

| Supply voltage, Vcc                   | 3.135 | 3.3 | 3.465   | V       |

| Power dissipation                     |       | 600 |         | mW      |

| Operating case temperature            | 0     |     | +70     | Degree  |

|                                       |       |     |         | Celsius |

| Signal Rate per channel               | 2.5   |     | 14.0625 | Gbps    |

| Transmitter differential input        | 120   |     | 1200    | mVpp    |

| voltage                               |       |     |         |         |

| Receiver differential output voltage, |       | 422 |         | mV      |

| peak-to-peak                          |       |     |         |         |

| Receiver differential output          |       | 100 |         | Ohms    |

| Impedance                             |       |     |         |         |

| Signaling rate/channel, NRZ           |       |     | 14.0625 | Gbps    |

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 3 of 15                |

**Transmitter Electrical Input Characteristics**

| Parameters                              | Min  | Тур | Max    | Units        |

|-----------------------------------------|------|-----|--------|--------------|

| Single-ended output voltage             | -0.3 |     | 4.0    | V            |

| Transmitter differential input voltage, | 120  |     | 1200   | mVpp         |

| peak-to-peak                            | 120  |     | 1200   | ширр         |

| J2 Jitter tolerance                     |      |     | 0.19   | UI           |

| J9 Jitter tolerance                     |      |     | 0.34   | UI           |

| Data Dependent Pulse Width Shrinkage    |      |     | 0.11   | UI           |

| SDD11 Differential input return loss    |      |     | see    | dB           |

|                                         |      |     | note 1 | ub           |

| SCC11 Common mode input return loss     |      |     | -2     | dB (see note |

|                                         |      |     | -2     | 2)           |

| SDC11 Common mode to differential       |      |     | see    | dB           |

| reflection                              |      |     | note 3 | ub           |

#### **Notes:**

1. SDD11 differential input return loss is defined at TP5a as:  $\leq$

$\{-12+1.71 \text{ SQRT}(f), 0.05 \le f \le 5.6;$

-6.7+13log(f/7),  $5.6 \le f < 14.1$ }, freq in GHz

- 2. SCC11 is measured at TP5a from 200MHz to 14.1 GHz

- 3. SDC11 is defined as  $\leq$  { -16+(2/3)f, measured at TP5a from 50MHz to 14.1 GHz} (TP5a is defined in the Infiniband Architecture specification)

**Receiver Electrical Output Characteristics**

| Parameters                          | Min                          | Тур | Max             | Units           |

|-------------------------------------|------------------------------|-----|-----------------|-----------------|

| Single-ended output voltage         | -0.3                         |     | 4.0             | V               |

| Receiver differential output        |                              | 100 |                 | Ohms            |

| impedance                           |                              | 100 |                 | Offilis         |

| J2 Jitter <sup>5</sup>              |                              |     | 0.44            | UI              |

| J9 Jitter <sup>5</sup>              |                              |     | 0.69            | UI              |

| Output transition time (20% to 80%) | 17                           |     |                 | ps              |

| SDD22 Differential output return    |                              |     | see             |                 |

| loss                                |                              |     | note 1          |                 |

| SCC22 Common mode output            |                              |     | -2              | dB (see note 2. |

| return loss                         |                              |     | -2              | ub (see note 2. |

| SDC22 Common mode to                |                              |     | see             | dB              |

| differential reflection             |                              |     | note 3          | ub              |

| Link bit error rate (BER)           | <10E-12                      |     | Bit             |                 |

| Eye mask parameter, time X          | 0.30                         |     | TIT             |                 |

| Differential output Voltage, Y1, Y2 | 100, 350 ( default setting = |     | UI (assertat)   |                 |

| _                                   | IBTA range 1)                |     | mV (see note 4) |                 |

#### **Notes:**

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 4 of 15                |

1. SDD22 differential output return loss is defined at TP7a as: ≤

$\{-12+1.71 \text{ SQRT}(f), 0.05 < f < 5.6;$

$-6.7+13\log(f/7)$ , 5.6 < f < 14.1}, freq in GHz

- 2. SCC22 measured at TP7a from 200MHz to 14.1 GHz

- 3. SDC22 is defined as:  $< \{-16+(2/3)f$ , measured at TP7a from 50MHz to 14.1 GHz $\}$

- 4. Eye mask Y1,Y2 = 50,225 (IBTA range 0 is supported)

- 5. J2 and J9 Jitter are tested under condition with maximum 2 nearest aggressors.

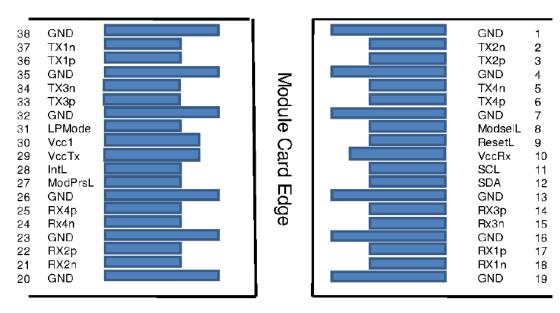

#### QSFP+ Pad layout

Top Side Viewed From Top Bottom Side Viewed From Bottom

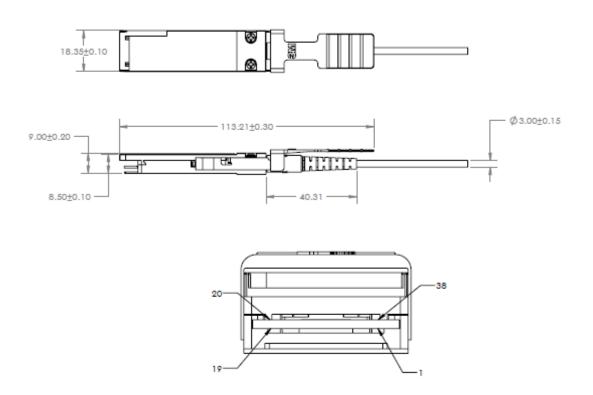

#### **Mechanical Characteristics**

| Parameters                     | Min  | Тур | Max  | Units |

|--------------------------------|------|-----|------|-------|

| Cable Installation Tension     |      |     | 90   | N     |

| Cable Operating Tension        |      |     | 31   | N     |

| Operating Cable Bend Radius    | 3    |     |      | cm    |

| Installation Cable Bend Radius | 6    |     |      | cm    |

| Cable Outer Diameter           | 2.85 | 3.0 | 3.15 | mm    |

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 5 of 15                |

#### **Link Performance**

The 3M Active Optical Cable (AOC) Assembly for QSFP+ FDR Applications uses advance OM2+ multimode fiber with overfilled modal bandwidth of >700MHz.Km and effective modal bandwidth of >950MHz.km at wavelength of 850nm. This allows excellent link performance up to 100 meter for InfiniBand<sup>TM</sup> FDR applications.

#### **Standards and Regulatory Compliance**

- Designed to meet SFF-8436 specification, Rev 4.2, March 21, 2012

- Supports Infiniband Architecture Specification Volume 2, Release 1.3 (November 6, 2012)

- Restriction on Hazardous Substances (RoHS) per EU requirements (ROHS directive )\*

- Class 1M Eye safe per IEC 60825-1/CDRH

- UL 94 –V0 rating

- FCC Class B and CE Emissions and Immunity requirements

- EN61000-4-2 (15KV air discharge during operation, and 8KV direct contact discharges to the case), Human Body Model per JEDEC JESD22-A114-B

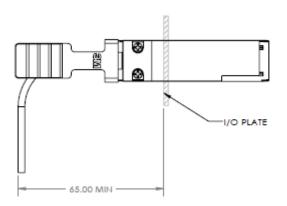

#### **Mechanical dimensions**

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 6 of 15                |

#### Laser safety warning

# INVISIBLE LASER RADIATION CLASS 1M LASER PRODUCT.

DO NOT VIEW THE END OF OPTICAL FIBER WITH OPTICAL INSTRUMENTS AS THIS MAY RESULT IN HAZARDOUS RADIATION EXPOSURE (i.e. FIBER OPTIC VIEWERS, HAND-HELD MAGNIFIERS OR BINOCULARS OR OTHER DIRECT IMAGING DEVICES).

| Document Number: 78-5102-0201-9 A                                                             | Issue Date: January 27, 2014 |

|-----------------------------------------------------------------------------------------------|------------------------------|

| Title: Product Data Sheet                                                                     | Supersedes:                  |

| Subject: 3M <sup>TM</sup> Active Optical Cable (AOC) Assemblies for QSFP+<br>FDR Applications | Page: 7 of 15                |

**QSFP** + Memory Map

| RO   Device type   identifier   Yes   identifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1 RO Revision compliance 2 RO Status  Status  Yes Bit 1 copies INTL lin Bit 0 is zero when mercady 3 RO Loss of signal  Bits 3-0 (receive LOS implemented, bit is sereceive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault  Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared  These bits are cleared  Yes. Bits 7 to 4 are see appropriate when merceive is approp | Default Value       |

| 1 RO Revision compliance 2 RO Status  1 RO Revision yes Bit 1 copies INTL lin  Bit 0 is zero when me ready 3 RO Loss of signal  Bits 3-0 (receive LOS implemented, bit is sereceive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault  Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared on read.  These bits are cleared on read.  These bits are cleared on read.  These bits are cleared yes. Bits 7 to 4 are see appropriate when me temperature goes ab below the thresholds the start of register per lintle output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |

| identifier  1 RO Revision compliance  2 RO Status  Yes Bit 1 copies INTL lin  Bit 0 is zero when meready  3 RO Loss of signal  Bits 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is serecive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault  Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared  These bits are cleare | Hex 0d              |

| compliance  2 RO Status  Yes Bit 1 copies INTL lin  Bit 0 is zero when me ready  3 RO Loss of signal  Bits 3-0 (receive LOS implemented, bit is serecive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault  Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared  These bits are cleared  Yes. Bits 7 to 4 are see and not masked  These bits are cleared  These bits are cleared  Yes. Bits 7 to 4 are see and not masked  These bits are cleared  Yes. Bits 7 to 4 are see and not masked  These bits are cleared  Yes. Bits 7 to 4 are see and not masked  These bits are cleared  Yes. Bits 7 to 4 are see and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ("QSFP+")           |

| RO Status Yes Bit 1 copies INTL lin Bit 0 is zero when meady  RO Loss of signal Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is serecive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  RO Temperature alarms  FRO Temperature alarms  FRO Temperature alarms  INTL output will be (low) if any of these appropriate when memperature goes abbelow the thresholds the start of register put in the start of register put in the start of register put in the start of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Hex 02              |

| RO Status Yes Bit 1 copies INTL lin Bit 0 is zero when meady  RO Loss of signal Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is serecive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  RO Temperature alarms  FRO Temperature alarms  FRO Temperature alarms  INTL output will be (low) if any of these appropriate when memperature goes abbelow the thresholds the start of register put in the start of register put in the start of register put in the start of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ("Infiniband spec") |

| Bit 1 copies INTL lin  Bit 0 is zero when moready  RO Loss of signal  Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is some receive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  RO TX fault  Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared  RO Temperature alarms  Pess. Bits 7 to 4 are see appropriate when more temperature goes ab below the thresholds the start of register points. INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                   |

| Bit 0 is zero when moready  3 RO Loss of signal Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is some receive is squelched low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared  These bits are cleared alarms appropriate when more temperature goes ab below the thresholds the start of register points. INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L line state        |

| RO Loss of signal Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is soreceive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  These bits are cleared appropriate when me temperature goes abbelow the thresholds the start of register put in the property in the search of th | (bit 2 zero =paged  |

| RO Loss of signal Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is soreceive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  These bits are cleared appropriate when me temperature goes abbelow the thresholds the start of register put in the property in the search of th |                     |

| RO Loss of signal Bit 7-4 (transmit LOS supported  Bits 3-0 (receive LOS implemented, bit is sereceive is squelched)  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  For appropriate when metemperature goes ab below the thresholds the start of register public low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | implemented)        |

| signal  Bits 3-0 (receive LOS implemented, bit is so receive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  France of the second of the start of register points. The second of the second of the start of register points and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1 /                 |

| Bits 3-0 (receive LOS implemented, bit is sereceive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared Yes. Bits 7 to 4 are see appropriate when metemperature goes abbelow the thresholds the start of register per INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11, 4               |

| implemented, bit is a receive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  Temperature alarms  Temperature goes ab below the thresholds the start of register put in the properties of the search  |                     |

| implemented, bit is a receive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  Temperature alarms  From the properties of the start of register points and not masked.  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LOS) are            |

| receive is squelched  INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  Temperature alarms  Yes. Bits 7 to 4 are se appropriate when metemperature goes abbelow the thresholds the start of register possible in the start of register possible.  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |

| INTL output will be (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared  These bits are cleared alarms  These bits 7 to 4 are see appropriate when metemperature goes ab below the thresholds the start of register points. INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  From temperature goes ab below the thresholds the start of register pure and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ned .               |

| (low) if any of these and not masked. The cleared on read.  4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  From temperature goes ab below the thresholds the start of register pure and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 he asserted       |

| and not masked. The cleared on read.  RO TX fault Yes (bits 3-0), bit wil any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  RO Temperature alarms  Pess. Bits 7 to 4 are se appropriate when metemperature goes abbelow the thresholds the start of register per suppose and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |

| cleared on read.  RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  RO Temperature alarms  Yes. Bits 7 to 4 are se appropriate when memperature goes abbelow the thresholds the start of register per suppose and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |

| 4 RO TX fault Yes (bits 3-0), bit will any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  Yes. Bits 7 to 4 are see appropriate when metemperature goes abbelow the thresholds the start of register points. INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The bits are        |

| any fault indicated by VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  Yes. Bits 7 to 4 are se appropriate when metemperature goes abbelow the thresholds the start of register publication.  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | will be set for n/a |

| VCSEL driver  INTL output will be (low) if any of these and not masked  These bits are cleared alarms  Yes. Bits 7 to 4 are se appropriate when metemperature goes about below the thresholds the start of register per support of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |

| INTL output will be (low) if any of these and not masked  These bits are cleared  These bits are cleared  Yes. Bits 7 to 4 are se appropriate when metemperature goes abbelow the thresholds the start of register pure start of register pure start of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ed by the           |

| (low) if any of these and not masked  These bits are cleared  RO Temperature alarms Yes. Bits 7 to 4 are se appropriate when metemperature goes abbelow the thresholds the start of register per start of the start of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

| (low) if any of these and not masked  These bits are cleared  RO Temperature alarms Yes. Bits 7 to 4 are se appropriate when metemperature goes abbelow the thresholds the start of register per start of the start of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 he asserted       |

| and not masked  These bits are cleared  RO Temperature alarms Temperature appropriate when metemperature goes about the start of register periods in the start of |                     |

| These bits are cleared RO Temperature alarms Yes. Bits 7 to 4 are see appropriate when me temperature goes abbelow the thresholds the start of register points.  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ese bits are set    |

| RO Temperature alarms Yes. Bits 7 to 4 are se appropriate when me temperature goes abbelow the thresholds the start of register per start of the sta |                     |

| RO Temperature alarms Yes. Bits 7 to 4 are se appropriate when me temperature goes abbelow the thresholds the start of register per start of the sta | eared on read.      |

| alarms appropriate when m temperature goes ab below the thresholds the start of register p  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |

| temperature goes ab below the thresholds the start of register p  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |

| below the thresholds the start of register p  INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

| INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |

| INTL output will be (low) if any of these and not masked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |