INTENDED FOR USE IN CIC, RIC, AND MINI-BTE APPLICATIONS. THIS IS A PAIR OF GE RECEIVERS WITH VERY LOW VIBRATION IN ALL DIRECTIONS. ONE GE RECEIVER IS REVERSE MAGNETIZED FOR MAGNETIC LEAKAGE CONSIDERATIONS. BOTH DAUGHTER UNITS HAVE THE CENTER TERMINAL CONNECTED TO CASE.

#### CONSTANT VOLTAGE DRIVE CONDITIONS 115 110 105 100 95 90 85 80 75 5 7 8 9 2 3 7 8 9 3 4 6 5 1000 100 10000

FREQUENCY IN HERTZ

### **ACOUSTICAL**

SENSITIVITY

DEVICE WILL PRODUCE THE SPL LISTED BELOW UNDER TEST CONDITIONS DESCRIBED IN TABLE 4. NOMINAL SENSITIVITY AT IKHZ IS dB RELATIVE TO  $20\mu P\alpha$ . ALL OTHER VALUES IN dB RELATIVE TO THE SENSITIVITY AT IkHz.

| •          |                |         |         |         |

|------------|----------------|---------|---------|---------|

| LIMIT TYPE | FREQUENCY (Hz) | MINIMUM | NOMINAL | MAXIMUM |

| REL        | 100            | -3.0    | 0.0     | + 3 . 0 |

| REL        | 250            | -2.5    | +0.5    | +3.5    |

| REL        | 500            | - 3 . 0 | 0.0     | + 3 . 0 |

| REF        | 1000           | -1.5    | 100.0   | +   . 5 |

| PEAK       | 2250 - 2750    | +3.5    | +6.5    | +9.5    |

| VALLEY     | 4000 - 5400    | -12.0   | - 9 . 0 | -6.0    |

| PEAK       | 4900 - 6700    | -8.5    | -5.5    | -2.5    |

TABLE I

TOTAL HARMONIC DISTORTION

DEVICE WILL NOT EXCEED TOTAL HARMONIC DISTORTION LEVELS LISTED BELOW.

| FREQUENCY (Hz) | AC DRIVE (Vrms) | DC BIAS (V) | LIMIT (%) |

|----------------|-----------------|-------------|-----------|

| 833            | 0.204           | 0           | 3         |

| 1250           | 0.204           | 0           | 3         |

| 833            | 0.576           | 0           | 8         |

| 1250           | 0.576           | 0           | 8         |

MAXIMUM OUTPUT LEVEL (TYPICAL)

| POWER (mW) | 500 Hz SPL<br>(dB) | REQUIRED VOLTAGE<br>(Vrms) | Peak SPL<br>(dB) | REQUIRED VOLTAGE<br>(Vrms) |

|------------|--------------------|----------------------------|------------------|----------------------------|

| 10         | 114.0              | 1,1                        | 124.0            | 1.6                        |

| 50         | 117.0              | 2.3                        | 128.0            | 3.1                        |

TABLE 3

#### **ELECTRICAL**

| DC RESISTANCE @ 20°C | 105.0 Ohms ± 10% |

|----------------------|------------------|

| IMPEDANCE @ 500 Hz   | 121.0 Ohms ± 15% |

| IMPEDANCE @ I kHz    | 144.4 Ohms ± 15% |

| INDUCTANCE @ 500 Hz  | 10.6 mH TYPICAL  |

| CAPACITANCE @ 10 MHz | 4.6 pF TYPICAL   |

TABLE 4

ISOLATION: CASE WILL BE ELECTRICALLY ISOLATED FROM THE COIL CIRCUIT.

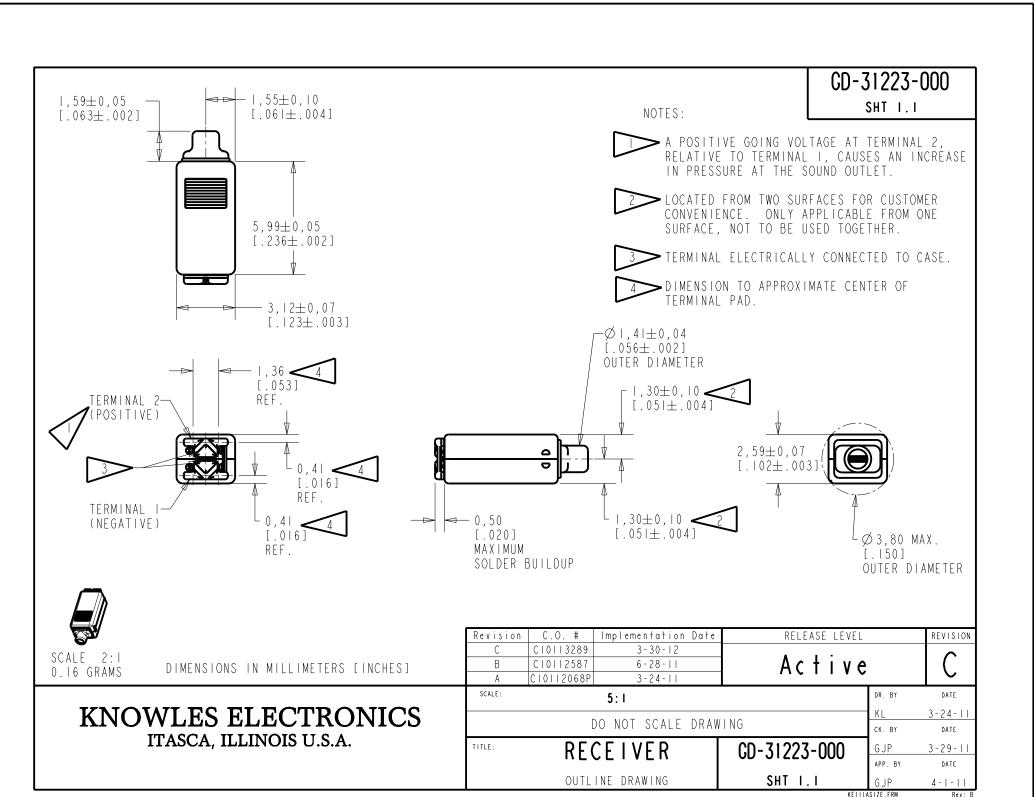

#### **MECHANICAL**

PORT LOCATION: 12S SOLDER TYPE: SAC305

TEMPERATURE

OPERATING: SENSITIVITY WILL NOT VARY MORE THAN +1/-3 dB AT 500 Hz FROM -17°C TO 63°C

STORAGE: -40°C TO 63°C

SHOCK RESISTANCE: 90% SURVIVAL RATE WITH THD @ 1/3 PEAK FREQUENCY LESS THAN 10%, THD @ 1/2 PEAK FREQUENCY LESS THAN 20% AND LESS THAN 3dB CHANGE IN SENSITIVITY AT IKHZ WHEN SUBJECTED TO 15,000 G.

RELEASE LEVEL

## **TEST CONDITIONS**

| NOMINAL SOURCE VOLTAGE | 0.204 Vrms, 0 mA DC BIAS                                        |

|------------------------|-----------------------------------------------------------------|

| SOURCE IMPEDANCE       | < I Ohm                                                         |

| TUBING                 |                                                                 |

| COUPLER CAVITY         | 2 CM <sup>3</sup> , SIMULATED ANSI S3.7 TYPE HA-3 (IEC 60318-5) |

TABLE 4

| B<br>A                                                                                                                                                                                                       | C10113289<br>C10112587<br>C10112068P | 3-30-12<br>6-28-11<br>3-24-11 |        | Active              |               | C                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------|--------|---------------------|---------------|-----------------------|

| WHEN TEST LIMITS ARE USED TO ESTABLISH INCOMING INSPECTION ACCEPTANCE/REJECTION CRITERIA, CORRELATION OF TEST EQUIPMENT WITH KNOWLES IS ALSO REQUIRED FOR ELIMINATION OF EQUIPMENT AND TEST METHOD VARIATION |                                      |                               | DR. BY | DATE<br>3 - 24 - 11 |               |                       |

| TITLE:                                                                                                                                                                                                       | D.E.                                 | CFIVER                        |        | CD-31223-000        | CK. BY<br>GJP | DATE<br>3 - 2 9 - 1 1 |

|                                                                                                                                                                                                              |                                      | CLIVLIN<br>ICE SPECIFICATIO   | N      | SHT 2.1             | APP. BY       | DATE 4 -              |

Revision C.O. # Implementation Date

# **KNOWLES ELECTRONICS** ITASCA, ILLINOIS U.S.A.