# LAN9116

# Highly Efficient Single-Chip 10/100 Non-PCI Ethernet Controller

## Highlights

- Member of LAN9118 Family; optimized for medium-high performance applications

- Easily interfaces to most 32-bit and 16-bit embedded CPU's

- · Efficient architecture with low CPU overhead

- Integrated PHY

- Supports audio & video streaming over Ethernet: 1-2 high-definition (HD) MPEG2 streams

- Medium-high speed member of LAN9118 Family (all members are pin-compatible)

# **Target Applications**

- Medium-range Cable, satellite, and IP set-top boxes

- Digital video recorders and DVD recorders/players

- High definition televisions

- · Digital media clients/servers and home gateways

- · Video-over IP Solutions, IP PBX & video phones

- Wireless routers & access points

### **Key Benefits**

- Non-PCI Ethernet controller for medium-high performance applications

- 32-bit interface

- Burst-mode read support

- · Eliminates dropped packets

- Internal buffer memory can store over 200 packets

- Supports automatic or host-triggered PAUSE and back-pressure flow control

- Minimizes CPU overhead

- Supports Slave-DMA

- Interrupt Pin with Programmable Hold-off timer

- Reduces system cost and increases design flexibility

- SRAM-like interface easily interfaces to most embedded CPU's or SoC's

- Low-cost, low--pin count non-PCI interface for embedded designs

- Reduced Power Modes

- Numerous power management modes

- Wake on LAN\*

- Magic packet wakeup\*

- Wakeup indicator event signal

- Link Status Change

- · Single chip Ethernet controller

- Fully compliant with IEEE 802.3/802.3u standards

- Integrated Ethernet MAC and PHY

- 10BASE-T and 100BASE-TX support

- Full- and Half-duplex support

- Full-duplex flow control

- Backpressure for half-duplex flow control

- Preamble generation and removal

- Automatic 32-bit CRC generation and checking

- Automatic payload padding and pad removalLoop-back modes

- Flexible address filtering modes

- One 48-bit perfect address

- 64 hash-filtered multicast addresses

- Pass all multicast

- Promiscuous mode

- Inverse filtering

- Pass all incoming with status report

- Disable reception of broadcast packets

- Integrated Ethernet PHY

- Auto-negotiation

- Automatic polarity detection and correction

- · High-Performance host bus interface

- Simple, SRAM-like interface

- 32/16-bit data bus

- Large, 16Kbyte FIFO memory that can be allocated to RX or TX functions

- One configurable host interrupt

- · Miscellaneous features

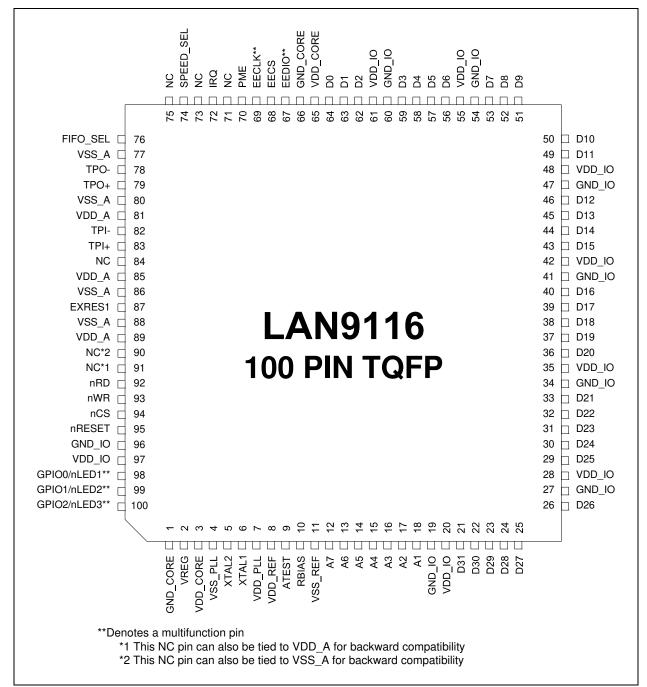

- Low profile 100-pin, TQFP RoHS Compliant package

- Integral 1.8V regulator

- General Purpose Timer

- Support for optional EEPROM

- Support for 3 status LEDs multiplexed with Programmable GPIO signals

- 3.3V Power Supply with 5V tolerant I/O

- 0 to 70°C

- \* Third-party brands and names are the property of their respective owners.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| 1.0 General Description                                                                                  |     |

|----------------------------------------------------------------------------------------------------------|-----|

| 1.0 General Description         2.0 Pin Description and Configuration         3.0 Functional Description |     |

| 3.0 Functional Description                                                                               |     |

| 4.0 Internal Ethernet PHY                                                                                |     |

| 5.0 Register Description<br>6.0 Timing Diagrams                                                          | 53  |

| 6.0 Timing Diagrams                                                                                      |     |

| 7.0 Operational Characteristics                                                                          | 100 |

| 8.0 Package Outline                                                                                      |     |

|                                                                                                          | 104 |

| Appendix A: Data Sheet Revision History                                                                  | 105 |

| The Microchip Web Site                                                                                   | 106 |

| Customer Change Notification Service                                                                     | 106 |

| Customer Support                                                                                         | 106 |

| Product Identification System                                                                            | 107 |

# 1.0 GENERAL DESCRIPTION

The LAN9116 is a full-featured, single-chip 10/100 Ethernet controller designed for embedded applications where performance, flexibility, ease of integration and system cost control are required. The LAN9116 has been architected to provide the best price-performance ratio for any 32-bit application with medium-high performance requirements. The LAN9116 is fully IEEE 802.3 10BASE-T and 802.3u 100BASE-TX compliant.

The LAN9116 includes an integrated Ethernet MAC and PHY with a high-performance SRAM-like slave interface. The simple, yet highly functional host bus interface provides a glue-less connection to most common 16-bit and 32-bit microprocessors and microcontrollers. The LAN9116 includes large transmit and receive data FIFOs to accommodate high latency applications. In addition, the LAN9116 memory buffer architecture allows the most efficient use of memory resources by optimizing packet granularity.

#### Applications

The LAN9116 is well suited for medium-high-performance embedded applications, including:

- Medium-range cable, satellite and IP set-top boxes

- · Digital video recorders

- DVD Recorders/Players

- High-definition televisions

- · Digital media clients/servers

- · Home gateways

The LAN9116 also supports features which reduce or eliminate packet loss. Its internal 16-KByte SRAM can hold over 200 received packets. If the receive FIFO gets too full, the LAN9116 can automatically generate flow control packets to the remote node, or assert back-pressure on the remote node by generating network collisions.

The LAN9116 supports numerous power management and wakeup features. The LAN9116 can be placed in a reduced power mode and can be programmed to issue an external wake signal via several methods, including "Magic Packet", "Wake on LAN" and "Link Status Change". This signal is ideal for triggering system power-up using remote Ethernet wakeup events. The device can be removed from the low power state via a host processor command.

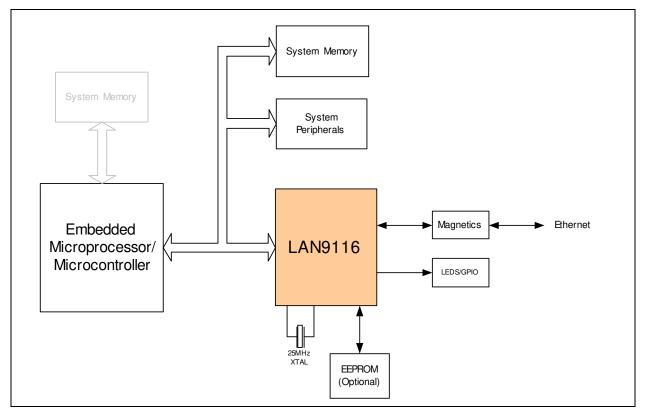

FIGURE 1-1: SYSTEM BLOCK DIAGRAM UTILIZING THE LAN9116

The Microchip LAN9116 integrated 10/100 MAC/PHY controller is a peripheral chip that performs the function of translating parallel data from a host controller into Ethernet packets. The LAN9116 Ethernet MAC/PHY controller is designed and optimized to function in an embedded environment. All communication is performed with programmed I/O transactions using the simple SRAM-like host interface bus.

The diagram shown above, describes a typical system configuration of the LAN9116 in a typical embedded environment.

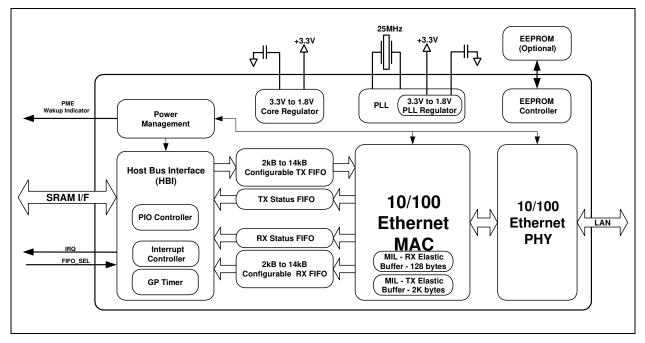

The LAN9116 is a general purpose, platform independent, Ethernet controller. The LAN9116 consists of four major functional blocks. The four blocks are:

- 10/100 Ethernet PHY

- 10/100 Ethernet MAC

- RX/TX FIFOs

- Host Bus Interface (HBI)

#### 1.1 Internal Block Overview

This section provides an overview of each of these functional blocks as shown in Figure 1-2, "Internal Block Diagram".

#### FIGURE 1-2: INTERNAL BLOCK DIAGRAM

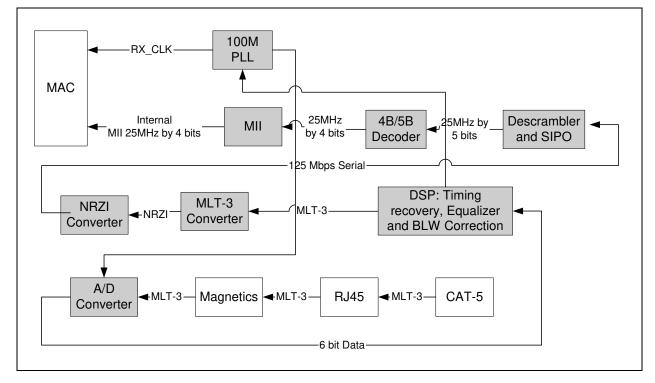

### 1.2 10/100 Ethernet PHY

The LAN9116 integrates an IEEE 802.3 physical layer for twisted pair Ethernet applications. The PHY can be configured for either 100 Mbps (100Base-TX) or 10 Mbps (10Base-T) Ethernet operation in either full or half duplex configurations. The PHY block includes auto-negotiation.

Minimal external components are required for the utilization of the Integrated PHY.

# 1.3 10/100 Ethernet MAC

The transmit and receive data paths are separate within the MAC allowing the highest performance especially in full duplex mode. The data paths connect to the PIO interface Function via separate busses to increase performance. Payload data as well as transmit and receive status is passed on these busses.

A third internal bus is used to access the MAC's Control and Status Registers (CSR's). This bus is accessible from the host through the PIO interface function.

On the backend, the MAC interfaces with the internal 10/100 PHY through a the MII (Media Independent Interface) port internal to the LAN9116. The MAC CSR's also provides a mechanism for accessing the PHY's internal registers through the internal SMI (Serial Management Interface) bus.

The MAC Interface Layer (MIL), within the MAC, contains a 2K Byte transmit and a 128 Byte receive FIFO which is separate from the TX and RX FIFOs. The FIFOs within the MAC are not directly accessible from the host interface. The differentiation between the TX/RX FIFO memory buffers and the MAC buffers is that when the transmit or receive packets are in the MAC buffers, the host no longer can control or access the TX or RX data. The MAC buffers (both TX and RX) are in effect the working buffers of the Ethernet MAC logic. In the case of reception, the data must be moved first to the RX FIFOs for the host to access the data. For TX operations, the MIL operates in store-and-forward mode and will queue an entire frame before beginning transmission.

#### 1.4 Receive and Transmit FIFOs

The Receive and Transmit FIFOs allow increased packet buffer storage to the MAC. The FIFOs are a conduit between the host interface and the MAC through which all transmitted and received data and status information is passed. Deep FIFOs allow a high degree of latency tolerance relative to the various transport and OS software stacks thus reducing or minimizing overrun conditions. Like the MAC, the FIFOs have separate receive and transmit data paths. In addition, the RX and TX FIFOs are configurable in size, allowing increased flexibility.

#### 1.5 Interrupt Controller

The LAN9116 supports a single programmable interrupt. The programmable nature of this interrupt allows the user the ability to optimize performance dependent upon the application requirement. Both the polarity and buffer type of the interrupt pin are configurable for the external interrupt processing. The interrupt line can be configured as an open-drain output to facilitate the sharing of interrupts with other devices. In addition, a programmable interrupt de-assertion interval is provided.

#### 1.6 GPIO Interface

A 3-bit GPIO and 2-bit GPO (Multiplexed on the EEPROM and LED Pins) interface is included in the LAN9116. It is accessible through the host bus interface via the CSRs. The GPIO signals can function as inputs, push-pull outputs and open drain outputs. The GPIO's (GPO's are not configurable) can also be configured to trigger interrupts with programmable polarity.

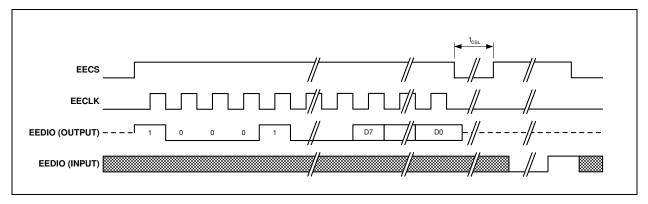

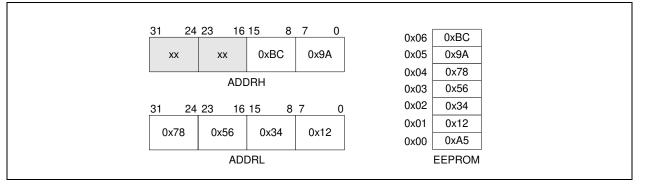

### 1.7 Serial EEPROM Interface

A serial EEPROM interface is included in the LAN9116. The serial EEPROM is optional and can be programmed with the LAN9116 MAC address. The LAN9116 can optionally load the MAC address automatically after power-on.

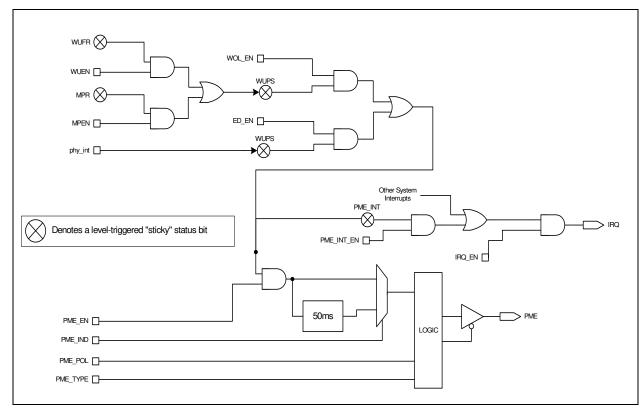

#### **1.8 Power Management Controls**

The LAN9116 supports comprehensive array of power management modes to allow use in power sensitive applications. Wake on LAN, Link Status Change and Magic Packet detection are supported by the LAN9116. An external PME (Power Management Event) interrupt is provided to indicate detection of a wakeup event.

### 1.9 General Purpose Timer

The general-purpose timer has no dedicated function within the LAN9116 and may be programmed to issue a timed interrupt.

### 1.10 Host Bus Interface (SRAM Interface)

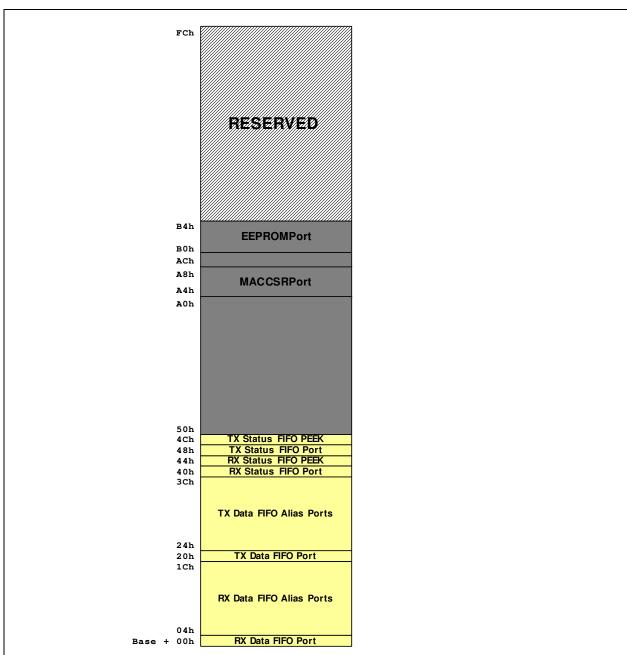

The host bus interface provides a FIFO interface for the transmit and receive data paths, as well as an interface for the LAN9116 Control and Status Registers (CSR's).

The host bus interface is the primary bus for connection to the embedded host system. This interface models an asynchronous SRAM. TX FIFO, RX FIFO, and CSR's are accessed through this interface. Programmed I/O transactions are supported.

The LAN9116 host bus interface supports 32-bit and 16-bit bus transfers; internally, all data paths are 32-bits wide. The LAN9116 can be interfaced to either Big-Endian or Little-Endian processors in either 32-bit or 16-bit external bus width modes of operation.

The host bus data Interface is responsible for host address decoding and data bus steering. The host bus interface handles the 16 to 32-bit conversion when the LAN9116 is configured with a 16-bit host interface. Additionally, when Big Endian mode is selected, the data path to the internal controller registers will be reorganized accordingly.

# LAN9116

# 2.0 PIN DESCRIPTION AND CONFIGURATION

| Pin No.                         | Name                 | Symbol   | Buffer<br>Type | # Pins | Description                                                                                                                                                                     |

|---------------------------------|----------------------|----------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-26,29-<br>33,36-40           | Host Data High       | D[31:16] | I/O8 (PD)      | 16     | Bi-directional data port.<br>Note that Pull-down's are disabled in 32<br>bit mode.                                                                                              |

| 43-46,49-<br>53,56-59,62-<br>64 | Host Data Low        | D[15:0]  | I/O8           | 16     | Bi-directional data port.                                                                                                                                                       |

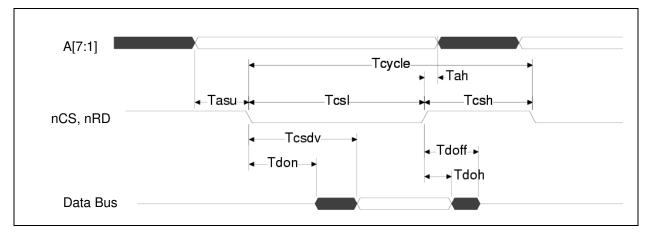

| 12-18                           | Host Address         | A[7:1]   | IS             | 7      | 7-bit Address Port. Used to select<br>Internal CSR's and TX and RX FIFOs.                                                                                                       |

| 92                              | Read Strobe          | nRD      | IS             | 1      | Active low strobe to indicate a read cycle.                                                                                                                                     |

| 93                              | Write Strobe         | nWR      | IS             | 1      | Active low strobe to indicate a write cycle. This signal, qualified with nCS, is also used to wakeup the LAN9116 when it is in a reduced power state.                           |

| 94                              | Chip Select          | nCS      | IS             | 1      | Active low signal used to qualify read<br>and write operations. This signal<br>qualified with nWR is also used to<br>wakeup the LAN9116 when it is in a<br>reduced power state. |

| 72                              | Interrupt<br>Request | IRQ      | O8/OD8         | 1      | Programmable Interrupt request.<br>Programmable polarity, source and<br>buffer types.                                                                                           |

| 76                              | FIFO Select          | FIFO_SEL | IS             | 1      | When driven high all accesses to the LAN9116 are to the RX or TX Data FIFOs. In this mode, the A[7:3] upper address inputs are ignored.                                         |

TABLE 2-1: HOST BUS INTERFACE SIGNALS

#### TABLE 2-2: DEFAULT ETHERNET SETTINGS

|           | Default Ethernet Settings |             |           |  |  |  |

|-----------|---------------------------|-------------|-----------|--|--|--|

| SPEED_SEL | Speed                     | Duplex      | Auto Neg. |  |  |  |

| 0         | 10MBPS                    | HALF-DUPLEX | DISABLED  |  |  |  |

| 1         | 100MBPS                   | HALF-DUPLEX | ENABLED   |  |  |  |

# TABLE 2-3: LAN INTERFACE SIGNALS

| Pin No. | Name                          | Symbol | Buffer<br>Type | # Pins | Description                                                  |

|---------|-------------------------------|--------|----------------|--------|--------------------------------------------------------------|

| 79      | TXP                           | TPO+   | AO             | 1      | Twisted Pair Transmit Output, Positive                       |

| 78      | TXN                           | TPO-   | AO             | 1      | Twisted Pair Transmit Output, Negative                       |

| 83      | RXP                           | TPI+   | AI             | 1      | Twisted Pair Receive Input, Positive                         |

| 82      | RXN                           | TPI-   | AI             | 1      | Twisted Pair Receive Input, Negative                         |

| 87      | PHY External Bias<br>Resistor | EXRES1 | AI             | 1      | Must be connected to ground through a 12.4K ohm 1% resistor. |

| Pin No. | Name                                             | Symbol                                    | Buffer<br>Type | # Pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------|-------------------------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67      | EEPROM Data,<br>GPO3, TX_EN,<br>TX_CLK, D32/nD16 | EEDIO/GPO3/<br>TX_EN/TX_CLK<br>(D32/nD16) | I/O8           | 1      | <b>EEPROM Data:</b> This bi-directional pin<br>can be connected to a serial<br>EEPROM DIO. This is optional.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                                                  |                                           |                |        | <b>General Purpose Output 3:</b> This pin<br>can also function as a general<br>purpose output, or it can be<br>configured to monitor the TX_EN or<br>TX_CLK signals on the internal MII<br>port. When configured as a GPO<br>signal, or as a TX_EN/TX_CLK<br>monitor, the EECS pin is deasserted<br>so as to never unintentionally access<br>the serial EEPROM. This signal<br>cannot function as a general-purpose<br>input.                                                                                                                                            |

|         |                                                  |                                           |                |        | <b>Data Bus Width Select:</b> This signal<br>also functions as a configuration input<br>on power-up and is used to select the<br>host bus data width. Upon deassertion<br>of reset, the value of the input is<br>latched. When high, a 32-bit data bus<br>is utilized. When low, a 16-bit interface<br>is utilized.                                                                                                                                                                                                                                                      |

| 68      | EEPROM Chip<br>Select                            | EECS                                      | O8             | 1      | Serial EEPROM chip select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 69      | EEPROM Clock,<br>GPO4 RX_DV,<br>RX_CLK           | EECLK/GPO4/<br>RX_DV/RX_CLK               | O8             | 1      | EEPROM Clock: Serial EEPROM<br>Clock pin.<br>General Purpose Output 4: This pin<br>can also function as a general-<br>purpose output, or it can be<br>configured to monitor the RX_DV or<br>RX_CLK signals on the internal MII<br>port. When configured as a GPO<br>signal, or as an RX_DV/RX_CLK<br>monitor, the EECS pin is deasserted<br>so as to never unintentionally access<br>the serial EEPROM. This signal<br>cannot function as a general-purpose<br>input.<br>Note: When the EEPROM inter-<br>face is not used, the<br>EECLK pin must be left<br>unconnected. |

TABLE 2-4: SERIAL EEPROM INTERFACE SIGNALS

#### TABLE 2-5: SYSTEM AND POWER SIGNALS

| Pin No. | Name      | Symbol | Buffer<br>Type | # Pins | Description                                                                                                                                                      |

|---------|-----------|--------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6       | Crystal 1 | XTAL1  | lclk           | 1      | External 25MHz Crystal Input.<br>Can also be connected to single-ended<br>TTL oscillator. If this method is<br>implemented, XTAL2 should be left<br>unconnected. |

| 5       | Crystal 2 | XTAL2  | Oclk           | 1      | External 25MHz Crystal output.                                                                                                                                   |

| Pin No.                   | Name             | Symbol    | Buffer<br>Type | # Pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|------------------|-----------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95                        | Reset            | nRESET    | IS<br>(PU)     | 1      | Active-low reset input. Resets all logic<br>and registers within the LAN9116 This<br>signal is pulled high with a weak<br>internal pull-up resistor. If nRESET is<br>left unconnected, the LAN9116 will rely<br>on its internal power-on reset circuitry<br><b>Note:</b> The LAN9116 must always<br>be read at least once after<br>power-up, reset, or upon<br>return from a power-saving<br>state or write operations will<br>not function. See Section<br>3.11, "Detailed Reset<br>Description," on page 31 for<br>additional information                                                                                                              |

| 70                        | Wakeup Indicator | PME       | O8/OD8         | 1      | <ul> <li>When programmed to do so, is asserted when the LAN9116 detects a wake event and is requesting the system to wake up from the associated sleep state. The polarity and buffer type of this signal is programmable.</li> <li>Note: Detection of a Power Management Event, and assertion of the PME signal will not wakeup the LAN9116. The LAN9116 will only wake up when it detects a host write cycle (assertion of nCS and nWR). Although any write to the LAN9116, regardless of the data written, will wake-up the device when it is in a power-saving mode, it is required that the BYTE_TEST register be used for this purpose.</li> </ul> |

| 71,73,7<br>5,84,90,<br>91 | Reserved         | Reserved  |                | 5      | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 74                        | 10/100 Selector  | SPEED_SEL | I (PU)         | 1      | This signal functions as a configuration<br>input on power-up and is used to select<br>the default Ethernet settings. Upon<br>deassertion of reset, the value of the<br>input is latched. This signal functions<br>as shown in Table 2-2, "Default<br>Ethernet Settings", below.                                                                                                                                                                                                                                                                                                                                                                         |

| TABLE 2-5: | SYSTEM AND POWER SIGNALS (CC | ONTINUED)                              |

|------------|------------------------------|----------------------------------------|

|            |                              | ······································ |

| TABLE 2                             | ABLE 2-5: SYSTEM AND POWER SIGNALS (CONTINUED)                                                                                             |                        |                 |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.                             | Name                                                                                                                                       | Symbol                 | Buffer<br>Type  | # Pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 100, 99,<br>98                      | General Purpose I/O<br>data,<br>nLED1 (Speed<br>Indicator),<br>nLED2 (Link &<br>Activity Indicator),<br>nLED3 (Full-<br>Duplex Indicator). | GPIO[2:0]/<br>LED[3:1] | IS/O12/<br>OD12 | 3      | <b>General Purpose I/O data:</b> These<br>three general-purpose signals are fully<br>programmable as either push-pull<br>output, open-drain output or input by<br>writing the GPIO_CFG configuration<br>register in the CSR's. They are also<br>multiplexed as GP LED connections.<br>GPIO signals are Schmitt-triggered<br>inputs. When configured as LED<br>outputs these signals are open-drain.                                                                                                                                           |  |

|                                     |                                                                                                                                            |                        |                 |        | <b>nLED1 (Speed Indicator).</b> This signal<br>is driven low when the operating speed<br>is 100Mbs, during auto-negotiation and<br>when the cable is disconnected. This<br>signal is driven high only during 10Mbs<br>operation.                                                                                                                                                                                                                                                                                                              |  |

|                                     |                                                                                                                                            |                        |                 |        | <b>nLED2 (Link &amp; Activity Indicator).</b><br>This signal is driven low (LED on)<br>when the LAN9116 detects a valid link.<br>This signal is pulsed high (LED off) for<br>80mS whenever transmit or receive<br>activity is detected. This signal is then<br>driven low again for a minimum of<br>80mS, after which time it will repeat the<br>process if TX or RX activity is detected.<br>Effectively, LED2 is activated solid for a<br>link. When transmit or receive activity<br>is sensed LED2 will flash as an activity<br>indicator. |  |

|                                     |                                                                                                                                            |                        |                 |        | <b>nLED3 (Full-Duplex Indicator).</b> This signal is driven low when the link is operating in full-duplex mode.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 10                                  | RBIAS                                                                                                                                      | RBIAS                  | AI              | 1      | <b>PLL Bias:</b> Connect to an external 12.0K ohm 1.0% resistor to ground. Used for the PLL Bias circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 9                                   | Test Pin                                                                                                                                   | ATEST                  | Ι               | 1      | This pin must be connected to VDD for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 2                                   | Internal Regulator<br>Power                                                                                                                | VREG                   | Р               | 1      | 3.3V input for internal voltage regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 20,28,3<br>5,<br>42,48,5<br>5,61,97 | +3.3V I/O Power                                                                                                                            | VDD_IO                 | Р               | 8      | +3.3V I/O logic power supply pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 19,27,3<br>4,41,47,<br>54,60,9<br>6 | I/O Ground                                                                                                                                 | GND_IO                 | Р               | 8      | Ground for I/O pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 81,85,8<br>9                        | +3.3V Analog Power                                                                                                                         | VDD_A                  | Р               | 3      | +3.3V Analog power supply pins. See Note 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 77,80,8<br>6,88                     | Analog Ground                                                                                                                              | VSS_A                  | Р               | 4      | Ground for analog circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 3,65                                | Core Voltage<br>Decoupling                                                                                                                 | VDD_CORE               | Ρ               | 2      | 1.8 V from internal core regulator. Both<br>pins must be connected together<br>externally and then tied to a 10uF 0.1-<br>Ohm ESR capacitor, in parallel with a<br>0.01uF capacitor to Ground next to<br>each pin. These pins must not be used<br>to supply power to other external<br>devices. See Note 2-1                                                                                                                                                                                                                                  |  |

# TABLE 2-5: SYSTEM AND POWER SIGNALS (CONTINUED)

| Pin No. | Name             | Symbol   | Buffer<br>Type | # Pins | Description                                                                                                                                                                                                                                                         |

|---------|------------------|----------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,66    | Core Ground      | GND_CORE | Р              | 2      | Ground for internal digital logic                                                                                                                                                                                                                                   |

| 7       | PLL Power        | VDD_PLL  | Р              | 1      | 1.8V Power from the internal PLL<br>regulator. This external pin must be<br>connected to a 10uF 0.1-Ohm ESR<br>capacitor, in parallel with a 0.01uF<br>capacitor to Ground. This pin must not<br>be used to supply power to other<br>external devices. See Note 2-1 |

| 4       | PLL Ground       | VSS_PLL  | Р              | 1      | GND for the PLL                                                                                                                                                                                                                                                     |

| 8       | Reference Power  | VDD_REF  | Р              | 1      | Connected to 3.3v power and used as<br>the reference voltage for the internal<br>PLL                                                                                                                                                                                |

| 11      | Reference Ground | VSS_REF  | Р              | 1      | Ground for internal PLL reference voltage                                                                                                                                                                                                                           |

TABLE 2-5: SYSTEM AND POWER SIGNALS (CONTINUED)

**Note 2-1** Please refer to the Microchip application note AN 12.5 titled "Designing with the LAN9118 - Getting Started". It is also important to note that this application note applies to the whole Microchip LAN9118 family of Ethernet controllers. However, subtle differences may apply.

# 2.1 Buffer Types

#### TABLE 2-6:BUFFER TYPES

| Туре | Description                           |

|------|---------------------------------------|

| I    | Input pin                             |

| IS   | Schmitt triggered Input               |

| 012  | Output with 12mA sink and 12mA source |

| OD12 | Open-drain output with 12mA sink      |

| IO8  | I/O with 8mA symmetrical drive        |

| OD8  | Open-drain output with 8mA sink       |

| O8   | Output 8mA symmetrical drive          |

| PU   | 50uA (typical) internal pull-up       |

| PD   | 50uA (typical) internal pull-down     |

| AI   | Analog input                          |

| AO   | Analog output                         |

| AIO  | Analog bi-directional                 |

| ICLK | Crystal oscillator input pin          |

| OCLK | Crystal oscillator output pin         |

# 3.0 FUNCTIONAL DESCRIPTION

## 3.1 10/100 Ethernet MAC

The Ethernet Media Access controller (MAC) incorporates the essential protocol requirements for operating an Ethernet/IEEE 802.3-compliant node and provides an interface between the host subsystem and the internal Ethernet PHY. The MAC can operate in either 100-Mbps or 10-Mbps mode.

The MAC operates in both half-duplex and full-duplex modes. When operating in half-duplex mode, the MAC complies fully with Section 4 of ISO/IEC 8802-3 (ANSI/IEEE standard) and ANSI/IEEE 802.3 standards. When operating in full-duplex mode, the MAC complies with IEEE 802.3x full-duplex operation standard.

The MAC provides programmable enhanced features designed to minimize host supervision, bus utilization, and preor post-message processing. These features include the ability to disable retries after a collision, dynamic FCS (Frame Check Sequence) generation on a frame-by-frame basis, automatic pad field insertion and deletion to enforce minimum frame size attributes, and automatic retransmission and detection of collision frames.

The MAC can sustain transmission or reception of minimally-sized back-to-back packets at full line speed with an interpacket gap (IPG) of 9.6 microseconds for 10 Mbps and 0.96 microseconds for 100 Mbps.

The primary attributes of the MAC Function are:

- · Transmit and receive message data encapsulation

- · Framing (frame boundary delimitation, frame synchronization)

- Error detection (physical medium transmission errors)

- · Media access management

- Medium allocation (collision detection, except in full-duplex operation)

- · Contention resolution (collision handling, except in full-duplex operation)

- · Flow control during full-duplex mode

- Decoding of control frames (PAUSE command) and disabling the transmitter

- Generation of control frames

- · Interface to the internal PHYI

The transmit and receive data paths are separate within the LAN9116 from the MAC to host interface allowing the highest performance, especially in full duplex mode. Payload data as well as transmit and receive status are passed on these busses.

A third internal bus is used to access the MAC's "Control and Status Registers" (CSR's). This bus is also accessible from the host.

On the backend, the MAC interfaces with the 10/100 PHY through an internal MII (Media Independent Interface) port, internal to the LAN9116. The MAC CSR's also provide a mechanism for accessing the PHY's internal registers through the internal SMI (Serial Management Interface) bus.

The receive and transmit FIFOs allow increased packet buffer storage to the MAC. The FIFOs are a conduit between the host interface and the MAC through which all transmitted and received data and status information is passed. Deep FIFOs allow a high degree of latency tolerance relative to the various transport and OS software stacks reducing and minimizing overrun conditions. Like the MAC, the FIFOs have separate receive and transmit data paths.

The LAN9116 can store up to 250 Ethernet packets utilizing FIFOs, totaling 16K bytes, with a packet granularity of 4 bytes. This memory is shared by the RX and TX blocks and is configurable in terms of allocation. This depth of buffer storage minimizes or eliminates receive overruns.

# 3.2 Flow Control

The LAN9116 Ethernet MAC supports full-duplex flow control using the pause operation and control frame. It also supports half-duplex flow control using back pressure.

#### 3.2.1 FULL-DUPLEX FLOW CONTROL

The pause operation inhibits data transmission of data frames for a specified period of time. A Pause operation consists of a frame containing the globally assigned multicast address (01-80-C2-00-00-01), the PAUSE opcode, and a parameter indicating the quantum of slot time (512 bit times) to inhibit data transmissions. The PAUSE parameter may range from 0 to 65,535 slot times. The Ethernet MAC logic, on receiving a frame with the reserved multicast address and PAUSE opcode, inhibits data frame transmissions for the length of time indicated. If a Pause request is received while a transmission is in progress, then the pause will take effect after the transmission is complete. Control frames are received and processed by the MAC and are passed on.

The MAC also transmits control frames (pause command) via both hardware and software control. The software driver requests the MAC to transmit a control frame and gives the value of the PAUSE time to be used in the control frame. The MAC Function constructs a control frame with the appropriate values set in all the different fields (as defined in the 802.3x specification) and transmits the frame to the MII interface. The transmission of the control frame is not affected by the current state of the Pause timer value that is set because of a recently received control frame.

#### 3.2.2 HALF-DUPLEX FLOW CONTROL (BACKPRESSURE)

In half-duplex mode, back pressure is used for flow control. Whenever the receive buffer/FIFO becomes full or crosses a certain threshold level, the MAC starts sending a Jam signal. The MAC transmit logic enters a state at the end of current transmission (if any), where it waits for the beginning of a received frame. Once a new frame starts, the MAC starts sending the Jam signal, which will result in a collision. After sensing the collision, the remote station will back off its transmission. The MAC continues sending the jam to make other stations defer transmission. The MAC only generates this collision-based back pressure when it receives a new frame, in order to avoid any late collisions.

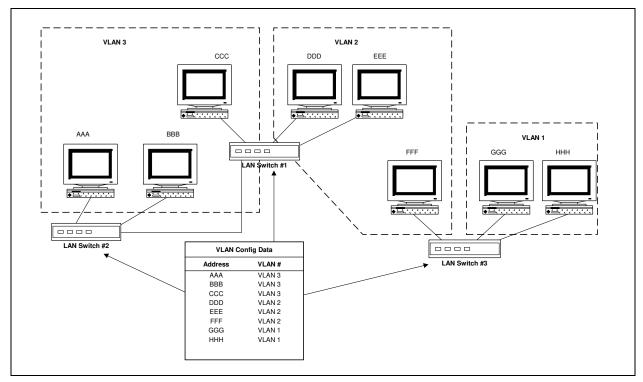

#### 3.2.3 VIRTUAL LOCAL AREA NETWORK (VLAN)

VLAN is a means to form a "broadcast domain" without restriction on the physical or geographical location on the members of that domain. VLAN can be implemented in any number of different factors, such as:

- · Physical port

- MAC address

- Layer-3 unicast address

- · Multicast address

- Date/time in combination with MAC address, etc.

An example of a VLAN is depicted in Figure 3-1, "VLAN Topology". It demonstrates the freedom from physical constraint on the network, and the ability to divide a single switched network into a smaller broadcast domain.

Moreover, VLAN offers a number of other advantages, such as:

**Configurability:** Changes to an existing VLAN can be made on the network administrative level, rather than on the hardware level. A member of a VLAN can thus change its MAC address or its port and still be a member of the same VLAN. Extra routing is not necessary.

**Security:** VLAN can improve security by demanding a predefined authentication before admitting a new member to the domain.

**Network efficiency:** Allows shielding one system resource from traffic not meant for that resource. A workstation in one VLAN is shielded from traffic on another VLAN, increasing that workstation's efficiency.

Broadcast containment: Leakage of broadcast frames from one VLAN to another is prevented.

FIGURE 3-1: VLAN TOPOLOGY

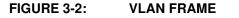

When the members of a VLAN are not located on the same physical medium, the VLAN uses a tag to help it determine how to forward the frame from one member to another. The tag structure was proprietary until the IEEE released a supplement to 802.3 defining the VLAN frame structure, including the tag. This new frame structure for VLAN is depicted in Figure 3-2, "VLAN Frame".

The MAC Function recognizes transmitted and received frames tagged with either one-level or two-level VLAN IDs. The MAC compares the thirteenth and fourteenth bytes of transmit and receive frames to the contents of both the one-level VLAN tag register and the two-level VLAN tag register. If a match is found, the MAC Function identifies the frame as either a one- or two-level VLAN frame, depending on where the match was found. Upon recognizing that a frame has a VLAN tag, counter thresholds are adjusted to account for the extra bytes that the VLAN tag adds to the frame. The maximum length of the good packet is thus changed from 1518 bytes to 1522 bytes.

# 3.3 Address Filtering Functional Description

The Ethernet address fields of an Ethernet Packet, consists of two 6-byte fields: one for the destination address and one for the source address. The first bit of the destination address signifies whether it is a physical address or a multicast address.

The LAN9116 address check logic filters the frame based on the Ethernet receive filter mode that has been enabled. Filter modes are specified based on the state of the control bits in Table 3-1, "Address Filtering Modes", which shows the various filtering modes used by the Ethernet MAC Function. These bits are defined in more detail in the "MAC Control Register". Please refer to Section 5.4.1, "MAC\_CR—MAC Control Register," on page 75 for more information on this register.

If the frame fails the filter, the Ethernet MAC function does not receive the packet. The host has the option of accepting or ignoring the packet.

|       | ſ    | ſ       | T  |        |                                                                                                     |

|-------|------|---------|----|--------|-----------------------------------------------------------------------------------------------------|

| MCPAS | PRMS | INVFILT | НО | HPFILT | Description                                                                                         |

| 0     | 0    | 0       | 0  | 0      | MAC address perfect filtering only for all addresses.                                               |

| 0     | 0    | 0       | 0  | 1      | MAC address perfect filtering for<br>physical address and hash filtering<br>for multicast addresses |

| 0     | 0    | 0       | 1  | 1      | Hash Filtering for physical and multicast addresses                                                 |

| 0     | 0    | 1       | 0  | 0      | Inverse Filtering                                                                                   |

| Х     | 1    | 0       | Х  | Х      | Promiscuous                                                                                         |

| 1     | 0    | 0       | 0  | Х      | Pass all multicast frames. Frames with physical addresses are perfect-filtered                      |

| 1     | 0    | 0       | 1  | 1      | Pass all multicast frames. Frames with physical addresses are hash-filtered                         |

TABLE 3-1: ADDRESS FILTERING MODES

#### 3.4 Filtering Modes

#### 3.4.1 PERFECT FILTERING

This filtering mode passes only incoming frames whose destination address field exactly matches the value programmed into the MAC Address High register and the MAC address low register. The MAC address is formed by the concatenation of the above two registers in the MAC CSR Function.

#### 3.4.2 HASH ONLY FILTERING

This type of filtering checks for incoming Receive packets with either multicast or physical destination addresses, and executes an imperfect address filtering against the hash table.

During imperfect hash filtering, the destination address in the incoming frame is passed through the CRC logic and the upper six bits of the CRC register are used to index the contents of the hash table. The hash table is formed by merging the register's multicast hash table high and multicast hash table low in the MAC CSR Function to form a 64-bit hash table. The most significant bit determines the register to be used (High/Low), while the other five bits determine the bit within the register. A value of 00000 selects Bit 0 of the multicast hash table low register and a value of 11111 selects Bit 31 of the multicast hash table high register.

#### 3.4.2.1 Hash Perfect Filtering

In hash perfect filtering, if the received frame is a physical address, the LAN9116 Packet Filter block perfect-filters the incoming frame's destination field with the value programmed into the MAC Address High register and the MAC Address Low register. If the incoming frame is a multicast frame, however, the LAN9116 packet filter function performs an imperfect address filtering against the hash table.

The imperfect filtering against the hash table is the same imperfect filtering process described in the "Hash Only Filtering" section above.

#### 3.4.2.2 Inverse Filtering

In inverse filtering, the LAN9116 Packet Filter Block accepts incoming frames with a destination address not matching the perfect address (i.e., the value programmed into the MAC Address High register and the MAC Address Low register in the CRC block and rejects frames with destination addresses matching the perfect address.

For all filtering modes, when MCPAS is set, all multicast frames are accepted. When the PRMS bit is set, all frames are accepted regardless of their destination address. This includes all broadcast frames as well.

#### 3.5 Wake-up Frame Detection

Setting the Wake-Up Frame Enable bit (WUEN) in the "WUCSR—Wake-up Control and Status Register", places the LAN9116 MAC in the wake-up frame detection mode. In this mode, normal data reception is disabled, and detection logic within the MAC examines receive data for the pre-programmed wake-up frame patterns. The LAN9116 can be programmed to notify the host of the wake-up frame detection with the assertion of the host interrupt (IRQ) or assertion of the power management event signal (PME). Upon detection, the Wake-Up Frame Received bit (WUFR) in the WUCSR is set. When the host clears the WUEN bit the LAN9116 will resume normal receive operation.

Before putting the MAC into the wake-up frame detection state, the host must provide the detection logic with a list of sample frames and their corresponding byte masks. This information is written into the Wake-up Frame Filter register (WUFF). Please refer to Section 5.4.11, "WUFF—Wake-up Frame Filter," on page 82 for additional information on this register.

The MAC supports four programmable filters that support many different receive packet patterns. If remote wake-up mode is enabled, the remote wake-up function receives all frames addressed to the MAC. It then checks each frame against the enabled filter and recognizes the frame as a remote wake-up frame if it passes the wakeup frame filter register's address filtering and CRC value match.

In order to determine which bytes of the frames should be checked by the CRC module, the MAC uses a programmable byte mask and a programmable pattern offset for each of the four supported filters.

The pattern's offset defines the location of the first byte that should be checked in the frame. Since the destination address is checked by the address filtering Function, the pattern offset is always greater than 12.

The byte mask is a 31-bit field that specifies whether or not each of the 31 contiguous bytes within the frame, beginning in the pattern offset, should be checked. If bit j in the byte mask is set, the detection logic checks byte offset +j in the frame. In order to load the Wake-up Frame Filter register, the host LAN driver software must perform eight writes to the Wake-up Frame Filter register (WUFF). The Diagram shown in Table 3-2, "Wake-Up Frame Filter Register Structure" below, shows the wake-up frame filter register's structure.

- **Note 3-1** Wake-up frame detection can be performed when LAN9116 is in the D0 or D1 power states. In the D0 state, wake-up frame detection is enabled when the WUEN bit is set.

- **Note 3-2** Wake-up frame detection, as well as Magic Packet detection, is always enabled and cannot be disabled when the device enters the D1 state.

- **Note 3-3** When wake-up frame detection is enabled via the WUEN bit of the WUCSR—Wake-up Control and Status Register, a broadcast wake-up frame will wake-up the device despite the state of the Disable Broadcast Frames (BCAST) bit in the MAC\_CR—MAC Control Register.

#### TABLE 3-2: WAKE-UP FRAME FILTER REGISTER STRUCTURE

|                                 | Filter 0 Byte Mask                          |  |                                |                 |                     |          |                     |  |

|---------------------------------|---------------------------------------------|--|--------------------------------|-----------------|---------------------|----------|---------------------|--|

|                                 | Filter 1 Byte Mask                          |  |                                |                 |                     |          |                     |  |

|                                 | Filter 2 Byte Mask                          |  |                                |                 |                     |          |                     |  |

| Filter 3 E                      |                                             |  |                                | yte Mask        |                     |          |                     |  |

| Reserved                        | Reserved Filter 3 Reserved Filter 2 Command |  |                                |                 | Filter 1<br>Command | Reserved | Filter 0<br>Command |  |

| Filter 3 Offset Filter 2 Offset |                                             |  | Filter 10ffset Filter 0 Offset |                 |                     |          |                     |  |

| Filter 1 CRC-16                 |                                             |  |                                | Filter 0 CRC-16 |                     |          |                     |  |

| Filter 3 CRC-16                 |                                             |  |                                | Filter 2 CRC-16 |                     |          |                     |  |

The Filter i Byte Mask defines which incoming frame bytes Filter i will examine to determine whether or not this is a wake-up frame. Table 3-3, describes the byte mask's bit fields.

#### TABLE 3-3:FILTER I BYTE MASK BIT DEFINITIONS

|       | Filter i Byte Mask Description                                                                                                                                                             |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Field | Description                                                                                                                                                                                |  |  |  |  |  |

| 31    | Must be zero (0)                                                                                                                                                                           |  |  |  |  |  |

| 30:0  | <b>Byte Mask:</b> If bit j of the byte mask is set, the CRC machine processes byte number pattern - (offset + j) of the incoming frame. Otherwise, byte pattern - (offset + j) is ignored. |  |  |  |  |  |

The Filter i command register controls Filter i operation. Table 3-4 shows the Filter I command register.

#### TABLE 3-4: FILTER I COMMAND BIT DEFINITIONS

|       | Filter i Commands                                                                                                                                                                                  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Field | Description                                                                                                                                                                                        |  |  |  |  |  |  |

| 3     | Address Type: Defines the destination address type of the pattern. When bit is set, the pattern applies only to multicast frames. When bit is cleared, the pattern applies only to unicast frames. |  |  |  |  |  |  |

| 2:1   | RESERVED                                                                                                                                                                                           |  |  |  |  |  |  |

| 0     | Enable Filter: When bit is set, Filter i is enabled, otherwise, Filter i is disabled.                                                                                                              |  |  |  |  |  |  |

The Filter i Offset register defines the offset in the frame's destination address field from which the frames are examined by Filter i. Table 3-5 describes the Filter i Offset bit fields.

#### TABLE 3-5: FILTER I OFFSET BIT DEFINITIONS

|       | Filter i Offset Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 7:0   | <b>Pattern Offset:</b> The offset of the first byte in the frame on which CRC is checked for wake-up frame recognition. The minimum value of this field must be 12 since there should be no CRC check for the destination address and the source address fields. The MAC checks the first offset byte of the frame for CRC and checks to determine whether the frame is a wake-up frame. Offset 0 is the first byte of the incoming frame's destination address. |  |  |  |  |  |  |

The Filter i CRC-16 register contains the CRC-16 result of the frame that should pass Filter i.

Table 3-6 describes the Filter i CRC-16 bit fields.

#### TABLE 3-6:FILTER I CRC-16 BIT DEFINITIONS

|       | Filter i CRC-16 Description                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Field | Description                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 15:0  | <b>Pattern CRC-16:</b> This field contains the 16-bit CRC value from the pattern and the byte mask programmed to the wake-up filter register Function. This value is compared against the CRC calculated on the incoming frame, and a match indicates the reception of a wakeup frame. |  |  |  |  |  |

#### 3.5.1 MAGIC PACKET DETECTION

Setting the Magic Packet Enable bit (MPEN) in the "WUCSR—Wake-up Control and Status Register", places the LAN9116 MAC in the "Magic Packet" detection mode. In this mode, normal data reception is disabled, and detection logic within the MAC examines receive data for a Magic Packet. The LAN9116 can be programmed to notify the host of the "Magic Packet" detection with the assertion of the host interrupt (IRQ) or assertion of the power management event signal (PME). Upon detection, the Magic Packet Received bit (MPR) in the WUCSR is set. When the host clears the MPEN bit the LAN9116 will resume normal receive operation. Please refer to Section 5.4.12, "WUCSR—Wake-up Control and Status Register," on page 82 for additional information on this register.

In Magic Packet mode, the Power Management Logic constantly monitors each frame addressed to the node for a specific Magic Packet pattern. It checks only packets with the MAC's address or a broadcast address to meet the Magic Packet requirement. The Power Management Logic checks each received frame for the pattern 48h FF\_FF\_FF\_FF\_FF\_FF\_FF\_FF after the destination and source address field. The 16 repetitions may be anywhere in the frame but must be preceded by the synchronization stream. The device will also accept a multicast frame, as long as it detects the 16 duplications of the MAC address. If the MAC address of a node is 00h 11h 22h 33h 44h 55h, then the MAC scans for the following data sequence in an Ethernet: Frame.

Destination Address Source Address ......FF FF FF FF FF FF FF 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 22 33 44 55 00 11 20 10 10 10 10 1

...CRC

It should be noted that Magic Packet detection can be performed when LAN9116 is in the D0 or D1 power states. In the D0 state, "Magic Packet" detection is enabled when the MPEN bit is set. In the D1 state, Magic Packet detection, as well as wake-up frame detection, are automatically enabled when the device enters the D1 state.

### 3.6 32-bit vs. 16-bit Host Bus Width Operation

The LAN9116 can be configured to communicate with the host bus via either a 32-bit or a 16-bit bus. An external strap is used to select between the two modes. 32-bit mode is the native environment for the LAN9116 Ethernet controller and no special requirements exist for communication in this mode. However, when this part is used in the 16-bit mode, two writes or reads must be performed back to back to properly communicate.

The bus width is set by strapping the EEDIO pin; this setting can be read from bit 2 of the "Hardware Configuration Register". Please refer to Section 5.3.9, "HW\_CFG—Hardware Configuration Register," on page 61 for additional information on this register.

#### 3.6.1 16-BIT BUS WRITES

The host processor is required to perform two contiguous 16-bit writes to complete a single DWORD transfer. This DWORD must begin and end on a DWORD address boundary (A[2] and higher, cannot change during a sixteen bit write). No ordering requirements exist. The processor can access either the low or high word first, as long as the next write is performed to the other word. If a write to the same word is performed, the LAN9116 disregards the transfer.

#### 3.6.2 16-BIT BUS READS

The host processor is required to perform two consecutive 16-bit reads to complete a single DWORD transfer. This DWORD must begin and end on a DWORD address boundary (A[2] and higher, cannot change during a sixteen bit read). No ordering requirements exist. The processor can access either the low or high word first, as long as the next read is performed from the other word. If a read to the same word is performed, the data read is invalid and should be re-read. This is not a fatal error. The LAN9116 will reset its read counters and restart a new cycle on the next read. The Upper 16 data pins (D[31:16]) are not driven by the LAN9116 in 16-bit mode. These pins have internal pull-down's and the signals are left in a high-impedance state.

#### 3.7 Big and Little Endian Support

The Microchip LAN9116 supports "Big-" or "Little-Endian" processors in either 16 or 32-bit bus width modes. To support big-endian processors, the hardware designer must explicitly invert the layout of the byte lanes. In addition, for a 16-bit interface, the WORD\_SWAP—Word Swap Control must be set correctly following Table 3-7, "Byte Lane Mapping".

The host bus interface can be selected via an external strap to translate the data bus into either mode. Please refer to Table 2-4, "Serial EEPROM Interface Signals," on page 10, for information on multiplexed signal D32/nD16 for more information on data bus width selection.

Additionally, please refer to Section 5.3.17, "WORD\_SWAP—Word Swap Control," on page 68 for additional information on status indication on Endian modes.

| Made of Operation | Data Pins                                                  |          |         |                 | Description |                                                                                       |  |  |  |

|-------------------|------------------------------------------------------------|----------|---------|-----------------|-------------|---------------------------------------------------------------------------------------|--|--|--|

| Mode of Operation | D[31:24]                                                   | D[23:16] | D[15:8] | D[7:0]          | -           | Description                                                                           |  |  |  |

| 32-bit            | Byte 3<br>(MSB)                                            | Byte 2   | Byte 1  | Byte 0<br>(LSB) | Endianes    | e native mode of the LAN9116.<br>s does not matter when both<br>nes are in operation. |  |  |  |

| Mode 0 (WORD_SW   | Mode 0 (WORD_SWAP—Word Swap Control equal to FFFFFFFh)     |          |         |                 |             |                                                                                       |  |  |  |

| A1 = 0            | A1 = 0 Byte 3 Byte                                         |          |         |                 |             | This mode can be used by 32-                                                          |  |  |  |

| A1 = 1            |                                                            |          | Byte 1  | Byte 0          |             | bit processors operating with an external 16-bit bus.                                 |  |  |  |

| Mode 1 (WORD_SW   | Mode 1 (WORD_SWAP—Word Swap Control not equal to FFFFFFFh) |          |         |                 |             |                                                                                       |  |  |  |

| A1 = 0            |                                                            |          | Byte 1  | Byte 0          | Note:       | This mode can also be used by                                                         |  |  |  |

| A1 = 1            |                                                            |          | Byte 3  | Byte 2          |             | native 16-bit processors.                                                             |  |  |  |

#### TABLE 3-7:BYTE LANE MAPPING

Regarding the 32-bit mode description of operation comment described in the table above, mentioning "It should be noted that Endianess does not matter when both WORD lanes are in operation" is true for the LAN9116 device. However, as in all designs, it is important for the PCB layout designer to route the signal byte lanes appropriately relative to the processor type (Big vs. Little Endian).

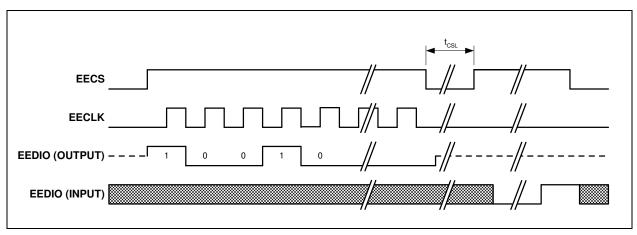

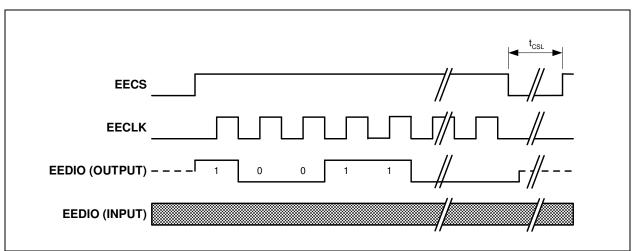

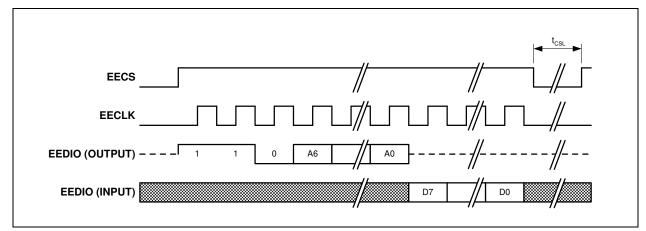

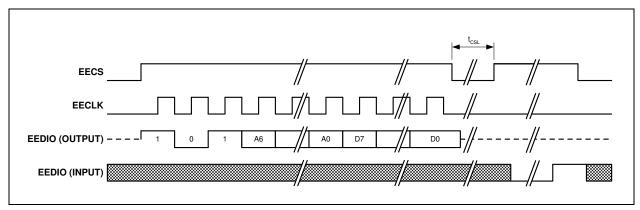

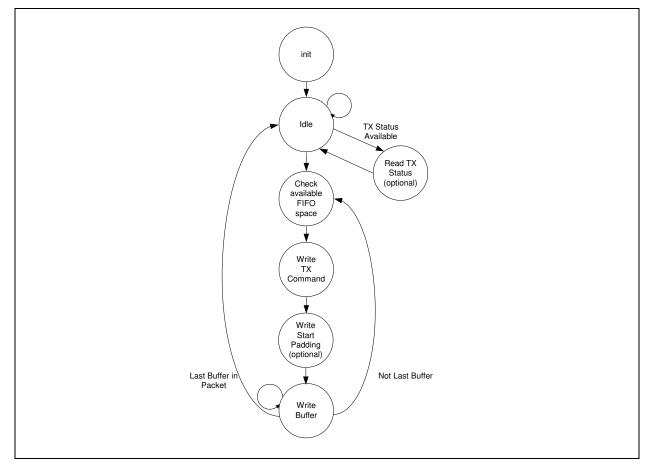

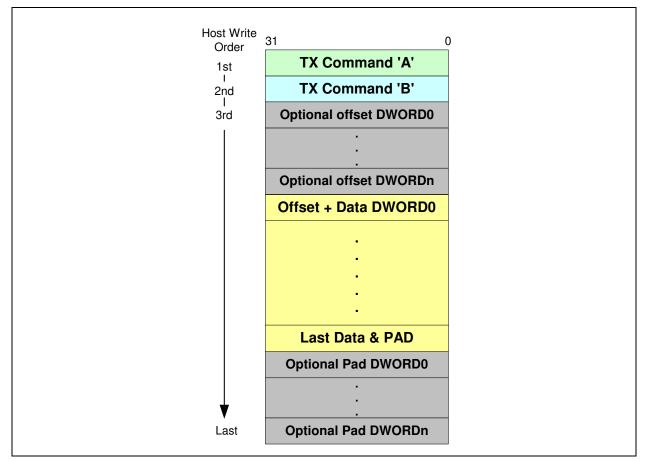

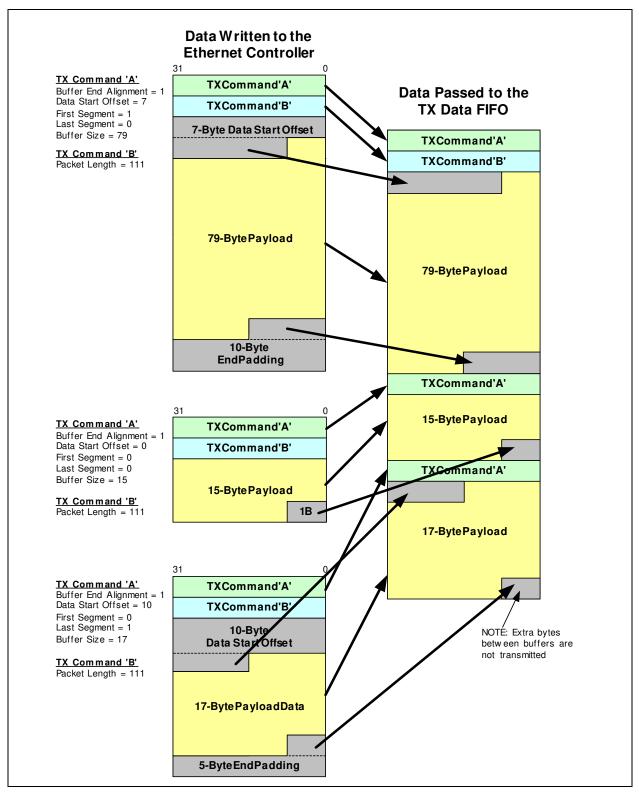

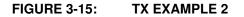

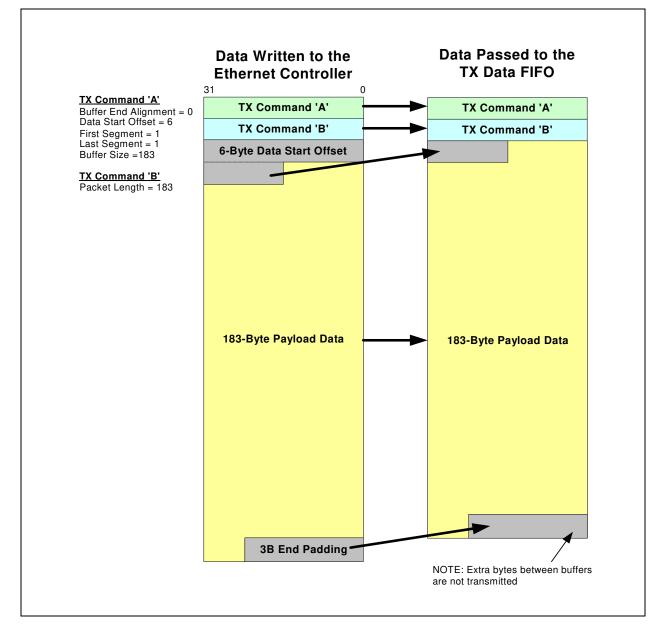

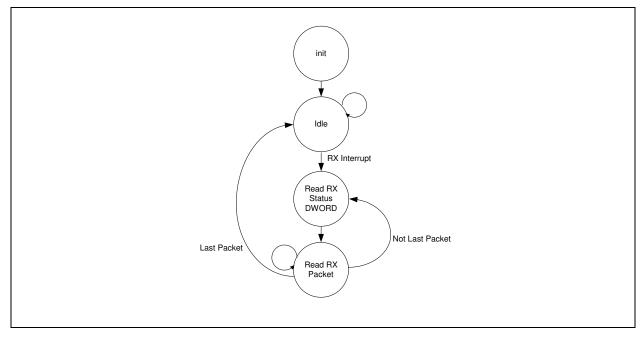

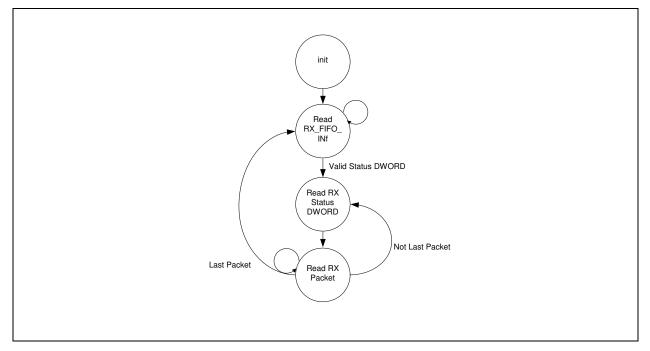

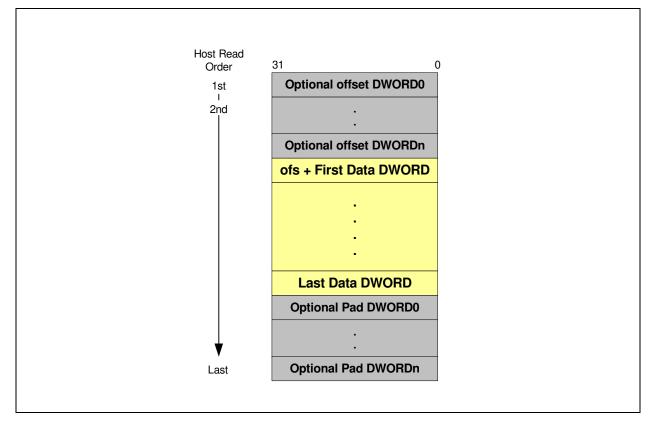

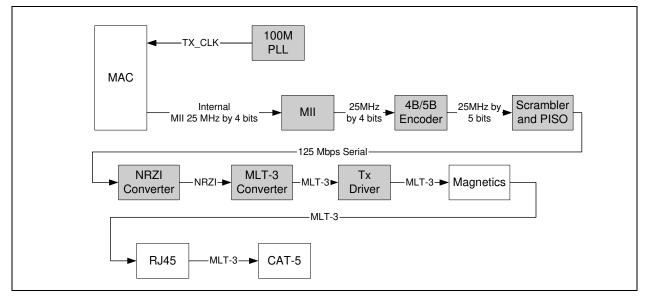

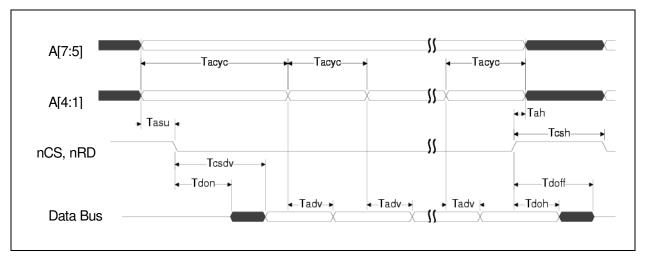

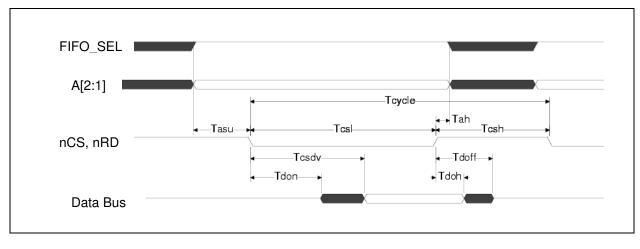

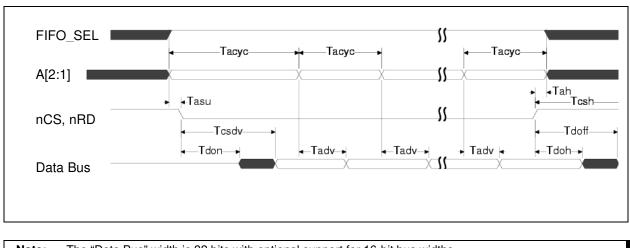

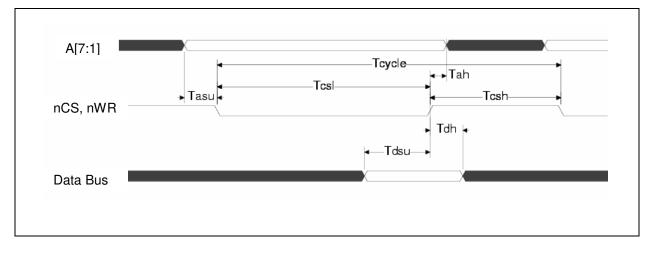

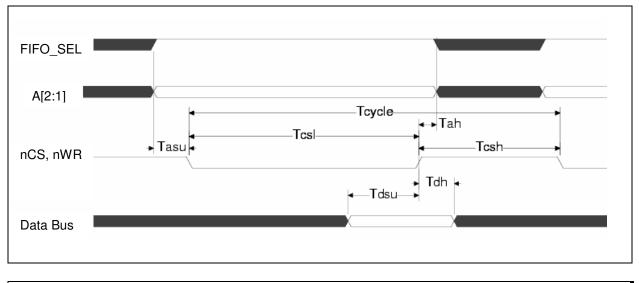

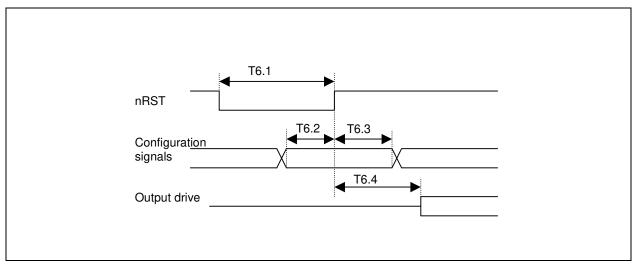

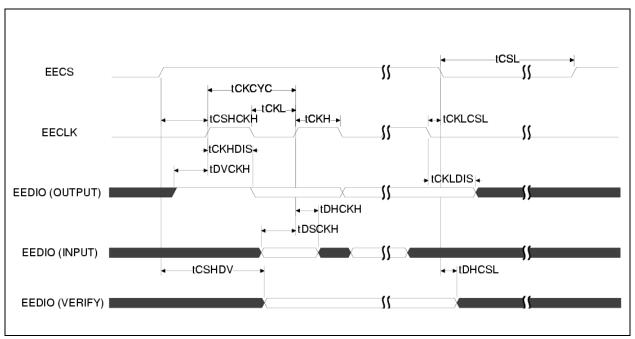

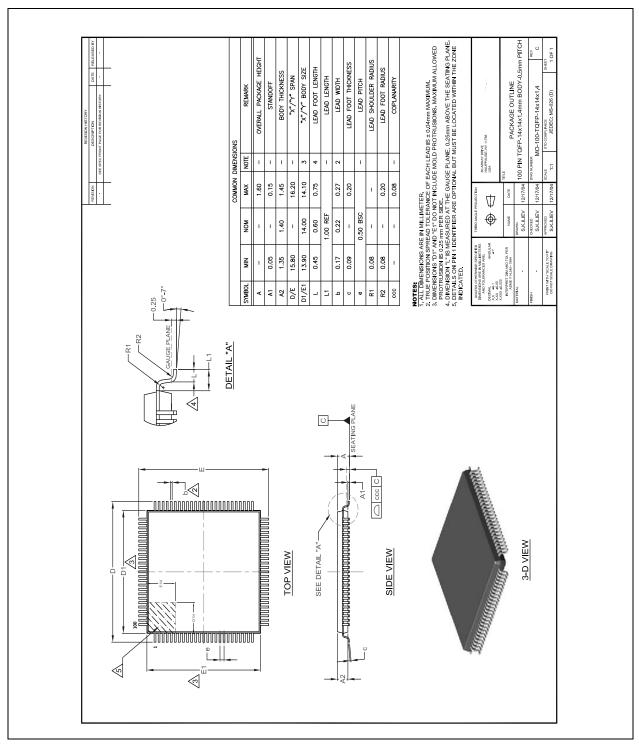

### 3.8 General Purpose Timer (GP Timer)