# **General Description**

The BDE-WF3235 module, is a 802.11abgn, IPv4 & IPv6 Low Energy module based on CC3235SF SoC.

The module offers a unique combination of lower power, integration of all external components including dual band chip antenna at a very affordable cost.

Created for IoT, the BDE-WF3235 module is a wireless module that integrates two physically separated on-chip MCUs, application processor and network processor. The BDE-WF3235 module is supported by easy to work with software to lower the threshold of using Wi-Fi technology or speeding up design time significantly. The combination of affordable cost, lowest power and ease of use makes it an ideal product for the mass market, including the makers community.

# **Key Features**

- Fully integrated and green and RoHS modules include all required clocks, SPI flash, and passives

- 802.11a/b/g/n: 2.4 GHz and 5 GHz

- FIPS 140-2 Level 1 validated IC inside

- Multilayered security features help developers protect identities, data, and software IP

- Low-power modes for battery-powered applications

- Coexistence with 2.4-GHz radios

- Industrial temperature: -40°C to +85°C

- BDE-WF3235 module includes a chip antenna for easy integration into the host system

- 1.27-mm pitch QFM package for easy assembly and low-cost PCB design

- Transferrable Wi-Fi Alliance® certification

- Application microcontroller subsystem:

- > Arm® Cortex®-M4 core at 80 MHz

- User-dedicated memory:

- 256KB of RAM

- Optional 1MB of executable flash

- > Rich set of peripherals and timers:

- McASP supports two I2S channels

- SD, SPI, I2C, UART

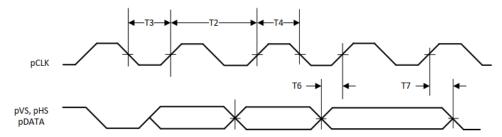

- 8-bit synchronous imager interface

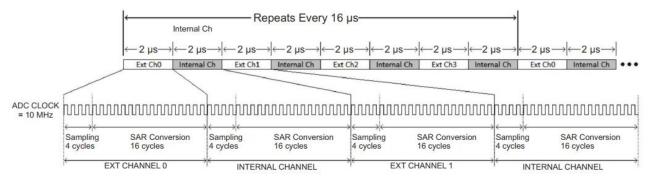

- 4-channel 12-bit ADCs

- 4 general-purpose timers (GPT) with 16-bit PWM mode

- · Watchdog timer

- Up to 27 GPIO pins

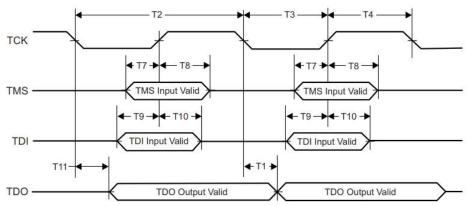

- Debug interfaces: JTAG, cJTAG, SWD

- Wi-Fi network processor subsystem:

- ➤ Wi-Fi® core:

- 802.11 a/b/g/n 2.4 GHz and 5 GHz

- Modes:

- Access point (AP)

- Station (STA)

- Wi-Fi Direct® (only supported on 2.4GHz)

- Security:

- WEP

- WPA™/ WPA2™ PSK

- WPA2 Enterprise

- WPA3™ Personal

- Internet and application protocols:

- HTTPs server, mDNS, DNS-SD, DHCP

- IPv4 and IPv6 TCP/IP stack

- 16 BSD sockets (fully secured TLS v1.2 and SSL 3.0)

- > Built-in power management subsystem:

- Configurable low-power profiles (always on, intermittently connected, tag)

- Advanced low-power modes

- Integrated DC/DC regulators

- Multilayered security features:

- > Separate execution environments

- Networking security

- Device identity and key

- Hardware accelerator cryptographic engines(AES, DES, SHA/MD5, CRC)

- File system security (encryption, authentication, access control)

- ➤ Initial secure programming

- > Software tamper detection

- > Secure boot

- Certificate signing request (CSR)

- Unique per device key pair

- Application throughput

- UDP: 16 Mbps

- > TCP: 13 Mbps

- Power-Management Subsystem:

### BDE-WF3235SN

# TEXAS INSTRUMENTS Partner

Wi-Fi Dual-Band Module Datasheet

- ➤ Integrated DC/DC converters support a wide range of supply voltage:

- Single wide-voltage supply VBAT: 2.3 V to 3.6 V

- > Advanced low-power modes:

- Shutdown: 1 μA, Hibernate: 5.5 μA

- Low-power deep sleep (LPDS):

120 μA

- Idle connected (MCU in LPDS): 710 μA

- RX traffic (MCU active): 59 mA

- TX traffic (MCU active): 223 mA

- ➤ Wi-Fi TX power

- 2.4 GHz: 16 dBm at 1 DSSS

- 5 GHz: 15.1 dBm at 6 OFDM

- ➤ Wi-Fi RX sensitivity

- 2.4 GHz: -94.5 dBm at 1 DSSS

- 5 GHz: -89 dBm at 6 OFDM

- Additional integrated components

- > 40.0-MHz crystal

- > 32.768-kHz crystal (RTC)

- > 32Mbit SPI serial flash

- > RF filters, diplexer and passive components

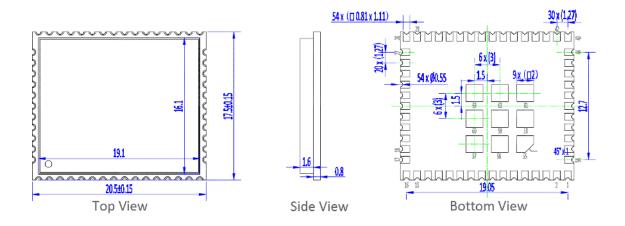

- Footprint-compatible QFM package

- > 1.27-mm pitch, 63-pin, 20.5mm × 17.5mm

- Module supports the TI SimpleLink Developer's Ecosystem

# **Applications**

- For Internet of Things applications, such as:

- > Medical and Healthcare

- Multiparameter Patient Monitor

- Electrocardiogram (ECG)

- Electronic Hospital Bed & Bed Control

- Telehealth Systems

- Building and Home Automation:

- HVAC Systems & Thermostat

- Video Surveillance, Video Doorbells, and Low-Power Camera

- Building Security Systems and E-locks

- Appliances

- Asset Tracking

- > Factory Automation

- Grid Infrastructure

TEXAS INSTRUMENTS Partner

Wi-Fi Dual-Band Module Datasheet

# **Device Family**

### Table 0-1. BDE-WF3235 Device Family

| Part Number          | Core Chip | Description                                                          | Size (mm)         | Package |

|----------------------|-----------|----------------------------------------------------------------------|-------------------|---------|

| BDE-<br>WF3235SA32   | CC3235S   | With 32Mbit external flash, with chip antenna                        | 20.5 × 23 × 2.4   | SMD-63  |

| BDE-<br>WF3235SAU32  | CC3235S   | With 32Mbit external flash, with U.FL connector for external antenna | 20.5 × 23 × 2.4   | SMD-63  |

| BDE-<br>WF3235SN32   | CC3235S   | With 32Mbit external flash, without antenna                          | 20.5 × 17.5 × 2.4 | SMD-63  |

| BDE-<br>WF3235SFA0   | CC3235SF  | Without external flash, with chip antenna                            | 20.5 × 23 × 2.4   | SMD-63  |

| BDE-<br>WF3235SFAU0  | CC3235SF  | Without external flash, with U.FL connector for external antenna     | 20.5 × 23 × 2.4   | SMD-63  |

| BDE-<br>WF3235SFA32  | CC3235SF  | With 32Mbit external flash, with chip antenna                        | 20.5 × 23 × 2.4   | SMD-63  |

| BDE-<br>WF3235SFAU32 | CC3235SF  | With 32Mbit external flash, with U.FL connector for external antenna | 20.5 × 23 × 2.4   | SMD-63  |

| BDE-<br>WF3235SFN0   | CC3235SF  | Without external flash, without antenna                              | 20.5 × 17.5 × 2.4 | SMD-63  |

| BDE-<br>WF3235SFN32  | CC3235SF  | With 32Mbit external flash, without antenna                          | 20.5 × 17.5 × 2.4 | SMD-63  |

# BDE TEXAS INSTRUMENTS Partner

Datasheet

# Wi-Fi Dual-Band Module

# **Contents**

| Ger | neral Description                                                            | 1  |

|-----|------------------------------------------------------------------------------|----|

| Key | Features                                                                     | 1  |

| App | plications                                                                   | 2  |

| Dev | rice Family                                                                  | 3  |

| Con | ntents                                                                       | 4  |

| 1.  | References                                                                   | 6  |

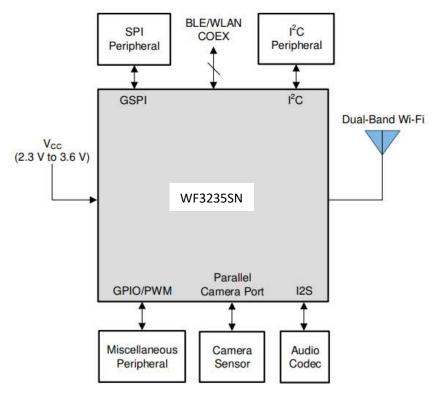

| 2.  | Block Diagram                                                                | 7  |

| 3.  | Terminal Configuration and Functions                                         | 8  |

|     | 3.1 Pin Diagram                                                              | 8  |

|     | 3.2 Pin Attributes and Pin Multiplexing                                      | 8  |

|     | 3.3 Signal Descriptions                                                      | 24 |

|     | 3.4 Drive Strength and Reset States for Analog-Digital Multiplexed Pins      | 29 |

|     | 3.5 Pad State After Application of Power to Chip, but Before Reset Release   |    |

|     | 3.6 Connections for Unused Pins                                              | 30 |

| 4.  | Specifications                                                               | 31 |

|     | 4.1 Absolute Maximum Ratings                                                 | 31 |

|     | 4.2 ESD Ratings                                                              | 32 |

|     | 4.3 Recommended Operating Conditions                                         | 32 |

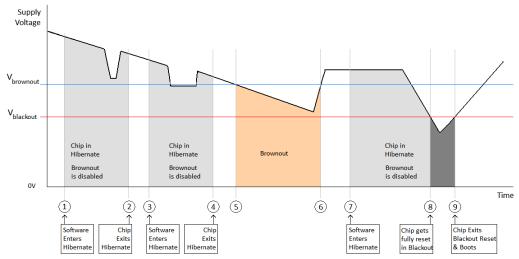

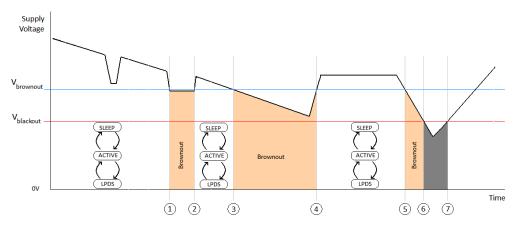

|     | 4.4 Brownout and Blackout Conditions                                         | 33 |

|     | 4.5 Electrical Characteristics for GPIO Pins                                 |    |

|     | 4.5.1 Electrical Characteristics for Pin Internal Pullup and Pulldown (25°C) |    |

|     | 4.6 BLE and WLAN Coexistence Requirements                                    |    |

|     | 4.7 Reset Requirement                                                        |    |

|     | 4.8Timing and Switching Characteristics                                      | 37 |

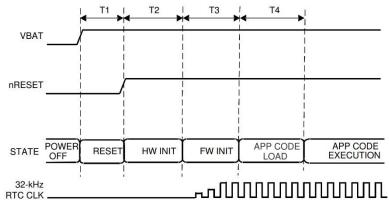

|     | 4.8.1 Power-Up Sequencing                                                    |    |

|     | 4.8.2 Power-Down Sequencing                                                  |    |

|     | 4.8.3 Device Reset                                                           |    |

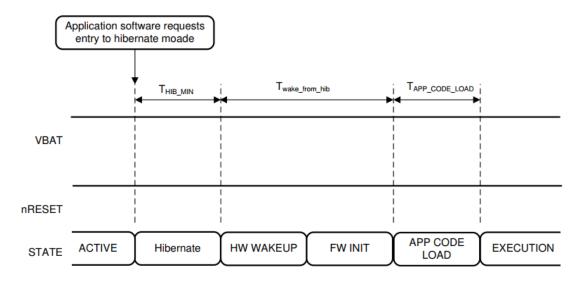

|     | 4.8.4 Wake Up From Hibernate Timing                                          | 39 |

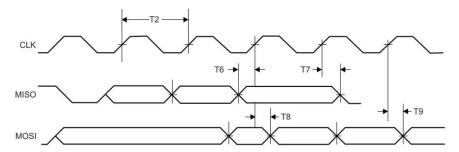

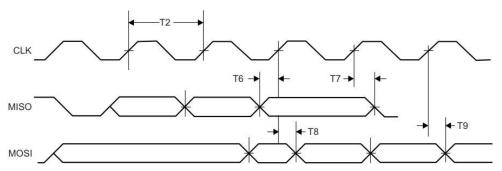

|     | 4.8.5 Peripherals Timing                                                     |    |

| 5.  | Detailed Description                                                         |    |

|     | 5.1 Overview                                                                 |    |

|     | 5.2 Functional Block Diagram                                                 | 51 |

|     | 5.3 Arm Cortex-M4 Processor Core Subsystem                                   | 52 |

|     | 5.4 Wi-Fi Network Processor Subsystem                                        | 53 |

|     | 5.4.1 WLAN                                                                   |    |

|     | 5.4.2 Network Stack                                                          | 53 |

|     | 5.5 Security                                                                 |    |

|     | 5.6 Power-Management Subsystem                                               |    |

|     | 5.6.1 VBAT Wide-Voltage Connection                                           |    |

|     | 5.7 Low-Power Operating Mode                                                 |    |

|     | 5.8 Memory                                                                   | 60 |

|     | 5.8.1 Internal Memory                                                        |    |

|     | 5.9 Restoring Factory Default Configuration                                  |    |

|     | 5.10 Boot Modes                                                              |    |

|     | 5.11 Hostless Mode                                                           |    |

| 6.  | Applications, Implementation, and Layout                                     |    |

|     | 6.1 Typical Application                                                      |    |

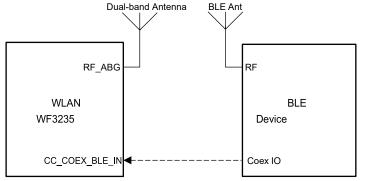

|     | 6.1.1 BLE/2.4 GHz Radio Coexistence                                          |    |

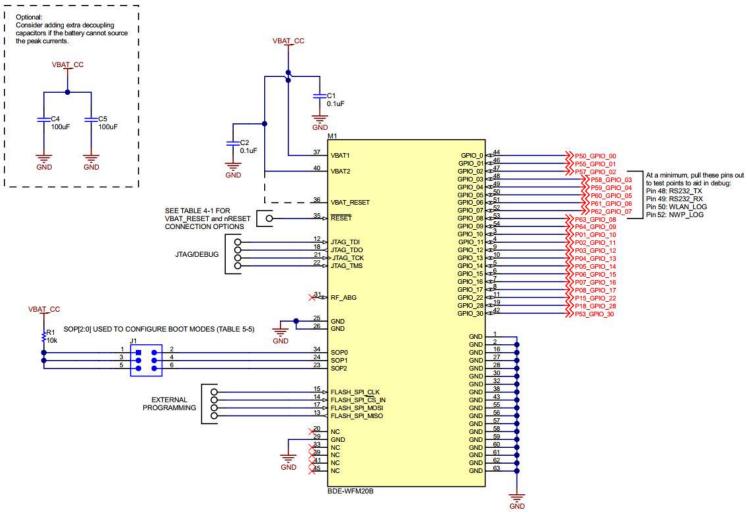

|     | 6.1.2 Typical Application Schematic                                          |    |

|     | 6.2 Device Connection and Layout Fundamentals                                |    |

|     | •                                                                            |    |

# BDE-WF3235SN

| Wi | -Fi Dual-Band Module                              | Datasheet |

|----|---------------------------------------------------|-----------|

|    | 6.2.1 Power Supply Decoupling and Bulk Capacitors | 68        |

|    | 6.2.2 Reset                                       |           |

|    | 6.2.3 Unused Pins                                 | 68        |

|    | 6.3 PCB Layout Guidelines                         | 68        |

| 7. | Mechanical Specifications                         | 70        |

|    | 7.1 Dimensions                                    | 70        |

| 8. | Ordering Information                              | 71        |

| 9. | Revision History                                  | 71        |

# 1. References

[1] CC3235S resources: https://www.ti.com/product/CC3235S

[2] CC3235SF resources: https://www.ti.com/product/CC3235SF

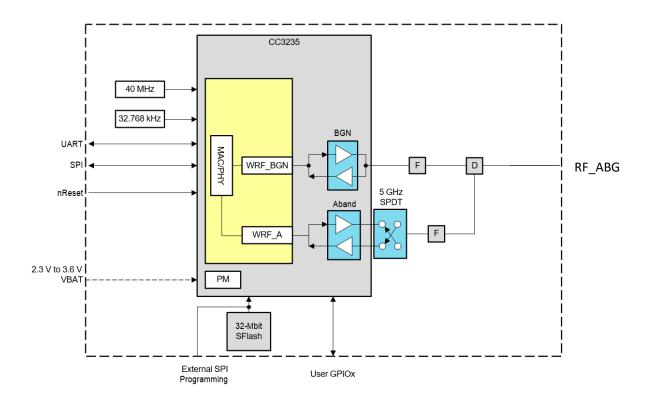

# 2. Block Diagram

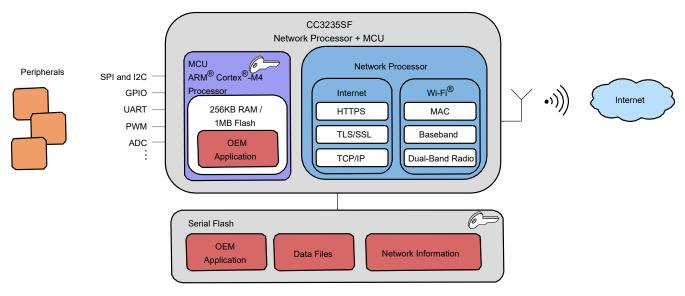

BDE-WF3235 module is based on the TI Instruments CC3235SF SoC. With an integrated 32Mbit flash, 40MHz XTAL and a dual band chip antenna, it allows faster time to market at reduced development cost.

The module, as seen in Figure 1, comprises of:

- 32 Mbit SPI Flash

- 40MHz XTAL

- 32.768kHz XTAL

- 2 filters

- a SPDT

- a diplexer

- a dual band chip antenna

Figure 2-1. BDE-WF3235 Module Block Diagram

TEXAS INSTRUMENTS

Partner

Wi-Fi Dual-Band Module Datasheet

# 3. Terminal Configuration and Functions

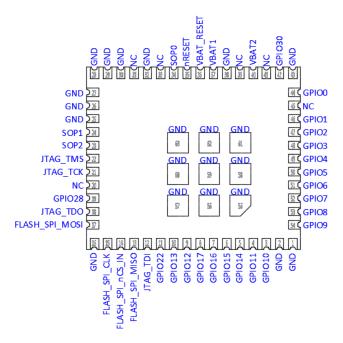

# 3.1 Pin Diagram

Figure 3-1. Pin Diagram Bottom View

# 3.2 Pin Attributes and Pin Multiplexing

Table 3-1. Pin Description

| Pin# | Pin Name | Type <sup>(1)</sup> | Description                                                             |

|------|----------|---------------------|-------------------------------------------------------------------------|

| 1    | GND      | 1                   | Ground                                                                  |

| 2    | GND      | -                   | Ground                                                                  |

| 3    | GPIO10   | I/O                 | GPIO                                                                    |

| 4    | GPIO11   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 5    | GPIO14   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 6    | GPIO15   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 7    | GPIO16   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 8    | GPIO17   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 9    | GPIO12   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 10   | GPIO13   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 11   | GPIO22   | I/O                 | GPIO <sup>(2)</sup>                                                     |

| 12   | JTAG_TDI | I/O                 | JTAG TDI input. Leave unconnected if not used on product <sup>(2)</sup> |

| Pin# | Pin Name         | Type <sup>(1)</sup> | Description                                                     |  |  |  |  |

|------|------------------|---------------------|-----------------------------------------------------------------|--|--|--|--|

| 13   | FLASH_SPI_MISO   | I                   | External serial flash programming: SPI data in                  |  |  |  |  |

| 14   | FLASH_SPI_nCS_IN | I                   | External serial flash programming: SPI chip select (active low) |  |  |  |  |

| 15   | FLASH_SPI_CLK    | I                   | External serial flash programming: SPI clock                    |  |  |  |  |

| 16   | GND              | _                   | Ground                                                          |  |  |  |  |

# Wi-Fi Dual-Band Module

Datasheet

| al-Dalia Module | 1                                                                                                                                                                     | Datasiic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLASH_SPI_MOSI  | 0                                                                                                                                                                     | External serial flash programming: SPI data out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| JTAG_TDO        | I/O                                                                                                                                                                   | JTAG TDO output. Leave unconnected if not used on product <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO28          | I/O                                                                                                                                                                   | GPIO <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NC              | -                                                                                                                                                                     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| JTAG_TCK        | I/O                                                                                                                                                                   | JTAG TCK input. Leave unconnected if not used on product. (2) An intern $100-k\Omega$ pulldown resistor is tied to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| JTAG_TMS        | I/O                                                                                                                                                                   | JTAG TMS input. Leave unconnected if not used on product. (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SOP2            | _                                                                                                                                                                     | An internal 100-k $\Omega$ pulldown resistor is tied to this SOP pin. An external 10-k resistor is required to pull this pin high. See Section 5.11 for SOP[2: configuration modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SOP1            | _                                                                                                                                                                     | An internal 100-k $\Omega$ pulldown resistor is tied to this SOP pin. An external 10-k resistor is required to pull this pin high. See Section 5.11 for SOP[2: configuration modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND             | _                                                                                                                                                                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC              | _                                                                                                                                                                     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND             | _                                                                                                                                                                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC              | _                                                                                                                                                                     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SOP0            | -                                                                                                                                                                     | An internal 100-k $\Omega$ pulldown resistor is tied to this SOP pin. An external 10-k resistor is required to pull this pin high. See Section 5.11 for SOP[2: configuration modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| nRESET          | I                                                                                                                                                                     | There is an internal, 100-kΩ pullup resistor option from the nRESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VBAT_RESET      | -                                                                                                                                                                     | <ul> <li>pin to VBAT_RESET. Note: VBAT_RESET is not connected to VBAT1 or VBAT2 within the module. The following connection schemes are recommended:</li> <li>Connect nRESET to a switch, external controller, or host, only if nRESET will be in a defined state under all operating conditions. Leave VBAT_RESET unconnected to save power.</li> <li>If nRESET cannot be in a defined state under all operating condition connect VBAT_RESET to the main module power supply (VBAT1 ar VBAT2). Due to the internal pullup resistor a leakage current of 3.3 V 100 kΩ is expected.</li> </ul>                                                   |

| VBAT1           | Power                                                                                                                                                                 | Power supply for the module, must be connected to battery (2.3 V to 3.6 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND             | _                                                                                                                                                                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC              | _                                                                                                                                                                     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VBAT2           | Power                                                                                                                                                                 | Power supply for the module, must be connected to battery (2.3 V to 3.6 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC              | -                                                                                                                                                                     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIO30          | I/O                                                                                                                                                                   | GPIO <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND             | _                                                                                                                                                                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | FLASH_SPI_MOSI  JTAG_TDO  GPIO28  NC  JTAG_TCK  JTAG_TMS  SOP2  SOP1  GND  GND  GND  GND  GND  GND  GND  NC  GND  NC  SOP0  nRESET  VBAT1  GND  NC  VBAT2  NC  GPIO30 | FLASH_SPI_MOSI         O           JTAG_TDO         I/O           RPIO28         I/O           NC         -           JTAG_TCK         I/O           JTAG_TMS         I/O           SOP2         -           SOP2         -           SOP1         -           GND         -           GND         -           GND         -           GND         -           GND         -           NC         -           SOP0         -           NC         -           NC         -           VBAT_RESET         I           VBAT1         Power           NC         -           VBAT2         Power           NC         -           GPIO30         I/O |

| Pin# | Pin Name | Type <sup>(1)</sup> | Description         |

|------|----------|---------------------|---------------------|

| 44   | GPIO0    | I/O                 | GPIO <sup>(2)</sup> |

| 45   | NC       | 1                   | No Connect          |

| 46   | GPIO1    | I/O                 | GPIO <sup>(2)</sup> |

| 47   | GPIO2    | I/O                 | GPIO <sup>(2)</sup> |

### BDE-WF3235SN

| Wi-Fi Dua | al-Band Module |     | Datasheet           |

|-----------|----------------|-----|---------------------|

| 48        | GPIO3          | I/O | GPIO <sup>(2)</sup> |

| 49        | GPIO4          | I/O | GPIO <sup>(2)</sup> |

| 50        | GPIO5          | I/O | GPIO <sup>(2)</sup> |

| 51        | GPIO6          | I/O | GPIO <sup>(2)</sup> |

| 52        | GPIO7          | I/O | GPIO <sup>(2)</sup> |

| 53        | GPIO8          | I/O | GPIO <sup>(2)</sup> |

| 54        | GPIO9          | I/O | GPIO <sup>(2)</sup> |

| 55        | GND            | -   | Thermal ground      |

| 56        | GND            | -   | Thermal ground      |

| 57        | GND            | -   | Thermal ground      |

| 58        | GND            | -   | Thermal ground      |

| 59        | GND            | -   | Thermal ground      |

| 60        | GND            | -   | Thermal ground      |

| 61        | GND            | -   | Thermal ground      |

| 62        | GND            | -   | Thermal ground      |

| 63        | GND            | -   | Thermal ground      |

(1) I = input; O = output; I/O = bidirectional

(2) For pin multiplexing details, see Table 3-2.

The module makes extensive use of pin multiplexing to accommodate the large number of peripheral functions in the smallest possible package. To achieve this configuration, pin multiplexing is controlled using a combination of hardware configuration (at module reset) and register control.

The board and software designers are responsible for the proper pin multiplexing configuration. Hardware does not ensure that the proper pin multiplexing options are selected for the peripherals or interface mode used. Table 3-2 describes the general pin attributes and presents an overview of pin multiplexing. All pin multiplexing options are configurable using the pin MUX registers. The following special considerations apply:

- All I/Os support drive strengths of 2, 4, and 6 mA. Drive strength is individually configurable for each pin.

- All I/Os support 10-µA pullup and pulldown resistors.

- By default, all I/Os float in the Hibernate state. However, the default state can be changed by SW.

- All digital I/Os are non fail-safe.

#### Note

If an external device drives a positive voltage to the signal pads and the BDE-WF3235 module is not powered, DC is drawn from the other device. If the drive strength of the external device is adequate, an unintentional wakeup and boot of the BDE-WF3235 module can occur. To prevent current draw, we recommend any one of the following conditions:

- All devices interfaced to the BDE-WF3235 module must be powered from the same power rail as the chip.

- Use level shifters between the device and any external devices fed from other independent rails.

- The nRESET pin of the BDE-WF3235 module must be held low until the VBAT supply to the module is driven and stable.

- All GPIO pins default to high impedance unless programmed by the MCU. The bootloader sets the TDI, TDO, TCK, TMS, and Flash\_SPI pins to mode 1. All the other pins are left in the Hi-Z state.

The ADC inputs are tolerant up to 1.8 V (see Table 4-17 for more details about the usable range of the ADC). On the other hand, the digital pads can tolerate up to 3.6 V. Hence, take care to prevent accidental damage to the ADC inputs. We recommend first disabling the output buffers of the digital I/Os corresponding to the desired ADC channel (that is, converted to Hi-Z state), and thereafter disabling the respective pass switches (S7 [Pin 47], S8 [Pin 48], S9 [Pin 49], and S10 [Pin 50]). For more information, see Table 3-4.

Table 3-2. Pin Attributes and Pin Multiplexing

|         | GE        | NERAL PIN | ATTRIBUTE                     | S                                 |                       |                              |                                             | FUNCTIO     | N                         |                     | PAD STATES           |       |            |

|---------|-----------|-----------|-------------------------------|-----------------------------------|-----------------------|------------------------------|---------------------------------------------|-------------|---------------------------|---------------------|----------------------|-------|------------|

| kg. Pin | Pin Alias | Use       | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG | Dig. Pin Mux<br>Config. Reg. | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name | Signal Description        | Signal<br>Direction | LPDS                 | Hib   | nRESET = 0 |

| 1       | GND       | GND       | N/A                           | N/A                               | N/A                   | N/A                          | N/A                                         | GND         | GND                       | N/A                 | N/A                  | N/A   | N/A        |

| 2       | GND       | GND       | N/A                           | N/A                               | N/A                   | N/A                          | N/A                                         | GND         | GND                       | N/A                 | N/A                  | N/A   | N/A        |

|         |           |           |                               |                                   |                       | GPIO_PAD_<br>CONFIG_10       | 0                                           | GPIO10      | GPIO                      | I/O                 | Hi-Z, Pull,<br>Drive |       |            |

|         |           |           |                               | No                                | No                    |                              | 1                                           | I2C_SCL     | I2C clock                 | I/O (open<br>drain) | Hi-Z, Pull,<br>Drive | Hi-Z, |            |

| 3       | GPIO10    | I/O       | No                            |                                   |                       |                              | 3                                           | GT_PWM06    | Pulse-width modulated O/P | 0                   | Hi-Z, Pull,<br>Drive | Pull, | Hi-Z       |

|         |           |           |                               |                                   |                       | (0x4402 E0C8)                | 7                                           | UART1_TX    | UART TX data              | 0                   | 1                    | Drive |            |

|         |           |           |                               |                                   |                       |                              | 6                                           | SDCARD_CLK  | SD card clock             | 0                   | 0                    |       |            |

|         |           |           |                               |                                   |                       |                              | 12                                          | GT_CCP01    | Timer capture port        | 1                   | Hi-Z, Pull,<br>Drive |       |            |

|          | GE        | NERAL PIN | ATTRIBUTE                     | s                                 |                       |                              |                                             | FUNCTION       | ı                             |                     | PAD STATES           |                |            |  |

|----------|-----------|-----------|-------------------------------|-----------------------------------|-----------------------|------------------------------|---------------------------------------------|----------------|-------------------------------|---------------------|----------------------|----------------|------------|--|

| Pkg. Pin | Pin Alias | Use       | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG | Dig. Pin Mux<br>Config. Reg. | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name    | Signal Description            | Signal<br>Direction | LPDS                 | Hib            | nRESET = 0 |  |

|          |           |           |                               |                                   |                       |                              | 0                                           | GPIO11         | GPIO                          | I/O                 | Hi-Z,<br>Pull, Drive |                |            |  |

|          | GPIO11    |           |                               |                                   |                       |                              | 1                                           | I2C_SDA        | I2C data                      | I/O (open<br>drain) | Hi-Z,<br>Pull, Drive |                |            |  |

|          |           |           |                               |                                   |                       |                              | 3                                           | GT_PWM07       | Pulse-width modulated O/P     | 0                   | Hi-Z,<br>Pull, Drive |                |            |  |

|          |           |           |                               | s No                              | No                    | GPIO PAD                     | 4                                           | pXCLK (XVCLK)  | Free clock to parallel camera | 0                   | 0                    | Hi-Z,          |            |  |

| 4        |           | I/O       | Yes                           |                                   |                       | CONFIG_11<br>(0x4402 E0CC)   | 6                                           | SDCARD_CMD     | SD card command line          | I/O (open<br>drain) | Hi-Z,<br>Pull, Drive | Pull,<br>Drive | Hi-Z       |  |

|          |           |           |                               |                                   |                       |                              | 7                                           | UART1_RX       | UART RX data                  | ı                   | Hi-Z,<br>Pull, Drive |                |            |  |

|          |           |           |                               |                                   |                       |                              | 12                                          | GT_CCP02       | Timer capture port            | I                   | Hi-Z,<br>Pull, Drive |                |            |  |

|          |           |           |                               |                                   |                       |                              | 13                                          | MCAFSX         | I2S audio port frame sync     | 0                   | Hi-Z,<br>Pull, Drive |                |            |  |

|          |           |           |                               |                                   |                       |                              | 0                                           | GPIO14         | GPIO                          | I/O                 |                      |                |            |  |

|          |           |           |                               | o No                              | No                    |                              | 5                                           | I2C_SCL        | I2C clock                     | I/O<br>(open drain) |                      |                | Hi-Z       |  |

| 5        | GPIO14    | I/O       | No                            |                                   |                       | GPIO_PAD_<br>CONFIG_14       | 7                                           | GSPI_CLK       | General SPI clock             | I/O                 | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull, |            |  |

|          |           |           |                               |                                   |                       | (0x4402 E0D8)                | 4                                           | pDATA8(CAM_D4) | Parallel camera<br>data bit 4 | I                   | i uii, biive         | Drive          |            |  |

|          |           |           |                               |                                   |                       |                              | 12                                          | GT_CCP05       | Timer capture port            | I                   |                      |                |            |  |

|          | GE        | NERAL PIN | ATTRIBUTE                     | :S                                |                       |                              |                                             | FUNCTION            | N .                           |                     | PAD STATES                                                           |                         |            |  |  |

|----------|-----------|-----------|-------------------------------|-----------------------------------|-----------------------|------------------------------|---------------------------------------------|---------------------|-------------------------------|---------------------|----------------------------------------------------------------------|-------------------------|------------|--|--|

| Pkg. Pin | Pin Alias | Use       | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG | Dig. Pin Mux<br>Config. Reg. | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name         | Signal Description            | Signal<br>Direction | LPDS                                                                 | Hib                     | nRESET = 0 |  |  |

|          |           |           |                               |                                   |                       |                              | 0                                           | GPIO15              | GPIO                          | I/O                 |                                                                      |                         |            |  |  |

|          |           |           |                               |                                   |                       |                              | 5                                           | I2C_SDA             |                               | I/O<br>(open drain) |                                                                      | Hi-Z,<br>Pull,<br>Drive |            |  |  |

|          |           |           |                               |                                   |                       | GPIO_PAD_                    | 7                                           | GSPI_MISO           | General SPI MISO              | I/O                 | Hi-Z,                                                                |                         | Hi-Z       |  |  |

| 6        | GPIO15    | I/O       | No                            | No                                | No                    | CONFIG_15<br>(0x4402 E0DC)   | 4                                           | pDATA9<br>(CAM_D5)  | Parallel camera<br>data bit 5 | I                   | Pull, Drive                                                          |                         |            |  |  |

|          |           |           |                               |                                   |                       |                              |                                             |                     |                               | 13                  | GT_CCP06                                                             | Timer capture port      | I          |  |  |

|          |           |           |                               |                                   |                       |                              | 8                                           | SDCARD_<br>DATA0    | SD card data                  | I/O                 |                                                                      |                         |            |  |  |

|          |           |           |                               | No                                |                       |                              | 0                                           | GPIO16              | GPIO                          | I/O                 | Hi-Z,<br>Pull, Drive<br>Hi-Z,<br>Pull, Drive<br>Hi-Z,<br>Pull, Drive |                         |            |  |  |

|          |           |           | I/O No                        |                                   |                       | GPIO_PAD_                    | 7                                           | GSPI_MOSI           | General SPI MOSI              | I/O                 | Hi-Z,                                                                | Hi-Z,                   |            |  |  |

| 7        | GPIO16    | I/O       |                               |                                   | No                    | CONFIG_16<br>(0x4402 E0E0)   | 4                                           | pDATA10<br>(CAM_D6) | Parallel camera<br>data bit 6 | I                   | Hi-Z,<br>Pull, Drive                                                 | Pull,<br>Drive          | Hi-Z       |  |  |

|          |           |           |                               |                                   |                       |                              | 5                                           | UART1_TX            | UART1 TX data                 | 0                   | 1                                                                    |                         |            |  |  |

|          |           |           |                               |                                   | 13                    | GT_CCP07                     | Timer capture port                          | I                   | Hi-Z,<br>Pull, Drive          |                     |                                                                      |                         |            |  |  |

|          |           |           |                               |                                   |                       |                              | 8                                           | SDCARD_CLK          | SD card clock                 | 0                   | Zero                                                                 |                         |            |  |  |

|          | GE        | NERAL PIN | ATTRIBUTE                     | S                                 |                       |                                         |                                             | FUNCTION            | ı                                  |                                          | Р                    | AD STAT                 | ES             |       |

|----------|-----------|-----------|-------------------------------|-----------------------------------|-----------------------|-----------------------------------------|---------------------------------------------|---------------------|------------------------------------|------------------------------------------|----------------------|-------------------------|----------------|-------|

| Pkg. Pin | Pin Alias | Use       | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG | Dig. Pin Mux<br>Config. Reg.            | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name         | Signal Description                 | Signal<br>Direction                      | LPDS                 | Hib                     | nRESET = 0     |       |

|          |           |           |                               |                                   |                       |                                         | 0                                           | GPIO17              | GPIO                               | I/O                                      |                      |                         |                |       |

|          |           |           |                               |                                   |                       |                                         | 5                                           | UART1_RX            | UART1 RX data                      | I                                        |                      |                         |                |       |

| 8        | GPIO17    | I/O       | Yes                           | No                                | No                    | GPIO_PAD_<br>CONFIG_17                  | 7                                           | GSPI_CS             | General SPI chip select            | I/O                                      | Hi-Z,                | Hi-Z,<br>Pull,<br>Drive | Hi-Z           |       |

|          |           |           |                               |                                   |                       | (0x4402 E0E4)                           | 4                                           | pDATA11<br>(CAM_D7) | Parallel camera<br>data bit 7      | I                                        | Pull, Drive          |                         |                |       |

|          |           |           |                               |                                   |                       |                                         | 8                                           | SDCARD_CMD          | SD card command line               | I/O                                      |                      |                         |                |       |

|          | GPIO12    |           |                               |                                   |                       | GPIO_PAD_<br>CONFIG_12<br>(0x4402 E0D0) | 0                                           | GPIO12              | GPIO                               | I/O                                      | Hi-Z,<br>Pull, Drive |                         |                |       |

|          |           |           |                               |                                   | No No                 |                                         | CONFIG_12                                   | 3                   | McACLK                             | I <sup>2</sup> S audio port clock output | 0                    | Hi-Z,<br>Pull, Drive    |                |       |

| 9        |           | I/O       | No                            | No                                |                       |                                         |                                             | 4                   | pVS (VSYNC)                        | Parallel camera vertical sync            | I                    | Hi-Z,<br>Pull, Drive    | Hi-Z,<br>Pull, | Hi-Z  |

| 3        | GI 1012   |           |                               | NO                                |                       |                                         |                                             | 5                   | I2C_SCL                            | I <sup>2</sup> C clock                   | I/O<br>(open drain)  | Hi-Z,<br>Pull, Drive    | Drive          | 111-2 |

|          |           |           |                               |                                   |                       |                                         | 7                                           | UART0_TX            | UART0 TX data                      | 0                                        | 1                    |                         |                |       |

|          |           |           |                               |                                   |                       |                                         | 12                                          | GT_CCP03            | Timer capture port                 | I                                        | Hi-Z,<br>Pull, Drive |                         |                |       |

|          |           |           |                               |                                   |                       |                                         | 0                                           | GPIO13              | GPIO                               | I/O                                      |                      |                         |                |       |

|          |           |           |                               |                                   |                       | ODIO DAD                                | 5                                           | I2C_SDA             | I <sub>2</sub> C data              | I/O<br>(open drain)                      |                      | 11: 7                   |                |       |

| 10       | GPIO13    | I/O       | Yes                           | No                                | No                    | GPIO_PAD_<br>CONFIG_13<br>(0x4402 E0D4) | 4                                           | pHS (HSYNC)         | Parallel camera<br>horizontal sync | I                                        | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull,<br>Drive | Hi-Z           |       |

|          |           | ı         |                               |                                   |                       | (UX44UZ EUD4)                           | 7                                           | UART0_RX            | UART0 RX data                      | I                                        |                      | Dilve                   |                |       |

|          |           |           |                               |                                   |                       |                                         | 12                                          | GT_CCP04            | Timer capture port                 | I                                        |                      |                         |                |       |

|          | GE                   | NERAL PIN   | ATTRIBUTE                     | s                                 |                       |                                         |                                             | FUNCTION             | ı                                                     |                     | Р                    | AD STAT                 | ES         |

|----------|----------------------|-------------|-------------------------------|-----------------------------------|-----------------------|-----------------------------------------|---------------------------------------------|----------------------|-------------------------------------------------------|---------------------|----------------------|-------------------------|------------|

| Pkg. Pin | Pin Alias            | Use         | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG | Dig. Pin Mux<br>Config. Reg.            | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name          | Signal Description                                    | Signal<br>Direction | LPDS                 | Hib                     | nRESET = 0 |

|          |                      |             |                               |                                   |                       |                                         | 0                                           | GPIO22               | GPIO                                                  | I/O                 |                      |                         |            |

| 11       | GPIO22               | I/O         | No                            | No                                | No                    | GPIO_PAD_<br>CONFIG_22<br>(0x4402 E0F8) | 7                                           | McAFSX               | I2S audio port frame sync                             | 0                   | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull,<br>Drive | Hi-Z       |

|          |                      |             |                               |                                   |                       | (011110= -010)                          | 5                                           | GT_CCP04             | Timer capture port                                    | 1                   |                      |                         |            |

|          |                      |             |                               |                                   |                       |                                         | 1                                           | TDI                  | JTAG TDI. Reset default pinout.                       | I                   | Hi-Z,                |                         |            |

|          |                      |             |                               |                                   | Muxed with            | GPIO_PAD_                               | 0                                           | GPIO23               | GPIO                                                  | I/O                 | Pull, Drive          | Hi-Z,                   |            |

| 12       | JTAG_TDI             | TAG_TDI I/O | I/O No                        | No                                | JTAG TDI              | CONFIG_23<br>(0x4402 E0FC)              | 2                                           | UART1_TX             | UART1 TX data                                         | 0                   | 1                    | Pull,<br>Drive          | Hi-Z       |

|          |                      |             |                               |                                   |                       |                                         | 9                                           | I2C_SCL              | I2C clock                                             | I/O (open<br>drain) | Hi-Z,<br>Pull, Drive |                         |            |

| 13       | FLASH_<br>SPI_ MISO  | N/A         | N/A                           | N/A                               | N/A                   | N/A                                     | N/A                                         | FLASH_SPI_MISO       | Data from SPI serial flash (fixed default)            | N/A                 | Hi-Z                 | Hi-Z                    | Hi-Z       |

| 14       | FLASH_<br>SPI_nCS_IN | N/A         | N/A                           | N/A                               | N/A                   | N/A                                     | N/A                                         | FLASH_SPI_nCS_<br>IN | Chip select to SPI<br>serial flash (fixed<br>default) | N/A                 | 1                    | Hi-Z,<br>Pull,<br>Drive | Hi-Z       |

| 15       | FLASH_<br>SPI_CLK    | N/A         | N/A                           | N/A                               | N/A                   | N/A                                     | N/A                                         | FLASH_SPI_ CLK       | Clock to SPI serial flash<br>(fixed default)          | N/A                 | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull,<br>Drive | Hi-Z       |

| 16       | GND                  | GND         | N/A                           | N/A                               | N/A                   | N/A                                     | N/A                                         | GND                  | GND                                                   | N/A                 | N/A                  | N/A                     | N/A        |

| 17       | FLASH_<br>SPI_MOSI   | N/A         | N/A                           | N/A                               | N/A                   | N/A                                     | N/A                                         | FLASH_SPI_MOSI       | Data to SPI serial flash<br>(fixed default)           | N/A                 | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull,<br>Drive | Hi-Z       |

|          | GE        | NERAL PIN      | ATTRIBUTE                     | S                                 |                             |                                          |                                             | FUNCTION    | N                                      |                     | P                    | AD STAT                 | ES                          |      |

|----------|-----------|----------------|-------------------------------|-----------------------------------|-----------------------------|------------------------------------------|---------------------------------------------|-------------|----------------------------------------|---------------------|----------------------|-------------------------|-----------------------------|------|

| Pkg. Pin | Pin Alias | Use            | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG       | Dig. Pin Mux<br>Config. Reg.             | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name | Signal Description                     | Signal<br>Direction | LPDS                 | Hib                     | nRESET = 0                  |      |

|          |           |                |                               |                                   |                             |                                          | 1                                           | TDO         | JTAG TDO. Reset default pinout.        | 0                   |                      |                         |                             |      |

|          |           |                |                               |                                   |                             |                                          | 0                                           | GPIO24      | GPIO                                   | I/O                 |                      |                         |                             |      |

|          |           |                |                               |                                   |                             | ODIO DAD                                 | 5                                           | PWM0        | Pulse-width modulated O/P              | 0                   |                      | Driven high in          |                             |      |

| 18       | JTAG_TDO  | I/O            | Yes                           | No                                | Muxed with<br>JTAG TDO      | GPIO_PAD_<br>CONFIG_ 24<br>(0x4402 E100) | CONFIG_ 24                                  | 2           | UART1_RX                               | UART1 RX data       | I                    | Hi-Z,<br>Pull, Drive    | SWD;<br>driven<br>low in 4- | Hi-Z |

|          |           |                |                               |                                   |                             | I2C data                                 | I/O<br>(open drain)                         |             | wire<br>JTAG                           |                     |                      |                         |                             |      |

|          |           |                |                               |                                   |                             |                                          | 4                                           | GT_CCP06    | Timer capture port                     | 1                   |                      |                         |                             |      |

|          |           |                |                               |                                   |                             |                                          | 6                                           | McAFSX      | I2S audio port frame sync              | 0                   |                      |                         |                             |      |

| 19       | GPIO28    | I/O            | No                            | No                                | No                          | GPIO_PAD_<br>CONFIG_ 40<br>(0x4402 E140) | 0                                           | GPIO28      | GPIO                                   | I/O                 | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull,<br>Drive | Hi-Z                        |      |

| 20       | NC        | WLAN<br>analog | N/A                           | N/A                               | N/A                         | N/A                                      | N/A                                         | NC          | Reserved                               | N/A                 | N/A                  | N/A                     | N/A                         |      |

| 21       | JTAG_TCK  | I/O            | No                            | No                                | Muxed with<br>JTAG/         | GPIO_PAD_<br>CONFIG_ 28                  | 1                                           | TCK         | JTAG/SWD TCK.<br>Reset default pinout. | I                   | Hi-Z,                | Hi-Z,<br>Pull,          | Hi-Z                        |      |

|          |           |                |                               |                                   | SWD- TCK                    | (0x4402 E110)                            | 8                                           | GT_PWM03    | Pulse-width modulated O/P              | 0                   | Pull, Drive          | Drive                   |                             |      |

| 22       | JTAG_TMS  | I/O            | No                            | No                                | Muxed with<br>JTAG/<br>SWD- | / GPIO_PAD_                              | 1                                           | TMS         | JTAG/SWD TMS.<br>Reset default pinout. | I/O                 | Hi-Z,<br>Pull, Drive | Hi-Z,<br>Pull,          | Hi-Z                        |      |

|          |           |                |                               |                                   | TMSC                        | (0x4402 E114)                            | 0                                           | GPIO29      | GPIO                                   |                     | ruli, Dilve          | Drive                   |                             |      |

Datasheet Wi-Fi Dual-Band Module

|          | GI             | ENERAL PIN A   | ATTRIBUTE                     | S                                 |                       |                              |                                             | FUNCTIO     | N                                       |                     | Р                    | AD STAT       | ES         |

|----------|----------------|----------------|-------------------------------|-----------------------------------|-----------------------|------------------------------|---------------------------------------------|-------------|-----------------------------------------|---------------------|----------------------|---------------|------------|

| Pkg. Pin | Pin Alias      | Use            | Select as<br>Wakeup<br>Source | Config.<br>Addl.<br>Analog<br>Mux | Muxed<br>With<br>JTAG | Dig. Pin Mux<br>Config. Reg. | Dig. Pin<br>Mux<br>Config.<br>Mode<br>Value | Signal Name | Signal Description                      | Signal<br>Direction | LPDS                 | Hib           | nRESET = 0 |

|          |                |                |                               |                                   |                       |                              | 0                                           | GPIO25      | GPIO                                    | 0                   | Hi-Z,<br>Pull, Drive |               |            |

|          |                |                |                               |                                   |                       |                              | 9                                           | GT_PWM02    | Pulse-width modulated O/P               | 0                   | Hi-Z,<br>Pull, Drive |               |            |

| 23       | SOP2           | O only         | No                            | No                                | No                    | GPIO_PAD_<br>CONFIG_ 25      | 2                                           | McAFSX      | I2S audio port frame sync               | 0                   | Hi-Z,<br>Pull, Drive | Driven<br>Low | Hi-Z       |

|          |                |                |                               |                                   |                       | (0x4402 E104)                |                                             | TCXO_EN     | Enable to optional external 40-MHz TCXO | 0                   | 0                    | LOW           |            |

|          |                |                |                               |                                   |                       |                              |                                             | SOP2        | Sense-on-power 2                        | I                   | Hi-Z,<br>Pull, Drive |               |            |

| 24       | SOP1           | Config sense   | N/A                           | N/A                               | N/A                   | N/A                          | N/A                                         | SOP1        | Sense-on-power 1                        | N/A                 | N/A                  | N/A           | N/A        |

| 25       | GND            | GND            | N/A                           | N/A                               | N/A                   | N/A                          | N/A                                         | GND         | GND                                     | N/A                 | N/A                  | N/A           | N/A        |

| 26       | GND            | GND            | N/A                           | N/A                               | N/A                   | N/A                          | N/A                                         | GND         | GND                                     | N/A                 | N/A                  | N/A           | N/A        |

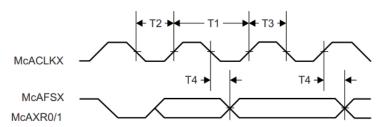

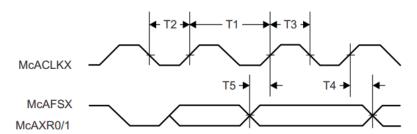

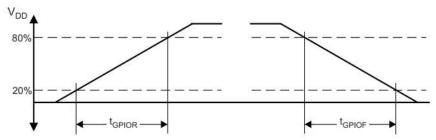

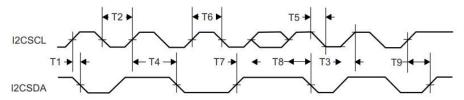

| 27       | GND            | GND            | N/A                           | N/A                               | N/A                   | N/A                          | N/A                                         | GND         | GND                                     | N/A                 | N/A                  | N/A           | N/A        |