## Description

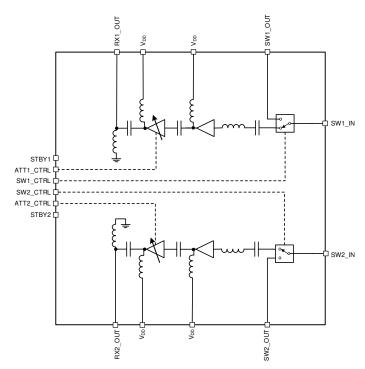

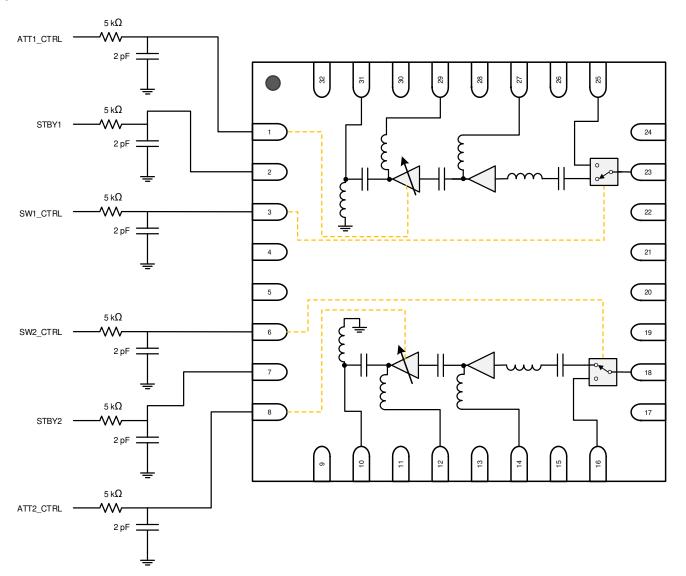

The F0453B is an integrated dual-path RF front-end consisting of an RF switch and two gain stages with 6dB gain control used in the analog front-end receiver of an Active Antenna System (AAS). The F0453B supports frequencies from 3300MHz to 4000MHz.

The F0453B provides 34.5dB gain with +23dBm OIP3, +15dBm output P1dB, and 1.35dB noise figure at 3500MHz. Gain is reduced 6dB in a single step with a maximum settling time of 31ns. The device uses a single 3.3V supply and 130mA of  $I_{DD}$ .

The F0453B is offered in a 5  $\times$  5  $\times$  0.8 mm, 32-LGA package with 50 $\Omega$  input and output amplifier impedances for ease of integration into the signal path.

#### Competitive Advantage

- High integration

- Low noise and high linearity

- On-chip matching and bias

- Extremely low current consumption

### Typical Applications

- Multi-mode, Multi-carrier receivers

- 4.5G (LTE Advanced)

- 5G band 42 and 43

#### **Features**

- Gain at 3500MHz

- 34.5dB typical in High Gain Mode

- 28.5dB typical in Low Gain Mode

- 1.35dB NF at 3500MHz

- +23dBm OIP3 at 3500MHz

- OP1dB at 3500MHz

- +15dBm in High Gain Mode

- +14dBm in Low Gain Mode

- 50Ω single-ended input / output amplifier impedances

- $I_{DD} = 130mA$

- Independent Standby Mode for power savings

- Supply voltage: +3.15V to +3.45V

- 5 × 5 mm, 32-LGA package

- -40°C to +105°C exposed pad operating temperature range

### Block Diagram

## Contents

| Pin Assignments                              | 5  |

|----------------------------------------------|----|

| Pin Descriptions                             | 6  |

| Absolute Maximum Ratings                     | 7  |

| Recommended Operating Conditions             | 8  |

| Electrical Characteristics: General          | 9  |

| Electrical Characteristics: 3300MHz [1]      | 11 |

| Electrical Characteristics: 3300MHz [2]      | 12 |

| Electrical Characteristics: 3400–3600MHz [1] | 13 |

| Electrical Characteristics: 3400–3600MHz [2] | 14 |

| Electrical Characteristics: 3600-3800MHz [1] | 15 |

| Electrical Characteristics: 3600-3800MHz [2] | 16 |

| Electrical Characteristics: 3800-4000MHz [1] | 17 |

| Electrical Characteristics: 3800-4000MHz [2] | 18 |

| Thermal Characteristics                      | 19 |

| Typical Operating Conditions                 | 19 |

| Programming                                  | 24 |

| Evaluation Kit Picture                       | 25 |

| Evaluation Kit / Applications Circuit        | 26 |

| Evaluation Kit Operation                     | 28 |

| Power Supply Setup                           | 28 |

| Standby (STBY) Pin                           | 28 |

| Gain Step Control Setup                      | 29 |

| Switch Control Pin                           | 29 |

| Mode Control Setup                           | 29 |

| Power-On Procedure                           | 29 |

| Power-Off Procedure                          | 29 |

| Application Information                      | 30 |

| Power Supplies                               | 30 |

| Control Pin Interface                        | 30 |

| Package Outline Drawings                     | 31 |

| Ordering Information                         | 31 |

| Marking Diagram                              | 31 |

| Revision History                             | 31 |

# List of Figures

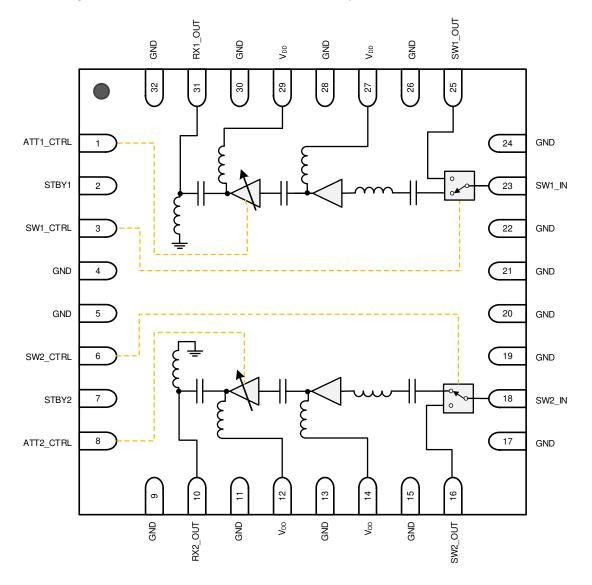

| Figure 1.  | Pin Assignments for 5 × 5 × 0.8 mm 32-LGA – Top View                  | 5   |

|------------|-----------------------------------------------------------------------|-----|

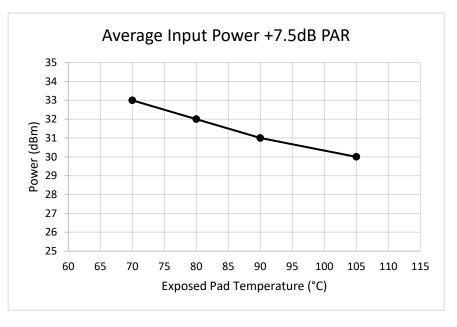

| Figure 2.  | Typical TX Input Power and Reduced Exposed Pad Temperature Profile[c] | 8   |

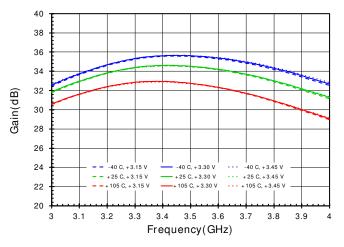

| Figure 3.  | Rx Mode Gain (High Gain)                                              | .20 |

| Figure 4.  | Rx Mode Gain (Low Gain)                                               | .20 |

| Figure 5.  | Rx Mode Channel Isolation (High Gain)                                 | .20 |

| Figure 6.  | Rx Mode Channel Isolation (Low Gain)                                  | .20 |

| Figure 7.  | Rx Mode Input Return Loss (High Gain)                                 | .20 |

| Figure 8.  | Rx Mode Input Return Loss (Low Gain)                                  | .20 |

| Figure 9.  | Rx Mode Output Return Loss (High Gain)                                | .21 |

| Figure 10. | Rx Mode Output Return Loss (Low Gain)                                 | .21 |

| Figure 11. | Rx Mode OP1dB vs. Frequency (High Gain)                               | .21 |

| Figure 12. | Rx Mode OP1dB vs. Frequency (Low Gain)                                | .21 |

| Figure 13. | Rx Mode OIP3 vs. Frequency (High Gain)                                | .21 |

| Figure 14. | Rx Mode OIP3 vs. Frequency (Low Gain)                                 | .21 |

| Figure 15. | Tx Mode Isolation (SW_IN to RX_OUT)                                   | .22 |

| Figure 16. | Tx Mode Channel Isolation (Switch Inputs)                             | .22 |

| Figure 17. | Tx Mode Input Return Loss                                             | .22 |

| Figure 18. | Stability Factor                                                      | .22 |

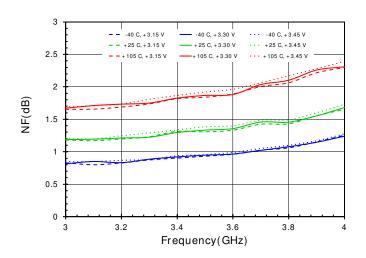

| Figure 19. | Rx Mode Noise Figure (High Gain)                                      | .22 |

| Figure 20. | Rx Mode Noise Figure (Low Gain)                                       | .22 |

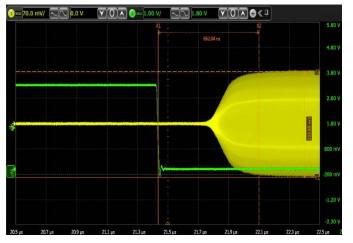

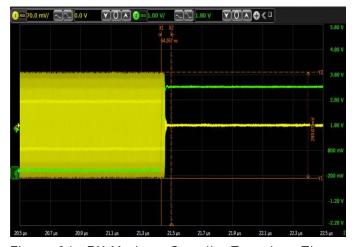

| Figure 21. | Switching Time from TX to RX Mode                                     | .23 |

| Figure 22. | Switching Time from RX to TX Mode                                     | .23 |

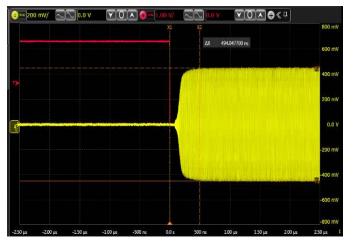

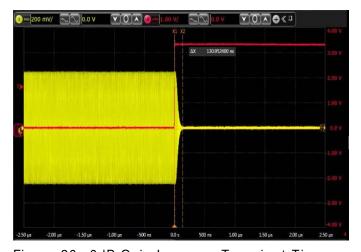

| Figure 23. | Standby to RX Mode Transient Time                                     | .23 |

| Figure 24. | RX Mode to Standby Transient Time                                     | .23 |

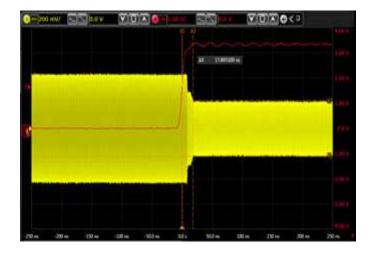

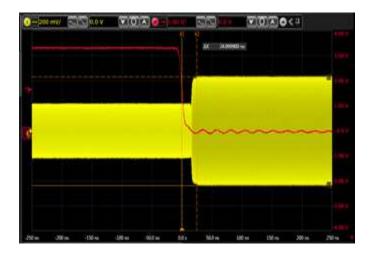

| Figure 25. | 6dB Gain Reduction Transient Time                                     | .23 |

| Figure 26. | 6dB Gain Increase Transient Time                                      | .23 |

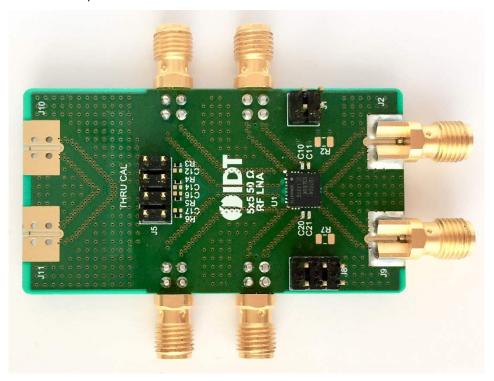

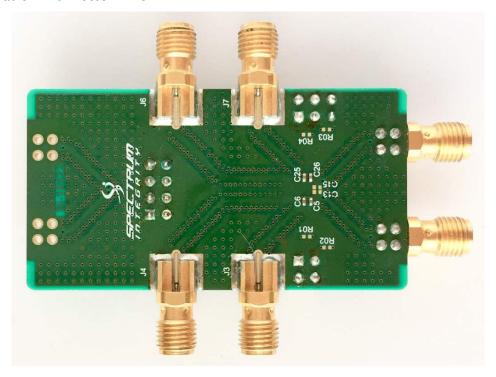

| Figure 27. | Evaluation Kit: Top View                                              | .25 |

| Figure 28. | Evaluation Kit: Bottom View                                           | .25 |

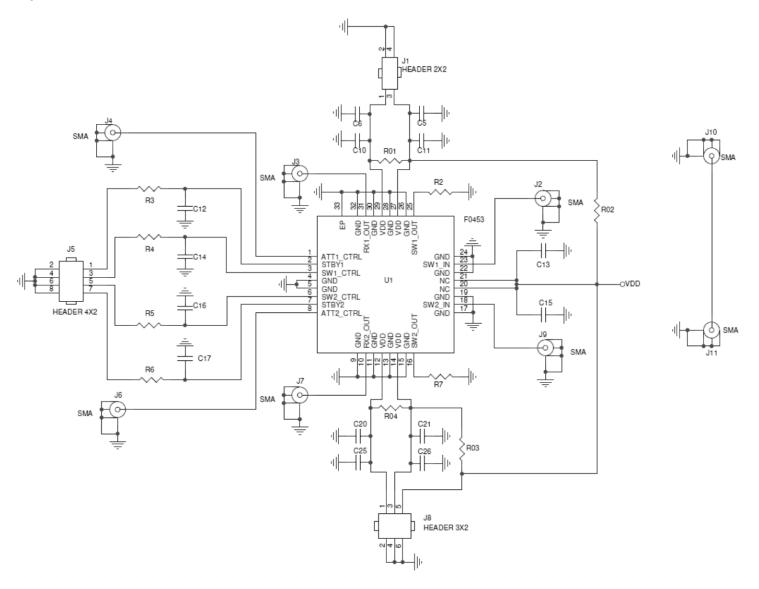

| Figure 29. | Electrical Schematic                                                  | .26 |

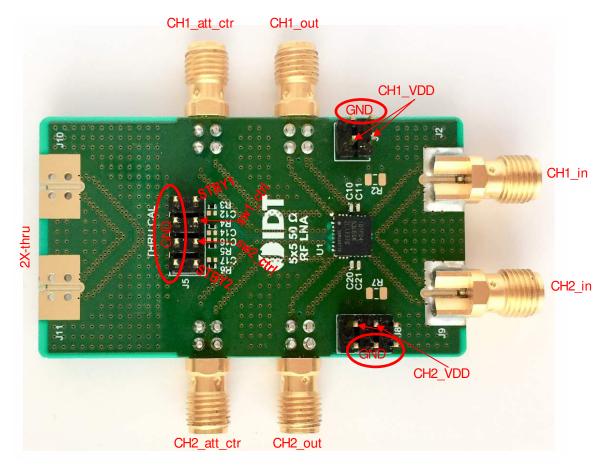

| Figure 30. | Connections of Evaluation Board                                       | .28 |

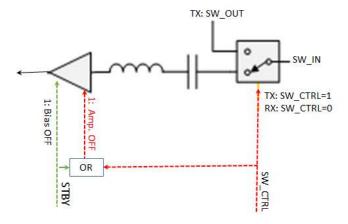

| Figure 31. | Standby and Switch Control Logics                                     | .29 |

|            | Control Pin Interface Schematic                                       | 30  |

## List of Tables

| Table 1.  | Pin Descriptions                                                                       | 6  |

|-----------|----------------------------------------------------------------------------------------|----|

| Table 2.  | Absolute Maximum Ratings                                                               |    |

| Table 3.  | Recommended Operating Conditions                                                       | 8  |

| Table 4.  | Electrical Characteristics: General                                                    | 9  |

| Table 5.  | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance                    | 11 |

| Table 6.  | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance | 12 |

| Table 7.  | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance                    | 13 |

| Table 8.  | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance | 14 |

| Table 9.  | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance                    | 15 |

| Table 10. | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance |    |

| Table 11. | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance                    | 17 |

| Table 12. | Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance | 18 |

|           | Thermal Characteristics                                                                |    |

| Table 14. | Gain Step Truth Table                                                                  | 24 |

|           | Standby and RF Switch Truth Table                                                      |    |

| Table 16. | Bill of Material (BOM)                                                                 | 27 |

# Pin Assignments

Figure 1. Pin Assignments for  $5 \times 5 \times 0.8$  mm 32-LGA – Top View

# Pin Descriptions

Table 1. Pin Descriptions

| Number                                                                  | Name      | Description                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                       | ATT1_CTRL | 1-bit 6dB gain control for path 1. (Low/open = no attenuation; High = 6dB attenuation). A $500k\Omega$ pull-down resistor is connected between this input and GND.                                                                                                     |

| 2                                                                       | STBY1     | Standby (Low/open = path 1 power ON; High = path 1 power OFF). A $500k\Omega$ pull-down resistor is connected between this input and GND.                                                                                                                              |

| 3                                                                       | SW1_CTRL  | RF SWITCH 1 control (Low/open = select main RX PATH 1; High = termination). SW1_CTRL also puts path 1 into Standby Mode for minimum current consumption. A $500k\Omega$ pull-down resistor is connected between this input and GND.                                    |

| 4, 5, 9, 11,<br>13, 15, 17,<br>19, 20, 21,<br>22, 24, 26,<br>28, 30, 32 | GND       | Ground these pins.                                                                                                                                                                                                                                                     |

| 12, 14, 27, 29                                                          | VDD       | Power supply. Bypass to GND with capacitors shown in the F0453B Application Circuit (see Figure 29) as close as possible to pin.                                                                                                                                       |

| 6                                                                       | SW2_CTRL  | RF SWITCH 2 control (Low/open = select main RX PATH 2; High = termination). SW2_CTRL also puts path 2 into Standby Mode for minimum current consumption. A $500k\Omega$ pull-down resistor is connected between this input and GND.                                    |

| 7                                                                       | STBY2     | Standby (Low/open = path 2 power ON; High = path 2 power OFF). A $500k\Omega$ pull-down resistor is connected between this input and GND.                                                                                                                              |

| 8                                                                       | ATT2_CTRL | 1-bit 6dB gain control for path 2. (Low/open = no attenuation; High = 6dB attenuation). A $500k\Omega$ pull-down resistor connects between this input and GND.                                                                                                         |

| 10                                                                      | RX2_OUT   | RF output path 2 matched to $50\Omega$ . Use external DC block as close to the pin as possible.                                                                                                                                                                        |

| 16                                                                      | SW2_OUT   | RF2 switch output matched to $50\Omega$ . Use external $50\Omega$ terminating resistor with proper power rating as required for the application.                                                                                                                       |

| 18                                                                      | SW2_IN    | RF2 switch input matched to $50\Omega$ . Use external DC block as close to the pin as possible.                                                                                                                                                                        |

| 23                                                                      | SW1_IN    | RF1 switch input matched to $50\Omega$ . Use external DC block as close to the pin as possible.                                                                                                                                                                        |

| 25                                                                      | SW1_OUT   | RF1 switch output matched to $50\Omega$ . Use external $50\Omega$ terminating resistor with proper power rating as required for the application                                                                                                                        |

| 31                                                                      | RX1_OUT   | RF output path 1 matched to $50\Omega$ . Use external DC block as close to the pin as possible.                                                                                                                                                                        |

|                                                                         | — EPAD    | Exposed Pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device into the PCB ground planes. These multiple via grounds are also required to achieve the noted RF performance. |

## Absolute Maximum Ratings

Stresses beyond those listed below may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                  | Symbol              | Minimum | Maximum                | Units |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------------------------|-------|

| V <sub>DD</sub> to GND                                                                                                                                                                     | $V_{DD}$            | -0.3    | +3.6                   | ٧     |

| STBY1, STBY2, ATT1_CTRL, ATT2_CTRL, SW1_CTRL, SW2_CTRL to GND                                                                                                                              | V <sub>CTRL</sub>   | -0.3    | V <sub>DD</sub> + 0.25 | V     |

| SW1_IN, SW2_IN, RX1_OUT, RX2_OUT, SW1_OUT, SW2_OUT to GND Externally Applied DC Voltage                                                                                                    | Vsw                 | -50     | 50                     | mV    |

| Tx Mode CW Average Input Power +7.5dB PAR at SW1_IN, SW2_IN ports, 10s, 89% Duty Cycle $50\Omega,T_{\text{EPAD}}=105^{\circ}\text{C}^{\text{[a]}},V_{\text{DD}}=+3.3\text{V}$              | P <sub>ABS_TX</sub> | +31     | +33 <sup>[b]</sup>     | dBm   |

| Rx Mode Average Input Power +7.5dB PAR at SW1_IN, SW2_IN ports, 1 hour single event, 50% Duty Cycle $50\Omega,T_{\text{EPAD}}=105^{\circ}\text{C}^{\text{[a]}},V_{\text{DD}}=+3.3\text{V}$ | P <sub>ABS_RX</sub> |         | +8                     | dBm   |

| Storage Temperature Range                                                                                                                                                                  | T <sub>ST</sub>     | -65     | +150                   | °C    |

| Lead Temperature (soldering, 10s)                                                                                                                                                          | $T_{LEAD}$          |         | +260                   | °C    |

| Electrostatic Discharge – HBM (JEDEC/ESDA JS-001-2012)                                                                                                                                     | Vesdhbm             |         | 1500<br>(Class 1C)     | V     |

| Electrostatic Discharge – CDM<br>(JEDEC JS-002-2014)<br>ALL pins except pins 16, 18, 23, 25                                                                                                | Vesdcdm             |         | 500<br>(Class C2a)     | V     |

| Electrostatic Discharge – CDM<br>(JEDEC JS-002-2014)<br>Pins 16, 18, 23, 25                                                                                                                | Vesdcdm             |         | 125<br>(Class C0b)     | V     |

<sup>[</sup>a]  $T_{EPAD} = Temperature of the exposed paddle.$

<sup>[</sup>b] RF input exposures greater than +31dBm and up to +33dBm for multiple extended periods will affect device reliability and lifetime if the maximum recommended input junction temperature is exceeded.

## Recommended Operating Conditions

Table 3. Recommended Operating Conditions

| Parameter                                                                                          | Symbol              | Condition      | Minimum | Typical | Maximum            | Units |

|----------------------------------------------------------------------------------------------------|---------------------|----------------|---------|---------|--------------------|-------|

| Power Supply Voltage                                                                               | $V_{DD}$            |                | 3.15    | 3.3     | 3.45               | V     |

| Operating Temperature Range                                                                        | T <sub>EPAD</sub>   | Exposed Paddle | -40     |         | +105               | °C    |

| RF Frequency Range                                                                                 | $f_{RF}$            |                | 3300    |         | 4000               | MHz   |

| Tx Mode CW Average Input Power, +7.5dB PAR, Full Life Time $^{[a]}$ 50 $\Omega$ , $V_{DD}$ = +3.3V | Рмах_тх             | 89% Duty Cycle |         |         | +30 <sup>[b]</sup> | dBm   |

| Rx Mode CW Average Input Power, +7.5dB PAR, Full Life Time $^{[a]}$ 50 $\Omega$ , $V_{DD}$ = +3.3V | P <sub>MAX_RX</sub> | 89% Duty Cycle |         |         | -25                | dBm   |

| Port Impedance (SW1_IN, SW2_IN, RX1_OUT, RX2_OUT)                                                  | Z <sub>RF</sub>     |                |         | 50      |                    | Ω     |

| Junction Temperature                                                                               | TJ                  |                |         |         | +125               | °C    |

<sup>[</sup>a] Assumes device environmental temperature cycling within the specified exposed pad operating temperature range of -40°C and 105°C and a maximum junction temperature of 125°C.

Figure 2. Typical TX Input Power and Reduced Exposed Pad Temperature Profile [9]

<sup>[</sup>c] Profile represents estimates to maintain maximum junction temperature ≤ 125°C using Renesas-specific evaluation board and test environment.

<sup>[</sup>b] Operation beyond the maximum recommended operating input power level should be limited and have reduced exposed pad temperatures to maintain device reliability per foundry guidelines (see Figure 2). Electrical characteristics and lifetime are not guaranteed for RF input power levels beyond what is specified in this table.

## Electrical Characteristics: General

Table 4. Electrical Characteristics: General

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD} = +3.3V$ ,  $T_{EPAD} = +25^{\circ}C$ , STBY = LOW, RX output power = -10dBm,  $Z_{S} = Z_{L} = 50\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                         | Symbol          | Condition                                                                                           | Minimum             | Typical | Maximum                          | Units |

|-----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|---------------------|---------|----------------------------------|-------|

| Logic Input High Threshold        | V <sub>IH</sub> |                                                                                                     | 1.17 <sup>[a]</sup> |         | Lower of (V <sub>DD</sub> , 3.3) | V     |

| Logic Input Low Threshold         | V <sub>IL</sub> |                                                                                                     | -0.3                |         | 0.55                             | V     |

| Logic Current                     | lıн, lı∟        | For each control pin                                                                                | -10                 |         | 10                               | μΑ    |

|                                   |                 | 2 paths in Rx Mode                                                                                  |                     | 130     | 180                              |       |

|                                   |                 | 1 path in Rx Mode<br>1 path in Tx Mode                                                              |                     | 70      | 100                              |       |

| DC Current                        | I <sub>DD</sub> | 1 path in Rx Mode<br>1 path in Standby Mode                                                         |                     | 67      |                                  | mA    |

|                                   |                 | 1 path in Tx Mode<br>1 path in Standby Mode                                                         |                     | 5       |                                  |       |

|                                   |                 | 2 paths in Standby Mode                                                                             |                     | 5       |                                  |       |

| Cain Stan                         | Gstep           | f <sub>RF</sub> = 3300MHz to 3800MHz                                                                |                     | 6       |                                  | 4D    |

| Gain Step                         |                 | f <sub>RF</sub> = 3800MHz to 4000MHz                                                                |                     | 5       |                                  | dB    |

| Gain Step Absolute Error          | GSTEP_ERR       | Relative to maximum gain, over-voltage, and temperature                                             |                     | ±0.5    |                                  | dB    |

| Relative Phase Gain Step          | Gstep_ph        |                                                                                                     |                     | 21      |                                  | deg   |

| Gain Step Settling Time [b]       | Gstep_set       | 50% control logic to RF output within ±0.1dB of final value                                         |                     | 26      | 31                               | ns    |

| Gain Step Phase Settling Time [b] | GSTEP_PHSET     | 50% control logic to RF output within ±1 degree of final value                                      |                     | 17      | 30                               | ns    |

| Power ON Switching Time [b]       | SWon            | To Rx Mode from Tx Mode 50% control logic to RF output settled to within ±0.1dB of final value      |                     |         | 1                                | μs    |

| Power OFF Switching Time [b]      | SWoff           | To Tx Mode from Rx Mode<br>50% control logic to RF input<br>settled within ±0.1dB of final<br>value |                     |         | 0.5                              | μs    |

| Parameter                      | Symbol        | Condition                                                                                        | Minimum | Typical | Maximum | Units |

|--------------------------------|---------------|--------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| Power ON from Standby Mode [b] | SWon_standby  | To Rx Mode from Standby<br>Mode<br>50% STBY to RF output settled<br>within ±0.1dB of final value |         |         | 1       | μs    |

| Power OFF to Standby Mode [b]  | SWoff_STANDBY | To Standby Mode from Rx<br>Mode<br>50% STBY to gain below<br>-25dB from max gain                 |         |         | 1       | μs    |

<sup>[</sup>a] Items in the Minimum/Maximum columns in *bold italics* are confirmed by test. Items in the Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] f<sub>RF</sub> = 3500MHz. Assumes the control signal is clean and no external RC circuitry is required on the pin. Adding RC circuitry increases switching time.

# Electrical Characteristics: 3300MHz [1]

Table 5. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3300MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter          | Symbol             | Condition                                                | Minimum | Typical | Maximum | Units |

|--------------------|--------------------|----------------------------------------------------------|---------|---------|---------|-------|

|                    |                    | Measured at SW1_IN, SW2_IN<br>High Gain Mode,            | 11      | 17      |         |       |

| Input Return Loss  | RL <sub>IN</sub>   | Measured at SW1_IN, SW2_IN Low Gain Mode,                | 9       | 15      |         | dB    |

|                    |                    | Measured at SW1_IN, SW2_IN TX mode [a] [b]               | 9       | 13      |         |       |

| Output Return Loss | RLout              | Measured at RX1_OUT,<br>RX2_OUT,<br>High/Low Gain Modes, | 5       | 6       |         | dB    |

| Reverse Isolation  | ISO <sub>REV</sub> | RX1_OUT to SW1_IN, or RX2_OUT to SW2_IN                  | 44      | 60      |         | dB    |

|                    | GнG                | High Gain Mode                                           | 32      | 34      | 36      |       |

| Gain               | Gнg_темр           | T <sub>EPAD</sub> = -40 to 105°C                         | 31      |         | 37      | dB    |

| Gain Attenuated    | G <sub>LG</sub>    | Low Gain Mode                                            |         | 28      |         | dB    |

| Noise Figure       | NF                 | Measured at antenna port ideally matched to LNA          |         | 1.3     | 1.5     | dB    |

| Noise Figure       | NIE                | T <sub>EPAD</sub> = 105°C                                |         |         | 2       |       |

| Noise Figure       | NF Low Ga          | Low Gain Mode                                            |         | 1.3     |         | dB    |

<sup>[</sup>a] Specification reflects use of an external termination resistor at SW1\_OUT, SW2\_OUT with an RL > 22dB.

<sup>[</sup>b] Performance can be further improved with tuning at the SW1\_OUT and SW2\_OUT ports.

## Electrical Characteristics: 3300MHz [2]

Table 6. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3300MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol             | Condition                                                                                                                                                                           | Minimum | Typical | Maximum | Units |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                                    | OIP3 <sub>1</sub>  | Pout = 0dBm/tone<br>5MHz tone separation                                                                                                                                            |         | 23      |         |       |

|                                    | OIP3 <sub>2</sub>  | Pout = 0dBm/tone 5MHz tone separation T <sub>EPAD</sub> = -40 to 105°C                                                                                                              | 20      |         |         |       |

| Output Third-Order Intercept Point | OIP3₃              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode                                                                                                                                 |         | 23      |         | dBm   |

|                                    | OIP34              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                | 18      |         |         |       |

|                                    | OP1dB <sub>1</sub> | High Gain Mode <sup>[b]</sup>                                                                                                                                                       | G-23    | 15      |         |       |

| Outsid A ID Oursians in            | OP1dB <sub>2</sub> | High Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                     | G-24    |         |         | -ID   |

| Output 1dB Compression             | OP1dB₃             | Low Gain Mode                                                                                                                                                                       |         | 13      |         | dBm   |

|                                    | OP1dB <sub>4</sub> | Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                      | G-18    |         |         |       |

| Channel Isolation                  | ISOch              | $RFISO_1 = \left(\frac{RX1\_OUT}{RX2\_OUT}\right)_{dB}$ with $-60 \le SW1\_IN \le -30dBm$ $RFISO_2 = \left(\frac{RX2\_OUT}{RX1\_OUT}\right)_{dB}$ with $-60 \le SW2\_IN \le -30dBm$ | 40      | 50      |         | dB    |

| RF Switch Isolation                | ISO <sub>SW</sub>  | Tx Mode  Measured at SW_IN to  RX_OUT of the same channel                                                                                                                           | 50      | 60      |         | dB    |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] In the OP1dB calculation formula, "G" denotes the gain of each part instance at the frequency of interest and appropriate High / Low gain state.

## Electrical Characteristics: 3400-3600MHz [1]

Table 7. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3500MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                                                  | Symbol               | Condition                                                                                                                                                   | Minimum           | Typical | Maximum | Units |

|------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|---------|-------|

|                                                            |                      | Measured at SW1_IN, SW2_IN<br>High Gain Mode,<br>fre = 3400MHz to 3600MHz                                                                                   | 14 <sup>[a]</sup> | 20      |         |       |

| Input Return Loss                                          | $RL_IN$              | Measured at SW1_IN, SW2_IN<br>Low Gain Mode,<br>f <sub>RF</sub> = 3400MHz to 3600MHz                                                                        | 13                | 20      |         | dB    |

|                                                            |                      | Measured at SW1_IN, SW2_IN TX mode [b] [c]                                                                                                                  | 9                 | 13      |         |       |

| Output Return Loss                                         | RL <sub>OUT</sub>    | Measured at RX1_OUT,<br>RX2_OUT,<br>High/Low Gain Modes,<br>f <sub>RF</sub> = 3400MHz to 3600MHz                                                            | 6                 | 9       |         | dB    |

| Reverse Isolation, RX1_OUT to SW1_IN, or RX2_OUT to SW2_IN | ISOREV               | f <sub>RF</sub> = 3400MHz to 3600MHz                                                                                                                        | 50                | 60      |         | dB    |

|                                                            | GнG                  | High Gain Mode                                                                                                                                              | 32                | 34.5    | 37      |       |

| Gain                                                       | G <sub>HG_ТЕМР</sub> | T <sub>EPAD</sub> = -40 to 105°C                                                                                                                            | 31                |         | 38      | dB    |

| Gain Attenuated                                            | G <sub>LG</sub>      | Low Gain Mode                                                                                                                                               | 25.5              | 28.5    | 31.5    | dB    |

| Gain Ripple                                                | Gripple              | f <sub>RF</sub> = 3400MHz to 3600MHz<br>(Difference between maximum<br>and minimum gain in each<br>100MHz subrange within the<br>specified frequency range) |                   | ±0.2    |         | dB    |

|                                                            |                      | Measured at antenna port ideally matched to LNA                                                                                                             |                   | 1.35    | 1.55    |       |

| Noise Figure                                               | NF                   | T <sub>EPAD</sub> = 105°C                                                                                                                                   |                   |         | 2.1     | dB    |

|                                                            |                      | Low Gain Mode                                                                                                                                               |                   | 1.4     |         |       |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] Specification reflects use of an external termination resistor at SW1\_OUT, SW2\_OUT with a RL > 22dB.

<sup>[</sup>c] Performance can be further improved with tuning at the SW1\_OUT and SW2\_OUT ports.

### Electrical Characteristics: 3400-3600MHz [2]

Table 8. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3500MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol             | Condition                                                                                                                                                                           | Minimum | Typical | Maximum | Units |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                                    | OIP3 <sub>1</sub>  | Pout = 0dBm/tone<br>5MHz tone separation                                                                                                                                            |         | 23      |         |       |

|                                    | OIP3 <sub>2</sub>  | Pout = 0dBm/tone 5MHz tone separation T <sub>EPAD</sub> = -40 to 105°C                                                                                                              | 20      |         |         |       |

| Output Third-Order Intercept Point | OIP3₃              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode                                                                                                                                 |         | 23      |         | dBm   |

|                                    | OIP34              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                | 18      |         |         |       |

|                                    | OP1dB <sub>1</sub> | High Gain Mode [b]                                                                                                                                                                  | G-23    | 15      |         |       |

| Outs 444D Outs and in              | OP1dB <sub>2</sub> | High Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                     | G-24    |         |         | -ID   |

| Output 1dB Compression             | OP1dB₃             | Low Gain Mode                                                                                                                                                                       |         | 14      |         | dBm   |

|                                    | OP1dB4             | Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                      | G-18    |         |         |       |

| Channel Isolation                  | ISOch              | $RFISO_1 = \left(\frac{RX1\_OUT}{RX2\_OUT}\right)_{dB}$ with $-60 \le SW1\_IN \le -30dBm$ $RFISO_2 = \left(\frac{RX2\_OUT}{RX1\_OUT}\right)_{dB}$ with $-60 \le SW2\_IN \le -30dBm$ | 40      | 50      |         | dB    |

| RF Switch Isolation                | ISOsw              | Tx Mode  Measured at SW_IN to  RX_OUT of the same channel                                                                                                                           | 50      | 60      |         | dB    |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] In the OP1dB calculation formula, "G" denotes the gain of each part instance at the frequency of interest and appropriate High / Low gain state.

## Electrical Characteristics: 3600-3800MHz [1]

#### Table 9. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3700MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol             | Condition                                                                                                                                                   | Minimum           | Typical | Maximum | Units |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|---------|-------|

|                                    |                    | Measured at SW1_IN, SW2_IN<br>High Gain Mode,<br>fre = 3600MHz to 3800MHz                                                                                   | 14 <sup>[a]</sup> | 20      |         |       |

| Input Return Loss                  | RL <sub>IN</sub>   | Measured at SW1_IN, SW2_IN<br>Low Gain Mode,<br>f <sub>RF</sub> = 3600MHz to 3800MHz                                                                        | 13                | 20      |         | dB    |

|                                    |                    | Measured at SW1_IN, SW2_IN TX mode [b] [c]                                                                                                                  | 9                 | 13      |         |       |

| Output Return Loss                 | RLout              | Measured at RX1_OUT,<br>RX2_OUT,<br>High/Low Gain Modes,<br>f <sub>RF</sub> = 3600MHz to 3800MHz                                                            | 8                 | 11      |         | dB    |

| Reverse Isolation, S <sub>12</sub> | ISO <sub>REV</sub> | f <sub>RF</sub> = 3600MHz to 3800MHz                                                                                                                        | 50                | 60      |         | dB    |

| Orin                               | GнG                | High Gain Mode                                                                                                                                              | 32                | 33.5    | 37      | -ID   |

| Gain                               | Gнg_темр           | T <sub>EPAD</sub> = -40 to 105°C                                                                                                                            | 30                |         | 38      | dB    |

| Gain Attenuated                    | G <sub>LG</sub>    | Low Gain Mode                                                                                                                                               | 25                | 28      | 31.5    | dB    |

| Gain Ripple                        | GRIPPLE            | f <sub>RF</sub> = 3600MHz to 3800MHz<br>(Difference between maximum<br>and minimum gain in each<br>100MHz subrange within the<br>specified frequency range) |                   | ±0.4    |         | dB    |

|                                    |                    | Measured at antenna port ideally matched to LNA                                                                                                             |                   | 1.45    | 1.60    |       |

| Noise Figure                       | NF                 | T <sub>EPAD</sub> = 105°C                                                                                                                                   |                   |         | 2.25    | dB    |

|                                    |                    | Low Gain Mode                                                                                                                                               |                   | 1.5     |         |       |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] Specification reflects use of an external termination resistor at SW1\_OUT, SW2\_OUT with a RL > 22dB.

<sup>[</sup>c] Performance can be further improved with tuning at the SW1\_OUT and SW2\_OUT ports.

### Electrical Characteristics: 3600-3800MHz [2]

Table 10. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3700MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol             | Condition                                                                                                                                                                           | Minimum | Typical | Maximum | Units |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                                    | OIP3 <sub>1</sub>  | Pout = 0dBm/tone<br>5MHz tone separation                                                                                                                                            |         | 23      |         |       |

|                                    | OIP3 <sub>2</sub>  | Pout = 0dBm/tone 5MHz tone separation T <sub>EPAD</sub> = -40 to 105°C                                                                                                              | 20      |         |         |       |

| Output Third-Order Intercept Point | OIP3₃              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode                                                                                                                                 |         | 23      |         | dBm   |

|                                    | OIP34              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                | 18      |         |         |       |

|                                    | OP1dB <sub>1</sub> | High Gain Mode [b]                                                                                                                                                                  | G-23    | 15      |         |       |

| Outsid A ID Oursians in            | OP1dB <sub>2</sub> | High Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                     | G-24    |         |         | -ID   |

| Output 1dB Compression             | OP1dB₃             | Low Gain Mode                                                                                                                                                                       |         | 14      |         | dBm   |

|                                    | OP1dB <sub>4</sub> | Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                      | G-18    |         |         |       |

| Channel Isolation                  | ISOch              | $RFISO_1 = \left(\frac{RX1\_OUT}{RX2\_OUT}\right)_{dB}$ with $-60 \le SW1\_IN \le -30dBm$ $RFISO_2 = \left(\frac{RX2\_OUT}{RX1\_OUT}\right)_{dB}$ with $-60 \le SW2\_IN \le -30dBm$ | 40      | 50      |         | dB    |

| RF Switch Isolation                | ISO <sub>SW</sub>  | Tx Mode  Measured at SW_IN to  RX_OUT of the same channel                                                                                                                           | 50      | 60      |         | dB    |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] In the OP1dB calculation formula, "G" denotes the gain of each part instance at the frequency of interest and appropriate High / Low gain state.

## Electrical Characteristics: 3800-4000MHz [1]

Table 11. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3900MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol             | Condition                                                                                                                                                   | Minimum                  | Typical | Maximum | Units |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|---------|-------|

|                                    |                    | Measured at SW1_IN, SW2_IN<br>High Gain Mode,<br>fre = 3800MHz to 4000MHz                                                                                   | <b>11</b> <sup>[a]</sup> | 17      |         |       |

| Input Return Loss                  | RL <sub>IN</sub>   | Measured at SW1_IN, SW2_IN<br>Low Gain Mode,<br>f <sub>RF</sub> = 3800MHz to 4000MHz                                                                        | 9                        | 16      |         | dB    |

|                                    |                    | Measured at SW1_IN, SW2_IN TX mode [b] [c]                                                                                                                  | 9                        | 15      |         |       |

| Output Return Loss                 | RLout              | Measured at RX1_OUT,<br>RX2_OUT,<br>High/Low Gain Modes,<br>f <sub>RF</sub> = 3800MHz to 4000MHz                                                            | 9                        | 12      |         | dB    |

| Reverse Isolation, S <sub>12</sub> | ISO <sub>REV</sub> | f <sub>RF</sub> = 3800MHz to 4000MHz                                                                                                                        | 45                       | 55      |         | dB    |

| Onin                               | Gнg                | High Gain Mode                                                                                                                                              | 29.5                     | 32      | 34.5    | -ID   |

| Gain                               | Gнg_темр           | T <sub>EPAD</sub> = -40 to 105°C                                                                                                                            | 27.5                     |         | 35.5    | dB    |

| Gain Attenuated                    | G <sub>LG</sub>    | Low Gain Mode                                                                                                                                               |                          | 27      |         | dB    |

| Gain Ripple                        | GRIPPLE            | f <sub>RF</sub> = 3800MHz to 4000MHz<br>(Difference between maximum<br>and minimum gain in each<br>100MHz subrange within the<br>specified frequency range) |                          | ±0.5    |         | dB    |

|                                    |                    | Measured at antenna port ideally matched to LNA                                                                                                             |                          | 1.55    | 1.8     |       |

| Noise Figure                       | NF                 | T <sub>EPAD</sub> = 105°C                                                                                                                                   |                          |         | 2.5     | dB    |

|                                    |                    | Low Gain Mode                                                                                                                                               |                          | 1.6     |         |       |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] Specification reflects use of an external termination resistor at SW1\_OUT, SW2\_OUT with a RL > 22dB.

<sup>[</sup>c] Performance can be further improved with tuning at the SW1\_OUT and SW2\_OUT ports.

### Electrical Characteristics: 3800-4000MHz [2]

Table 12. Electrical Characteristics: RX Path in Rx Mode Cascaded Performance and TX Performance

See the F0453B Application Circuit in Figure 29. Specifications apply when operated as an Rx RF amplifier with  $V_{DD}$  = +3.3V,  $f_{RF}$  = 3900MHz,  $T_{EPAD}$  = +25°C, STBY = LOW, RX output power = -10dBm,  $Z_S$  =  $Z_L$  = 50 $\Omega$ , and EVKit trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol             | Condition                                                                                                                                                                           | Minimum | Typical | Maximum | Units |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                                    | OIP3 <sub>1</sub>  | Pout = 0dBm/tone<br>5MHz tone separation                                                                                                                                            |         | 22      |         |       |

|                                    | OIP3₂              | Pout = 0dBm/tone 5MHz tone separation T <sub>EPAD</sub> = -40 to 105°C                                                                                                              | 18      |         |         |       |

| Output Third-Order Intercept Point | OIP3₃              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode                                                                                                                                 |         | 22      |         | dBm   |

|                                    | OIP34              | Pout = 0dBm/tone 5MHz tone separation Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                | 17      |         |         |       |

|                                    | OP1dB <sub>1</sub> | High Gain Mode [b]                                                                                                                                                                  | G-23    | 13      |         |       |

| Outsid A ID Oursian sign           | OP1dB <sub>2</sub> | High Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                     | G-24    |         |         | dD    |

| Output 1dB Compression             | OP1dB₃             | Low Gain Mode                                                                                                                                                                       |         | 12      |         | dBm   |

|                                    | OP1dB <sub>4</sub> | Low Gain Mode T <sub>EPAD</sub> = -40 to 105°C                                                                                                                                      | G-18    |         |         |       |

| Channel Isolation                  | ISOch              | $RFISO_1 = \left(\frac{RX1\_OUT}{RX2\_OUT}\right)_{dB}$ with $-60 \le SW1\_IN \le -30dBm$ $RFISO_2 = \left(\frac{RX2\_OUT}{RX1\_OUT}\right)_{dB}$ with $-60 \le SW2\_IN \le -30dBm$ | 37      | 47      |         | dB    |

| RF Switch Isolation                | ISOsw              | Tx Mode  Measured at SW_IN to  RX_OUT of the same channel                                                                                                                           | 50      | 60      |         | dB    |

<sup>[</sup>a] Items in Minimum/Maximum columns in *bold italics* are confirmed by test. Items in Minimum/Maximum columns NOT in bold italics are confirmed by design characterization.

<sup>[</sup>b] In the OP1dB calculation formula, "G" denotes the gain of each part instance at the frequency of interest and appropriate High / Low gain state.

#### Thermal Characteristics

Table 13. Thermal Characteristics

| Parameter                                                                   | Symbol         | Value | Units |

|-----------------------------------------------------------------------------|----------------|-------|-------|

| Junction-to-Ambient Thermal Resistance                                      | $\theta_{JA}$  | 43    | °C/W  |

| Junction-to-Case Thermal Resistance (Case is defined as the exposed paddle) | $	heta$ JC_BOT | 11.7  | °C/W  |

| Moisture Sensitivity Rating (Per J-STD-020)                                 |                | MSL3  |       |

# Typical Operating Conditions

Unless otherwise noted:

- $V_{DD} = +3.3V$

- T<sub>EPAD</sub> = 25°C

- $Z_L = Z_S = 50\Omega$  single-ended with matching networks

- STBY = Low or open

- SW\_CTRL = Low or open

- Gain Setting = High Gain Mode

- P<sub>IN</sub> ≤ -30dBm

- All temperatures are referenced to the exposed paddle

- Evaluation Kit traces and connector losses are de-embedded

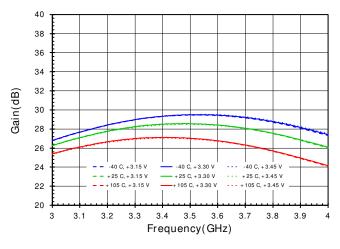

Figure 3. Rx Mode Gain (High Gain)

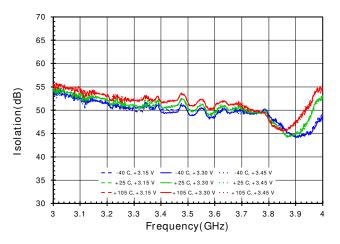

Figure 5. Rx Mode Channel Isolation (High Gain)

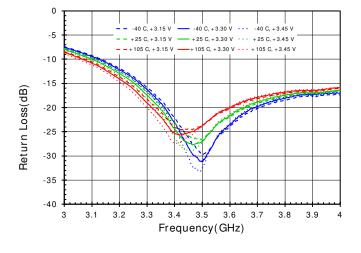

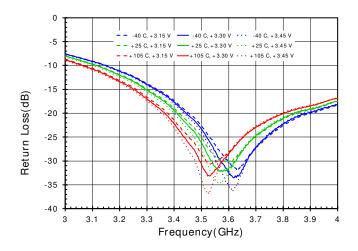

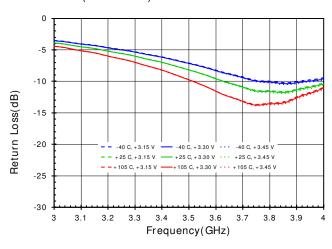

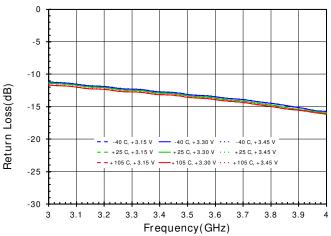

Figure 7. Rx Mode Input Return Loss (High Gain)

Figure 4. Rx Mode Gain (Low Gain)

Figure 6. Rx Mode Channel Isolation (Low Gain)

Figure 8. Rx Mode Input Return Loss (Low Gain)

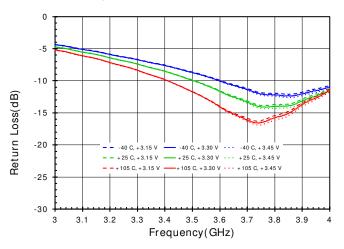

Figure 9. Rx Mode Output Return Loss (High Gain)

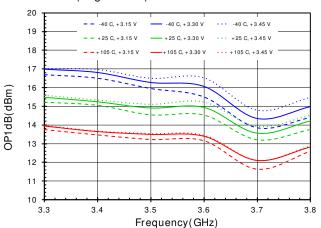

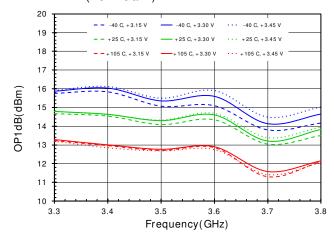

Figure 11. Rx Mode OP1dB vs. Frequency (High Gain)

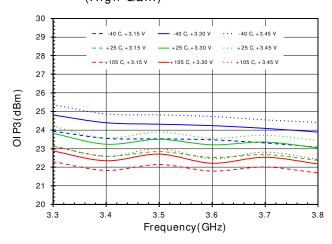

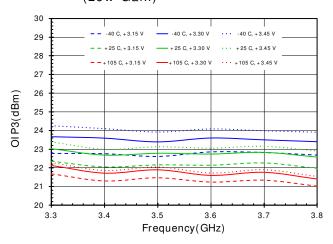

Figure 13. Rx Mode OIP3 vs. Frequency (High Gain)

Figure 10. Rx Mode Output Return Loss (Low Gain)

Figure 12. Rx Mode OP1dB vs. Frequency (Low Gain)

Figure 14. Rx Mode OIP3 vs. Frequency (Low Gain)

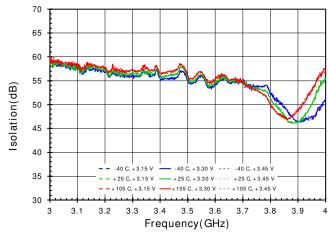

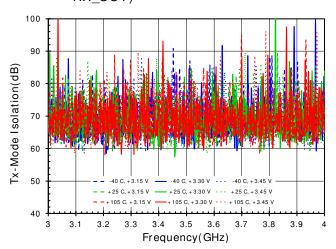

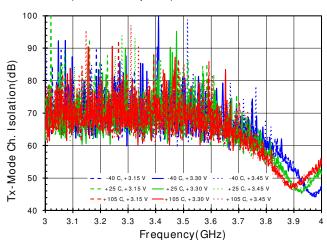

Figure 15. Tx Mode Isolation (SW\_IN to RX\_OUT)

Figure 17. Tx Mode Input Return Loss

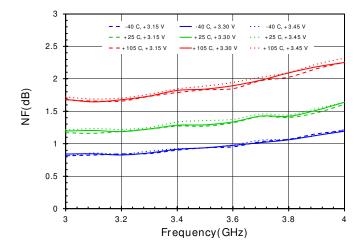

Figure 19. Rx Mode Noise Figure (High Gain)

Figure 16. Tx Mode Channel Isolation (Switch Inputs)

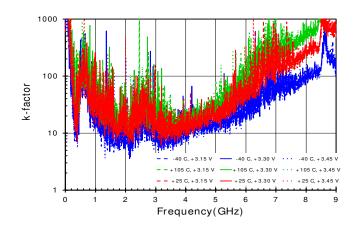

Figure 18. Stability Factor

Figure 20. Rx Mode Noise Figure (Low Gain)

Figure 21. Switching Time from TX to RX Mode

Figure 23. Standby to RX Mode Transient Time

Figure 25. 6dB Gain Reduction Transient Time

Figure 22. Switching Time from RX to TX Mode

Figure 24. RX Mode to Standby Transient Time

Figure 26. 6dB Gain Increase Transient Time

# Programming

Table 14. Gain Step Truth Table

| ATT1_CTRL, ATT2_CTRL | Attenuation Setting |

|----------------------|---------------------|

| Low or NC            | 0dB                 |

| High                 | 6dB                 |

Table 15. Standby and RF Switch Truth Table

In TX Mode, the amplifiers are OFF, but the bias will remain ON for fast turn-on recovery time.

| STBY      | SW_CTRL           | MODE    | Amplifier State |

|-----------|-------------------|---------|-----------------|

| Low or NC | Low or NC         | RX      | ON              |

| Low or NC | High              | TX      | OFF             |

| High      | High or Low or NC | STANDBY | OFF             |

# **Evaluation Kit Picture**

Figure 27. Evaluation Kit: Top View

Figure 28. Evaluation Kit: Bottom View

# Evaluation Kit / Applications Circuit

Figure 29. Electrical Schematic

Table 16. Bill of Material (BOM)

| Part Reference                      | QTY | Description                                      | Manufacturer Part #  | Manufacturer          |

|-------------------------------------|-----|--------------------------------------------------|----------------------|-----------------------|

| R3, R4, R5, R6                      | 4   | 0Ω Jumper 1/10W                                  | ERJ2GE0R00X          | Panasonic             |

| R2, R7                              | 2   | 50Ω termination (0805)                           | PCAN0805E49R9BST5    | VISHAY                |

| C10, C11, C20, C21                  | 4   | Cap 8pF (0402)                                   | GRM1555C1H8R0DA01D   | Murata                |

| C5, C6, C25, C26                    | 4   | Cap 1µF, 10V, X5R (0402)                         | GRM155R61A105KE15D   | Murata                |

| J5                                  | 1   | 2x4 Pin Header                                   | 67996_108HLF         | Digi-Key/Amphenol FCI |

| J1                                  | 1   | 2x2 Pin Header                                   | 67996-104HLF         | Digi-Key/Amphenol FCI |

| J8                                  | 1   | 2x3 Pin Header                                   | 67996-106HLF         | Digi-Key/Amphenol FCI |

| J2, J3, J4, J6, J7, J9,<br>J10, J11 | 8   | SMA Edge Mount                                   | 142-0761-881         | Cinch Connectivity    |

| C12, C13, C14, C15,<br>C16, C17     |     | Do not Install                                   |                      |                       |

| U1                                  | 1   | Dual Path RF Switch with LNA<br>and DVGA 5X5 QFN | F0453BZL LEG32K      | IDT                   |

| SI 10522                            | 1   | Printed Circuit Board                            | F0453B EVKIT SI10522 |                       |

### **Evaluation Kit Operation**

#### Power Supply Setup

Set up a power supply in the voltage range of 3.15V to 3.45V with the power supply output disabled. The voltage is applied by wiring to Pin 1 and 3 of header J1 for CH1\_VDD, and wiring to Pin 1 and 3 of header J8 for CH2\_VDD, as displayed in Figure 30.

Figure 30. Connections of Evaluation Board

### Standby (STBY) Pin

The Evaluation Board can control the F0453B for standby operation. On header J5, the standby pins are pin 2 for CH1 and pin 8 for CH2 as shown in Figure 30. Ground (logic LOW) pins are available to make a connection with a jumper. VDD (logic HIGH) could be wired either from CH1\_VDD of header J1 or CH2\_VDD of header J8.

To place channel 1 in the normal operation mode (on), use one of these options:

- Keep STBY1 open by making no connection on pin 2 of J5, or

- Apply a logic LOW signal to STBY1 by making a connection between pin 1 and pin 2 of J5.

To place channel 1 in the standby mode (off), apply a logic HIGH signal to the STBY1 by making a connection between pin 2 of J5 and pin 1 (or pin 3) of J1.

To place channel 2 in the normal operation mode (on), use one of these options:

- Keep STBY2 open by making no connection on pin 8 of J5, or

- Apply a logic LOW signal to STBY2 by making a connection between pin 7 and pin 8 of J5.

To place channel 2 in the standby mode (off), apply a logic HIGH signal to the STBY2 by making a connection between pin 8 of J5 and pin 1 (or pin 3) of J8.

#### Gain Step Control Setup

To get 6dB gain attenuation for channel 1, make a connection of SMA Connector J4, marked as "CH1\_att\_ctr" in Figure 30, to logic HIGH (see also Error! Reference source not found.). In contrast, if J4 is open or logic LOW the minimum attenuation is obtained for channel 1.

To get 6dB gain attenuation for channel 2, make a connection of SMA Connector J6, marked as "CH2\_att\_ctr" in Figure 30, to logic HIGH. In contrast, if J6 is open or logic LOW the minimum attenuation is obtained for channel 2.

#### Switch Control Pin

To switch channel 1 into TX throw, make a connection of pin 4 of J5, marked as "sw1\_ctr" in Figure 30, to logic HIGH (see also Error! Reference source not found.). In contrast, if pin 4 of J5 is open or logic LOW the result is to switch channel 1 into RX throw.

To switch channel 2 into TX throw, make a connection of pin 6 of J5, marked as "sw2\_ctr" in Figure 30, to logic HIGH. In contrast, if pin 6 of J5 is open or logic LOW the result is to switch channel 2 into RX throw.

#### Mode Control Setup

There are three operation modes as displayed in Table 13. Based on each mode, set up the standby pin and switch control pin as described in Standby (STBY) Pin and in Switch Control Pin. The standby and switch control logic are displayed in the following figure.

Figure 31. Standby and Switch Control Logics

#### Power-On Procedure

Set up the voltage supplies and Evaluation Board as described in Power Supply Setup with the Standby (STBY) Pin set for open or logic LOW, then enable the power supply.

#### Power-Off Procedure

Disable the power supply.

### **Application Information**

#### Power Supplies

A common  $V_{DD}$  power supply should be used for all pins requiring DC power. All supply pins should be bypassed with external capacitors to minimize noise and fast transients. Supply noise can degrade the noise figure, and fast transients can trigger ESD clamps and cause them to fail. Supply voltage change or transients should have a slew rate smaller than  $1V/20\mu s$ . In addition, all control pins should remain at  $0V(\pm 0.3V)$  while the supply voltage ramps up or while it returns to zero.

#### Control Pin Interface

If control signal integrity is a concern and clean signals cannot be guaranteed due to overshoot, undershoot, ringing, etc., the following circuit at the input of each control pin is recommended. This applies to control pins 1, 2, 3, 6, 7, and 8 displayed in Figure 32.

Figure 32. Control Pin Interface Schematic

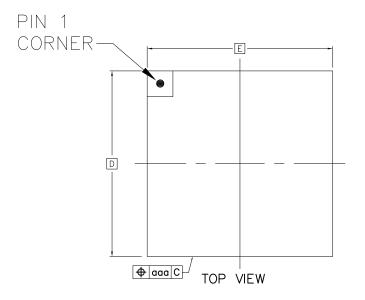

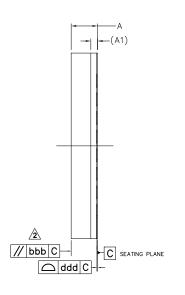

## Package Outline Drawings

The package outline drawings are located at the end of this document and are accessible from the Renesas website (see package links in Ordering Information). The package information is the most current data available and is subject to change without revision of this document.

## Ordering Information

| Part Number | Package                          | MSL Rating | Carrier Type | Temp. Range    |

|-------------|----------------------------------|------------|--------------|----------------|

| F0453BLEGK  | 5.0 × 5.0 × 0.8 mm <u>32-LGA</u> | MSL3       | Tray         | -40° to +105°C |

| F0453BLEGK8 | 5.0 × 5.0 × 0.8 mm <u>32-LGA</u> | MSL3       | Reel         | -40° to +105°C |

| F0453BEVBK  | Evaluation Board                 |            |              |                |

# Marking Diagram

IDTF04 53BLEGK #YYWW\$

LOT

- Lines 1 and 2 indicate the part number

- Line 3 indicates the following:

- "#" denotes stepping

- "YY" is the last two digits of the year; "WW" is the work week number when the part was assembled.

- "\$" denotes the mark code.

## **Revision History**

| Revision Date    | Description of Change                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| July 13, 2021    | <ul> <li>Updated the V<sub>IL</sub> specification in Table 4.</li> <li>Completed other minor changes</li> </ul> |

| December 9, 2019 | Updated to reflect 3.3GHz specifications.                                                                       |

| August 29, 2019  | <ul> <li>Updated to reflect 4GHz specifications</li> <li>Completed other minor improvements</li> </ul>          |

| March 20, 2019   | Initial release.                                                                                                |

|     | REVISIONS                 |              |          |

|-----|---------------------------|--------------|----------|

| REV | DESCRIPTION               | DATE CREATED | AUTHOR   |

| 01  | MODIFIED DIMENSION "A"    | 2/8/17       | SRIKANTH |

| 00  | INITIAL RELEASE           | 1/9/17       | SRIKANTH |

|     | REFER TO DCP FOR OFFICIAL | RELEASE DATE |          |

| 9 E2 — 16 — 17 L  |

|-------------------|

| 0.10 17           |

|                   |

| e /2 D2\$0.1\$CAB |

| nX b • 0.10 CAB   |

|                   |

| 32 25 1           |

| BOTTOM VIEW       |

#### NOTES:

- 1. ALL DIMENSIONS IN MM.

- PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

| SYMBOL | DIMENSION |      |      |

|--------|-----------|------|------|

|        | MIN.      | NOM. | MAX. |

| Α      | 0.64      | _    | 0.80 |

| A1     | 0.18 REF. |      |      |

| D      | 5.0 BSC   |      |      |

| E      | 5.0 BSC   |      |      |

| b      | 0.20      | 0.25 | 0.30 |

| L      | 0.35      | 0.40 | 0.45 |

| L1     | 0.05      | 0.10 | 0.15 |

| е      | 0.5 BSC   |      |      |

| D2     | 1.95      | 2.00 | 2.05 |

| E2     | 1.95      | 2.00 | 2.05 |

| aaa    | 0.10      |      |      |

| bbb    | 0.10      |      |      |

| ddd    | 0.08      |      |      |

| TOLERANCES UNLESS SPECIFII DECIMAL AND XX± ± XXXX± XXXX± | GULAR | IDT™<br>ww.IDT.com            | 6024 Silve<br>San Jose,<br>PHONE: (4<br>FAX: (408 | CA 9513<br>08) 727- | 8<br>6116 |

|----------------------------------------------------------|-------|-------------------------------|---------------------------------------------------|---------------------|-----------|

| ^^^                                                      | TITLE | TITLE LEGGE BLOWNER OUT IN    |                                                   |                     |           |

|                                                          | 11116 | TITLE LEG32 PACKAGE OUTLINE   |                                                   |                     |           |

|                                                          |       | 5.0 x 5.0 mm BODY             |                                                   |                     |           |

|                                                          |       |                               |                                                   |                     |           |

|                                                          |       | 0.8 mm Thick, 0.5mm PITCH LGA |                                                   |                     |           |

|                                                          | SIZE  | DRAWING No.                   |                                                   |                     | REV       |

|                                                          | C     | PSC-4684                      |                                                   |                     | 01        |

|                                                          | DO N  | OT SCALE DRAWING              |                                                   | SHEET               | 1 OF 2    |

| REVISIONS |                                        |              |          |  |  |

|-----------|----------------------------------------|--------------|----------|--|--|

| REV       | DESCRIPTION                            | DATE CREATED | AUTHOR   |  |  |

| 01        | MODIFIED DIMENSION "A"                 | 2/8/17       | SRIKANTH |  |  |

| 00        | INITIAL RELEASE                        | 1/9/17       | SRIKANTH |  |  |

|           | REFER TO DCP FOR OFFICIAL RELEASE DATE |              |          |  |  |

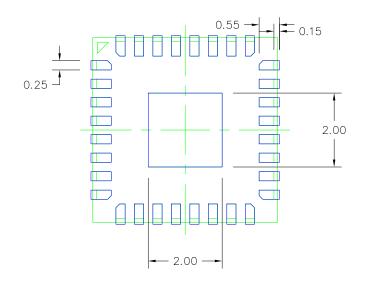

RECOMMENDED LAND PATTERN DIMENSION

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MM. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- 3. COMPONENT OUTLINE SHOWS FOR REFERENCE IN GREEN.

- 4. LAND PATTERN IN BLUE. NSMD PATTERN ASSUMED.

- 5. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| TOLERANCES<br>UNLESS SPE<br>DECIMAL<br>XX±<br>XXX±<br>XXXX± |  | **San Jose, CA 95138 **PHONE: (408) 727–6116 **WWW.IDT.com**FAX: (408) 492–8674  **TITLE LEG32 PACKAGE OUTLINE 5.0 x 5.0 mm BODY 0.8 mm Thick, 0.5mm PITCH LGA |                         |         |           |

|-------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|-----------|

|                                                             |  |                                                                                                                                                                |                         |         |           |

|                                                             |  | SIZE<br>C                                                                                                                                                      | drawing No.<br>PSC-4684 |         | REV<br>01 |

|                                                             |  | DO NO                                                                                                                                                          | OT SCALE DRAWING        | SHEET 2 | OF 2      |