"Spansion, Inc." and "Cypress Semiconductor Corp." have merged together to deliver high-performance, high-quality solutions at the heart of today's most advanced embedded systems, from automotive, industrial and networking platforms to highly interactive consumer and mobile devices. The new company "Cypress Semiconductor Corp." will continue to offer "Spansion, Inc." products to new and existing customers.

## **Continuity of Specifications**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

## **Continuity of Ordering Part Numbers**

Cypress continues to support existing part numbers. To order these products, please as any the Ordering Part Numbers listed in this document. in this document.

For More Information Please contact your local sales office for additional information about Cypres products and solutions.

ut Cypy Recommended for Not Recommended

# S29WS512R, S29WS256R, S29WS128R

# 512/256/128 Mb (32/16/8M x 16 bit) 1.8 V S29WS-R MirrorBit® Flash

This product family has been retired and is not recommended for designs. For new and current designs, S29WS512P, S29WS256P, and S29WS128P supersedes S29WS512R, S29WS256R, and S29WS128R respectively. This is the factoryrecommended migration path. Please refer to the S29WS-P data sheet for specifications and ordering information.

Availability of this document is retained for reference and historical purposes only.

## Features

- 65 nm MirrorBit Technology

- Single supply 1.8 V read/program/erase (1.70 V 1.95 V)

- Wireless Temperature range (-25°C to +85°C)

- 16-bit (Word) data bus width

- Simultaneous Read/Write (SRW) operation

- Read from one bank while programming or erasing in another bank

- Memory array is divided into 16 equal size banks

- Programmable linear (8/16) with wrap around and continuos burst read modes

- RDY output for data transfer flow control

- Sector Frase

- Four 32 Kbyte sectors at top or bottom of memory array - All other sectors are 128 Kbytes

- Write Buffer Programming up to 64 -byte groups

- write operation status register bits indicate program and erace operation completion Program-Erase Endurance

- 100,000 cycles per sector (typical)

- 10-year data retention (typical)

- Data Protection

- Low V<sub>CC</sub> write inhibit

- Secured Silicon Sector

- 512 Bytes of Secured Silicon Sector region consisting of One Time Program (OTP) area of 256 bytes each for factory and customer

- Hardware Sector Protection (via ACC pin)

- All sectors protected when ACC input is at VIL

- Boot code controlled sector protection - A range of sectors may be protected to prevent program and erase

- unit the hext hardware reset or power is removed from the device Dynamic sector protection

- All sectors are unprotected at power on for simplified system production test & programming

- A single command is used to protect all sectors from program or erase

- A single sector at a time may be unprotected by a command to enable programming or erase.

- Common Flash Interface (CFI) data structure

- Offered Packages

- 512/256/128R: 84-ball FBGA (11.6mm x 8mm) VBH084

# **Performance Characteristics**

| Read Access Times (maximum values)            |     |  |  |  |  |  |  |

|-----------------------------------------------|-----|--|--|--|--|--|--|

| Speed Option (MHz) 1                          |     |  |  |  |  |  |  |

| Synch. Internal Access, ns (t <sub>IA</sub> ) | 75  |  |  |  |  |  |  |

| Synch. Burst Access, ns (t <sub>BACC</sub> )  | 7.6 |  |  |  |  |  |  |

| Asynch. Access Time, ns (t <sub>ACC</sub> )   | 80  |  |  |  |  |  |  |

| Current Consumption (typical values)                 |       |  |  |  |  |  |  |

|------------------------------------------------------|-------|--|--|--|--|--|--|

| Burst Read @ 104 MHz (I <sub>CCB</sub> )             | 32 mA |  |  |  |  |  |  |

| Simultaneous Operation @ 104 MHz (I <sub>CC5</sub> ) | 52 mA |  |  |  |  |  |  |

| Program (I <sub>CC2</sub> )                          | 20 mA |  |  |  |  |  |  |

| Erase (I <sub>CC2</sub> )                            | 20 mA |  |  |  |  |  |  |

| Standby Mode (I <sub>CC3</sub> )                     | 20 µA |  |  |  |  |  |  |

| Typical Program & Erase Times (typical values)                 |         |

|----------------------------------------------------------------|---------|

| Effective Write Buffer Programming (V <sub>CC</sub> ) Per Word | 12.5 µs |

| Effective Write Buffer Programming (VACC) Per Word             | 8 µs    |

| Sector Erase (32 KByte Sector) (V <sub>CC</sub> )              | 0.35 s  |

| Sector Erase (128 KByte Sector) (V <sub>CC</sub> )             | 0.8 s   |

Not Recommended for New Design

# Contents

| Performance Characteristics       3         1. General Description       5         2. Ordering Information       5         2.1 Valid Combinations       5         3. Input/Output Descriptions & Logic Symbol       6         4. Block Diagrams       7         5. Physical Dimensions/Connection Diagrams       7         5. Physical Dimensions/Connection Diagrams       7         5. Special Handling Instructions for FBGA Package       7         5.3 Connection Diagrams and Physical Dimensions       8         6. Product Overview       10         7. Address Space Maps       10         7. Address Space Maps       10         7. Address & Quantity Nomenclature       11         7.2 Flash Memory Array       12         7.3 Device ID and CFI (ID-CFI)       21         8. Device Operations       23         8.1 Device Bus Operations       24         8.2 Asynchronous Read       25         8.4 Synchronous (Burst) Read Mode and Configuration Register       26         8.5 Status Register       34         8.6 Blank Check       34         8.7 Simultaneous Read/Write       35         8.8 Writing Commands/Command Sequences       35 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.Ordering Information52.1Valid Combinations53.Input/Output Descriptions & Logic Symbol64.Block Diagrams75.Physical Dimensions/Connection Diagrams75.Physical Dimensions/Connection Diagrams75.1Related Documents75.2Special Handling Instructions for FBGA Package75.3Connection Diagrams and Physical Dimensions86.Product Overview107.Address Space Maps107.1Data Address & Quantity Nomenclature117.2Flash Memory Array127.3Device ID and CFI (ID-CFI)218.Device Operations238.1Device Bus Operations248.2Asynchronous Read248.3Page Mode Read25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1       Valid Combinations       5         3.       Input/Output Descriptions & Logic Symbol       6         4.       Block Diagrams       7         5.       Physical Dimensions/Connection Diagrams       7         5.1       Related Documents       7         5.2       Special Handling Instructions for FBGA Package       7         5.3       Connection Diagrams and Physical Dimensions       8         6.       Product Overview       10         7.       Address Space Maps       10         7.1       Data Address & Quantity Nomenclature       11         7.2       Flash Memory Array.       12         7.3       Device ID and CFI (ID-CFI)       21         8.       Device Operations       23         8.1       Device Bus Operations       24         8.2       Asynchronous Read       24         8.3       Page Mode Read       25                                                                                                                                                                                                                                                                                                     |

| 4.       Block Diagrams       7         5.       Physical Dimensions/Connection Diagrams       7         5.1       Related Documents       7         5.2       Special Handling Instructions for FBGA Package       7         5.3       Connection Diagrams and Physical Dimensions       8         6.       Product Overview       10         7.       Address Space Maps       10         7.1       Data Address & Quantity Nomenclature       11         7.2       Flash Memory Array       12         7.3       Device ID and CFI (ID-CFI)       21         8.       Device Operations       23         8.1       Device Bus Operations       24         8.2       Asynchronous Read       24         8.3       Page Mode Read       25                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.       Physical Dimensions/Connection Diagrams       7         5.1       Related Documents       7         5.2       Special Handling Instructions for FBGA Package       7         5.3       Connection Diagrams and Physical Dimensions       8         6.       Product Overview       10         7.       Address Space Maps       10         7.1       Data Address & Quantity Nomenclature       11         7.2       Flash Memory Array       12         7.3       Device ID and CFI (ID-CFI)       21         8.       Device Operations       23         8.1       Device Bus Operations       24         8.2       Asynchronous Read       24         8.3       Page Mode Read       25                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.1Related Documents75.2Special Handling Instructions for FBGA Package75.3Connection Diagrams and Physical Dimensions86.Product Overview107.Address Space Maps107.Address & Quantity Nomenclature117.2Flash Memory Array127.3Device ID and CFI (ID-CFI)218.Device Operations238.1Device Bus Operations248.2Asynchronous Read248.3Page Mode Read25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.Address Space Maps107.1Data Address & Quantity Nomenclature117.2Flash Memory Array127.3Device ID and CFI (ID-CFI)218.Device Operations238.1Device Bus Operations248.2Asynchronous Read248.3Page Mode Read25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1Data Address & Quantity Nomenclature117.2Flash Memory Array127.3Device ID and CFI (ID-CFI)218.Device Operations238.1Device Bus Operations248.2Asynchronous Read248.3Page Mode Read25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8.1Device Bus Operations248.2Asynchronous Read248.3Page Mode Read25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>8.4 Synchronous (Burst) Read Mode and Configuration<br/>Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>9.</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5 | Sector Protection/Unprotection<br>Sector Lock/Unlock Command<br>Sector Lock Range Command<br>Hardware Data Protection Methods<br>SSR Lock<br>Secure Silicon Region | 43<br>43<br>44<br>44 |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 10.                                          | Power Conservation Modes                                                                                                                                           |                      |

|                                              | Standby Mode                                                                                                                                                       |                      |

|                                              | Automatic Sleep Mode                                                                                                                                               |                      |

| 10.3                                         | Output Disable (OE#)                                                                                                                                               | 46                   |

| 11.                                          | Electrical Specifications                                                                                                                                          | 47                   |

| 11.1                                         | Absolute Maximum Rating                                                                                                                                            | 47                   |

| 11.2                                         | Operating Ranges<br>DC Characteristics<br>Capacitance<br>AC Test Conditions                                                                                        | 47                   |

| 11.3                                         | DC Characteristics                                                                                                                                                 | 48                   |

| 11.4                                         | Capacitance.                                                                                                                                                       | 49                   |

| 11.5                                         | AC Test Conditions                                                                                                                                                 | 49                   |

| 11.6                                         | Key to Switching Waveforms                                                                                                                                         | 50                   |

|                                              | V <sub>CC</sub> PowerDp                                                                                                                                            |                      |

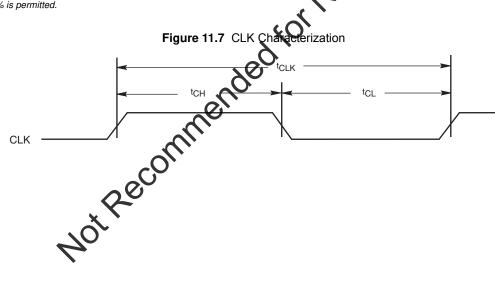

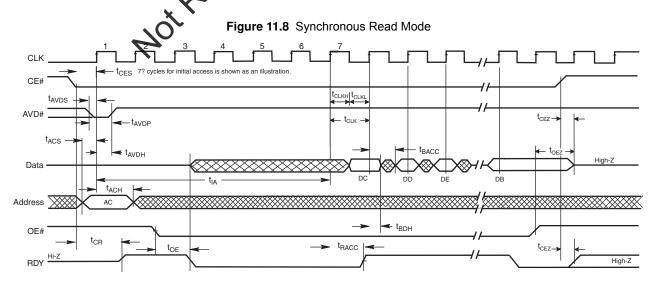

| 11.8                                         | CLK Characterization                                                                                                                                               | 51                   |

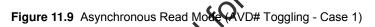

| 11.9                                         | AC characteristics                                                                                                                                                 | 52                   |

| 12.                                          | Appendix                                                                                                                                                           | 63                   |

| 12.1                                         | command Definitions                                                                                                                                                | 63                   |

| 12.2                                         | Device ID and Common Flash Memory Interface                                                                                                                        |                      |

|                                              | Address Map                                                                                                                                                        | 65                   |

| 13.                                          | Revision History                                                                                                                                                   | 71                   |

|                                              | -                                                                                                                                                                  |                      |

# 1. General Description

The Spansion S29WS512/256/128R are Mirrorbit flash products fabricated on 65 nm process technology. These burst mode flash devices are capable of performing simultaneous read and write operations with zero latency on two separate banks using separate data and address pins. These products can operate up to 104 MHz and use a single V<sub>CC</sub> of 1.7 V to 1.95 V that makes them ideal for today's demanding wireless applications requiring higher density, better performance and lowered power consumption.

# 2. Ordering Information

This product family has been retired and is not recommended for designs. For new and current designs, S29WS512P, S29WS256P, and S29WS128P supersedes S29WS512R, S29WS256R, and S29WS128R respectively. This is the factory-recommended migration path. Please refer to the S29WS-P data sheet for specifications and ordering information.

Availability of this document is retained for reference and historical purposes only.

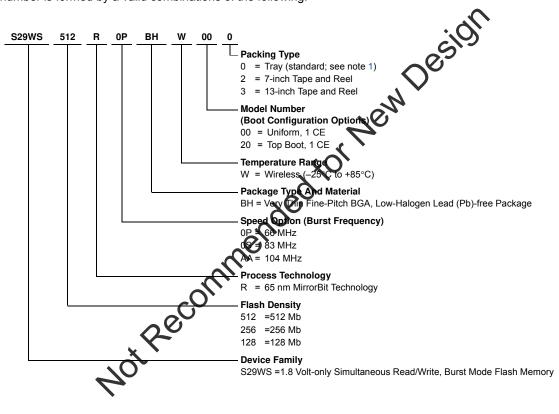

The order number is formed by a valid combinations of the following:

## 2.1 Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| S2                           | 9WS-R Valid (   | Combinations (Notes 1, 2)                      |                     |                  |                          |                   |

|------------------------------|-----------------|------------------------------------------------|---------------------|------------------|--------------------------|-------------------|

| Base Ordering<br>Part Number | Speed<br>Option | Package Type, Material, &<br>Temperature Range | Packing<br>Type     | Model<br>Numbers | Package Type<br>(Note 2) | Product<br>Status |

| S29WS512R                    |                 |                                                |                     |                  | 11.6 mm x 8 mm           |                   |

| S29WS256R                    | 0P, 0S, AA      | BHW (Low-Halogen, Lead<br>(Pb)-free)           | 0, 2, 3<br>(Note 1) | 00, 20           | 84-ball                  | Advance           |

| S29WS128R                    |                 | ()                                             | (11010-1)           |                  | MCP-Compatible           |                   |

Notes:

1. Type 0 is standard. Specify other options as required.

2. BGA package marking omits leading S29 and packing type designator from ordering part number.

# 3. Input/Output Descriptions & Logic Symbol

Table identifies the input and output package connections provided on the device.

### Table 3.1 Input/Output Descriptions

| Symbol           | Туре       | Description                                                                                                                                                                                                                                                                      |

|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amax – A0        | Input      | Higher order address lines. Amax = A24 for WS512R, A23 for WS256R, A22 for WS128R                                                                                                                                                                                                |

| DQ15 – DQ0       | I/O        | Data input/output                                                                                                                                                                                                                                                                |

| F1-CE#           | Input      | Flash-1 Chip Enable. Asynchronous relative to CLK. Used to select the first portion of the flash device address space that can be directly selected by one host chip enable signal.                                                                                              |

| F2-CE#           | Input      | Flash-2 Chip Enable. Asynchronous relative to CLK. Used to select the first portion of the flash device address space that can be directly selected by one host chip enable signal.                                                                                              |

| OE#              | Input      | Output Enable. Asynchronous relative to CLK for the Burst mode                                                                                                                                                                                                                   |

| WE#              | Input      | Write Enable                                                                                                                                                                                                                                                                     |

| V <sub>CC</sub>  | Supply     | Device Power Supply                                                                                                                                                                                                                                                              |

| V <sub>CCQ</sub> | Supply     | Input/Output Power Supply (must be ramped simultaneously with V <sub>CC</sub> )                                                                                                                                                                                                  |

| V <sub>SS</sub>  | Supply     | Ground                                                                                                                                                                                                                                                                           |

| NC               | No Connect | No Connected internally                                                                                                                                                                                                                                                          |

| RDY              | Output     | Ready. Indicates when valid burst data is ready to be read                                                                                                                                                                                                                       |

| CLK              | Input      | The first rising edge of CLK in conjunction with AVD# low latence address input and activates burst mode operation. After the initial word is output, subsequent rising edges of CLK increment the internal address counter. CLK should remain low during asynchronous access    |

| AVD#             | Input      | Address Valid input. Indicates to device that the valid address is present on the address inputs. $V_{IL}$ = for asynchronous mode, indicates valid address; for burst mode, cause staring address to be latched on rising edge of CLK. $V_{IH}$ = device ignores address inputs |

| RESET#           | Input      | Hardware Reset. Low = device resets and returns to reading array data.                                                                                                                                                                                                           |

| ACC              | Input      | Accelerated input. At $V_{IL}$ , disables all program and experimentations. Should be at $V_{IH}$ for all other polyinons.                                                                                                                                                       |

| RFU              | Reserved   | Reserved for future use                                                                                                                                                                                                                                                          |

Not Record

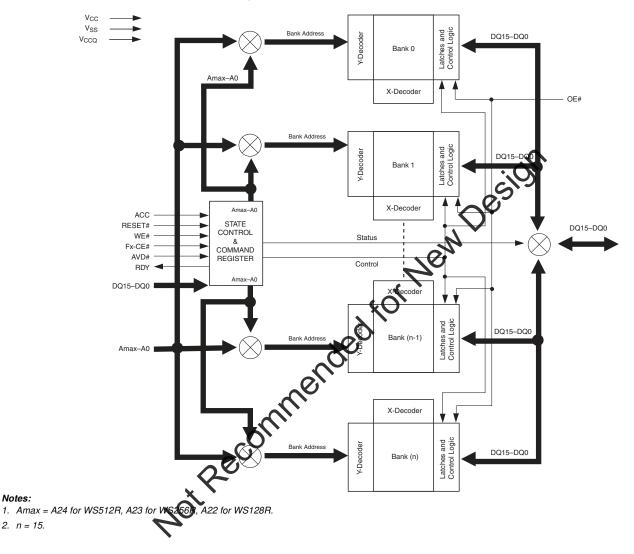

# 4. Block Diagrams

Figure 4.1 Simultaneous Operation Circuit

# 5. Physical Dimensions/Connection Diagrams

This section shows the I/O designations and package specifications.

## 5.1 Related Documents

The following documents contain information related to this family of flash devices. Click on the title or go to www.spansion.com to download the PDF file, or request a copy from your sales office.

Considerations for X-ray Inspection of Surface-Mounted Flash Integrated Circuits

# 5.2 Special Handling Instructions for FBGA Package

Special handling is required for flash memory products in FBGA packages.

Flash memory devices in FBGA packages may be damaged if exposed to ultrasonic cleaning methods. The package and/or data integrity may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

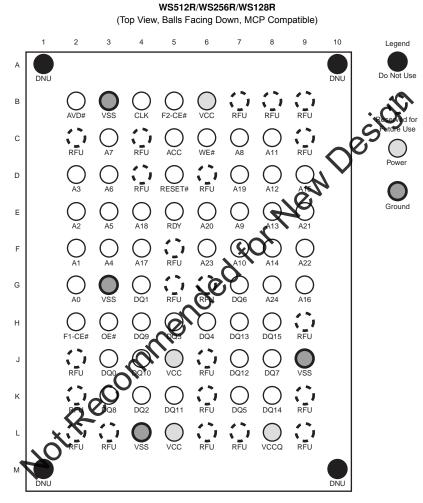

# 5.3 Connection Diagrams and Physical Dimensions

Figure 5.1 84-ball Fine-Pitch Ball Grid Array

#### Notes

- 1. Ball G8 is RFU on the WS256R.

- 2. Ball G8 is A24 on densities  $\geq$  256 Mbit.

- 3. Address signals numbered greater than Amax of a particular device are reserved for future use and only indicate where the higher order address will be in higher density members of related or future family devices.

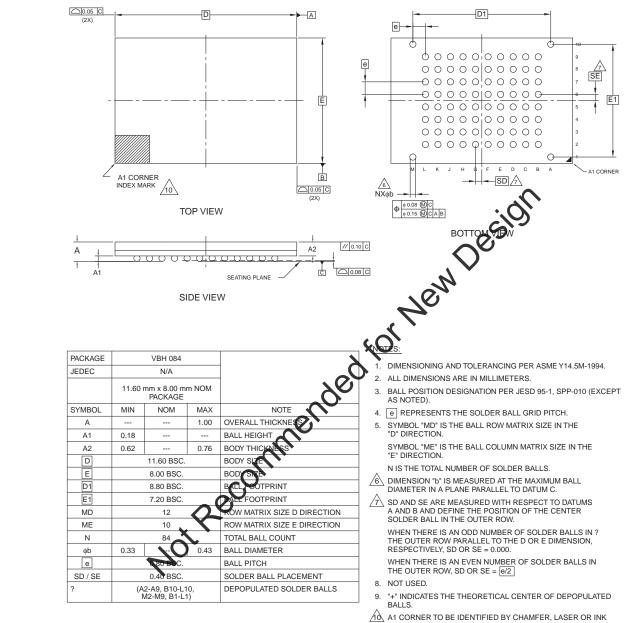

## VBH084—84-ball Fine-Pitch Ball Grid Array (FBGA) 11.6 x 8 mm MCP Compatible Package

MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

3339 \ 16-038.25b

#### Note:

1. BSC is an ANSI standard for Basic Space Centering.

# 6. Product Overview

The S29WS-R family consists of 128 Mbit to 1 Gbit, 1.8-V only, simultaneous read/write, burst-mode, flash devices. These devices have a 16 bit (word) wide data bus. All read accesses provide 16 bits of data on each bus transfer cycle. All writes take 16 bits of data from each bus transfer cycle.

| Device    | Mbits | Mbytes | Mwords | Banks | Mbytes / Bank |

|-----------|-------|--------|--------|-------|---------------|

| S29WS128R | 128   | 16     | 8      | 16    | 1             |

| S29WS256R | 256   | 32     | 16     | 16    | 2             |

| S29WS512R | 512   | 64     | 32     | 16    | 4             |

The flash memory array is divided into banks as shown in the above table. A bank is the address range within which one program, or erase operation may be in progress at the same time as one read operation is in progress in any other bank of the memory. This multiple bank structure enables Simultaneous Read and Write (SRW) so that code may be executed or data read from one bank while a group of data is programmed, or erased as a background task in one other bank.

Each bank is divided into sectors. A sector is the minimum address range of data which can be eased to an all Ones state. There are four 32 Kbyte sectors which are located either at the bottom or top of the memory array depending on the device model purchased. These are called boot sectors because they are often used for holding boot core or parameters that need to be protected or erased separately from other data in the flash array. All other sectors are a uniform size of 128 Kbytes.

Programming is done via a 64 Byte write buffer. It is possible to program from one to 2 words (64 bytes) in each programming operation.

The S29WS family is capable of continuous, synchronous burst read or linear read (8- or 16-word aligned group) with wrap around. A wrapped burst begins at the initial location and continues to the end of a 8- or 16-word aligned group then "wraps-around" to continue at the beginning of the 8, or 16-word aligned group. The burst completes with the last word before the initial location. Word wrap around burst is generally used for processor cache line fill.

# 7. Address Space Maps

There are five address spaces within each device:

- A Non-Volatile Flash Memory Array used to storage of data that may be randomly read and reprogrammed

- A Read Only Memory Array used for factory programmed permanent device characteristics information. This area contains the Device Identification (ID) and Common Flash Interface (CFI) information.

- A One Time Programmable A One Time Programmable A One Time Programmable permanent data, and customer programmable permanent data. This is called the Secure Silicon Region (SSR).

- An OTP location used to permanently protect the SSR. This is call the SSR Lock.

- A volatile register used to configure device behavior options. This is called the Configuration Register.

The main Flash Memory Array is the primary and default address space but, it may be partially overlaid by the other four address spaces with one alternate address space available at any one time. The location where the alternate address space is overlaid is defined by the address provided in the command that enables each overlay. The portion of the command address that is sufficient to select a sector is used to select the sector that is overlaid by an alternate Address Space Overlay (ASO).

Any address range, within the overlaid sector, not defined by an overlay address map, is reserved for future use. All read accesses outside of an address map within the selected sector, return non-valid data. The locations will display actively driven data but the meaning of whatever ones or zeros appear are not defined.

There are three operation modes for each bank that determine what portions of the address space are readable at any given time:

- Read Mode

- Embedded Algorithm (EA) Mode

- Address Space Overlay (ASO) Mode

Each bank of the device can be in any operation mode but, only one bank can be in EA or ASO mode at any one time.

In Read Mode a Flash Memory Array bank may read directly by asynchronous or synchronous accesses from the host system bus. The Flash Control Unit (CU) puts all banks in Read mode during Power-on, a Hardware Reset, after a Command Reset, or after a bank is returned to Read mode from EA mode. A bank with a suspended EA is considered to be returned to Read mode even though some or all of the data in the bank may be in an invalid state and thus not useful if read.

In EA mode the flash memory array data in a bank is stable but undefined, and effectively unavailable for read access from the host system. While in EA mode the bank is used by the CU in the execution of commands. Typical EA mode operations are programming or erasing of data in the flash array. All other banks are available for read access while the one bank is in EA mode. This ability to read from one bank while another bank is used in the execution of a command is called Simultaneous Read and Write (SRW) and allows for continued operation of the system via the reading of data or execution of code from other banks while one bank is programming or erasing data as a relatively long time frame background task.

In ASO mode, one of the overlay address spaces are overlaid in a bank (entered). That bank is in ASO mode and no other bank may be in EA or ASO mode. All EA activity must be completed before entering any ASO mode. A command for entering an EA or ASO mode while another bank is in EA or ASO mode will be ignored.

While an ASO mode is active (entered) in a bank, a read for flash array data to any other bank is aboved. ASO mode selects a specific sector for the overlaid address space. Other sectors in the ASO bank still provide flash aread data and may be read during ASO mode.

The ASOs are functionally tied to the lowest address bank. The commands used to overall these areas must select a sector address within the lowest address bank.

While SSR Lock, SSR, or Configuration Register is overlaid only the SSR Lock, SSC or Configuration Register respectively may be programmed in the overlaid sector. While any of these ASO areas are being programmed the ASO bank switches to EA mode. The ID/CFI and factory portion of the SSR ASO is not customer programmable.

The address nomenclature used in this document is a shorthand form that shows addresses are formed from a concatenation of high order bits, sufficient to select a Sector Address (SA), with low order bits to select a location within the sector. When in Read mode and reading from the flash array the entire address is used to select a specific word for asynchronous read or the starting word address of a burst read. When writing a command, the address the between SA and the command specified least significant bits must be Zero to allow for future extension of an overlay address map.

# 7.1 Data Address & Quantity Nomenclature

A **Bit** is a single One or Zero data value. A **Byte** is a group of 8 bits aligned on an 8 bit address boundary. A **Word** is a group of 16 bits aligned on a 16 bit address boundary. A **Koye** (KB) is 1024 Bytes (not 1000 Bytes).

Throughout this document **quantities of data are generally expressed in terms of bytes**. Example: most sectors have 128 Kbytes of data and is written as 128 Kbytes of 126 KB. Addresses are also expressed in byte units. A 128 Kbyte sector has an address range from 00000h to 1FFFFh Byte locations. Byte units are used because most host systems and software for these systems use byte resolution addresses. Software & hardware developers most often calculate code and data sizes in terms of bytes, so this is more familiar terminology than deveribing data sizes in bits or words. In general, data units will not be abbreviated if possible so that full unit names of Byte, Word, or bit are used. However, there may be cases where capital B is used for byte units and lower case b is used for bit units, in situations where space is limited such as in table column headers.

In some cases data quantities will also be expressed in word or bit units in addition to the quantity shown in bytes. This may be done as an aid to readers familiar with prior device generation documentation which often provided only word or bit unit values. Word units may also be used to emphasize that, in the memory devices described in this documentation, data is always exchanged with the host system in word units. Each bus cycle transfer of read or write data on the host system bus is a transfer 16 bits of data. A read bus cycle is always a 16 bit wide transfer of data to the host system whether the host system chooses to look at all the bits or not. A write bus cycle is always a transfer of 16 bits to the memory device and the device will store all 16 bits to a register. In the case of a program operation all 16 bits of each word to be programmed will be stored in the flash array.

Because data is always transferred in word units, the memory devices being discussed use only the address signals from the system necessary to select words. Most host systems use address line A0 to select bytes and a1 to select words. Flash memories with word wide data paths have traditionally started their address signal numbering with A0 being the selector for words because a byte select input is not needed. So, system address a[max] to a1 are connected to flash A[max] to A0.

In prior generation flash documentation, address values used in commands to the flash were documented from the viewpoint of the flash device - the bit pattern appearing on flash address inputs A10 to A0. However, most software is written with addresses expressed in bytes. This means the address patterns shown in flash command tables have traditionally been shifted by one bit to

~

express them as byte address values in flash control programs. Example: a prior generation flash data sheet would show a command write of data value xxA0h to address 555h; this is an address pattern of 101010101010 b on flash address inputs A10 to A0; but software would define this as a byte address value of AAAh since the least significant address bit is not used by the flash); which is 101010101010 b on system address bus a11 to a0. Because system a11 to a1 is connected to flash A10 to A0 the flash word address of 555h and the system byte address of AAAh provides the same bit pattern on the same address inputs. Because all address values are being documented as system byte addresses, that are more familiar to software writers, the command tables have addresses that are shifted from those shown in prior generation devices.

## 7.2 Flash Memory Array

The Non-Volatile Flash Memory Array is organized as shown in the following tables. Devices have either all uniform size sectors or four smaller sectors at either the top or bottom of the device.

| System Address Signals  | a11 | a10 | a9           | a8  | а7  | a6 | a5  | a4 | a3  | a2 |    | a0 |

|-------------------------|-----|-----|--------------|-----|-----|----|-----|----|-----|----|----|----|

| System Byte Address Hex |     | ļ   | Ą            |     | A   |    |     |    |     | 0  | 0  |    |

| Binary Pattern          | 1   | 0   | 1            | 0   | 1   | 0  | 1   | 0  | 1   | 3  | 1  | 0  |

| Flash Word Address Hex  |     | 5   |              |     |     | 5  |     |    |     | 5  |    |    |

| Flash Address Signals   | A10 | A9  | A8           | A7  | A6  | A5 | A4  | A3 | A N | A1 | A0 |    |

|                         |     | 4°  | <sup>e</sup> | cor | nne | A5 | 201 | 01 |     |    |    |    |

Table 7.1 System Versus Flash View of Address

| Bank Size<br>(Mbit) | Sector<br>Count | Sector<br>Size<br>(Kbyte) | Bank | Sector<br>Range | Address Range<br>(word) | Address Range (byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Notes       |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|---------------------|-----------------|---------------------------|------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--|--|-------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|---|-------------|--|--|--|--|--|--|--|--|---|-------------|--|----|----------------|

|                     |                 |                           |      | SA000           | 000000h-003FFFh         | 000000h-007FFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     | 4               | 32                        |      | SA001           | 004000h-007FFFh         | 008000h-00FFFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     | 4               | 52                        |      | SA002           | 008000h-00BFFFh         | 010000h-017FFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

| 32                  |                 |                           | 0    | SA003           | 00C000h-00FFFFh         | 018000h-01FFFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     |                 |                           |      | SA004           | 010000h-01FFFFh         | 020000h-03FFFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     | 31              | 128                       |      | ÷               |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     |                 |                           |      | SA034           | 1F0000h-1FFFFFh         | 3E0000h-3FFFFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     |                 |                           | 1    | SA035-SA066     | 200000h-3FFFFFh         | 400000h-7FFFFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     |                 |                           | 2    | SA067-SA098     |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     |                 |                           |      |                 |                         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SA097-SA130 |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

|                     |                 |                           |      |                 |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4           | SA131-SA162 |  |  | Address to Sector |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  |   |             |  |    |                |

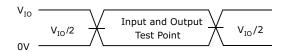

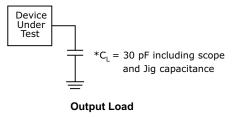

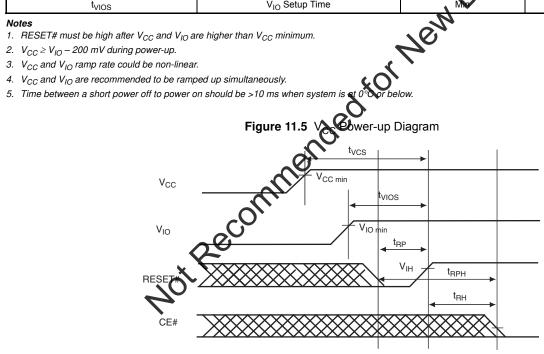

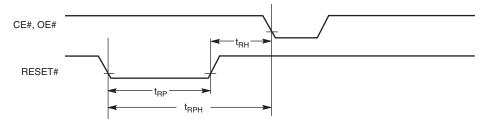

|                     |                 |                           |      |                 |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |             |  |  |                   |  |  |  |  |  |  |  |  |  |  |  |  |  |   |             |  |  |  |  |  |  |  |  | 5 | SA163-SA194 |  | ÷. | Ending Address |