## MIC2155

### Two-Phase Single-Output PWM Synchronous Buck Control IC

### **Features**

- · Synchronous Buck Control IC with Outputs Switching 180 Degrees Out of Phase

- Remote Sensing with Internal Differential Amplifier

- 4.5V-to-14.5V Input Voltage Range

- Adjustable Output Voltages down to 0.7V

- 1% Output Voltage Accuracy

- · Starts up into a Pre-biased Output

- 500 kHz PWM Operation

- Adaptive Gate Drive allows Efficiencies of over

- · Adjustable Current Limit with no Sense Resistor

- · Senses Low-Side MOSFET Current

- · Internal Drivers allow 25A per Phase

- · Power Good Output allows Simple Sequencing

- · Dual Enable Pins with Micro-Power Shutdown and UVLO

- · Programmable Soft-Start Pin

- · Output Overvoltage Protection

- · Works with Ceramic Output Capacitors

- · Multi-Input Supply Capability

- Single-Output High-Current Capability with Master/Slave Current Sharing

- **External Synchronization**

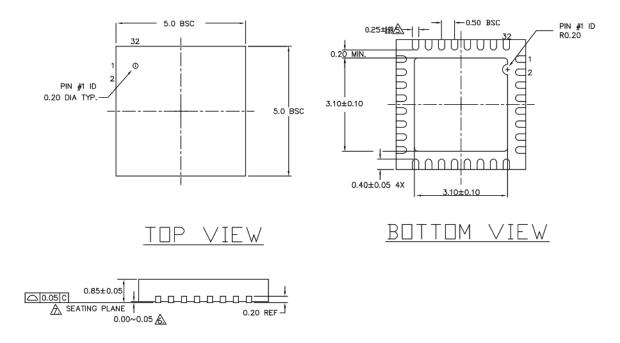

- Small Footprint 32-Pin 5 mm × 5 mm VQFN

- Junction Temperature Range of -40°C to +125°C

### **Applications**

- · Multi-Output Power Supplies with Sequencing

- DSP, FPGA, CPU and ASIC Power Supplies

- · DSL Modems

- · Telecommunications and Networking Equipment

- Servers

### **General Description**

MIC2155 is a two-phase, single-output synchronous buck control IC that features small size, high efficiency, and a high level of flexibility. The IC implements a 500 kHz Voltage mode PWM control with the outputs switching 180 degrees out of phase. The result of the out-of-phase operation is 1 MHz (or 600 kHz) input ripple with ripple current cancellation, minimizing the required input filter capacitance. A 1% output voltage tolerance allows the maximum level of system performance. Internal drivers with adaptive gate drive allow the highest efficiency with the minimum external components.

Two independent enable pins and a power good output are provided, allowing a high level of control and sequencing capability.

The MIC2155 has an operating junction temperature ranging from -40°C to +125°C.

Data sheets and support documentation can be found on the Microchip website at www.microchip.com.

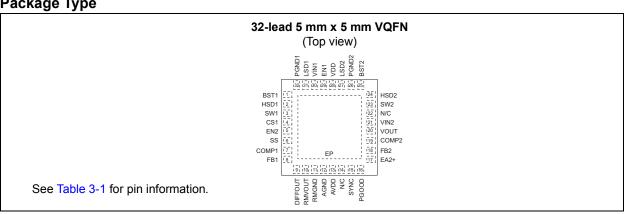

### Package Type

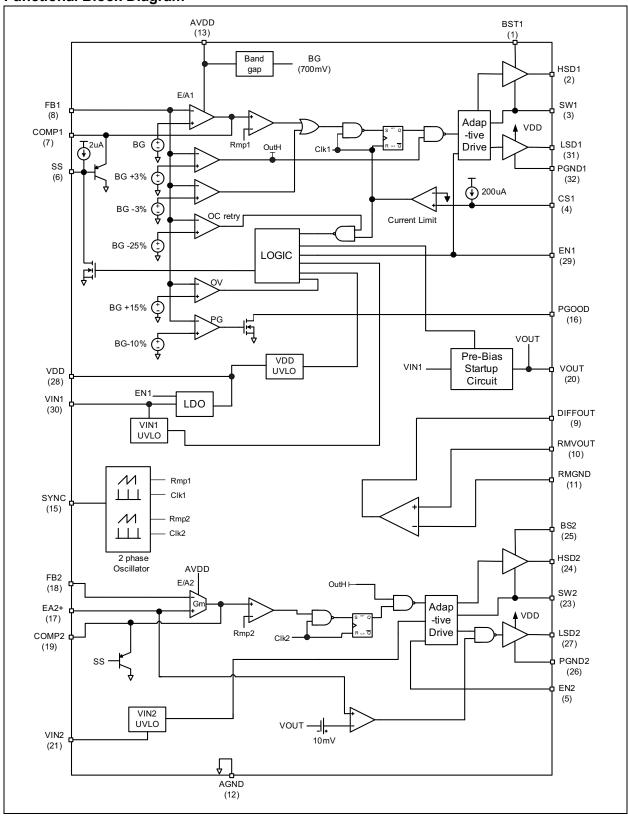

### **Functional Block Diagram**

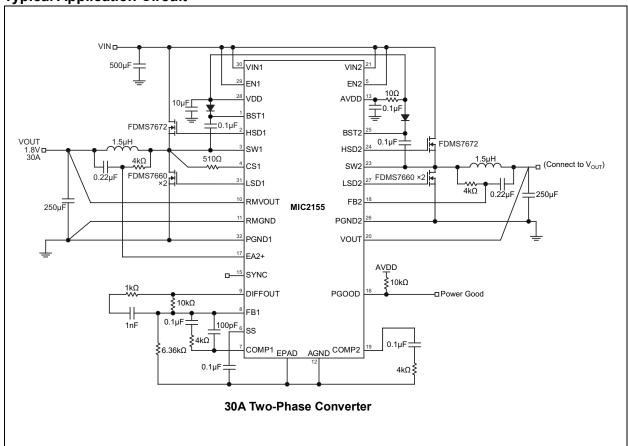

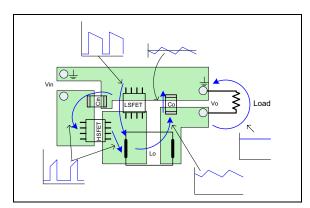

### **Typical Application Circuit**

### 1.0 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings†**

| Supply Voltage, (V <sub>IN1</sub> ,V <sub>IN2</sub> )                                                  | –0.3V to 15V        |

|--------------------------------------------------------------------------------------------------------|---------------------|

| Bootstrapped Voltage, (V <sub>BST</sub> )                                                              | V <sub>IN</sub> +6V |

| SS, FB1, RMV <sub>OUT</sub> , RM <sub>GND</sub> , A <sub>VDD</sub> , SYNC, EA2+, FB2, V <sub>OUT</sub> |                     |

| CS1, EN1, EN2                                                                                          | –0.3V to 15V        |

| Junction Temperature, T <sub>J</sub>                                                                   | –40°C to +150°C     |

| Storage Temperature, T <sub>S</sub>                                                                    |                     |

| ESD, Machine Model                                                                                     | 100V                |

| ESD, Human Body Model                                                                                  | 1500V               |

| Lead Temperature (Soldering 10 Seconds)                                                                | 260°C               |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

| Parameter      | Sym.                               | Min. | Тур. | Max.  | Unit | Conditions |

|----------------|------------------------------------|------|------|-------|------|------------|

| Supply Voltage | V <sub>IN1,</sub> V <sub>IN2</sub> | +4.5 | _    | +14.5 | V    | Note 1     |

| Output Voltage | V <sub>OUT</sub>                   | +0.7 |      | +3.6  | ٧    | Note 1     |

Note 1: The device is not guaranteed to function outside its operating rating.

### DC ELECTRICAL CHARACTERISTICS

| Parameter                                                             | Sym.                               | Min. | Тур. | Max.  | Unit | Conditions                                                  |

|-----------------------------------------------------------------------|------------------------------------|------|------|-------|------|-------------------------------------------------------------|

| Supply Voltage                                                        | V <sub>IN1</sub> ,V <sub>IN2</sub> | +4.5 | _    | +14.5 | V    |                                                             |

| Output Voltage                                                        | V <sub>OUT</sub>                   | +0.7 | _    | +3.6  | V    |                                                             |

| V <sub>IN</sub> ,V <sub>DD,</sub> V <sub>REF</sub> SUPPLY             |                                    |      |      | •     | •    |                                                             |

| Total Quiescent Supply Current, I <sub>VIN1</sub> + I <sub>VIN2</sub> | I <sub>VIN</sub>                   |      | 6    | 10    | mA   | V <sub>FB</sub> = 0.8V (both O/Ps;<br>non-switching)        |

| Shutdown Current                                                      | I <sub>SD</sub>                    | _    | 210  | 300   | μA   | $V_{EN1} = V_{EN2} = 0V$                                    |

| CH1 V <sub>IN</sub> UVLO Start Voltage                                | V <sub>IN1UV_R</sub>               | 3.6  | 4    | 4.4   | V    | V <sub>DD</sub> = Open                                      |

| CH1 V <sub>IN</sub> UVLO Stop Voltage                                 | V <sub>IN1UV_F</sub>               | 3.4  | 3.97 | 4.2   | V    | V <sub>DD</sub> = Open                                      |

| CH2 V <sub>IN</sub> UVLO Start Voltage                                | V <sub>IN2UV_R</sub>               | 2.5  | 2.7  | 2.9   | V    | V <sub>DD</sub> = Open                                      |

| CH2 V <sub>IN</sub> UVLO Stop Voltage                                 | V <sub>IN2UV_F</sub>               | 2.3  | 2.5  | 2.7   | V    | V <sub>DD</sub> = Open                                      |

| V <sub>DD</sub> UVLO Start Voltage                                    | $V_{DDUV\_R}$                      | _    | 3.6  | _     | V    | $V_{IN1} = V_{DD}$ for $V_{IN} < 6V$                        |

| V <sub>DD</sub> UVLO Stop Voltage                                     | $V_{DDUV_F}$                       | _    | 3.3  | _     | V    | V <sub>IN1</sub> = V <sub>DD</sub> for V <sub>IN</sub> < 6V |

| V <sub>IN</sub> UVLO Hysteresis                                       | V <sub>INUV_HYS</sub>              | _    | 40   | _     | mV   | V <sub>DD</sub> = open                                      |

| V <sub>EN</sub> Shutdown Threshold                                    | V <sub>EN_SD</sub>                 | 0.6  | 1    | 1.6   | V    | Each Channel                                                |

| V <sub>EN</sub> Hysteresis                                            | V <sub>EN_HYS</sub>                | _    | 30   | _     | mV   | Each Channel                                                |

| Internal Bias Voltage                                                 | \/                                 | 4.9  | 5.25 | 5.6   | V    | I <sub>VDD</sub> = -75 mA                                   |

| internal bias voltage                                                 | $V_{DD}$                           | 4.9  | 5    | 5.6   | V    | $I_{VDD} = -50 \text{ mA}, V_{IN} = 6V$                     |

Note 1: Specification is obtained by characterization and is not 100% tested.

<sup>2:</sup> Minimum on-time before automatic cycle skipping begins.

### DC ELECTRICAL CHARACTERISTICS

| Electrical Specifications: $T_J = 25^{\circ}C$ ; V $-40^{\circ}C \le T_J \le 125^{\circ}C$ . | EN = V <sub>IN1</sub> = V <sub>IN2</sub> | <sub>2</sub> =12V; | unless  | otherw           | ise speci         | fied. Bold values indicate                                              |

|----------------------------------------------------------------------------------------------|------------------------------------------|--------------------|---------|------------------|-------------------|-------------------------------------------------------------------------|

| Parameter                                                                                    | Sym.                                     | Min.               | Тур.    | Max.             | Unit              | Conditions                                                              |

| OSCILLATOR/PWM SECTION                                                                       | -                                        | •                  |         |                  | •                 |                                                                         |

| PWM Frequency per Channel                                                                    | f <sub>s</sub>                           | 450                | 510     | 550              | kHz               |                                                                         |

| Sync Range                                                                                   | f <sub>SYNC</sub>                        | 860                | _       | 1200             | kHz               | Sync Input is 2x PWM<br>Frequency                                       |

| Sync Level                                                                                   | V <sub>SYNC</sub>                        | 0.5                | _       | 3                | V                 |                                                                         |

| Maximum Duty Cycle                                                                           | D <sub>(MAX)</sub>                       | 80                 | _       | _                | %                 | Each channel                                                            |

| Minimum Headroom between $V_{DD}$ and $V_{OUT}$                                              | V <sub>HR(MIN)</sub>                     | -                  | _       | 1.3              | ٧                 | Required for remote sense amplifier use                                 |

| Minimum On-Time                                                                              | t <sub>ON(MIN)</sub>                     | _                  | 30      | _                | ns                | Each channel (Note 2)                                                   |

| REGULATION                                                                                   | ,                                        | 1                  |         | 1                | 1                 | 1                                                                       |

| CH1 Foodback Voltage Reference                                                               | \/                                       | 693                | 697     | 707              | mV                | +/–1%                                                                   |

| CH1 Feedback Voltage Reference                                                               | $V_{FB}$                                 | 686                | 697     | 714              | mV                | +/-2%                                                                   |

| CH1 Feedback Bias Current                                                                    | I <sub>FB</sub>                          | _                  | 30      | _                | nA                | $V_{FB} = 0.7V$                                                         |

| Output Voltage Line Regulation                                                               | ΔV <sub>OUT_LINE</sub>                   | _                  | 0.08    | _                | %                 | $4.5V \le V_{IN} \le 14.5V$                                             |

| Output Voltage Load Regulation                                                               | $\Delta V_{OUT\_LOAD}$                   | _                  | 0.5     | _                | %                 |                                                                         |

| Output Voltage Total Regulation                                                              | ΔV <sub>OUT_TOTAL</sub>                  | _                  | 0.6     | _                | %                 | $4.5V \le V_{IN} \le 14.5V$ ; $1A \le I_{OUT} \le 10A (V_{OUT} = 2.5V)$ |

| CHANNEL CURRENT BALANCING                                                                    | 1                                        |                    |         |                  |                   |                                                                         |

| Asynchronous Mode V <sub>TH</sub> for Slave<br>Output                                        | V <sub>TH_ASYN</sub>                     | _                  | 10      | _                | mV                |                                                                         |

| ERROR AMPLIFIER (CH1)                                                                        |                                          |                    |         |                  |                   |                                                                         |

| DC Gain                                                                                      | G <sub>EA1</sub>                         | _                  | 70      | _                | dB                |                                                                         |

| Output Sourcing/Sinking Current                                                              | I <sub>SNK/SRC</sub>                     | _                  | 1       | _                | mA                |                                                                         |

| ERROR AMPLIFIER (CH2)                                                                        | _                                        |                    |         |                  |                   |                                                                         |

| DC Gain                                                                                      | G <sub>EA2</sub>                         | _                  | 70      | _                | dB                |                                                                         |

| Transconductance                                                                             | 9 <sub>m</sub>                           | _                  | 1.25    | _                | mS                |                                                                         |

| DIFFERENTIAL AMPLIFIER                                                                       |                                          |                    |         |                  |                   |                                                                         |

| Voltage Gain                                                                                 | G <sub>DA</sub>                          | _                  | 1       | _                |                   |                                                                         |

| Offset Voltage                                                                               | V <sub>OS</sub>                          | -20                | _       | +20              | mV                |                                                                         |

| Output Sourcing Current Range                                                                | I <sub>SRC_DA</sub>                      | 0                  | _       | 500              | μΑ                |                                                                         |

| OUTPUT OVERVOLTAGE PROTECTION                                                                | DN                                       |                    |         |                  |                   |                                                                         |

| OV Threshold                                                                                 | $OV_TH$                                  | 106                | 109     | 114              | $%V_{REF}$        | $V_{FB} = OV_{TH}$ , Latch LSD High                                     |

| Delay Blanking time                                                                          | t <sub>BLANK_OV</sub>                    | _                  | 1       | _                | μs                |                                                                         |

| SOFT START                                                                                   |                                          |                    |         |                  |                   |                                                                         |

| Internal Soft-Start Source Current                                                           | I <sub>SS</sub>                          | 1.25<br><b>1</b>   | 2       | 2.75<br><b>4</b> | μA<br>μA          | $T_{J} = 25^{\circ}C$ $-40^{\circ}C \le T_{J} \le 125^{\circ}C$         |

| CURRENT SENSE                                                                                | •                                        | •                  | •       | 1                | •                 | •                                                                       |

| CS Overcurrent Trip Point Program Current                                                    | I <sub>CL</sub>                          | 180                | 195     | 220              | μA                |                                                                         |

| CS Comparator Sense Offset Voltage                                                           | V <sub>CL_OS</sub>                       | -10                | 0       | +10              | mV                | Senses drop across low-side FET                                         |

| POWER GOOD                                                                                   | 1                                        |                    |         |                  | 4                 | ı                                                                       |

| Power Good Threshold                                                                         | PG <sub>TH</sub>                         | 86                 | 88.5    | 91               | %V <sub>REF</sub> | Sweep V <sub>FB</sub> from Low to High                                  |

| Power Good Voltage Low                                                                       | V <sub>PG LOW</sub>                      | 1 —                | 0.225   | 0.3              | V                 | V <sub>FB</sub> = 0 V; I <sub>PGOOD</sub> = 1 mA                        |

| <b>Note 1:</b> Specification is obtained by c                                                |                                          | and is             | not 100 | 1% tests         | <u>-</u>          | . 2002                                                                  |

**Note 1:** Specification is obtained by characterization and is not 100% tested.

<sup>2:</sup> Minimum on-time before automatic cycle skipping begins.

### DC ELECTRICAL CHARACTERISTICS

**Electrical Specifications:**  $T_J = 25^{\circ}C$ ;  $V_{EN} = V_{IN1} = V_{IN2} = 12V$ ; unless otherwise specified. Bold values indicate –40°C ≤ T<sub>.1</sub> ≤ 125°C. Conditions Parameter Min. Тур. Max. Unit Sym. **GATE DRIVERS** Source into 3000 pF Source 23 ns t<sub>RISE</sub> Rise/Fall Time Sink out of 3000 pF 16 ns Sink  $t_{FALL}$ Source 1.6 3.5 Ω R<sub>HSD</sub> H High-Side Drive Resistance  $V_{DD} = V_{IN} = 5V$ Sink R<sub>HSD L</sub> 1.7 2.5 Ω 2 3.5 Ω Source R<sub>LSD</sub> <sub>H</sub>  $V_{DD} = V_{IN} = 5V$ Low-Side Drive Resistance Sink  $R_{LSD\_L}$ 1.4 2.5 Ω Driver Non-Overlap Time (Adaptive) 60 ns  $t_{NON}$

Note 1: Specification is obtained by characterization and is not 100% tested.

2: Minimum on-time before automatic cycle skipping begins.

### **TEMPERATURE SPECIFICATIONS**

| Parameter                      | Sym.                   | Min. | Тур. | Max. | Unit | Conditions |  |  |

|--------------------------------|------------------------|------|------|------|------|------------|--|--|

| TEMPERATURE RANGE              |                        |      |      |      |      |            |  |  |

| Operating Junction Temperature | TJ                     | -40  | _    | +125 | °C   |            |  |  |

| Maximum Junction Temperature   | T <sub>J(ABSMAX)</sub> | _    | _    | +150 | °C   |            |  |  |

| Ambient Storage Temperature    | T <sub>S</sub>         | -65  | _    | +150 | °C   |            |  |  |

| PACKAGE THERMAL RESISTANCE     |                        |      |      |      |      |            |  |  |

| 32-lead 5mm × 5mm VQFN         | $\theta_{JA}$          | _    | 50   | _    | °C/W |            |  |  |

| 32-lead 5mm × 5mm VQFN         | $\theta_{JC}$          | _    | 5    | _    | °C/W |            |  |  |

### 2.0 TYPICAL PERFORMANCE CURVES

Note:

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g. outside specified power supply range) and therefore outside the warranted range.

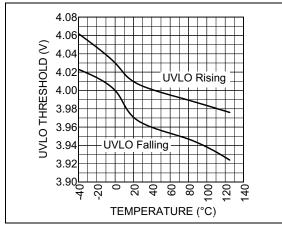

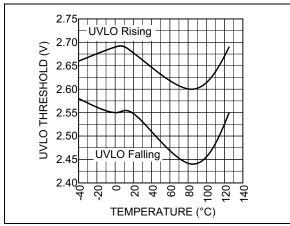

FIGURE 2-1: VN1 UVLO Threshold.

FIGURE 2-2: VIN2 UVLO Threshold.

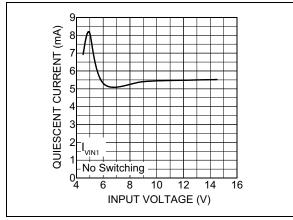

**FIGURE 2-3:** Quiescent Current 1 vs. Input Voltage.

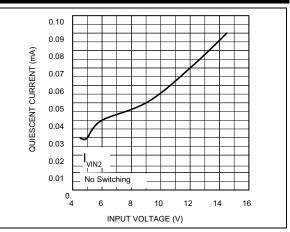

**FIGURE 2-4:** Quiescent Current 2 vs. Input Voltage.

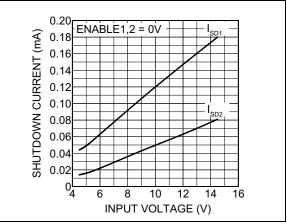

FIGURE 2-5: Shutdown Current vs. Input Voltage.

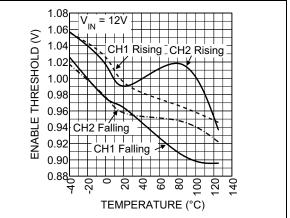

FIGURE 2-6: Enable Threshold vs Temperature.

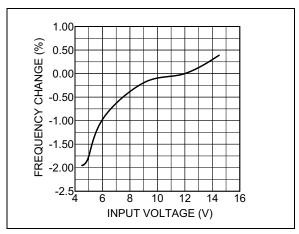

**FIGURE 2-7:** Change in Switching Frequency vs. Input Voltage.

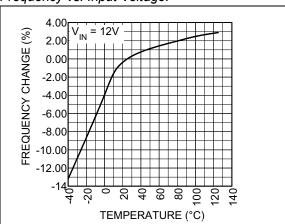

**FIGURE 2-8:** Change in Switching Frequency vs. Temperature.

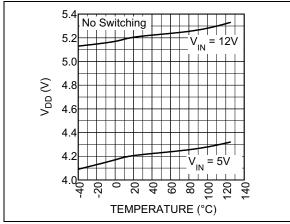

**FIGURE 2-9:**  $V_{DD}$  vs. Temperature.

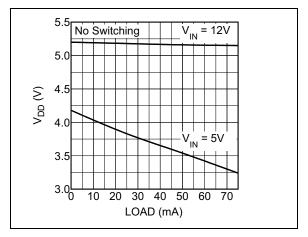

FIGURE 2-10: V<sub>DD</sub> vs. Load.

FIGURE 2-11: V<sub>DD</sub> vs. Input Voltage.

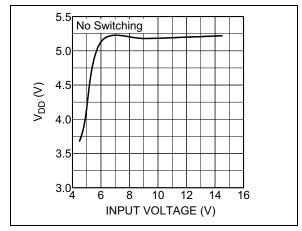

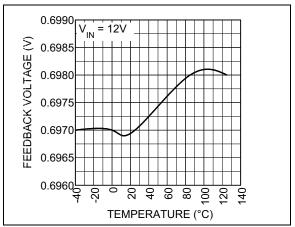

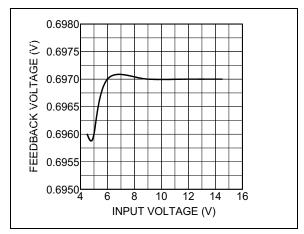

**FIGURE 2-12:** Feedback Voltage vs. Temperature.

**FIGURE 2-13:** Feedback Voltage vs. Input Voltage.

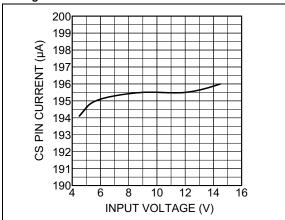

**FIGURE 2-14:** CS Pin Current vs. Input Voltage.

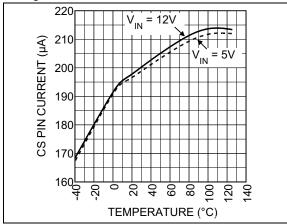

**FIGURE 2-15:** CS Pin Current vs. Temperature.

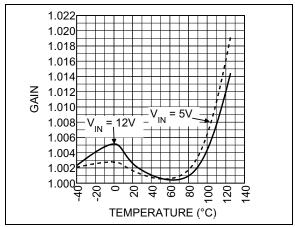

**FIGURE 2-16:** Differential Amplifier Gain vs. Temperature.

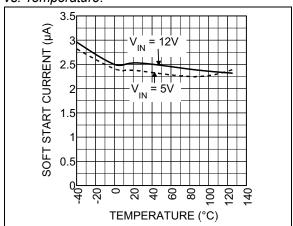

**FIGURE 2-17:** Soft-Start Current vs. Temperature.

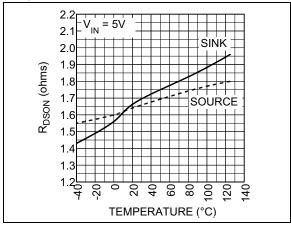

**FIGURE 2-18:** R<sub>DSON</sub> High-Side Drive Source/Sink.

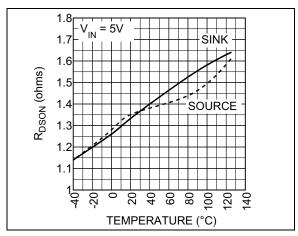

FIGURE 2-19: Source/Sink.

R<sub>DSON</sub> Low-Side Drive

### 3.0 PIN DESCRIPTION

The details on the pins of MIC2155 are listed in Table 3-1. Refer to **Package Type** for the location of pins.

TABLE 3-1: PIN FUNCTION TABLE

| IABLE 3-1. | FINFUNCTION                           | -<br>1                                                                                                                                                                                                                                     |  |  |  |

|------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Number | Pin Name                              | Description                                                                                                                                                                                                                                |  |  |  |

| 1          | BST1                                  | Boost 1 (input): Provides voltage for high-side MOSFET Driver 1. The gate drive voltage is higher than the high-side MOSFET source voltage by V <sub>DD</sub> minus a diode drop.                                                          |  |  |  |

| 2          | HSD1                                  | High-side Driver 1 (output): High-current driver output for Channel 1 external high-side MOSFET.                                                                                                                                           |  |  |  |

| 3          | SW1                                   | Switch Node 1 (output): Return for HSD1                                                                                                                                                                                                    |  |  |  |

| 4          | CS1                                   | Current Sense 1 (input): Current-limit comparator non-inverting input. Current sensed across the Channel 1 low-side FET during the off-time. Current limit is by the resistor between the CS1 pin and drain of the Channel 1 low-side FET. |  |  |  |

| 5          | EN2                                   | Enable 2 (input): Channel 2 enable. Pull high to enable. Pull low to disable.                                                                                                                                                              |  |  |  |

| 6          | SS                                    | Soft Start (input): Controls the turn-on time of the output voltage. Active at Power-up, Enable, and Current limit recovery.                                                                                                               |  |  |  |

| 7          | COMP1                                 | Compensation 1 (input): Output of the internal error amplifier for Channel 1.                                                                                                                                                              |  |  |  |

| 8          | FB1                                   | Feedback 1 (input): Negative input to the error amplifier of Channel 1.                                                                                                                                                                    |  |  |  |

| 9          | DIFFOUT                               | Output of remote sense differential amplifier.                                                                                                                                                                                             |  |  |  |

| 10         | RMVOUT                                | Remote $V_{OUT}$ : Connect to $V_{OUT}$ at the remote sense point. Input to precision differential amplifier.                                                                                                                              |  |  |  |

| 11         | RMGND                                 | Remote Ground: Connect to ground at the remote sense point. Input to precision differential amplifier.                                                                                                                                     |  |  |  |

| 12         | AGND                                  | Analog Ground                                                                                                                                                                                                                              |  |  |  |

| 13         | AVDD                                  | Analog Supply Voltage (input): Connect to V <sub>DD</sub> through an RC filter network.                                                                                                                                                    |  |  |  |

| 14         | N/C                                   | No connect                                                                                                                                                                                                                                 |  |  |  |

| 15         | SYNC                                  | Sync (input): Synchronizes switching to an external source. Leave floating when not used.                                                                                                                                                  |  |  |  |

| 16         | PGOOD                                 | Power Good (output): Asserts high when voltage on the FB pin rises above Power Good threshold.                                                                                                                                             |  |  |  |

| 17         | EA2+                                  | Positive Input to Channel 2 (current-sharing) error amplifier (Input): Connect to Channel 1 current sense.                                                                                                                                 |  |  |  |

| 18         | FB2                                   | Negative input to Channel 2 (current sharing) error amplifier (Input): Connect to Channel 2 current sense.                                                                                                                                 |  |  |  |

| 19         | COMP2                                 | Compensation 2 (input): Pin for external compensation of Channel 2 error amplifier.                                                                                                                                                        |  |  |  |

| 20         | VOUT                                  | Output Sense (input): Connect to output side of inductors. Used for current sharing.                                                                                                                                                       |  |  |  |

| 21         | VIN2                                  | Supply Voltage for Channel 2 (input): Used for Channel 2 UVLO circuit.                                                                                                                                                                     |  |  |  |

| 22         | N/C                                   | No connect                                                                                                                                                                                                                                 |  |  |  |

| 23         | SW2                                   | Switch Node 2 (output): Return for HSD2.                                                                                                                                                                                                   |  |  |  |

| 24         | HSD2                                  | High-side Driver 2 (output): High-current driver output for Channel 2 high-side MOSFET.                                                                                                                                                    |  |  |  |

| 25         | BST2                                  | Boost 2 (input): Provides voltage for high-side MOSFET driver in Channel 2. The gate drive voltage is higher than the high-side MOSFET source voltage by $V_{DD}$ minus a diode drop.                                                      |  |  |  |

| 26         | PGND2                                 | Power Ground 2: High current return for Low-Side Driver 2.                                                                                                                                                                                 |  |  |  |

| 27         | LSD2                                  | Low-side Driver 2 (output): High-current driver output for Channel 2 low-side external MOSFET.                                                                                                                                             |  |  |  |

|            | · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                                            |  |  |  |

## **MIC2155**

### TABLE 3-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                     |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28         | VDD      | 5V Internal Linear Regulator from $V_{\text{IN1}}$ (output): $V_{\text{DD}}$ is the external MOSFET gate driver supply voltage and an internal supply bus for the IC. When $V_{\text{IN1}}$ is <5V, this regulator operates in Dropout mode. Connect external bypass capacitor. |

| 29         | EN1      | Enable 1 (input): Output enable. Turns off both channels. Pull high to enable. Pull low to disable.                                                                                                                                                                             |

| 30         | VIN1     | Supply Voltage for Channel 1 (input): Used for UVLO and $V_{DD}$ circuits.                                                                                                                                                                                                      |

| 31         | LSD1     | Low-side Driver 1 (output): High-current driver output for Channel 1 low-side external MOSFET.                                                                                                                                                                                  |

| 32         | PGND1    | Power Ground 1: High current return for low-side Driver 1.                                                                                                                                                                                                                      |

| EP         | EPAD     | Exposed Pad (power): Must make a full connection to the GND plane to maximize thermal performance of the package.                                                                                                                                                               |

### 4.0 FUNCTIONAL DESCRIPTION

The MIC2155 is a two-phase, synchronous buck controller operating at a fixed frequency. The device switches at 500 kHz per phase (1 MHz at the input and output).

The following are some advantages of multi-phase operation:

- Smaller input and output filtering components are required because of current cancellation and higher input and output frequency.

- Faster transient response is possible with smaller output filter component values.

- Load current through each phase is one-half the total output current, which allows for even heat distribution and smaller components.

- Control circuitry forces better current sharing in the MOSFETs than paralleling FETs in a single-phase application.

The controller utilizes a Voltage-mode control scheme (VMC). Lossless current sharing is accomplished by sensing the DC voltage across each inductor winding. Lossless overcurrent protection is performed by sensing the voltage across the low-side MOSFET on-resistance during the off-time.

Other features of the controller are:

- · Overvoltage protection

- · Soft start

- UVLO

- Enable

- · Remote sensing

- · Pre-biased output startup

- · Multiple input supplies

- · Power good signal

- · Frequency synchronization

### 4.1 Startup

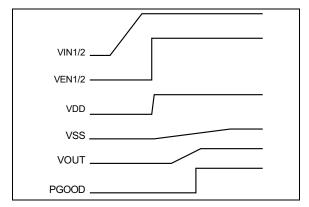

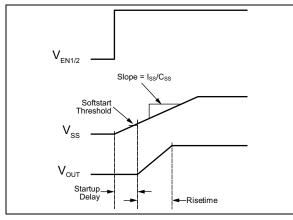

A typical startup sequence is shown in Figure 4-1 (also refer to the Functional Block Diagram). The enable pins are asserted after  $V_{\rm IN}$  is applied.  $V_{\rm DD}$  is immediately turned on and an internal FET releases the soft-start pin. The soft-start pin controls the error amplifier voltage. As  $V_{\rm SS}$  ramps up, it reaches a threshold where the gate drive is enabled and the MOSFETs start to switch at a very low duty cycle. The rise of the soft-start voltage controls the increase in  $V_{\rm OUT}$  by gradually allowing the COMP1 pin voltage to rise. A 10 mV offset in the current controller keeps the Channel 2 low-side drive off when the output current is low to prevent current from circulating between the phases. PGOOD is asserted when  $V_{\rm OUT}$  reaches the PGOOD threshold.

FIGURE 4-1: Startup Sequence.

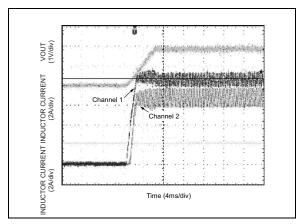

A typical output voltage and inductor current startup waveforms are shown in Figure 4-2.

FIGURE 4-2: Turn on Waveforms.

### 4.2 Soft-Start

The soft-start circuitry controls how fast the output voltage rises by controlling the COMP pin rise time. Without soft start, a fast or uncontrolled turn-on requires a higher current from the input source to charge up the output capacitance.

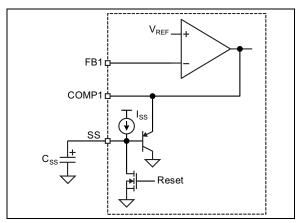

The soft-start circuitry also controls the delay time between the enable pin assertion to when  $V_{OUT}$  starts to rise. An internal 2  $\mu A$  (typical) soft-start current source is used to charge up an external soft-start capacitor. Figure 4-3 and Figure 4-4 show the soft-start circuitry and waveform timing.

The output voltage starts to rise when  $V_{SS}$  is approximately 1 diode drop above ground, 0.6V.

FIGURE 4-3:

Soft-Start Circuit.

FIGURE 4-4:

Soft-Start Waveforms.

The startup delay and output voltage rise time can be programmed by the external soft-start capacitor value and approximated using the formula in Equation 4-1 and Equation 4-2, respectively.

### **EQUATION 4-1:**

Delay:

$$t_d = \frac{C_{SS} \times 0.6V}{I_{SS}}$$

### **EQUATION 4-2:**

Rise time:

$$t_R = \frac{C_{SS} \times V_{OUT}}{V_{IN} \times I_{SS}}$$

The soft start pin is pulled to ground and the soft-start capacitor is discharged under the following conditions:

- · EN1 pin De-asserted

- UVLO on the  $V_{IN1}$  or  $V_{DD}$  pins

- Overcurrent

- Overvoltage (latched off)

### 4.3 Enable

There is an enable pin for each of the two channels. Asserting EN1 enables Channel 1 gate drive and VDD internal 5V LDO as well as releases the soft-start circuit. De-asserting EN1 disables the gate drive, discharges  $C_{SS}$ , and disables  $V_{DD}$ . It brings the controller into a low-current OFF state.

Enable 2 only controls switching of Channel 2. Disabling Channel 2 stops the switching of the power FETs on Channel 2 which reduces the  $V_{DD}$  current draw. This can improve efficiency when operating at low output current, especially when large MOSFETs are used.

## 4.4 Supply Voltages and Internal Regulator

The MIC2155 is powered from a 4.5V to 14.5V supply. The two input supply pins (VIN1 and VIN2) are connected together in most applications. They are powered separately in configurations with two input supply voltages.

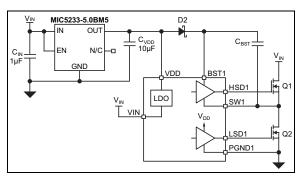

VIN1 supplies an internal LDO, which generates the  $V_{DD}$  supply voltage. VDD is used to power the gate drive circuitry and must be externally decoupled to the power ground pins (PGND1 and PGND2). A 10  $\mu$ F ceramic capacitor is recommended for most applications. The AVDD pin is the supply pin for the Bandgap reference and internal analog circuits. A small RC filter (10 $\Omega$ , 0.1  $\mu$ F) connected to AVDD is recommended to help attenuate switching noise from the VDD supply.

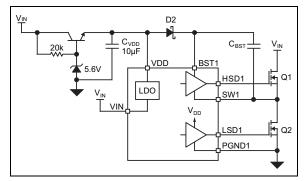

The dropout of the internal VDD regulator causes VDD to drop if VIN1 is below 6V. When operating below 6V, VDD may be jumpered to VIN1. This bypasses the internal LDO and prevents VDD from dropping out.

An external LDO or simple series pass regulator can be used to limit the VDD voltage for applications with an input voltage that spans above and below the 6V maximum  $V_{DD}$  limit. Figure 4-5 and Figure 4-6 illustrate two examples of regulating VDD with external circuitry.

FIGURE 4-5:

LDO Regulator.

FIGURE 4-6: Emitter Follower Regulator.

The internal VDD regulator can supply up to 75 mA of current to drive the external MOSFETs. Power dissipation inside the MIC2155 control IC is divided between power dissipated in the controller's analog circuitry and power dissipated in the drive circuitry. Drive circuitry power is almost always much greater than analog circuitry power. Total regulator power dissipation is calculated using Equation 4-3.

### **EQUATION 4-3:**

$$P_{DISS} = V_{IN} \times I_{IN} = V_{IN} \times (f_S \times Q_G + I_O)$$

Where:

Q<sub>G</sub> = total gate charge of all MOSFETs f<sub>S</sub> = switching frequency of each stage (500 kHz)

$I_{\mathbb{Q}}^{-}$  = controller quiescent current (non-switching supply current)

In some instances, power dissipation inside the control IC may limit the controller's maximum operating ambient temperature. An example is when the MIC2155 is powered from a 12V source and is driving 4 FETs. If each FET has a  $Q_G = 37$  nC, the total power dissipation in the MIC2155 is derived approximately with Equation 4-4.

### **EQUATION 4-4:**

$$P_{DISS} = 12V \times (37nc \times 4) \times 500kHz = 0.888W$$

The maximum operating ambient temperature is computed in Equation 4-5.

### **EQUATION 4-5:**

$$\begin{split} T_{A(MAX)} &= T_{J(MAX)} - P_{DISS} \times \theta_{JC} \\ T_{A(MAX)} &= 125^{\circ}C - 0.888\,W \times 50^{\circ}C/W \\ T_{A(MAX)} &= 81^{\circ}C \end{split}$$

Using an external LDO to supply VDD (as in Figure 4-5) can lower power dissipation in the controller and reduce junction temperature by supplying VDD externally. Using an external regulator, the power dissipated in the controller is reduced to the value as calculated in Equation 4-6.

### **EQUATION 4-6:**

$$P_{DISS} = 5V \times (37nC \times 4) \times 500kHz = 0.37W$$

Careful selection and temperature rise calculations of the external LDO should be done to prevent an excessively high LDO junction temperature.

### 4.5 UVLO

Separate UVLO circuits monitor VIN1, VIN2 and VDD. Switching on Channel 1 is inhibited until the voltages on the VIN1 and VDD pins are greater than their respective UVLO thresholds. The gate drive on Channel 2 is inhibited until the VIN2 pin voltage exceeds its UVLO threshold.

Individual UVLO thresholds are necessary to allow proper operation from separate input supplies. The VIN1 threshold prevents the IC from switching if the input voltage is too low to properly source the VDD voltage. The VIN2 UVLO threshold is lower than VIN1 to allow operation from a low-voltage input.

Channel 1 switches and provides a regulated output voltage even if the VIN2 UVLO prevents Channel 2 from switching.

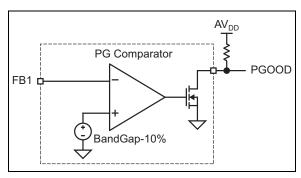

### 4.6 Power Good

The power good signal asserts high when the output voltage is greater than the power good threshold. The power good circuit compares a portion of the reference voltage to the voltage on the feedback pin. The output is an open drain FET as shown in Figure 4-7. To assert high, it must be pulled up to AVDD through a resistor.

FIGURE 4-7: Power Good.

The power good signal may be connected to the enable pin of other power supplies and be used to sequence the other outputs.

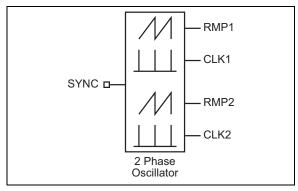

## 4.7 Oscillator and Frequency Synchronization

The internal oscillator free runs at a fixed frequency and requires no external components. The oscillator generates two clock signals that are 180 degrees out of phase with each other. This forces each channel of the controller to switch 180 degrees out of phase, which reduces input and output ripple current.

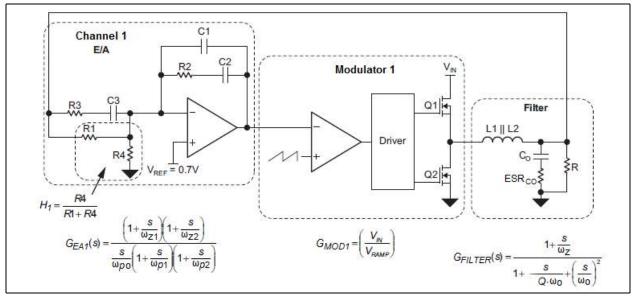

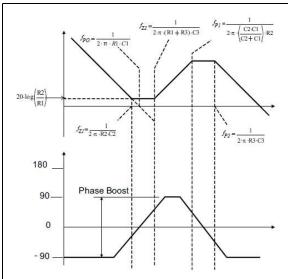

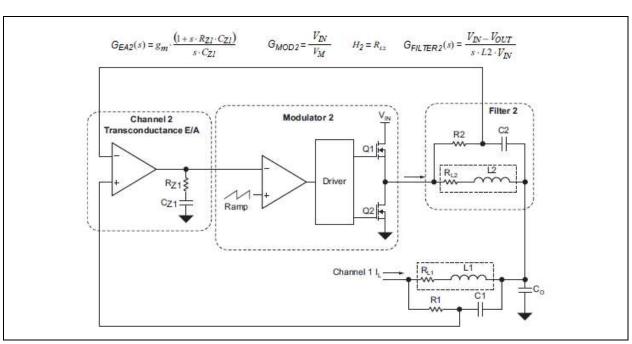

The internal oscillator generates a clock signal and ramp signal. The clock signal terminates the switching cycle for each channel. The ramp voltage signal for Channel 1 is compared with the output of the Channel 1 error amplifier and regulates the output voltage. The ramp signal for Channel 2 is compared with the Channel 2 error amplifier output and forces the output current of Channel 2 to match that of Channel 1. See Figure 4-8.

**FIGURE 4-8:** Oscillator and Sync Diagram.

The SYNC input (pin 15) allows the MIC2155 to synchronize to an external clock signal. When synchronized, each channel switches at half of the synchronization frequency. Limitations on the synchronization frequency and signal amplitude are listed in the **Section 1.0** "Electrical Characteristics". When not used, the sync pin should be left open (no connect).

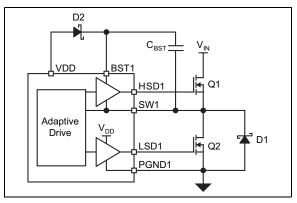

### 4.8 MOSFET Gate-Drive Circuitry

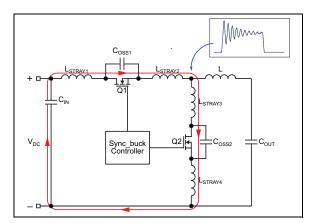

The high-side drive circuit is designed to switch an N-channel MOSFET. Figure 4-9 shows a diagram of the gate drive and bootstrap circuit. D2 and  $C_{\rm BST}$  comprise the bootstrap circuit, which is used to supply drive voltage to the high-side FET. Bootstrap capacitor  $C_{\rm BST}$  is charged through diode D2 while the low-side MOSFET is on and the voltage on the SW pin is approximately 0V. When the high-side MOSFET driver is turned on, energy from  $C_{\rm BST}$  is used to charge the MOSFET gate, turning on the FET. As the MOSFET turns on, the voltage on the SW pin increases to approximately  $V_{\rm IN}$ .  $V_{\rm CBST}$  floats up by VIN, diode D2 is reversed biased and  $V_{\rm BST}$  is pulled high while continuing to keep the high-side MOSFET on. The

high-side drive voltage, which is derived from  $V_{DD}$ , is approximately 4.5V due to the voltage drop across D2. When operating at 4.5V  $V_{IN}$ , without connecting  $V_{DD}$  to  $V_{IN}$ , the gate drive voltage to the high-side FET could be as low as 3.2V. MOSFETs with an appropriate  $V_{GS}$  threshold should be used in this situation.

The voltage on the bootstrap capacitor drops each time it delivers charge to turn on the MOSFET. The voltage drop depends on the gate charge required by the MOSFET. Most MOSFET specifications specify gate charge vs.  $V_{GS}$ . Based on this information and a recommended  $\Delta V_{CBST}$  of less than 0.1V, the minimum value of bootstrap capacitance is calculated as shown in Equation 4-7.

### **EQUATION 4-7:**

$$C_{BST} \ge \frac{Q_{GATE}}{\Delta V_{CBST}}$$

Where

$Q_{GATE}$  = Total Gate Charge of high-side MOSFET  $\Delta V_{CBST}$  = Voltage Drop across the  $C_{BST}$  capacitor

A minimum value of 0.1  $\mu$ F is required for each of the bootstrap capacitors, regardless of the MOSFETs being driven. Larger or paralleled MOSFETs may require larger capacitance values for proper operation. Placement is critical. The bootstrap capacitors ( $C_{\rm BST}$ ) for the BST supply pins must be located close between the BST and SW pins. The etch connections should be short, wide and direct. The use of a ground plane to minimize connection impedance is recommended. Refer to Section 4.23 "General Layout and Component Placement" for more details.

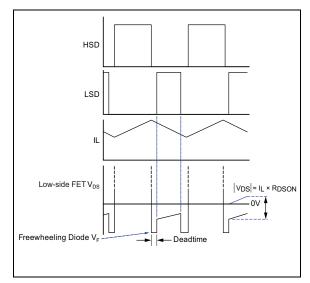

A delay between the switching of the two MOSFETs is necessary to prevent both MOSFETs from being on at the same time and shorting  $V_{\text{IN}}$  to ground. An adaptive gate drive in the controller monitors the switch node (SW1) and low-side driver (LSD1) to minimize dead time while preventing both MOSFETs from being on at the same time. This enables the use of a broad range of MOSFETS without requiring excessive dead time.

FIGURE 4-9: Gate Drive.

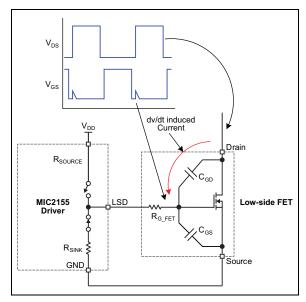

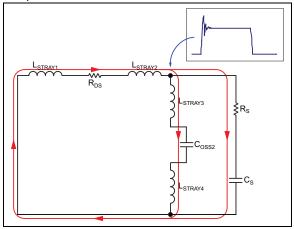

### 4.9 dv/dt-Induced Turn-On of the Low-Side MOSFET

As the high-side MOSFET turns on, the rising dv/dt on the switch-node forces current through  $C_{GD}$  of the low-side FET causing a glitch on the FET's gate. Figure 4-10 illustrates the basic mechanism causing this issue. If the glitch on the gate is greater than the FET's turn-on threshold, it may cause an unwanted turn-on of the low-side FET while the high-side FET is on. A short circuit between input and ground would occur. This condition lowers efficiency and increases power dissipation in both FETs. Additionally, turning on the low-side FET during the off-time could interfere with overcurrent sensing.

FIGURE 4-10: dv/dt-Induced Turn-on.

The following steps can be taken to lower the gate drive impedance, minimize the dv/dt-induced current, and lower the FETs susceptibility to the induced glitch:

- 1. Choose a low-side MOSFET with:

- $\bullet$  a high  $C_{GS}/C_{GD}$  ratio

- a low internal gate resistance

- Do not put a resistor between the LSD output and the gate of low-side MOSFET.

- 3. Ensure both the gate drive and return path PCB traces are short low-inductance connections.

- 4. Use a 4.5V  $V_{GS}$ -rated MOSFET because its higher gate threshold voltage is more immune to glitches than a 2.5V-rated or 3.3V-rated FET.

- 5. Connect V<sub>DD</sub> to V<sub>IN</sub> or a 5V supply if V<sub>IN</sub> is below 6V. The R<sub>DSON</sub> of the internal driver will be lower, and a 4.5V rated MOSFET can be used.

### 4.10 Remote Sense

Remote sensing provides accurate output voltage regulation by sensing at the load. Remote sensing makes up for losses in the power distribution path. It uses a unity gain differential amplifier to overcome voltage drops in both the output and return (ground) paths. The amplifier has a Common mode input range from –0.3V to 3.6V. For proper remote sense operation,  $V_{\rm IN}$  must be greater than 6V. If  $V_{\rm IN}$  is less than 6V, the  $V_{\rm DD}$  pin must be connected to  $V_{\rm IN}$  or externally supplied with 5V.

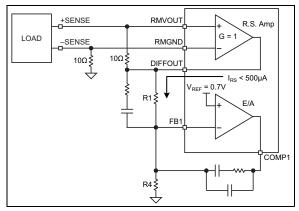

The output of the remote sense amplifier can source up to 500  $\mu$ A. The voltage divider resistors (R1 and R4 in Figure 4-12) must be chosen to insure the output current of the amplifier does not exceed the maximum of 500  $\mu$ A. See Equation 4-8.

### **EQUATION 4-8:**

$$R1_{MAX} \ge \frac{V_{OUT} - V_{REF}}{500 \, \mu A}$$

Where:

$$V_{REF} = 0.7 \text{V}$$

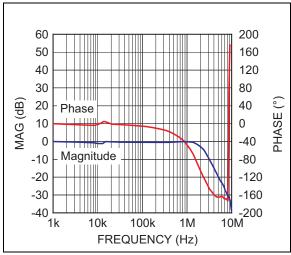

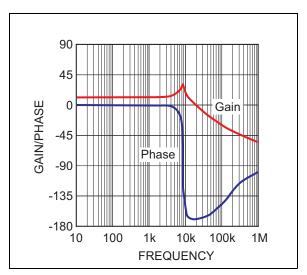

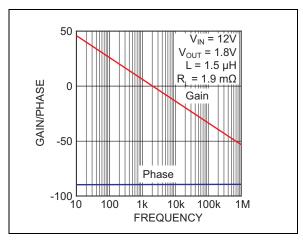

A gain/phase plot of the remote sense amplifier in Figure 4-11 shows a typical 2 MHz bandwidth. Phase lag is 45 degrees at 1 MHz.

FIGURE 4-11: Remote Sense Amplifier Gain/Phase Plot.

A typical remote sense configuration is shown in Figure 4-12. The output of the remote sense amplifier feeds a voltage divider (R1, R4), which is connected to the Channel 1 error amplifier. The divider and compensation network for the remote sense are the same as for a local sense configuration. The  $10\Omega$  resistors provide an alternate feedback path if the remote sense connections are removed or opened. The remote sense connections should not be shorted. Otherwise the output voltage will increase close to  $V_{\rm IN}$ . The OVP circuit in the controller does not protect against this type of fault when the feedback pin voltage is 0V.

FIGURE 4-12: Remote Sense.

### 4.11 Setting the Output Voltage

Regardless of whether the remote sensing or local output voltage sensing is used, the output voltage is set with voltage divider resistors R1 and R4 (See Figure 4-12.). The equation below is used to calculate  $V_{\rm OUT}$ .

### **EQUATION 4-9:**

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R4}\right)$$

Where:

$\rm V_{REF}$  = 0.7V

## 4.12 Current Limit and Overcurrent Protection

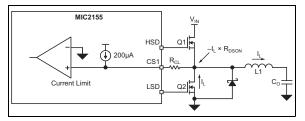

The MIC2155 uses the synchronous (low-side) MOSFETs R<sub>DSON</sub> to sense an over current condition. The low-side MOSFET is used because it displays lower parasitic oscillations after switching than the high-side MOSFET. Additionally, it improves the accuracy and reduces false tripping at lower voltage outputs and narrow duty cycles since the off-time increases as duty cycle decreases. Figure 4-13 shows the overcurrent detection circuit.

**FIGURE 4-13:** Overcurrent Detection Circuit.

Inductor current flows from the lower MOSFET source to the drain during off-time. The drain voltage becomes negative with respect to ground as the inductor current continues to flow from source to drain. This negative voltage is proportional to instantaneous inductor current times the low-side MOSFET RDSON. The voltage across the low-side FET becomes even more negative as the output current increases. Figure 4-14 shows the inductor current and low-side FET  $V_{DS}$ waveforms. The overcurrent detection circuit operates by passing a known fixed current source (about 200 µA typical) through a resistor R<sub>CI</sub>. This sets up an offset voltage ( $I_{CL} \times R_{CL}$ ) that is compared to the  $V_{DS}$  of the low-side FET. When source-to-drain voltage  $V_{SD}$  (I<sub>L</sub> xR<sub>DSON</sub>) is equal to this voltage, the MIC2155's over current trigger is set, which disables the next high-side gate drive pulse. After missing the high-side pulse, the overcurrent (OC) trigger is reset. If on the next low-side drive cycle, the current is still too high i.e.  $V_{CS1}$  is  $\leq 0V$ , another high-side pulse is missed and so on. This effectively reduces the overall energy transferred to the output and V<sub>OUT</sub> starts to fall.

The MIC2155 current limit circuit restricts the maximum peak inductor current. If the load tries to draw additional current, the output voltage drops until it is no longer within regulation limits. At this point, (75% of nominal output voltage) a Hiccup Current mode is initiated to protect downstream loads from excessive current during hard short circuits. This helps reduce the overall power dissipation in the PWM converter components during a fault.

**FIGURE 4-14:** Inductor Current and Low-Side FET V<sub>DS</sub> Waveforms.

The MIC2155 only senses current across the low-side MOSFET of Channel 1 since both channels operate in parallel. This means the total output current limit is approximately twice the calculated current limit.

### 4.13 Current Limit Setting

The current limit circuit responds to the peak inductor current flowing through the low-side FET. The value of  $R_{CL}$  can be estimated with a simple method or can be more accurately calculated by taking the inductor ripple current into account.

### 4.13.1 THE SIMPLE METHOD

The current limit setting resistor value can be quickly estimated with Equation 4-10.

### **EQUATION 4-10:**

$$R_{CL} = \frac{I_{OUT(OC)} \times R_{DSON(MAX)}}{2 \times 180 \,\mu A}$$

Where:

$I_{OUT(OC)}$  is the total output current limit at overcurrent.  $R_{DSON}$  is the maximum on-resistance of the low-side FET at the operating junction temperature.

### 4.13.2 ACCURATE METHOD

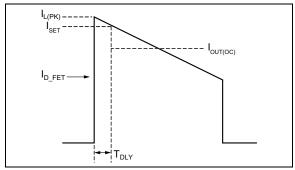

For designs where ripple current is significant when compared to  $I_{OUT}$  or for low duty cycle operation, calculating the current setting resistor  $R_{CL}$  should take into account that we are sensing the peak inductor current and that there is a blanking delay of approximately 100 ns. See Figure 4-15.

FIGURE 4-15: Overcurrent Waveform.

Equation 4-11, Equation 4-12, Equation 4-13 and Equation 4-14 are used to accurately calculate the current limit resistor value.

### **EQUATION 4-11:**

$$I_{L(PK)} = \frac{I_{OUT(OC)}}{2} + \frac{I_{L(PP)}}{2}$$

Where

$I_{L(PK)}$  = The peak inductor current in each phase

$I_{L(PP)}$  = The ripple inductor current in each phase

### **EQUATION 4-12:**

$$I_{L(PP)} = \frac{V_{OUT} \times (1-D)}{f_S \times L}$$

Where:

D = Duty cycle

f<sub>S</sub> = Switching frequency

L = Power inductor value

### **EQUATION 4-13:**

$$I_{SET} = I_{L(PK)} - \frac{V_{OUT} \times T_{DLY}}{I}$$

Where:

L = Power inductor value

T<sub>DLY</sub> = Current limit blanking time about 100 ns

### **EQUATION 4-14:**

$$R_{CL} = \frac{I_{SET} \times R_{DSON(MAX)}}{I_{CL(MIN)}}$$

Where:

I<sub>SET</sub> = Overcurrent setpoint

$I_{CL(MIN)}$  = Minimum overcurrent trip point program current

### **EQUATION 4-15:**

$$D = \frac{V_{OUT}}{V_{IN} \times Efficiency}$$

### 4.13.3 EXAMPLE

Consider a 12V-to-3.3V converter at a 30A total output current limit with 1.5  $\mu$ H power inductor and 90% efficiency at full load. Each channel will supply 15A at a 500 kHz switching frequency. The on-resistance of the low side MOSFET is 6 m $\Omega$ .

Equation 4-16 shows how to use the simple method and Equation 4-17 illustrates the accurate method.

### **EQUATION 4-16:**

$$R_{CL} = \frac{\frac{30A}{2} \times 6m\Omega}{180\mu A} = 500\Omega$$

### **EQUATION 4-17:**

$$D = \frac{3.3V}{12V \times 0.9} = 0.3$$

$$I_{L(PP)} = \frac{3.3V \times (1 - 0.3)}{500kHz \times 1.5\mu H} = 3.1A$$

$$I_{L(PK)} = \frac{30A}{2} + \frac{3.1A}{2} = 16.55A$$

$$I_{SET} = 16.55A - \frac{3.3V \times 100ns}{1.5\mu H} = 16.33A$$

$$R_{CL} = \frac{16.33A \times 6m\Omega}{180\mu A} = 544\Omega$$

Using the simple method here would result in a current limit point lower than expected.

This equation sets the target maximum current limit point per channel of the converter, but the actual maximum value will depend on the actual inductor value, actual  $I_{\text{CL}}$  and on resistance of the MOSFET under current limit conditions. This could be in the region of 50% higher and should be considered to ensure that all the power components are within their thermal limits unless thermal protection is implemented separately.

### 4.14 Inductor Current Sensing

Current sharing between the two phases is achieved by sensing the inductor current in each phase. Lossless inductor current sensing is used, which has the advantages of lower power loss and lower cost —over using a discrete resistor in series with the inductor.

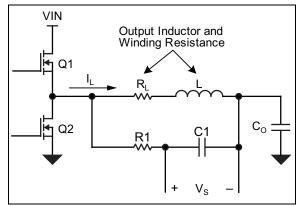

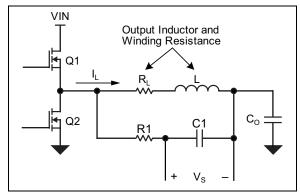

The inductor current sense circuit is shown in Figure 4-16. It extracts the voltage drop across the inductor's DC winding resistance.

FIGURE 4-16: Lossless Inductor Current Sense.

The voltage across capacitor C1 is computed with Equation 4-18.

### **EQUATION 4-18:**

$$V_S = I_L \times \left( R_L \times \frac{\frac{sL}{R_L} + 1}{sC1 \times R1 + 1} \right)$$

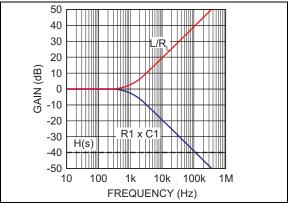

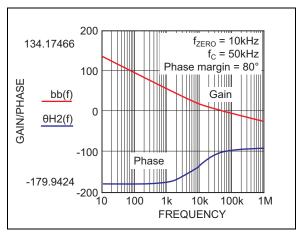

If the R1 × C1 time constant is equal to the L/R<sub>L</sub> time constant, the voltage across capacitor C1 equals the R<sub>L</sub> × I<sub>L</sub>. Figure 4-17 is a plot of this equation and shows the results graphically. It assumes an inductance of 1.5  $\mu$ H, R<sub>L</sub> = 0.01 $\Omega$ , C1 = 0.1  $\mu$ F, and R1 =1.5k. The time constants are equal and diverge at the same rate. The overall impedance, H(s), equals R<sub>L</sub> for all frequencies.

**FIGURE 4-17:** Current Sense Gain/Phase Plot.

**Current Sharing**

4.15

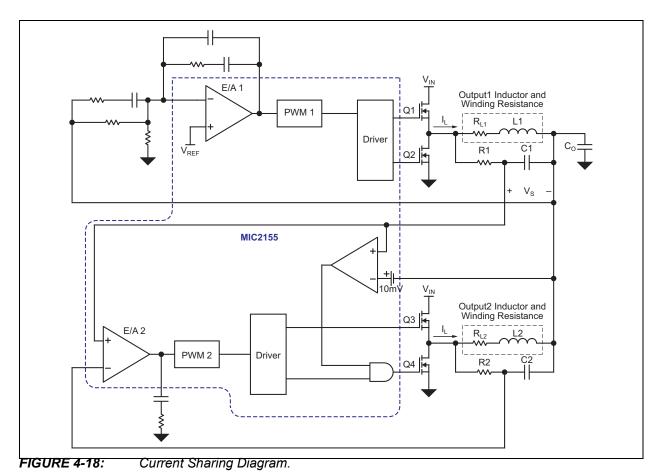

The schematic in Figure 4-18 illustrates the current sharing scheme. The error amplifier in Channel 1, E/A 1, monitors the output voltage and adjusts the duty cycle of Channel 1 to regulate that voltage. The inputs of transconductance error amplifier, E/A 2, are connected to the current sense points of each channel. The error amplifier 2 regulates Channel 2 current by monitoring and making reference to the current sense point of Channel 1 and forcing the current sense point of Channel 2 to be equal.

Any offset or difference in current between the two channels is caused by tolerances in the inductance, DCR, and tolerances of R1, C1, R2 and C2. Additionally, voltage offset in E/A 2 may cause variations in output current sharing. At lower currents, these variations may force the current of Channel 2 to be 0.

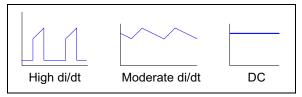

A nominal 10 mV offset inhibits the Channel 2 low-side MOSFET until the output current increases to the magnitude where the voltage across C1 is 10 mV. This prevents the low-side MOSFET of Channel 2 from sinking current to ground during startup or during low current operation.

### 4.16 Startup into a Pre-Biased Output

Soft-start circuitry in a conventional synchronous buck regulator forces the regulator to start up by initially operating at a minimum duty cycle and gradually increasing the duty cycle until the output voltage reaches regulation. In a synchronous buck power supply, a narrow duty cycle means the low-side MOSFET is on for most of the switching period. If the output voltage is not 0V, the wide on time of the low-side MOSFET may discharge the output and cause high reverse current to flow in the inductor.

The MIC2155 is designed to turn on into a pre-biased output without discharging the output. Circuitry in the controller monitors the input and output voltage and forces the soft-start circuit to initially operate at the proper duty cycle. This allows the output to turn on in a controlled fashion without discharging the output. The minimum output voltage for proper operation of the pre-bias startup circuitry is 0.6V. If  $V_{OUT}$  is less than 0.6V, a partial discharge of  $V_{OUT}$  may occur.

### 4.17 Separate Input Supplies

The MIC2155 can operate from two input supplies with different voltages. Each of the two channels can have a different input voltage and still share current. This allows the buck converter supply input to draw power from more than one supply source.

The controller will force the output currents of the two channels to be equal. Since the output voltage and currents of the two channels are the same, the input power drawn from each supply will approximately be the same. The input currents will be inversely proportional to the input voltages of each of the two supplies. For example, if the total output power is 50W and efficiency is 91%, the total input power from both supplies is calculated based on Equation 4-19.

### **EQUATION 4-19:**

$$P_{IN1} = \frac{P_{OUT}}{\eta} = \frac{50W}{0.91} = 55W$$

Each supply contributes approximately half the power. See Equation 4-20.

### **EQUATION 4-20:**

$$P_{IN1} = P_{IN2} = 27.5 W$$

For  $V_{IN1}$  = 12V and  $V_{IN2}$  = 3.3V, the following formula in Equation 4-21 are used.

### **EQUATION 4-21:**

$$\begin{split} I_{IN1} &= \frac{P_{IN1}}{V_{IN1}} = \frac{27.5\,W}{12\,V} = \,2.3\,A \\ I_{IN2} &= \frac{P_{IN2}}{V_{IN2}} = \,\frac{27.5\,W}{3.3\,V} = \,8.3\,A \end{split}$$

## 4.18 Component Selection, Guidelines and Design Example

The following section outlines a procedure for designing a two-phase synchronous buck converter using the MIC2155.

This example will use the following parameters:

$V_{IN} = 12V$   $V_{OUT} = 1.8V$  $I_{OUT} = 30A$

Switching frequency (f<sub>S</sub>) = 500 kHz/channel

### 4.18.1 OUTPUT FILTER SELECTION

The output filter is comprised of the output capacitors and the output inductors. The filter is designed to attenuate the output voltage ripple to the desired value. The output filter components also determine how well the buck converter responds to output load current transients. If output transients are significant, the

output capacitors should be chosen first to meet the transient specification. The output inductor is then selected to insure the filter attenuates the output ripple to meet the specification.

A second commonly used method of designing the filter is to select the inductor value to keep the ripple current between 20% and 30% of the full load output current for that channel. Then select the output capacitance to meet the output voltage ripple specification and output current transient specification.

Values for inductance, peak and RMS inductor currents are required to choose the output inductors. The input and output voltages and the inductance value determine the peak-to-peak inductor ripple current. Output capacitor selection requires information of transient current, RMS capacitor current and output voltage.

There are several tradeoffs to be made when selecting the output inductor. Generally, higher inductance values are used with higher input voltages. Larger peak-to-peak ripple currents increase the power dissipation in the inductor and MOSFETs. Larger output ripple currents also require more output capacitance to smooth out the larger ripple current. Smaller peak-to-peak ripple currents require a larger inductance value and therefore a larger size and more expensive inductor.

Higher switching frequencies allow the use of a small inductance but increase power dissipation in the inductor core and MOSFET switching loss. The MIC2155 switches at 500 kHz/channel and is designed to use a smaller inductor at the expense of higher switching losses and slightly lower efficiency.

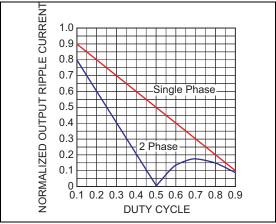

The peak output ripple current for a two-phase converter is shown in Figure 4-19. The graph shows that peak ripple current is a function of duty cycle. Since each channel is 180 degrees out of phase with the other, at 50% duty cycle, the output ripple currents from each channel cancel, and the output ripple current is close to zero.

FIGURE 4-19: Phase Output Ripple Current vs. Duty Cycle.

For this example, with  $V_{IN}$  = 12V,  $V_{OUT}$  = 1.8V and efficiency = 88%, the duty cycle is computed as shown in Equation 4-22.

### **EQUATION 4-22:**

$$D = \frac{V_{OUT}}{\eta \times V_{IN}} = \frac{1.8 \, V}{0.88 \times 12 \, V} = 0.17$$

Figure 4-19 shows the peak-to-peak output ripple current normalized by the maximum value, which is indicated in Equation 4-23.

### **EQUATION 4-23:**

$$I_{OPP(MAX)} = \frac{V_{OUT}}{f_S \times L}$$

The two-phase peak-to-peak output ripple current is less than that for a single-phase conversion. If  $V_{\rm IN}$  varies, the input voltage that generated the highest ripple current should be used for the calculation.

For this example, assume the output transient loading is small, and the filter design is based on output ripple voltage requirement.

The inductance value is calculated by Equation 4-24.

### **EQUATION 4-24:**

$$L = \frac{V_{OUT} \times (\eta \times V_{IN(MAX)} - V_{OUT})}{\eta \times V_{IN(MAX)} \times f_S \times 0.2 \times I_{O1(MAX)}}$$

Where:

$f_S$  = the switching frequency per channel 0.2 = the ratio of AC ripple current to DC maximum output current of each phase channel

$$\begin{split} &V_{IN(MAX)} = \text{the maximum input voltage} \\ &I_{O1(MAX)} \text{ is the DC maximum output current per channel} \\ &\text{or } 1/2 \text{ of the maximum total output current } (I_{OUT(MAX)}) \end{split}$$

$\eta$  is the converter's efficiency

A computation for this example is shown in Equation 4-25.

### **EQUATION 4-25:**

$$L = \frac{1.8\,V \times (0.88 \times 12\,V - 1.8\,V)}{0.88 \times 12\,V \times 500\,kHz \times 0.2 \times 15\,A} = 1\,\mu H$$

The peak-to-peak ripple current for each channel is calculated with Equation 4-26.

### **EQUATION 4-26:**

$$I_{L(PP)} = \frac{V_{OUT} \times (\eta \times V_{IN(MAX)} - V_{OUT})}{\eta \times V_{IN(MAX)} \times f_S \times L}$$

$$I_{L(PP)} = \frac{1.8 V \times (0.88 \times 12 V - 1.8 V)}{0.88 \times 12 V \times 500 kHz \times 1 \mu H} = 3A$$

The output capacitors see less ripple current than each channel because they are out of phase.

The calculation of the peak-to-peak output ripple current normalizing factor is shown in Equation 4-27.

### **EQUATION 4-27:**

$$I_{OPP(MAX)} = \frac{V_{OUT}}{f_S \times L} = \frac{1.8 \, V}{500 \, kHz \times 1 \, \mu H} = 3.6$$

The approximate output ripple current in the two-phase configuration at 17% duty cycle is determined from the graph in Equation 4-19 and can be computed with Equation 4-28.

### **EQUATION 4-28:**

$$I_{OPP} = 0.65 \times \frac{V_{OUT}}{f_S \times L} = 0.65 \times \frac{1.8 \, V}{500 \, kHz \times 1 \, \mu H} = 2.3 \, A$$

For the input and output voltage in this application, going to a two-phase design decreases the total output ripple current from  $3 A_{PP}$  to  $2.3 A_{PP}$ .

The peak inductor current in each channel is equal to the average maximum output current per channel plus one half of the peak-to -peak inductor ripple current. Refer to Equation 4-29.

### **EQUATION 4-29:**

$$I_{L(PK)} = I_{O1(MAX)} + 0.5 \times I_{L(PP)} = 15A + 0.5 \times 3A = 16.5A$$

The RMS inductor current is used to calculate the  $I^2 \times R$  losses in the inductor as shown in Equation 4-30.

### **EQUATION 4-30:**

$$I_{L(RMS)} = I_{O1(MAX)} \times \sqrt{1 + \frac{1}{12} \times \left(\frac{I_{L(PP)}}{I_{O1(MAX)}}\right)^2}$$

$$I_{L(RMS)} = 15A \times \sqrt{1 + \frac{1}{12} \times \left(\frac{3A}{15A}\right)^2} = 15.02A$$

Maximizing efficiency requires the proper selection of core material and minimizing the winding resistance. The high frequency operation of the MIC2155 requires the use of ferrite materials for all but the most cost-sensitive applications. Lower-cost iron powder cores may be used but the increase in core loss will reduce the efficiency of the buck converter. This is

especially noticeable at low output power. The inductor winding resistance decreases efficiency more significantly at the higher output current levels. The winding resistance must be minimized although this usually comes at the expense of a larger inductor size.

The power dissipated in the inductor is equal to the sum of the core and copper losses. At higher output loads, the core losses are usually insignificant and can be ignored. At lower output currents, the core losses can be a significant contributor. Core loss information is usually available from the magnetics vendor.

For this example, a Cooper HCF1305-1R0 inductor was chosen. Core loss for this application was taken from the data sheet and is 15 mW. Winding resistance is 1.9 m $\Omega$ .

Copper loss in the inductor is calculated with Equation 4-31.

### **EQUATION 4-31:**

$$\begin{split} P_{L(Cu)} &= \left(I_{L(RMS)}\right)^2 \times R_{WINDING} \\ &= (15.02A)^2 \times 1.9 m\Omega = \ 0.43 \, W \end{split}$$

The resistance of the copper wire, R<sub>WINDING</sub>, increases with temperature. If so desired, a more accurate calculation can be made if the maximum ambient temperature and temperature rise of the inductor is known. The value of the winding resistance at operating temperature is calculated with Equation 4-32.

### **EQUATION 4-32:**

$$R_{WINDING(HT)} = R_{WINDING(20)} \times (1 + 0.0042 \times (Temp_{HT} - T_{20}))$$

Where

$\label{eq:TempHT} \textit{Temp}_{\text{HT}} = \textit{the temperature of the wire under operating load} \\ \textit{T}_{\text{20}} = \textit{ambient room temperature}$

$R_{WINDING(20)}$  = the resistance of the winding at room temperature, usually specified by the manufacturer

For this example, the approximate power dissipation is 0.43W. From the manufacturer's data sheet, this causes a 20°C rise in inductor temperature. Assuming ambient temperature stayed at 20°C, the maximum winding resistance would be increased from 1.9  $m\Omega$  to the value calculated with Equation 4-33.

### **EQUATION 4-33:**

$$R_{WINDING(HT)} = 1.9m\Omega \times (1 + 0.0042 \times (40^{\circ}C - 20^{\circ}C)) = 2.06m\Omega$$

### 4.18.2 OUTPUT CAPACITOR SELECTION

In this example, the output capacitors are chosen to keep the output voltage ripple below a specified value. The output ripple voltage is determined by the capacitors' ESR (equivalent series resistance) and

capacitance. Voltage rating and RMS current capability are two other important factors in selecting the output capacitors.

Ceramic output capacitors and most polymer capacitors have very low ESR and are recommended for use with the MIC2155. The output capacitance is usually the primary cause of output ripple in ceramic and very low ESR capacitors. The minimum value of  $C_{OLIT}$  is calculated in Equation 4-34.

### **EQUATION 4-34:**

$$C_{OUT} \ge \frac{I_{OPP}}{8 \times \Delta V_{OPP} \times 2 \times f_S}$$

Where:

$\Delta V_{OPP}$  = peak-to-peak output voltage ripple in Steady state  $I_{OPP}$  = peak-to-peak ripple current as see by the capacitors  $f_S$  = per channel switching frequency

Notice the calculation is performed at 2x the switching frequency since the capacitors see ripple current from both phases.

For the example illustrated in Equation 4-35 using  $\Delta V_{OPP}$  = 10 mV, the minimum  $C_{OUT}$  is:

### **EQUATION 4-35:**

$$C_{OUT} {\geq \frac{2.3A}{8 \times 10 mV \times 2 \times 500 kHz}} = 29 \mu F$$

A capacitance at this low value is usually not used in high current converters because of transient output current requirements.

For load transient requirement consideration, the output voltage drop due to the load transient current step is mainly contributed by the output capacitance discharge to support the load current step. The required output capacitance can be estimated with Equation 4-36.

### **EQUATION 4-36:**

$$C_{OUT} > \frac{\Delta I_{LOAD} \times t_{RES}}{\Delta V_{OUT(LDT)}}$$

Where

$\Delta$  I<sub>LOAD</sub> = Load transient current step t<sub>RES</sub> = Load transient response time

$\Delta V_{OUT(LDT)}$  = Output voltage drop due to the load step

For this example, 500  $\mu$ F total capacitance is used. It is split up into four 47  $\mu$ F ceramic capacitors and two 150  $\mu$ F aluminum polymer capacitors connected in parallel.

The total output ripple is a combination of ripple voltages due to the ESR and the output capacitance. The steady-state total output ripple voltage is calculated in Equation 4-37.

### **EQUATION 4-37:**

$$\Delta V_{OUT} = \sqrt{\left(\frac{I_{OPP}}{8 \times C_{OUT} \times 2 \times f_S}\right)^2 + \left(I_{OPP} \times ESR_{COUT}\right)^2}$$

To increase reliability, the recommended voltage rating of the capacitor should be twice the output voltage for a tantalum and 20% greater for an aluminum electrolytic or ceramic.

The output capacitor RMS current is computed in Equation 4-38.

### **EQUATION 4-38:**

$$I_{COUT(RMS)} = \frac{I_{OPP}}{\sqrt{12}} = \frac{2.3A}{\sqrt{12}} = 0.66A$$

The power dissipated in the output capacitors can be calculated with Equation 4-39.

### **EQUATION 4-39:**

$$P_{DISS(COUT)} = \left(I_{COUT(RMS)}\right)^2 \times ESR_{COUT}$$

## 4.18.3 INDUCTOR CURRENT SENSE COMPONENTS

The RC circuit values that sense current across the inductor can be calculated once the inductor is selected. The circuit is shown in Figure 4-20.

FIGURE 4-20:

Inductor Current Sense.

For this example, the inductor has the following parametric values:

$L = 1 \mu H$

$R_I = 1.9 \text{ m}\Omega$

Proper sensing of the DC voltage across the inductor requires the  $L/R_L$  time constant be equal to the R1 × C1 time constant as shown in Equation 4-40.

### **EQUATION 4-40:**

$$\frac{L}{R_I} = C1 \times R1$$

A good range of values for C1 is 0.1  $\mu$ F to 1  $\mu$ F. For this example, C1 is chosen as 0.22  $\mu$ F. R1 is shown in Equation 4-41.

### **EQUATION 4-41:**

$$R1 = \frac{L}{R_L \times C1} = \frac{1 \mu H}{1.9 m\Omega \times 0.22 \mu F} = 2.39 k\Omega$$

### 4.18.4 INPUT CAPACITOR SELECTION

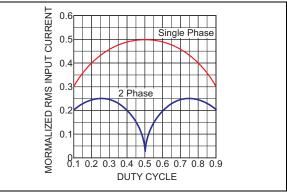

In addition to high-frequency ceramic capacitors, a larger bulk capacitance, either ceramic or aluminum electrolytic should be used to help attenuate ripple on the input and to supply current to the input during large output current transients. The input capacitors must be rated for the RMS input current of the buck converter. RMS input capacitor current is determined by the maximum output current. The graph in Figure 4-21 shows the normalized RMS input ripple current vs. duty cycle. Data is normalized to the output current.

For a two-phase converter operating at 17% duty cycle, the input RMS current is determined at the graph in Figure 4-21 and can be approximated by Equation 4-42.

### **EQUATION 4-42:**

$$I_{CIN(RMS)} \approx I_{OUT(MAX)} \times 0.24 = 30.4 \times 0.24 = 7.24$$

The power dissipated in the input capacitor is indicated in Equation 4-43.

### **EQUATION 4-43:**

$$P_{DISS(CIN)} = (I_{CIN(RMS)})^2 \times ESR_{CIN}$$

FIGURE 4-21: RMS Input Current vs. Duty Cycle.

### 4.18.5 MOSFET SELECTION

External N-channel logic-level power MOSFETs must be used for the high-side and low-side switches. The MOSFET gate-to-source drive voltage from the MIC2155 is regulated by an internal 5V  $V_{\rm DD}$  regulator. Logic level MOSFETs, whose operation is specified at  $V_{\rm GS}$  = 4.5V must be used. The MOSFET on-resistance  $R_{\rm DSON}$  is used to calculate the losses during the MOSFET's conduction time. If operating at 4.5  $V_{\rm IN}$ , without connecting  $V_{\rm DD}$  to  $V_{\rm IN}$ , the gate drive voltage to the high-side FET could be as low as 3.2V. MOSFETs with low  $V_{\rm GS}$  enhanced gates should be used in this situation.

It is important to note the on-resistance of a MOSFET increases at high junction temperature. A 75°C rise in junction temperature increases the channel resistance of the MOSFET by 40% to 75% of the resistance specified at 25°C. This change in resistance must be accounted for when calculating MOSFET power dissipation.

Total gate charge is the charge required to turn the MOSFET on and off under specified operating conditions ( $V_{DS}$  and  $V_{GS}$ ). The gate charge is supplied by the MIC2155 gate drive circuit. Gate charge can be a significant source of power dissipation in the controller due to the high switching frequencies and generally large MOSFETs that are driven. At low output load this power dissipation is noticeable as a reduction in efficiency.

The average current required to drive the MOSFETs is shown in Equation 4-44.

### **EQUATION 4-44:**

$$I_{DD} = Q_G \times f_S$$

Where: