### **DUAL HIGH-SPEED MOSFET DRIVER**

Check for Samples: TPS2811-Q1

#### **FEATURES**

- Qualified for Automotive Applications

- Industry-Standard Driver Replacement

- 25-ns Max Rise/Fall Times and 40-ns Max

Propagation Delay With 1-nF Load, V<sub>CC</sub> = 14 V

- 2-A Peak Output Current, V<sub>CC</sub> = 14 V

- 5-μA Supply Current With Input High or Low

- 4-V to 14-V Supply-Voltage Range; Internal Regulator Extends Range to 40 V

- -40°C to 125°C Ambient-Temperature Operating Range

#### DESCRIPTION

The TPS2811 dual high-speed MOSFET driver is capable of delivering peak currents of 2 A into highly capacitive loads. This performance is achieved with a design that inherently minimizes shoot-through current and consumes an order of magnitude less supply current than competitive products.

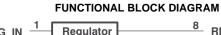

The TPS2811 driver include a regulator to allow operation with supply inputs between 14 V and 40 V. The regulator output can power other circuitry, provided power dissipation does not exceed package limitations. When the regulator is not required, REG\_IN and REG\_OUT can be left disconnected or both can be connected to  $V_{CC}$  or GND.

TPS2811 driver is available in an 8-pin TSSOP package and operates over a ambient temperature range of -40°C to 125°C.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACK       | AGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------|--------------------|-----------------------|------------------|

| -40°C to 125°C | TSSOP – PW | Reel of 2000       | TPS2811QPWRQ1         | 2811Q            |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLVSAE0 -JUNE 2010 www.ti.com

# **REGULATOR DIAGRAM** REG\_IN **7.5** Ω - REG\_OUT

#### **INPUT STAGE DIAGRAM**

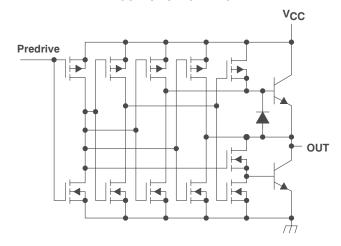

#### **OUTPUT STAGE DIAGRAM**

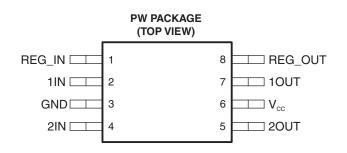

#### **TERMINAL FUNCTIONS**

|                 | TERMINAL | DESCRIPTION                       |

|-----------------|----------|-----------------------------------|

| NAME            | NO.      | DESCRIPTION                       |

| REG_IN          | 1        | Regulator input                   |

| 1IN             | 2        | Input 1                           |

| GND             | 3        | Ground                            |

| 2IN             | 4        | Input 2                           |

| 2OUT            | 5        | Output 2; $2OUT = \overline{2IN}$ |

| V <sub>CC</sub> | 6        | Supply voltage                    |

| 1OUT            | 7        | Output 1; $1OUT = \overline{1IN}$ |

| REG_OUT         | 8        | Regulator output                  |

## **ABSOLUTE MAXIMUM RATINGS**(1)(2)

over operating free-air temperature range (unless otherwise noted)

| $V_{CC}$         | Supply voltage                              |                       | -0.3 V to 15 V |

|------------------|---------------------------------------------|-----------------------|----------------|

|                  | Regulator input voltage range               | VCC -0.3 V to 42 V    |                |

|                  | Input voltage range                         | -0.3 V to VCC +0.5 V  |                |

|                  | Output voltage range                        | -0.5 < V < VCC +0.5 V |                |

|                  | Continuous regulator output current REG_OUT |                       | 25 mA          |

|                  | Continuous output current                   | 1OUT, 2OUT            | ±100 mA        |

| T <sub>A</sub>   | Operating ambient temperature range         |                       | −40°C to 125°C |

| T <sub>stg</sub> | Storage temperature range                   |                       | −65°C to 150°C |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                |                                     |                                       | MIN  | MAX      | UNIT     |

|----------------|-------------------------------------|---------------------------------------|------|----------|----------|

|                | Regulator input voltage             |                                       | 8    | 40       | <b>V</b> |

| $V_{CC}$       | Supply voltage                      |                                       | 4    | 14       | V        |

|                | Input voltage                       | 1IN, 2IN                              | -0.3 | $V_{CC}$ | <b>V</b> |

|                | Continuous regulator output current | REG_OUT                               | 0    | 20       | mA       |

| T <sub>A</sub> | Operating ambient temperature range | · · · · · · · · · · · · · · · · · · · | -40  | 125      | °C       |

#### **ELECTRICAL CHARACTERISTICS**

over recommended operating ambient temperature range,  $V_{CC} = 10 \text{ V}$ , REG\_IN open,  $C_L = 1 \text{ nF}$  (unless otherwise noted)

|                 | PARAMETER                              | TEST CONDITIONS                                | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|-----------------|----------------------------------------|------------------------------------------------|------|--------------------|------|------|

| INPU            | rs                                     |                                                |      |                    |      |      |

|                 |                                        | V <sub>CC</sub> = 5 V                          |      | 3.3                | 4    |      |

| $V_{T+}$        | Positive-going input threshold voltage | V <sub>CC</sub> = 10 V                         |      | 5.8                | 9    | V    |

|                 |                                        | V <sub>CC</sub> = 14 V                         |      | 8.3                | 13   |      |

|                 |                                        | V <sub>CC</sub> = 5 V                          | 1    | 1.6                |      |      |

| $V_{T_{-}}$     | Negative-going input threshold voltage | V <sub>CC</sub> = 10 V                         | 1    | 4.2                |      | V    |

|                 |                                        | V <sub>CC</sub> = 14 V                         | 1    | 6.2                |      |      |

|                 | Input hysteresis                       | V <sub>CC</sub> = 5 V                          |      | 1.6                |      | V    |

| II              | Input current                          | Inputs = 0 V or V <sub>CC</sub>                | -1   | 0.2                | 1    | μA   |

| Cı              | Input capacitance                      |                                                |      | 5                  | 10   | pF   |

| OUTP            | PUTS                                   |                                                |      |                    |      |      |

| .,              | High level entert valle en             | I <sub>O</sub> = −1 mA                         | 9.75 | 9.9                |      | V    |

| V <sub>OH</sub> | High-level output voltage              | $I_O = -100 \text{ mA}$                        | 8    | 9.1                |      | V    |

| V               | Low lovel output voltogo               | I <sub>O</sub> = 1 mA                          |      | 0.18               | 0.25 | V    |

| V <sub>OL</sub> | Low-level output voltage               | I <sub>O</sub> = 100 mA                        |      | 1                  | 2    | V    |

| Io              | Peak output current                    | V <sub>CC</sub> = 10 V                         |      | 2                  |      | Α    |

| REGU            | JLATOR                                 |                                                |      |                    | •    |      |

| Vo              | Output voltage                         | 14 ≤ REG_IN ≤ 40 V, 0 ≤ I <sub>O</sub> ≤ 20 mA | 10   | 11.5               | 13   | V    |

|                 | Output voltage in dropout              | I <sub>O</sub> = 10 mA, REG_IN = 10 V          | 9    | 9.6                |      | V    |

| SUPP            | LY CURRENT                             |                                                | *    |                    | •    |      |

| I <sub>CC</sub> | Supply current into V <sub>CC</sub>    | Inputs high or low                             |      | 0.2                | 5    | μΑ   |

|                 | Supply current into REG_IN             | REG_IN = 20 V, REG_OUT open                    |      | 40                 | 100  | μΑ   |

<sup>(1)</sup> Typical values are at  $T_A = 25$ °C unless otherwise noted.

<sup>(2)</sup> All voltages are with respect to device GND pin.

SLVSAE0 -JUNE 2010 www.ti.com

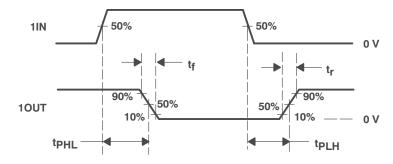

#### **SWITCHING CHARACTERISTICS**

over recommended operating ambient temperature range, REG\_IN open,  $C_L = 1$  nF (unless otherwise noted)

|                  | PARAMETER                                        | TEST CONDITIONS        | MIN TYP <sup>(1)</sup> | MAX | UNIT |

|------------------|--------------------------------------------------|------------------------|------------------------|-----|------|

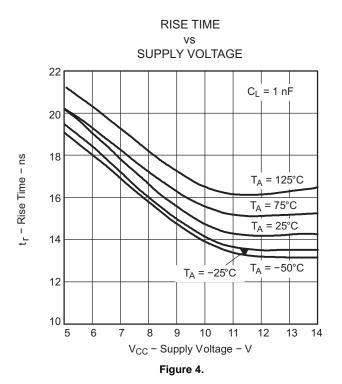

|                  |                                                  | V <sub>CC</sub> = 14 V | 14                     | 25  |      |

| t <sub>r</sub>   | Rise time                                        | V <sub>CC</sub> = 10 V | 15                     | 30  | ns   |

|                  |                                                  | V <sub>CC</sub> = 5 V  | 20                     | 35  |      |

|                  |                                                  | V <sub>CC</sub> = 14 V | 15                     | 25  |      |

| t <sub>f</sub>   | Fall time                                        | V <sub>CC</sub> = 10 V | 15                     | 30  | ns   |

|                  |                                                  | V <sub>CC</sub> = 5 V  | 18                     | 35  |      |

|                  |                                                  | V <sub>CC</sub> = 14 V | 25                     | 40  |      |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | V <sub>CC</sub> = 10 V | 25                     | 45  | ns   |

|                  |                                                  | V <sub>CC</sub> = 5 V  | 34                     | 50  |      |

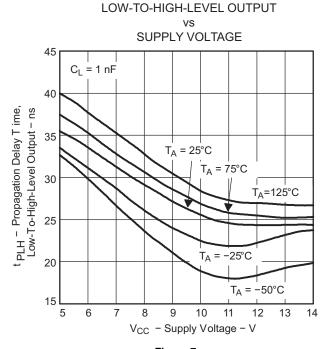

|                  |                                                  | V <sub>CC</sub> = 14 V | 24                     | 40  |      |

| t <sub>PLH</sub> | Propagation delay time low-to-high-level output  | V <sub>CC</sub> = 10 V | 26                     | 45  | ns   |

|                  |                                                  | V <sub>CC</sub> = 5 V  | 36                     | 50  |      |

<sup>(1)</sup> Typical values are at  $T_A = 25^{\circ}C$  unless otherwise noted.

#### PARAMETER MEASUREMENT INFORMATION

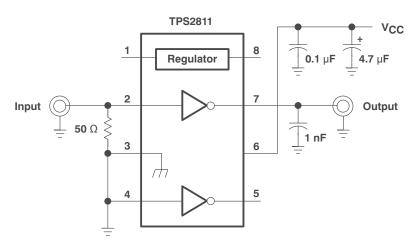

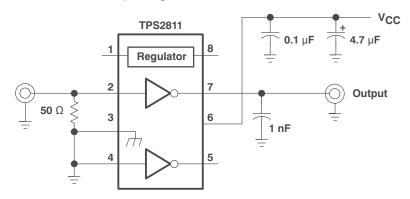

Figure 1. Test Circuit For Measurement of Switching Characteristics

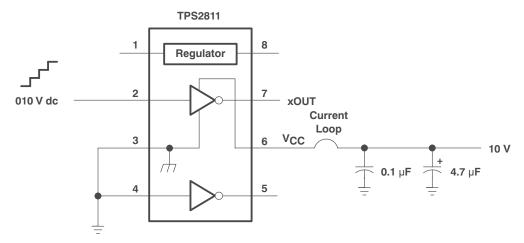

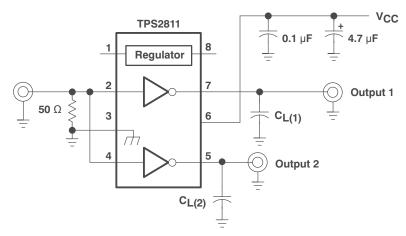

Figure 2. Shoot-Through Current Test Setup

Figure 3. Typical Timing Diagram

SLVSAE0 -JUNE 2010

www.ti.com

#### TYPICAL CHARACTERISTICS

# **Table 1. Characteristics Graphs and Application Information**

| PARAMETER                                                 |          | vs PARAMETER 2            | FIGURE     |

|-----------------------------------------------------------|----------|---------------------------|------------|

| Typical Characteristics                                   |          |                           |            |

| Rise time                                                 | Supply   | voltage                   | 4          |

| Fall time                                                 | Supply   | voltage                   | 5          |

| Propagation delay time                                    | Supply   | voltage                   | 6, 7       |

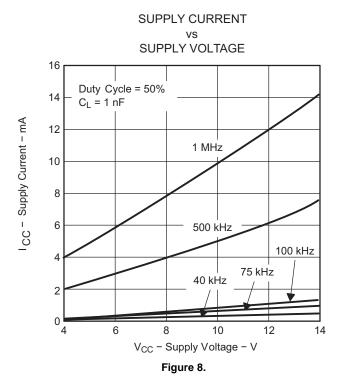

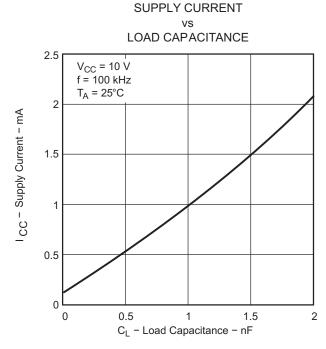

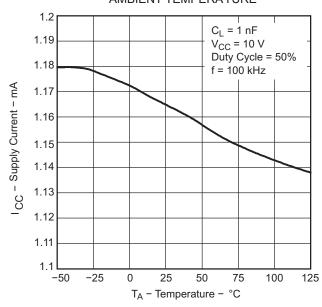

|                                                           | Supply   | voltage                   | 8          |

| Supply current                                            | Load ca  | pacitance                 | 9          |

|                                                           | Ambien   | t temperature             | 0          |

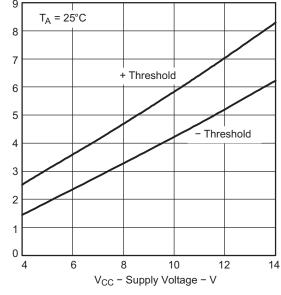

| nput threshold voltage                                    | Supply   | voltage                   | 11         |

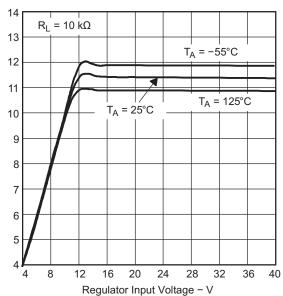

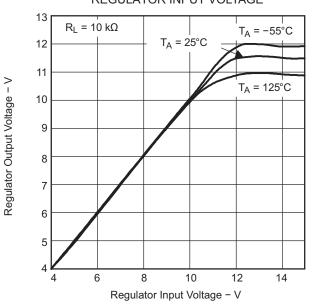

| Regulator output voltage                                  | Regulat  | or input voltage          | 12, 13     |

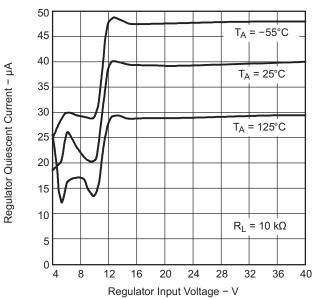

| Regulator quiescent current                               | Regulat  | or input voltage          | 14         |

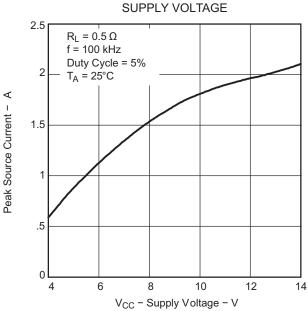

| Peak source current                                       | Supply   | voltage                   | 15         |

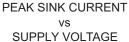

| Peak sink current                                         | Supply   | voltage                   | 16         |

| Phoof through august                                      | Input vo | ltage, high-to-low        | 17         |

| Shoot-through current                                     | Input vo | ltage, low-to-high        | 18         |

| General Applications                                      |          |                           |            |

| Switching test circuits and application information       |          |                           | 19, 20     |

| Voltage of 10LIT vs 20LIT                                 | Time     | Low-to-high               | 21, 22, 23 |

| Voltage of 10UT vs 20UT                                   | Time     | High-to-low               | 24, 25, 26 |

| Circuit for Measuring Paralleled Switching Characteristic | cs       |                           |            |

| Switching test circuits and application information       |          |                           | 27         |

| pout veltage ve output veltage                            | Time     | Low-to-high               | 28, 30     |

| nput voltage vs output voltage                            | Time     | High-to-low               | 29, 31     |

| Hex-1 to Hex-4 Application Information                    |          |                           |            |

| Oriving test circuit and application information          |          |                           | 32         |

|                                                           |          | Hex-1 size                | 33         |

|                                                           |          | Hex-2 size                | 36         |

| Orain-source voltage vs drain current                     | Time     | Hex-3 size                | 39         |

|                                                           |          | Hex-4 size                | 41         |

|                                                           |          | Hex-4 size parallel drive | 45         |

|                                                           |          | Hex-1 size                | 34         |

|                                                           |          | Hex-2 size                | 37         |

|                                                           | Time     | Hex-3 size                | 40         |

|                                                           |          | Hex-4 size                | 43         |

|                                                           |          | Hex-4 size parallel drive | 46         |

|                                                           |          | Hex-1 size                | 35         |

|                                                           |          | Hex-2 size                | 38         |

|                                                           | Time     | Hex-3 size                | 42         |

|                                                           |          | Hex-4 size                | 44         |

|                                                           |          | Hex-4 size parallel drive | 47         |

| Synchronous Buck Regulator Application                    |          |                           |            |

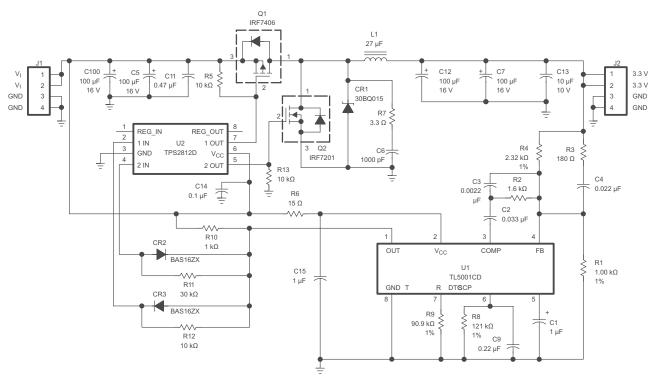

| 3.3-V 3-A Synchronous-Rectified Buck Regulator Circuit    |          |                           | 48         |

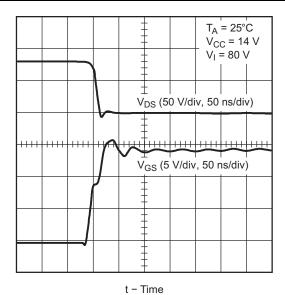

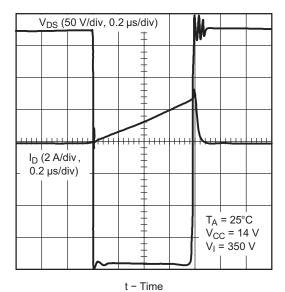

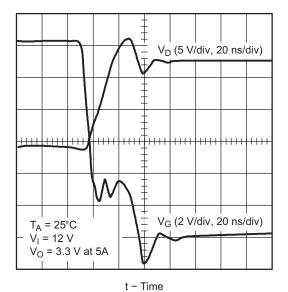

| Q1 drain voltage vs gate voltage at turn-on               | Time     |                           | 49         |

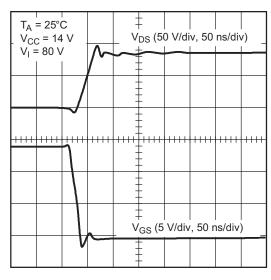

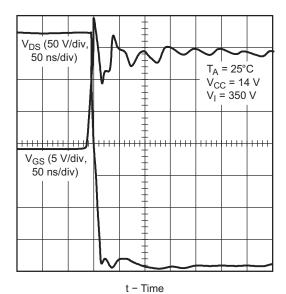

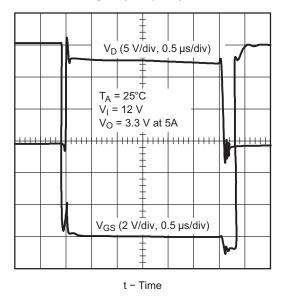

| Q1 drain voltage vs gate voltage at turn-off              | Time     |                           | 50         |

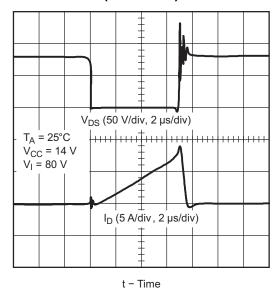

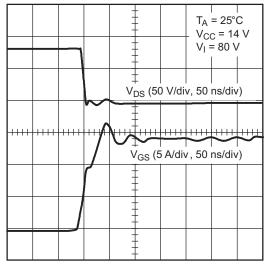

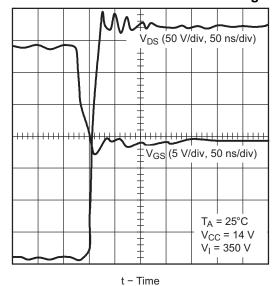

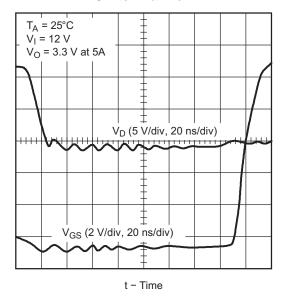

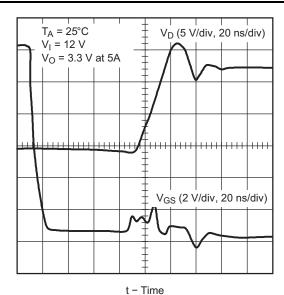

| Q1 drain voltage vs Q2 gate-source voltage                | Time     |                           | 51, 52, 53 |

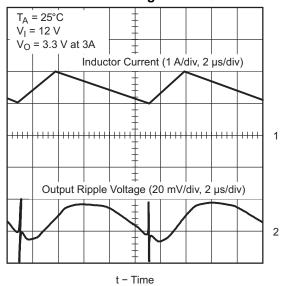

| Output ripple voltage vs inductor current                 | Time     | 3 A                       | 54         |

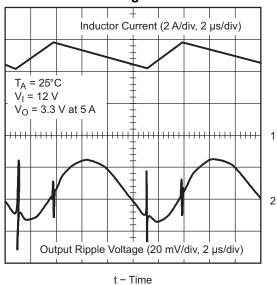

| Output hppie voltage vs inductor current                  | Time     | 5 A                       | 55         |

22  $C_L = 1 nF$ 20 18 - Fall Time - ns  $T_A = 125^{\circ}C$ T<sub>A</sub> = 75°C 16  $T_A = 25^{\circ}C$ 14  $T_A = -50$ °C T<sub>A</sub> = −25°C 12 10 6 8 9 10 11 12 13 14 5 V<sub>CC</sub> - Supply Voltage - V Figure 5.

**FALL TIME**

SUPPLY VOLTAGE

PROPAGATION DELAY TIME, HIGH-TO-LOW-LEVEL OUTPUT SUPPLY VOLTAGE 45  $C_L = 1 nF$ 40 : PHL - Propagation Delay T ime, High-To-Low-Level Output - ns 35 30  $T_A = 125^{\circ}C$ 25  $T_A = 25^{\circ}C$  $T_A = 75^{\circ}C$ 20  $T_A = -50^{\circ}C$  $T_A = -25^{\circ}C$ 15 10 6 9 5 8 13 14 V<sub>CC</sub> - Supply Voltage - V

Figure 6.

PROPAGATION DELAY TIME,

SUPPLY CURRENT

vs

AMBIENT TEMPERATURE

1.2

1.19

C<sub>L</sub> = 1 nF

INPUT THRESHOLD VOLTAGE

VS

SUPPLY VOLTAGE

TA = 25°C

Figure 9.

Figure 10.

Figure 11.

V<sub>IT</sub> - Input Threshold Voltage - V

Regulator Output Voltage - V

www.ti.com SLVSAE0 -JUNE 2010

# REGULATOR OUTPUT VOLTAGE

#### REGULATOR INPUT VOLTAGE

Figure 12.

# REGULATOR QUIESCENT CURRENT

#### REGULATOR INPUT VOLTAGE

Figure 14.

# REGULATOR OUTPUT VOLTAGE vs REGULATOR INPUT VOLTAGE

Figure 13.

# PEAK SOURCE CURRENT vs

Figure 15.

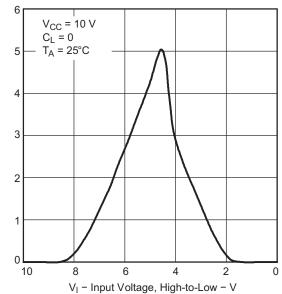

SHOOT-THROUGH CURRENT

#### INPUT VOLTAGE, HIGH-TO-LOW

Figure 17.

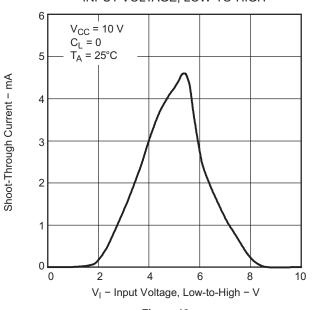

#### SHOOT-THROUGH CURRENT

#### vs INPUT VOLTAGE, LOW-TO-HIGH

Figure 18.

Shoot-Through Current - mA

#### **APPLICATION INFORMATION**

The TPS2811 circuits each contain one regulator and two MOSFET drivers. The regulator can be used to limit  $V_{CC}$  to between 10 V and 13 V for a range of input voltages from 14 V to 40 V, while providing up to 20 mA of dc drive. The TPS2811 has inverting drivers. These MOSFET drivers are capable of supplying up to 2.1 A or sinking up to 1.9 A (see Figures 15 and 16) of instantaneous current to n-channel or p-channel MOSFETs. The TPS2811 MOSFET drivers have very fast switching times combined with very short propagation delays. These features enhance the operation of today's high-frequency circuits.

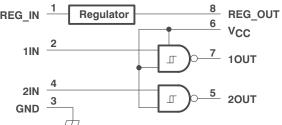

The CMOS input circuit has a positive threshold of approximately 2/3 of  $V_{CC}$ , with a negative threshold of 1/3 of  $V_{CC}$ , and a very high input impedance in the range of  $109\Omega$ . Noise immunity is also very high because of the Schmitt-trigger switching. In addition, the design is such that the normal shoot-through current in CMOS (when the input is biased halfway between  $V_{CC}$  and ground) is limited to less than 6 mA. The limited shoot-through is evident in the graphs in Figures 17 and 18. The input stage shown in the functional block diagram better illustrates the way the front end works. The circuitry of the device is such that regardless of the rise and/or fall time of the input signal, the output signal will always have a fast transition speed; this basically isolates the waveforms at the input from the output. Therefore, the specified switching times are not affected by the slopes of the input waveforms.

The basic driver portion of the circuits operate over a supply voltage range of 4 V to 14 V with a maximum bias current of 5  $\mu$ A. Each driver consists of a CMOS input and a buffered output with a 2-A instantaneous drive capability. They have propagation delays of less than 30 ns and rise and fall times of less than 20 ns each. Placing a 0.1- $\mu$ F ceramic capacitor between V<sub>CC</sub> and ground is recommended; this will supply the instantaneous current needed by the fast switching and high current surges of the driver when it is driving a MOSFET.

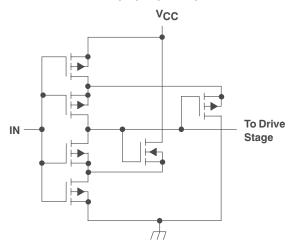

The output circuit is also shown in the functional block diagram. This driver uses a unique combination of a bipolar transistor in parallel with a MOSFET for the ability to swing from VCC to ground while providing 2 A of instantaneous driver current. This unique parallel combination of bipolar and MOSFET output transistors provides the drive required at  $V_{CC}$  and ground to guarantee turn-off of even low-threshold MOSFETs. Typical bipolar-only output devices don't easily approach  $V_{CC}$  or ground.

The regulator included in the TPS2811 has an input voltage range of 14 V to 40 V. It produces an output voltage of 10 V to 13 V and is capable of supplying from 0 to 20 mA of output current. In grounded source applications, this extends the overall circuit operation to 40 V by clamping the driver supply voltage ( $V_{CC}$ ) to a safe level for both the driver and the MOSFET gate. The bias current for full operation is a maximum of 150  $\mu$ A. A 0.1- $\mu$ F capacitor connected between the regulator output and ground is required to ensure stability. For transient response, an additional 4.7- $\mu$ F electrolytic capacitor on the output and a 0.1- $\mu$ F ceramic capacitor on the input will optimize the performance of this circuit. When the regulator is not in use, it can be left open at both the input and the output, or the input can be shorted to the output and tied to either the  $V_{CC}$  or the ground pin of the chip.

Product Folder Link(s): TPS2811-Q1

#### **Matching and Paralleling Connections**

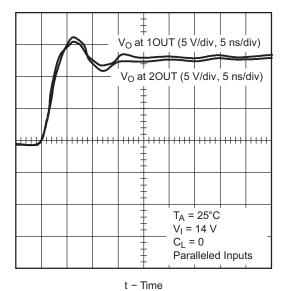

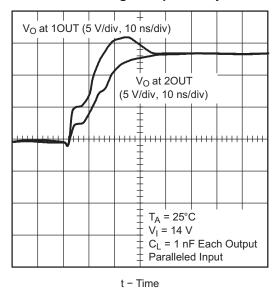

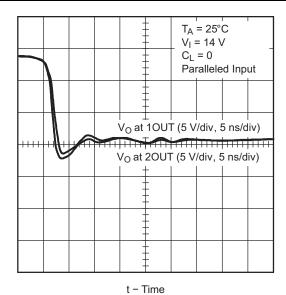

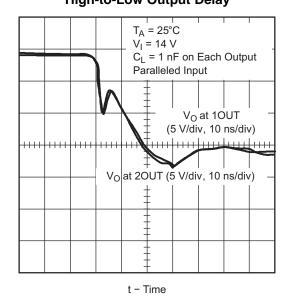

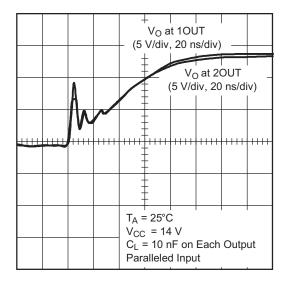

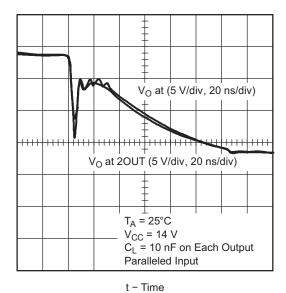

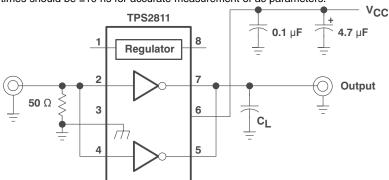

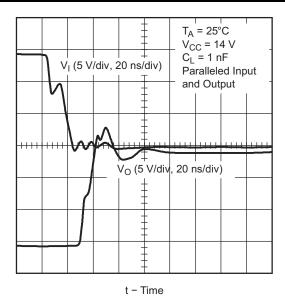

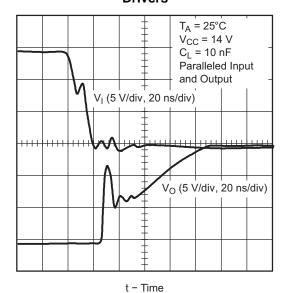

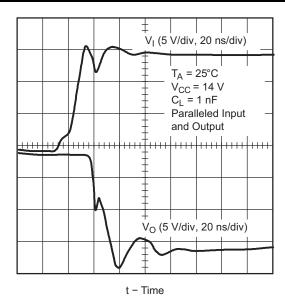

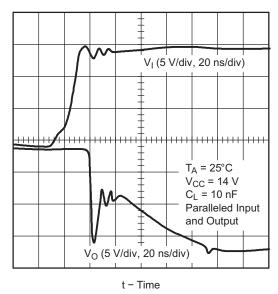

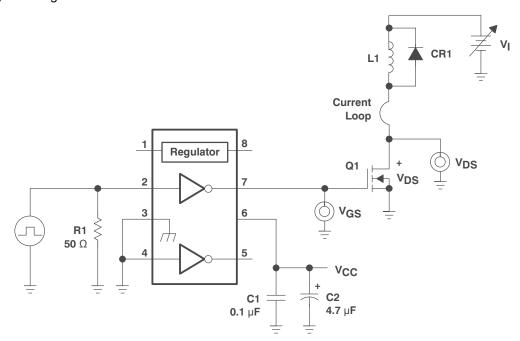

Figure 19 and Figure 20 show the delays for the rise and fall time of each channel. As can be seen on a 5-ns scale, there is very little difference between the two channels at no load. Figures 23 and 24 show the difference between the two channels for a 1-nF load on each output. There is a slight delay on the rising edge, but little or no delay on the falling edge. As an example of extreme overload, Figures 25 and 26 show the difference between the two channels, or two drivers in the package, each driving a 10-nF load. As would be expected, the rise and fall times are significantly slowed down. Figures 28 and 29 show the effect of paralleling the two channels and driving a 1-nF load. A noticeable improvement is evident in the rise and fall times of the output waveforms. Finally, Figures 30 and 31 show the two drivers being paralleled to drive the 10-nF load and as could be expected the waveforms are improved. In summary, the paralleling of the two drivers in a package enhances the capability of the drivers to handle a larger load. Because of manufacturing tolerances, it is not recommended to parallel drivers that are not in the same package.

Figure 19. Test Circuit for Measuring Switching Characteristics

A. Input rise and fall times should be ≤10 ns for accurate measurement of ac parameters.

Figure 20. Test Circuit for Measuring Switching Characteristics With the Inputs Connected in Parallel

12

Figure 21. Voltage of 10UT vs Voltage at 20UT, Low-to-High Output Delay

Figure 23. Voltage at 10UT vs Voltage at 20UT, Low-to-High Output Delay

Figure 22. Voltage at 10UT vs Voltage at 20UT, High-to-Low Output Delay

Figure 24. Voltage at 10UT vs Voltage at 20UT, High-to-Low Output Delay

TEXAS INSTRUMENTS

SLVSAE0 -JUNE 2010 www.ti.com

t - Time

Figure 25. Voltage at 10UT vs Voltage at 20UT, Low-to-High Output Delay

Figure 26. Voltage at 10UT vs Voltage at 20UT, High-to-Low Output Delay

A. Input rise and fall times should be ≤10 ns for accurate measurement of ac parameters.

Figure 27. Test Circuit for Measuring Paralleled Switching Characteristics

Submit Documentation Feedback

Figure 28. Input Voltage vs Output Voltage, Low-to-High Propagation Delay of Paralleled Drivers

Figure 30. Input Voltage vs Output Voltage, Low-to-High Propagation Delay of Paralleled Drivers

Figure 29. Input Voltage vs Output Voltage, High-to-Low Propagation Delay of Paralleled Drivers

Figure 31. Input Voltage vs Output Voltage, High-to-Low Propagation Delay of Paralleled Drivers

SLVSAE0 -JUNE 2010 www.ti.com

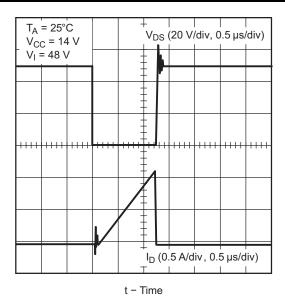

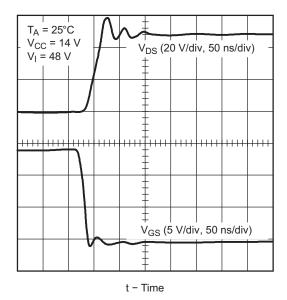

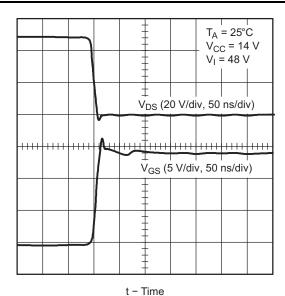

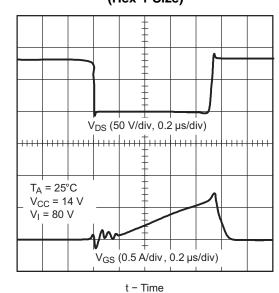

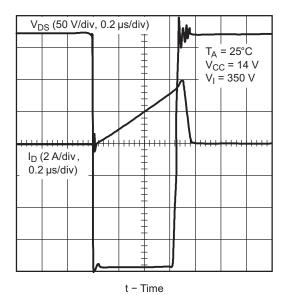

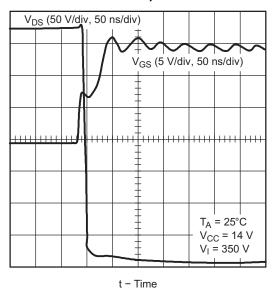

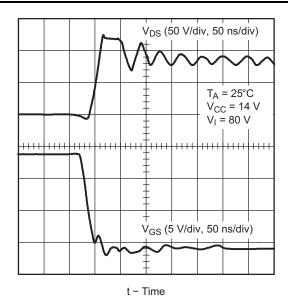

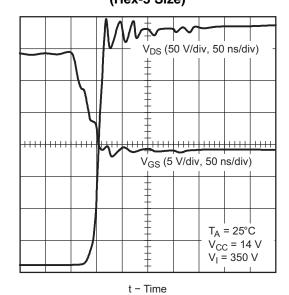

Figures 33 through 47 illustrate the performance of the TPS2811 driving MOSFETs with clamped inductive loads, similar to what is encountered in discontinuous-mode flyback converters. The MOSFETs that were tested range in size from Hex-1 to Hex-4, although the TPS28xx family is only recommended for Hex-3 or below.

The test circuit is shown in Figure 32. The layout rules observed in building the test circuit also apply to real applications. Decoupling capacitor C1 is a 0.1- $\mu$ F ceramic device, connected between V<sub>CC</sub> and GND of the TPS2811, with short lead lengths. The connection between the driver output and the MOSFET gate, and between GND and the MOSFET source, are as short as possible to minimize inductance. Ideally, GND of the driver is connected directly to the MOSFET source. The tests were conducted with the pulse generator frequency set very low to eliminate the need for heat sinking, and the duty cycle was set to turn off the MOSFET when the drain current reached 50% of its rated value. The input voltage was adjusted to clamp the drain voltage at 80% of its rating.

As shown, the driver is capable of driving each of the Hex-1 through Hex-3 MOSFETs to switch in 20 ns or less. Even the Hex-4 is turned on in less than 20 ns. Figures 45, 46 and 47 show that paralleling the two drivers in a package enhances the gate waveforms and improves the switching speed of the MOSFET. Generally, one driver is capable of driving up to a Hex-4 size. The TPS2811 family is even capable of driving large MOSFETs that have a low gate charge.

Figure 32. TPS2811 Driving Hex-1 through Hex-4 Devices

Submit Documentation Feedback

Figure 33. Drain-Source Voltage vs Drain Current, TPS2811 Driving an IRFD014 (Hex-1 Size)

Figure 35. Drain-Source Voltage vs Gate-Source Voltage, at Turn-off, TPS2811 Driving an IRFD014 (Hex-1 Size)

Figure 34. Drain-Source Voltage vs Gate-Source Voltage, at Turn-on, TPS2811 Driving an IRFD014 (Hex-1 Size)

Figure 36. Drain-Source Voltage vs Drain Current, TPS2811 Driving an IRFD120 (Hex-2 Size)

TEXAS INSTRUMENTS

SLVSAE0 -JUNE 2010 www.ti.com

Figure 37. Drain-Source Voltage vs Gate-Source Voltage, at Turn-on, TPS2811 Driving an IRFD120 (Hex-2 Size)

Figure 39. Drain-Source Voltage vs Drain Current, TPS2811 Driving an IRF530 (Hex-3 Size)

t - Time

Figure 38. Drain-Source Voltage vs Gate-Source Voltage, at Turn-off, TPS2811 Driving an IRFD120 (Hex-2 Size)

t - Time

Figure 40. Drain-Source Voltage vs Gate-Source Voltage, at Turn-on, TPS2811 Driving an IRF530 (Hex-3 Size)

Submit Documentation Feedback

Figure 41. Drain-Source Voltage vs Drain Current, One Driver, TPS2811 Driving an IRF840 (Hex-4 Size)

Figure 43. Drain-Source Voltage vs Gate-Source Voltage, at Turn-on, One Driver, TPS2811 Driving an IRF840 (Hex-4 Size)

Figure 42. Drain-Source Voltage vs Gate-Source Voltage, at Turn-off, TPS2811 Driving an IRF530 (Hex-3 Size)

Figure 44. Drain-Source Voltage vs Gate-Source Voltage, at Turn-off, One Driver, TPS2811 Driving an IRF840 (Hex-4 Size)

Copyright © 2010, Texas Instruments Incorporated Submit Documentation Feedback

TEXAS INSTRUMENTS

SLVSAE0 -JUNE 2010 www.ti.com

Figure 45. Drain-Source Voltage vs Drain Current, Parallel Drivers, TPS2811 Driving an IRF840 (Hex-4 Size)

Figure 46. Drain-Source Voltage vs Gate-Source Voltage, at Turn-on, Parallel Drivers, TPS2811 Driving an IRF840 (Hex-4 Size)

Figure 47. Drain-Source Voltage vs Gate-Source Voltage, at Turn-off, Parallel Drivers, TPS2811 Driving an IRF840 (Hex-4 Size)

20

#### Synchronous Buck Regulator

Figure 48 is the schematic for a 100-kHz synchronous-rectified buck converter implemented with a TL5001 pulse-width-modulation (PWM) controller and a TPS2812 driver. The bill of materials is provided in Table 1. The converter operates over an input range from 5.5 V to 12 V and has a 3.3-V output capable of supplying 3 A continuously and 5 A during load surges. The converter achieves an efficiency of 90.6% at 3 A and 87.6% at 5 A. Figures 49 and 50 show the power switch switching performance. The output ripple voltage waveforms are documented in Figures 54 and 55.

The TPS2812 drives both the power switch, Q2, and the synchronous rectifier, Q1. Large shoot-through currents, caused by power switch and synchronous rectifier remaining on simultaneously during the transitions, are prevented by small delays built into the drive signals, using CR2, CR3, R11, R12, and the input capacitance of the TPS2812. These delays allow the power switch to turn off before the synchronous rectifier turns on and vice versa. Figure 51 shows the delay between the drain of Q2 and the gate of Q1; expanded views are provided in Figures 52 and 53.

NOTE: If the parasitics of the external circuit cause the voltage to violate the Absolute Maximum Rating for the Output pins, Schottky diodes should be added from ground to output and from output to V<sub>CC</sub>.

Figure 48. 3.3-V 3-A Synchronous-Rectified Buck Regulator Circuit

SLVSAE0 -JUNE 2010 www.ti.com

# Table 2. Bill of Materials, 3.3-V, 3-A Synchronous-Rectified Buck Converter<sup>(1)</sup>

| REFERENCE     | DESCRIPTION                              | VENDO                   | OR           |  |

|---------------|------------------------------------------|-------------------------|--------------|--|

| U1            | TL5001CD, PWM                            | Texas Instruments       | 972-644-5580 |  |

| U2            | TPS2812D, N.I. MOSFET Driver             | Texas Instruments       | 972-644-5580 |  |

| CR1           | 3 A, 15 V, Schottky, 30BQ015             | International Rectifier | 310-322-3331 |  |

| CR2,CR3       | Signal Diode, BAS16ZX                    | Zetex                   | 516-543-7100 |  |

| C1            | 1 μF, 16 V, Tantalum                     |                         |              |  |

| C2            | 0.033 μF, 50 V                           |                         |              |  |

| C3            | 0.0022 μF, 50 V                          |                         |              |  |

| C4            | 0.022 μF, 50 V                           |                         |              |  |

| C5,C7,C10,C12 | 100 μF, 16 V, Tantalum, TPSE107M016R0100 | AVX                     | 800-448-9411 |  |

| C6            | 1000 pF, 50 V                            |                         |              |  |

| C9            | 0.22 μF, 50 V                            |                         |              |  |

| C11           | 0.47 μF, 50 V, Z5U                       |                         |              |  |

| C13           | 10 μF, 10 V, Ceramic, CC1210CY5V106Z     | TDK                     | 708-803-6100 |  |

| C14           | 0.1 μF, 50 V                             |                         |              |  |

| C15           | 1.0 μF, 50 V                             |                         |              |  |

| J1,J2         | 4-Pin Header                             | Nova Magnetics, Inc.    | 972-272-8287 |  |

| L1            | 27 μH, 3 A/5 A, SML5040                  | International Rectifier | 310-322-3331 |  |

| Q1            | IRF7406, P-FET                           | International Rectifier | 310-322-3331 |  |

| Q2            | IRF7201, N-FET                           |                         |              |  |

| R1            | 1.00 kΩ, 1%                              |                         |              |  |

| R2            | 1.6 kΩ                                   |                         |              |  |

| R3            | 180 Ω                                    |                         |              |  |

| R4            | 2.32 kΩ, 1 %                             |                         |              |  |

| R5,R12,R13    | 10 kΩ                                    |                         |              |  |

| R6            | 15 Ω                                     |                         |              |  |

| R7            | 3.3 Ω                                    |                         |              |  |

| R8            | 121 kΩ, 1%                               |                         |              |  |

| R9            | 90.9 kΩ, 1%                              |                         |              |  |

| R10           | 1 kΩ                                     |                         |              |  |

| R11           | 30 kΩ                                    |                         |              |  |

<sup>(1)</sup> Unless otherwise specified, capacitors are X7R ceramics, and resistors are 5%, 1/10 W.

Product Folder Link(s): TPS2811-Q1

Figure 49. Q1 Drain Voltage vs Gate Voltage, at Switch Turn-on

Figure 51. Q1 Drain Voltage vs Q2 Gate-Source Voltage

- - - - -

Figure 50. Q1 Drain Voltage vs Gate Voltage, at Switch Turn-off

Figure 52. Q1 Drain Voltage vs Q2 Gate-Source Voltage

Copyright © 2010, Texas Instruments Incorporated Submit Documentation Feedback

SLVSAE0 -JUNE 2010 www.ti.com

Figure 53. Q1 Drain Voltage vs Q2 Gate-Source Voltage

Figure 54. Output Ripple Voltage vs Inductor Current, at 3 A

Figure 55. Output Ripple Voltage vs Inductor Current, at 5 A

Submit Documentation Feedback

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                         |         |

| TPS2811QPWRQ1    | ACTIVE | TSSOP        | PW                 | 8    | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | 2811Q                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS2811-Q1:

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

• Catalog: TPS2811

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

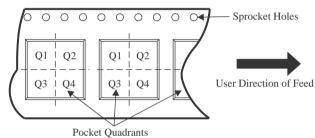

#### TAPE AND REEL INFORMATION

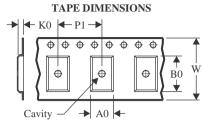

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

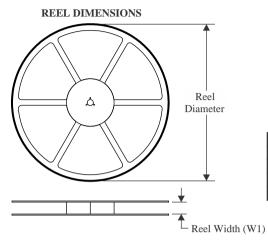

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2811QPWRQ1 | TSSOP           | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

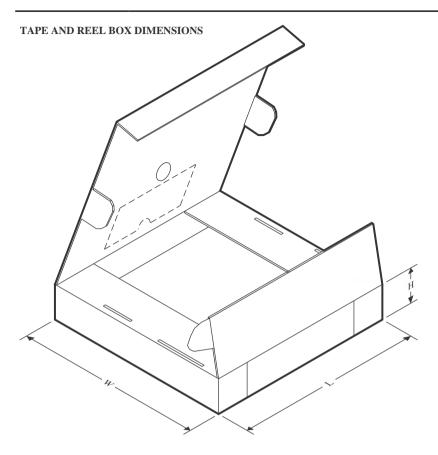

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TPS2811QPWRQ1 | TSSOP        | PW              | 8    | 2000 | 356.0       | 356.0      | 35.0        |  |

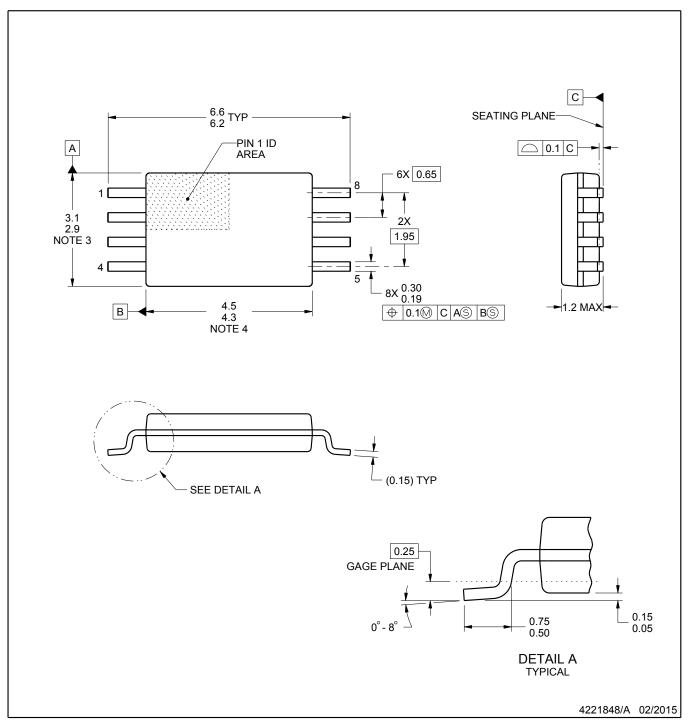

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153, variation AA.

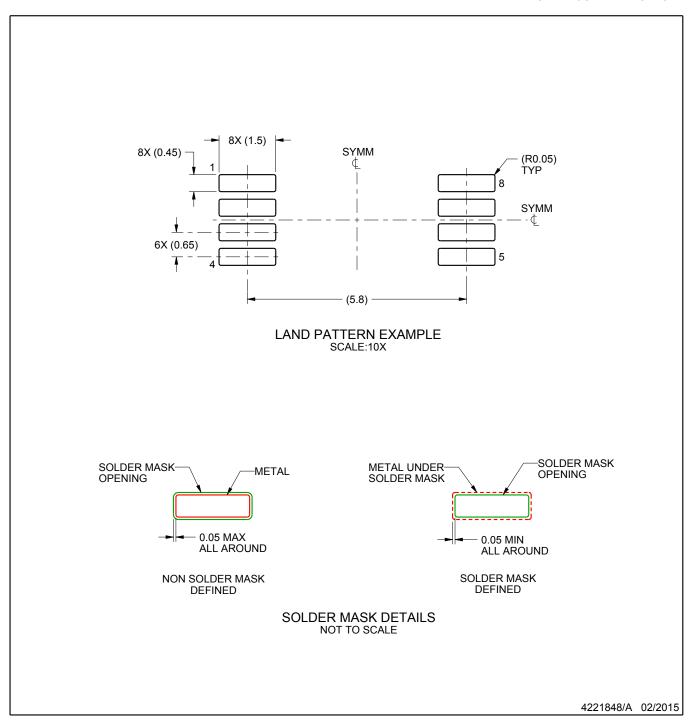

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

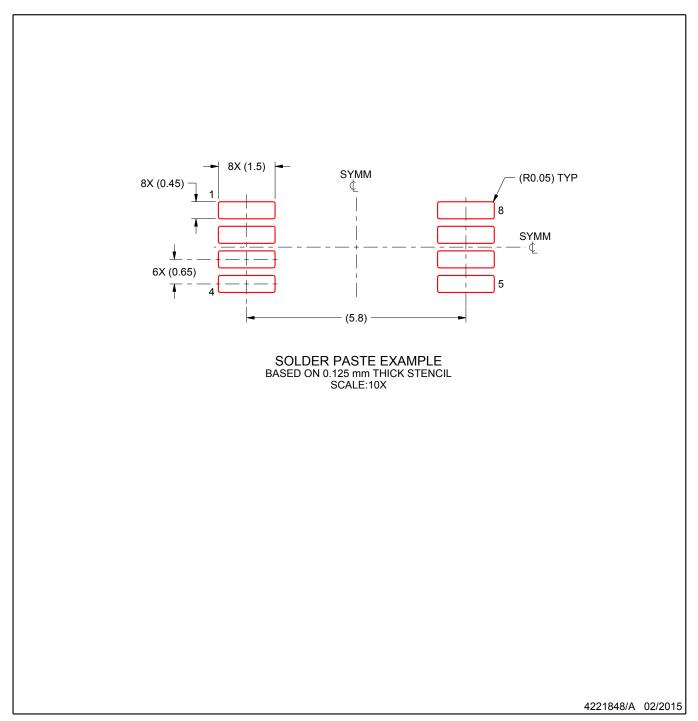

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated