# Precision Rail-to-Rail Input and Output Operational Amplifiers

# OP184/OP284/OP484

#### **FEATURES**

Single-Supply Operation Wide Bandwidth: 4 MHz Low Offset Voltage: 65  $\mu$ V Unity-Gain Stable

High Slew Rate: 4.0 V/ $\mu$ s Low Noise: 3.9 nV/ $\sqrt{\text{Hz}}$

#### **APPLICATIONS**

Battery Powered Instrumentation Power Supply Control and Protection Telecom DAC Output Amplifier ADC Input Buffer

#### **GENERAL DESCRIPTION**

The OP184/OP284/OP484 are single, dual and quad single-supply, 4 MHz bandwidth amplifiers featuring rail-to-rail inputs and outputs. They are guaranteed to operate from 3 to 36 (or  $\pm 1.5$  to  $\pm 18$ ) volts and will function with a single supply as low as 1.5 volts.

These amplifiers are superb for single-supply applications requiring both ac and precision dc performance. The combination of bandwidth, low noise and precision makes the OP184/OP284/OP484 useful in a wide variety of applications, including filters and instrumentation.

Other applications for these amplifiers include portable telecom equipment, power supply control and protection, and as amplifiers or buffers for transducers with wide output ranges. Sensors requiring a rail-to-rail input amplifier include Hall effect, piezo electric, and resistive transducers.

The ability to swing rail-to-rail at both the input and output enables designers to build multistage filters in single-supply systems and to maintain high signal-to-noise ratios.

The OP184/OP284/OP484 are specified over the HOT extended industrial (-40°C to +125°C) temperature range. The single and dual are available in 8-lead plastic DIP plus SO surface mount packages. The quad OP484 is available in 14-lead plastic DIPs and 14-lead narrow-body SO packages.

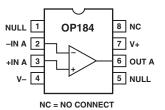

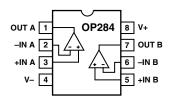

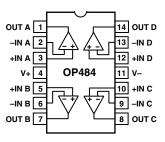

#### PIN CONFIGURATIONS

8-Lead Epoxy DIP (P Suffix) 8-Lead SO (S Suffix)

8-Lead Epoxy DIP (P Suffix) 8-Lead SO (S Suffix)

14-Lead Epoxy DIP (P Suffix) 14-Lead Narrow-Body SO (S Suffix)

# OP184/OP284/OP484—SPECIFICATIONS

# **ELECTRICAL CHARACTERISTICS** (@ $V_S = 5.0 \text{ V}, V_{CM} = 2.5 \text{ V}, T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                                                                                                      | Symbol                                                   | Conditions                                                                                                                                                                                                                                                                                                                | Min                       | Typ                      | Max        | Unit                                        |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|------------|---------------------------------------------|

| INPUT CHARACTERISTICS Offset Voltage "OP184/284E" Grade                                                        | Vos                                                      | (Note 1)<br>-40°C $\leq$ T <sub>A</sub> $\leq$ +125°C                                                                                                                                                                                                                                                                     |                           |                          | 65<br>165  | μV<br>μV                                    |

| Offset Voltage "OP184/284F" Grade                                                                              | V <sub>OS</sub>                                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                                    |                           |                          | 125<br>350 | μV<br>μV                                    |

| Offset Voltage "OP484E" Grade                                                                                  | Vos                                                      | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                                    |                           |                          | 75<br>175  | μV<br>μV                                    |

| Offset Voltage "OP484F" Grade                                                                                  | Vos                                                      | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                                    |                           |                          | 150<br>450 | μV<br>μV                                    |

| Input Bias Current                                                                                             | $I_B$                                                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                                    |                           | 60                       | 450<br>600 | nA<br>nA                                    |

| Input Offset Current                                                                                           | I <sub>OS</sub>                                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                                    |                           | 2                        | 50<br>50   | nA<br>nA                                    |

| Input Voltage Range<br>Common-Mode Rejection Ratio<br>Common-Mode Rejection Ratio<br>Large Signal Voltage Gain | CMRR<br>CMRR<br>A <sub>VO</sub>                          | $\begin{aligned} &V_{CM} = 0 \text{ V to 5 V} \\ &V_{CM} = 1.0 \text{ V to 4.0 V}, -40^{\circ}\text{C} \leq T_{A} \leq +125^{\circ}\text{C} \\ &R_{L} = 2 \text{ k}\Omega, 1 \text{ V} \leq V_{O} \leq 4 \text{ V} \\ &R_{L} = 2 \text{ k}\Omega, -40^{\circ}\text{C} \leq T_{A} \leq +125^{\circ}\text{C} \end{aligned}$ | 0<br>60<br>86<br>50<br>25 | 240                      | 5          | V<br>dB<br>dB<br>V/mV<br>V/mV               |

| Bias Current Drift                                                                                             | $\Delta I_B/\Delta T$                                    | N <sub>L</sub> = 2 N32, 40 C 3 I <sub>A</sub> 3 + 125 C                                                                                                                                                                                                                                                                   | 23                        | 150                      |            | pA/°C                                       |

| OUTPUT CHARACTERISTICS Output Voltage High Output Voltage Low Output Current                                   | $egin{array}{c} V_{OH} \ V_{OL} \ I_{OUT} \ \end{array}$ | $I_{L} = 1.0 \text{ mA}$ $I_{L} = 1.0 \text{ mA}$                                                                                                                                                                                                                                                                         | 4.85<br>±6.5              |                          | 125        | V<br>mV<br>mA                               |

| POWER SUPPLY Power Supply Rejection Ratio Supply Current/Amplifier Supply Voltage Range                        | PSRR<br>I <sub>SY</sub><br>V <sub>S</sub>                | $V_S = 2.0 \text{ V to } 10 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$<br>$V_O = 2.5 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                                                                                               | 76<br>3                   |                          | 1.45<br>36 | dB<br>mA<br>V                               |

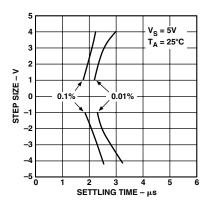

| DYNAMIC PERFORMANCE Slew Rate Settling Time Gain Bandwidth Product Phase Margin                                | SR<br>t <sub>s</sub><br>GBP<br>Øo                        | $R_L = 2 \text{ k}\Omega$<br>To 0.01%, 1.0 V Step                                                                                                                                                                                                                                                                         | 1.65                      | 2.4<br>2.5<br>3.25<br>45 |            | V/µs<br>µs<br>MHz<br>Degrees                |

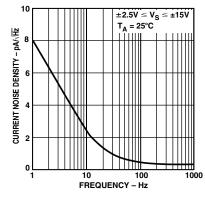

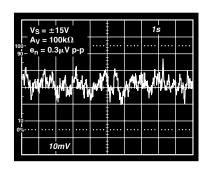

| NOISE PERFORMANCE Voltage Noise Voltage Noise Density Current Noise Density                                    | e <sub>N</sub> p-p<br>e <sub>N</sub><br>i <sub>N</sub>   | 0.1 Hz to 10 Hz<br>f = 1 kHz                                                                                                                                                                                                                                                                                              |                           | 0.3<br>3.9<br>0.4        |            | $\mu V p-p \\ nV/\sqrt{Hz} \\ pA/\sqrt{Hz}$ |

-2-

#### NOTES

<sup>&</sup>lt;sup>1</sup>Input Offset Voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power. Specifications subject to change without notice.

# **ELECTRICAL CHARACTERISTICS** (@ $V_S = 3.0$ V, $V_{CM} = 1.5$ V, $T_A = 25$ °C unless otherwise noted.)

| Parameter                               | Symbol          | Conditions                                                                                                                        | Min  | Typ | Max  | Unit           |  |

|-----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----------------|--|

| INPUT CHARACTERISTICS                   |                 |                                                                                                                                   |      |     |      |                |  |

| Offset Voltage "OP184/284E" Grade       | Vos             | (Note 1)                                                                                                                          |      |     | 65   | μV             |  |

|                                         |                 | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                            |      |     | 165  | μV             |  |

| Offset Voltage "OP184/284F" Grade       | Vos             |                                                                                                                                   |      |     | 125  | μV             |  |

|                                         |                 | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                            |      |     | 350  | μV             |  |

| Offset Voltage "OP484E" Grade           | Vos             |                                                                                                                                   |      |     | 100  | μV             |  |

|                                         |                 | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                            |      |     | 200  | μV             |  |

| Offset Voltage "OP484F" Grade           | V <sub>OS</sub> |                                                                                                                                   |      |     | 150  | μV             |  |

|                                         |                 | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                            |      |     | 450  | μV             |  |

| Input Bias Current                      | $I_B$           |                                                                                                                                   |      | 60  | 450  | nA             |  |

|                                         |                 | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                            |      |     | 600  | nA             |  |

| Input Offset Current                    | I <sub>OS</sub> | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                            |      |     | 50   | nA             |  |

| Input Voltage Range                     |                 |                                                                                                                                   | 0    |     | 3    | V              |  |

| Common-Mode Rejection Ratio             | CMRR            | $V_{CM} = 0 \text{ V to } 3 \text{ V}$                                                                                            | 60   |     |      | dB             |  |

| Common-Mode Rejection Ratio             | CMRR            | $V_{CM} = 0 \text{ V to } 3 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                    | 56   |     |      | dB             |  |

| OUTPUT CHARACTERISTICS                  |                 |                                                                                                                                   |      |     |      |                |  |

| Output Voltage High                     | V <sub>OH</sub> | $I_L = 1.0 \text{ mA}$                                                                                                            | 2.85 |     |      | V              |  |

| Output Voltage Low                      | V <sub>OL</sub> | $I_L = 1.0 \text{ mA}$                                                                                                            |      |     | 125  | mV             |  |

| POWER SUPPLY                            |                 |                                                                                                                                   |      |     |      |                |  |

| Power Supply Rejection Ratio            | PSRR            | $V_S = \pm 1.25 \text{ V to } \pm 1.75 \text{ V}$                                                                                 | 76   |     |      | dB             |  |

| Supply Current/Amplifier                |                 | $V_S = 1.25 \text{ V} \cdot 10^{-11.75} \text{ V}$<br>$V_O = 1.5 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ | 10   |     | 1.35 | mA             |  |

|                                         | I <sub>SY</sub> | V <sub>0</sub> - 1.5 V, -40 C S I <sub>A</sub> S +125 C                                                                           |      |     | 1.55 | ША             |  |

| DYNAMIC PERFORMANCE                     |                 |                                                                                                                                   |      |     |      |                |  |

| Gain Bandwidth Product                  | GBP             |                                                                                                                                   |      | 3   |      | MHz            |  |

| NOISE PERFORMANCE                       |                 |                                                                                                                                   |      |     |      |                |  |

|                                         | e <sub>N</sub>  | f = 1  kHz                                                                                                                        |      | 3.9 |      | $nV/\sqrt{Hz}$ |  |

| NOISE PERFORMANCE Voltage Noise Density | e <sub>N</sub>  | f = 1 kHz                                                                                                                         |      | 3.9 |      | $nV/\sqrt{F}$  |  |

#### NOTES

REV. B -3-

<sup>&</sup>lt;sup>1</sup>Input Offset Voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power.

Specifications subject to change without notice.

# **ELECTRICAL CHARACTERISTICS** (@ $V_s = \pm 15.0 \text{ V}$ , $V_{\text{CM}} = 0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                                | Symbol                           | Conditions                                                                                                                                       | Min  | Typ  | Max        | Unit           |

|------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------|----------------|

| INPUT CHARACTERISTICS                    |                                  |                                                                                                                                                  |      |      |            |                |

| Offset Voltage "OP184/284E" Grade        | Vos                              | (Note 1)                                                                                                                                         |      |      | 100        | μV             |

|                                          |                                  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                           |      |      | 200        | μV             |

| Offset Voltage "OP284F" Grade            | Vos                              |                                                                                                                                                  |      |      | 175        | μV             |

|                                          |                                  | $-40$ °C $\leq T_A \leq +125$ °C                                                                                                                 |      |      | 375        | μV             |

| Offset Voltage "OP484E" Grade            | Vos                              | 1000 177 11700                                                                                                                                   |      |      | 150        | μV             |

| Off III (ODAGAEN C. )                    |                                  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                           |      |      | 300        | μV             |

| Offset Voltage "OP484F" Grade            | Vos                              | 4000 c F c 110500                                                                                                                                |      |      | 250        | μV             |

| I P' C                                   | ,                                | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                           |      | 0.0  | 500        | μV             |

| Input Bias Current                       | $I_{B}$                          | 40°C < T < 1125°C                                                                                                                                |      | 80   | 450<br>575 | nA             |

| Innet Office Comment                     | т .                              | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |      |      | 575<br>50  | nA<br>nA       |

| Input Offset Current Input Voltage Range | I <sub>OS</sub>                  | $-40^{\circ}$ C $\leq 1_{\text{A}} \leq +125^{\circ}$ C                                                                                          | -15  |      | +15        | V              |

| Common-Mode Rejection Ratio              | CMRR                             | $V_{CM} = -14.0 \text{ V to } +14.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                           | 86   | 90   | 113        | dB             |

| Common-Mode Rejection Ratio              | CMRR                             | $V_{CM} = -15.0 \text{ V to } +15.0 \text{ V}$                                                                                                   | 80   | 90   |            | dB             |

| Large-Signal Voltage Gain                | A <sub>VO</sub>                  | $R_{L} = 2 k\Omega, -10 V \le V_{O} \le 10 V$                                                                                                    | 150  | 1000 |            | V/mV           |

| Large Orginal Voltage Gain               | 1100                             | $R_{L} = 2 \text{ k}\Omega, -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                                              | 75   | 1000 |            | V/mV           |

| Offset Voltage Drift "E" Grade           | $\Delta V_{OS}/\Delta T$         | 14L 2 14L, 10 0 = 1A = 11L3 0                                                                                                                    | . ,  | 0.2  | 2.00       | μV/°C          |

| Bias Current Drift                       | $\Delta I_B/\Delta T$            |                                                                                                                                                  |      | 150  |            | pA/°C          |

| OUTPUT CHARACTERISTICS                   | _                                |                                                                                                                                                  |      |      |            |                |

| Output Voltage High                      | V <sub>OH</sub>                  | $I_L = 1.0 \text{ mA}$                                                                                                                           | 14.8 |      |            | V              |

| Output Voltage Low                       | V <sub>OL</sub>                  | $I_L = 1.0 \text{ mA}$                                                                                                                           | 1110 |      | -14.875    | v              |

| Output Current                           | I <sub>OUT</sub>                 |                                                                                                                                                  | ±10  |      |            | mA             |

| POWER SUPPLY                             | 001                              |                                                                                                                                                  |      |      |            |                |

| Power Supply Rejection Ratio             | PSRR                             | $V_S = \pm 2.0 \text{ V to } \pm 18 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                             | 90   |      |            | dB             |

| Supply Current/Amplifier                 | I <sub>SY</sub>                  | $V_0 = 0 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                        |      |      | 2.0        | mA             |

| Supply Current/Amplifier                 | I <sub>SY</sub>                  | $V_S = \pm 18 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                   |      |      | 2.25       | mA             |

| DYNAMIC PERFORMANCE                      | -31                              | -3 -11 · ) 11 1 - A - 11 1                                                                                                                       |      |      |            |                |

| Slew Rate                                | SR                               | $R_{L} = 2 k\Omega$                                                                                                                              | 2.4  | 4.0  |            | V/µs           |

| Full-Power Bandwidth                     | BW <sub>p</sub>                  | $1\%$ Distortion, $R_L = 2 k\Omega$ , $V_O = 29 V p-p$                                                                                           | 2.4  | 35   |            | kHz            |

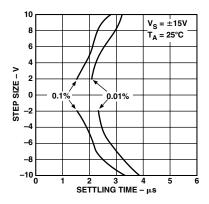

| Settling Time                            | t <sub>S</sub>                   | To 0.01%, 10 V Step                                                                                                                              |      | 4    |            | μs             |

| Gain Bandwidth Product                   | GBP                              | 10 0.0170, 10 1 5tep                                                                                                                             |      | 4.25 |            | MHz            |

| Phase Margin                             | Øo.                              |                                                                                                                                                  |      | 50   |            | Degrees        |

| NOISE PERFORMANCE                        |                                  |                                                                                                                                                  |      |      |            |                |

| Voltage Noise                            | a. n n                           | 0.1 Hz to 10 Hz                                                                                                                                  |      | 0.3  |            | μV p-p         |

| Voltage Noise Density                    | e <sub>N</sub> p-p               | f = 1 kHz                                                                                                                                        |      | 3.9  |            | $nV/\sqrt{Hz}$ |

| Current Noise Density                    | e <sub>N</sub><br>i <sub>N</sub> | 1 - 1 KIIL                                                                                                                                       |      | 0.4  |            | $pA/\sqrt{Hz}$ |

| NOTES                                    | *N                               |                                                                                                                                                  |      | 0.1  |            | PINVIIZ        |

-4-

NOTES

<sup>&</sup>lt;sup>1</sup>Input Offset Voltage measurements are performed by automated test equipment approximately 0.5 seconds after application of power. Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                               |

|--------------------------------------------------------------|

| Input Voltage                                                |

| Differential Input Voltage <sup>2</sup> ±0.6 V               |

| Output Short-Circuit Duration to GND <sup>3</sup> Indefinite |

| Storage Temperature Range                                    |

| P, S Packages65°C to +150°C                                  |

| Operating Temperature Range                                  |

| OP184/OP284/OP484E, F40°C to +125°C                          |

| Junction Temperature Range                                   |

| P, S Packages                                                |

| Lead Temperature Range (Soldering 60 sec) 300 $^{\circ}$ C   |

| Package Type            | $\theta_{JA}^{3}$ | $\theta_{ m JC}$ | Unit |

|-------------------------|-------------------|------------------|------|

| 8-Lead Plastic DIP (P)  | 103               | 43               | °C/W |

| 8-Lead SOIC (S)         | 158               | 43               | °C/W |

| 14-Lead Plastic DIP (P) | 83                | 39               | °C/W |

| 14-Lead SOIC (S)        | 92                | 27               | °C/W |

#### NOTES

#### **ORDERING GUIDE**

| Model    | Temperature     | Package             | Package |

|----------|-----------------|---------------------|---------|

|          | Range           | Description         | Option  |

| OP184EP* | -40°C to +125°C | 8-Lead Plastic DIP  | N-8     |

| OP184ES  | -40°C to +125°C | 8-Lead SOIC         | R-8     |

| OP184FP* | -40°C to +125°C | 8-Lead Plastic DIP  | N-8     |

| OP184FS  | -40°C to +125°C | 8-Lead SOIC         | R-8     |

| OP284EP  | -40°C to +125°C | 8-Lead Plastic DIP  | N-8     |

| OP284ES  | -40°C to +125°C | 8-Lead SOIC         | R-8     |

| OP284FP* | -40°C to +125°C | 8-Lead Plastic DIP  | N-8     |

| OP284FS  | -40°C to +125°C | 8-Lead SOIC         | R-8     |

| OP484ES  | -40°C to +125°C | 14-Lead SOIC        | R-14    |

| OP484FP  | -40°C to +125°C | 14-Lead Plastic DIP | N-14    |

| OP484FS  | -40°C to +125°C | 14-Lead SOIC        | R-14    |

#### NOTES

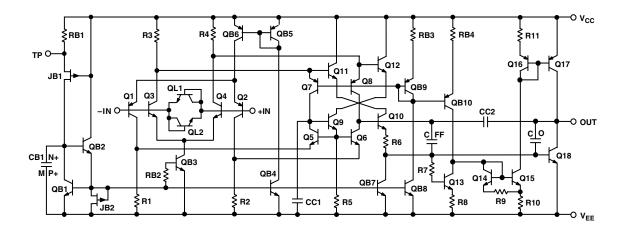

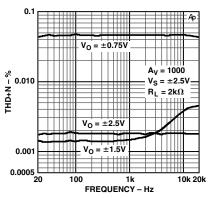

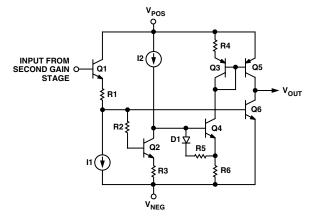

Figure 3. Simplified Schematic

REV. B –5–

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts unless otherwise noted.

$<sup>^2</sup> For input voltages greater than 0.6 volts, the input current should be limited to less than 5 mA to prevent degradation or destruction of the input devices.$

$<sup>^3\</sup>theta_{JA}$  is specified for the worst case conditions; i.e.,  $\theta_{JA}$  is specified for device in socket for cerdip and P-DIP packages;  $\theta_{JA}$  is specified for device soldered in circuit board for SOIC package.

<sup>\*</sup>Not for new design; obsolete April 2002.

# **OP184/OP284/OP484—Typical Performance Characteristics**

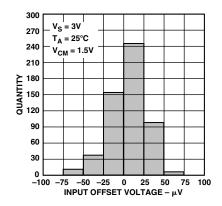

TPC 1. Input Offset Voltage Distribution

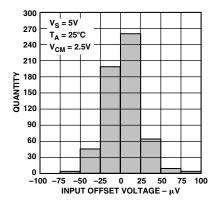

TPC 2. Input Offset Voltage Distribution

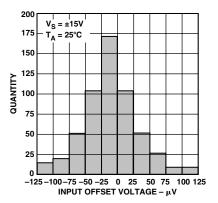

TPC 3. Input Offset Voltage Distribution

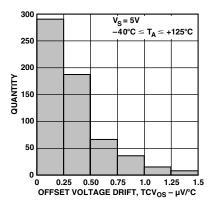

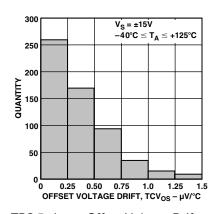

TPC 4. Input Offset Voltage Drift Distribution

TPC 5. Input Offset Voltage Drift Distribution

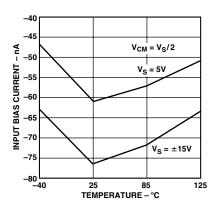

TPC 6. Bias Current vs. Temperature

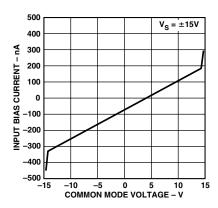

TPC 7. Input Bias Current vs. Common-Mode Voltage

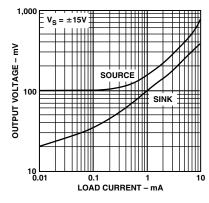

TPC 8. Output Voltage to Supply Rail vs. Load Current

-6-

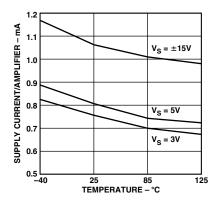

TPC 9. Supply Current vs. Temperature

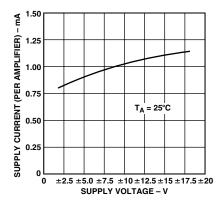

TPC 10. Supply Current vs. Supply Voltage

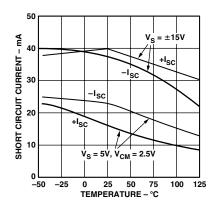

TPC 11. Short Circuit Current vs. Temperature

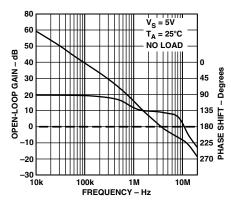

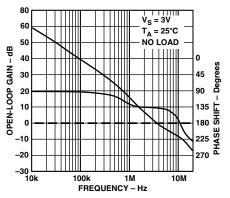

TPC 12. Open-Loop Gain and Phase vs. Frequency (No Load)

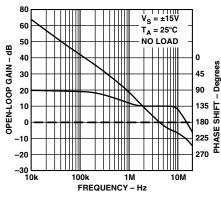

TPC 13. Open-Loop Gain and Phase vs. Frequency (No Load)

TPC 14. Open-Loop Gain and Phase vs. Frequency (No Load)

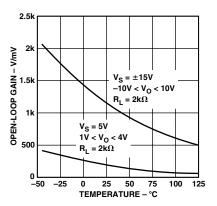

TPC 15. Open-Loop Gain vs. Temperature

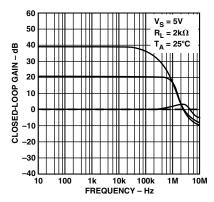

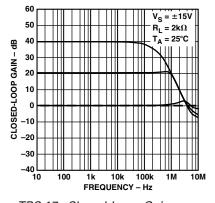

TPC 16. Closed-Loop Gain vs. Frequency (2  $k\Omega$  Load)

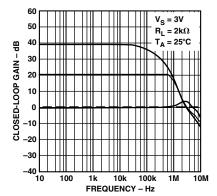

TPC 17. Closed-Loop Gain vs. Frequency (2  $k\Omega$  Load)

TPC 18. Closed-Loop Gain vs. Frequency (2  $k\Omega$  Load)

REV. B –7–

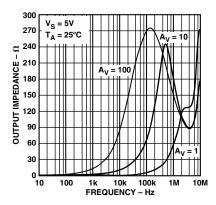

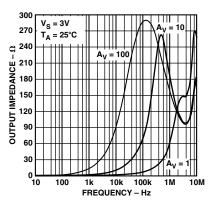

TPC 19. Output Impedance vs. Frequency

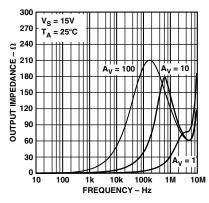

TPC 20. Output Impedance vs. Frequency

TPC 21. Output Impedance vs. Frequency

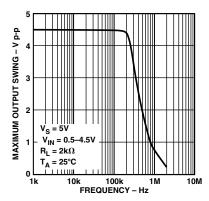

TPC 22. Maximum Output Swing vs. Frequency

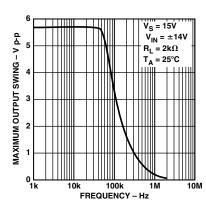

TPC 23. Maximum Output Swing vs. Frequency

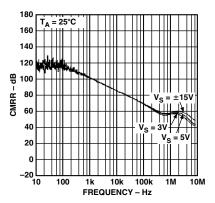

TPC 24. CMRR vs. Frequency

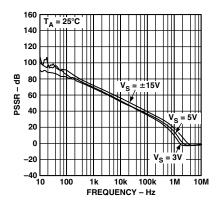

TPC 25. PSRR vs. Frequency

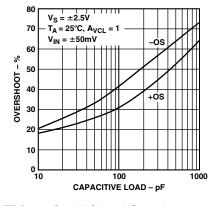

TPC 26. Small Signal Overshoot vs. Capacitive Load

-8-

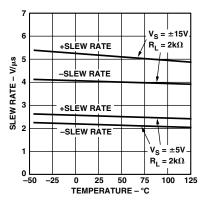

TPC 27. Slew Rate vs. Temperature

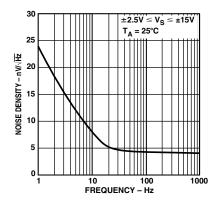

TPC 28. Voltage Noise Density vs. Frequency

TPC 29. Current Noise Density vs. Frequency

TPC 30. Settling Time vs. Step Size

TPC 31. Settling Time vs. Step Size

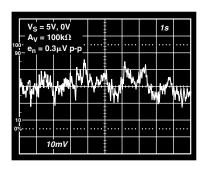

TPC 32. 0.1 Hz to 10 Hz Noise

TPC 33. 0.1 Hz to 10 Hz Noise

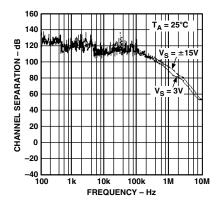

TPC 34. Channel Separation vs. Frequency

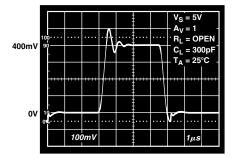

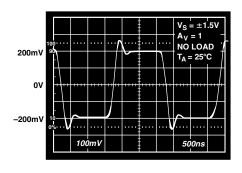

TPC 35. Small Signal Transient Response

TPC 36. Small Signal Transient Response

REV. B –9–

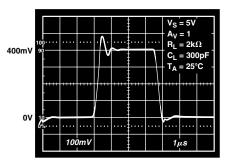

TPC 37. Small Signal Transient Response

TPC 38. Small Signal Transient Response

-10-

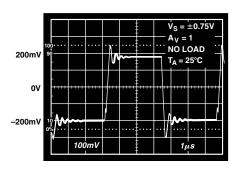

TPC 39. Total Harmonic Distortion vs. Frequency

#### **APPLICATIONS**

#### **Functional Description**

The OP284 and OP484 are precision single-supply, rail-to-rail operational amplifiers. Intended for the portable instrumentation marketplace, the OP184/OP284/OP484 combine the attributes of precision, wide bandwidth, and low noise to make it a superb choice in those single-supply applications that require both ac and precision dc performance. Other low supply voltage applications for which the OP284 is well suited are active filters, audio microphone preamplifiers, power supply control, and telecom. To combine all of these attributes with rail-to-rail input/output operation, novel circuit design techniques are used.

Figure 4. OP284 Equivalent Input Circuit

For example, Figure 4 illustrates a simplified equivalent circuit for the OP184/OP284/OP484's input stage. It is comprised of an NPN differential pair, Q1–Q2, and a PNP differential pair, Q3–Q4, operating concurrently. Diode network D1–D2 serves to clamp the applied differential input voltage to the OP284, thereby protecting the input transistors against avalanche damage. Input stage voltage gains are kept low for input rail-to-rail operation. The two pair of differential output voltages are connected to the OP284's second stage, which is a compound folded cascode gain stage. It is also in the second gain stage where the two pairs of differential output voltages are combined into a single-ended output signal voltage used to drive

the output stage. A key issue in the input stage is the behavior of the input bias currents over the input common-mode voltage range. Input bias currents in the OP284 are the arithmetic sum of the base currents in Q1–Q3 and in Q2–Q4. As a result of this design approach, the input bias currents in the OP284 not only exhibit different amplitudes, but also exhibit different polarities. This effect is best illustrated in TPC 6. It is, therefore, of paramount importance that the effective source impedances connected to the OP284's inputs be balanced for optimum dc and ac performance.

To achieve rail-to-rail output, the OP284 output stage design employs a unique topology for both sourcing and sinking current. This circuit topology is illustrated in Figure 5. As previously mentioned, the output stage is voltage-driven from the second gain stage. The signal path through the output stage is inverting; that is, for positive input signals, Q1 provides the base current drive to Q6 so that it conducts (sinks) current. For negative input signals, the signal path via Q1–Q2–D1–Q4–Q3 provides the base current drive for Q5 to conduct (source) current. Both amplifiers provide output current until they are forced into saturation, which occurs at approximately 20 mV from negative rail and 100 mV from the positive supply rail.

Figure 5. OP284 Equivalent Output Circuit

Thus, the saturation voltage of the output transistors sets the limit on the OP284's maximum output voltage swing. Output short circuit current limiting is determined by the maximum signal current into the base of Q1 from the second gain stage. Under output short circuit conditions, this input current level is approximately  $100~\mu A$ . With transistor current gains around 200, the short circuit current limits are typically 20~mA. The output stage also exhibits voltage gain. This is accomplished by use of common-emitter amplifiers, and as a result, the voltage gain of the output stage (thus, the open-loop gain of the device) exhibits a dependence to the total load resistance at the output of the OP284.

#### **Input Overvoltage Protection**

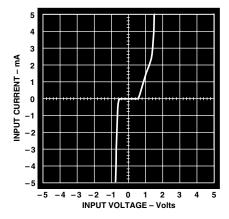

As with any semiconductor device, if conditions exist where the applied input voltages to the device exceed either supply voltage, the device's input overvoltage I-V characteristic must be considered. When an overvoltage occurs, the amplifier could be damaged, depending on the magnitude of the applied voltage and the magnitude of the fault current. Figure 6 illustrates the overvoltage I-V characteristic of the OP284. This graph was generated with the supply pins connected to GND and a curve tracer's collector output drive connected to the input.

Figure 6. Input Overvoltage I-V Characteristics of the OP284

As shown in the figure, internal p-n junctions to the OP284 energize and permit current flow from the inputs to the supplies when the input is 1.8 V more positive and 0.6 V more negative than the respective supply rails. As illustrated in the simplified equivalent circuit shown in Figure 4, the OP284 does not have any internal current limiting resistors; thus, fault currents can quickly rise to damaging levels.

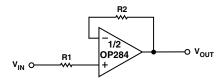

This input current is not inherently damaging to the device, provided that it is limited to 5 mA or less. For the OP284, once the input exceeds the negative supply by 0.6 V, the input current quickly exceeds 5 mA. If this condition continues to exist, an external series resistor should be added at the expense of additional thermal noise. Figure 7 illustrates a typical noninverting configuration for an overvoltage protected amplifier where the series resistance,  $R_{\rm S}$ , is chosen such that:

$$R_{S} = \frac{V_{IN\ (MAX\ )} - V_{SUPPLY}}{5\ mA}$$

Figure 7. A Resistance in Series with an Input Limits Overvoltage Currents to Safe Values

For example, a 1  $k\Omega$  resistor will protect the OP284 against input signals up to 5 V above and below the supplies. For other configurations where both inputs are used, then each input should be protected against abuse with a series resistor. Again, in order to ensure optimum dc and ac performance, it is recommended to balance source impedance levels. For more information on the general overvoltage characteristics of amplifiers, please refer to the 1993 System Applications Guide, Section 1, pages 56-69. This reference textbook is available from the Analog Devices Literature Center.

#### **Output Phase Reversal**

Some operational amplifiers designed for single-supply operation exhibit an output voltage phase reversal when their inputs are driven beyond their useful common-mode range. Typically for single-supply bipolar op amps, the negative supply determines the lower limit of their common-mode range. With these devices, external clamping diodes, with the anode connected to ground and the cathode to the inputs, prevent input signal excursions from exceeding the device's negative supply (i.e., GND), preventing a condition that could cause the output voltage to change phase. JFET-input amplifiers may also exhibit phase reversal, and, if so, a series input resistor is usually required to prevent it.

The OP284 is free from reasonable input voltage range restrictions, provided that input voltages no greater than the supply voltages are applied. Although the device's output will not change phase, large currents can flow through the input protection diodes as was shown in Figure 6. Therefore, the technique recommended in the Input Overvoltage Protection section should be applied to those applications where the likelihood of input voltages exceeding the supply voltages is high.

Designing Low Noise Circuits in Single Supply Applications In single supply applications, devices like the OP284 extend the dynamic range of the application through the use of rail-to-rail operation. In fact, the OP284 family is the first of its kind to combine single-supply, rail-to-rail operation and low noise in one device. It is the first device in the industry to exhibit an input noise voltage spectral density of less than  $4 \text{ nV}/\sqrt{\text{Hz}}$  at 1 kHz. It was also designed specifically for low-noise, single-supply applications, and as such, some discussion on circuit noise concepts in single-supply applications is appropriate.

REV. B –11–

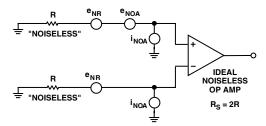

Referring to the op amp noise model circuit configuration illustrated in Figure 8, the expression for an amplifier's total equivalent input noise voltage for a source resistance level  $R_S$  is given by:

$$e_{nT} = \sqrt{2\left[\left(e_{nR}\right)^2 + \left(i_{nOA} \times R\right)^2\right] + \left(e_{nOA}\right)^2}$$

, units in  $\frac{V}{\sqrt{Hz}}$

where  $R_S = 2R = Effective$ , or equivalent, circuit source resistance,

$(e_{nOA})^2$  = Op amp equivalent input noise voltage spectral power (1 Hz BW),

$(i_{nOA})^2$  = Op amp equivalent input noise current spectral power (1 Hz BW),

$(e_{nR})^2$  = Source resistance thermal noise voltage power = (4kTR),

k = Boltzmann's constant =  $1.38 \times 10^{-23}$  J/K, and T = Ambient temperature of the circuit, in Kelvin, =  $273.15 + T_A$  (°C)

Figure 8. Op Amp Noise Circuit Model Used to Determine Total Circuit Equivalent Input Noise Voltage and Noise Figure

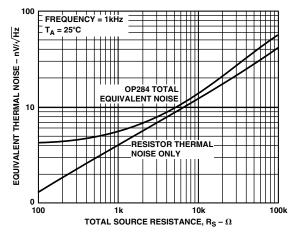

As a design aid, Figure 9 illustrates the total equivalent input noise of the OP284 and the total thermal noise of a resistor for comparison. Note that for source resistance less than 1 k $\Omega$ , the equivalent input noise voltage of the OP284 is dominant.

Figure 9. OP284 Total Noise vs. Source Resistance

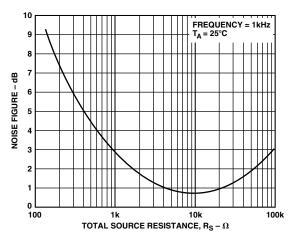

Since circuit SNR is the critical parameter in the final analysis, the noise behavior of a circuit is often expressed in terms of its noise figure, NF. Noise figure is defined as the ratio of a circuit's output signal-to-noise to its input signal-to-noise. An expression of a circuit's NF in dB, and in terms of the operational amplifier's voltage and current noise parameters defined previously, is given by:

$$NF(dB) = 10 \log \left[ 1 + \left( \frac{(e_{nOA})^2 + (i_{nOA} R_S)^2}{(e_{nRS})^2} \right) \right]$$

where NF(dB) = Noise figure of the circuit, expressed in dB,  $R_S$  = Effective, or equivalent, source resistance presented to amplifier,

$(e_{nOA})^2$  = OP284 noise voltage spectral power (1 Hz BW),  $(i_{nOA})^2$  = OP284 noise current spectral power (1 Hz BW),  $(e_{nRS})^2$  = Source resistance thermal noise voltage power = (4kTR<sub>S</sub>),

Circuit noise figure is straightforward to calculate because the signal level in the application is not required to determine it. However, many designers using NF calculations as the basis for achieving optimum SNR believe that low noise figure is equal to low total noise. In fact, the opposite is true, as illustrated in Figure 10. Here, the noise figure of the OP284 is expressed as a function of the source resistance level. Note that the lowest noise figure for the OP284 occurs at a source resistance level of  $10~\text{k}\Omega$ . However, Figure 9 shows that this source resistance level and the OP284 generate approximately  $14~\text{nV}/\sqrt{\text{Hz}}$  of total equivalent circuit noise. Signal levels in the application would invariably be increased to maximize circuit SNR—not an option in low voltage, single-supply applications.

Figure 10. OP284 Noise Figure vs. Source Resistance

In single supply applications, therefore, it is recommended for optimum circuit SNR to choose an operational amplifier with the lowest equivalent input noise voltage and to choose source resistance levels consistent in maintaining low total circuit noise.

REV. B

-12-

#### **Overdrive Recovery**

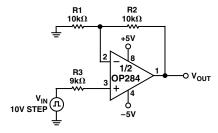

The overdrive recovery time of an operational amplifier is the time required for the output voltage to recover to its linear region from a saturated condition. The recovery time is important in applications where the amplifier must recover quickly after a large transient event. The circuit shown in Figure 11 was used to evaluate the OP284's overload recovery time. The OP284 takes approximately 2  $\mu s$  to recover from positive saturation and approximately 1  $\mu s$  to recover from negative saturation.

Figure 11. Output Overload Recovery Test Circuit

#### A Single-Supply, 3 V Instrumentation Amplifier

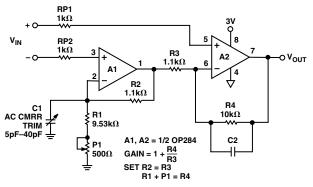

The OP284's low noise, wide bandwidth, and rail-to-rail input/ output operation makes it ideal for low supply voltage applications such as in a two op amp instrumentation amplifier as shown in Figure 12. The circuit uses the classic two op amp instrumentation amplifier topology with four resistors to set the gain. The transfer equation of the circuit is identical to that of a noninverting amplifier. Resistors R2 and R3 should be closely matched to each other as well as to resistors (R1 + P1) and R4 to ensure good common-mode rejection performance. Resistor networks should be used in this circuit for R2 and R3 because they exhibit the necessary relative tolerance matching for good performance. Matched networks also exhibit tight relative resistor temperature coefficients for good circuit temperature stability. Trimming potentiometer P1 is used for optimum dc CMR adjustment, and C1 is used to optimize ac CMR. With the circuit values as shown, circuit CMR is better than 80 dB over the frequency range of 20 Hz to 20 kHz. Circuit RTI (Referred-to-Input) noise in the 0.1 Hz to 10 Hz band is an impressively low 0.45 µV p-p. Resistors RP1 and RP2 serve to protect the OP284's inputs against input overvoltage abuse. Capacitor C2 can be included to the limit circuit bandwidth and, therefore, wide bandwidth noise in sensitive applications. The value of this capacitor should be adjusted depending on the required closedloop bandwidth of the circuit. The R4-C2 time constant creates a pole at a frequency equal to:

$$f(3 dB) = \frac{1}{2 \pi R4 C2}$$

Figure 12. A Single Supply, 3 V Low Noise Instrumentation Amplifier

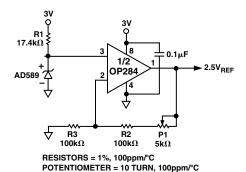

#### A 2.5 V Reference from a 3 V Supply

In many single-supply applications, the need for a 2.5 V reference often arises. Many commercially available monolithic 2.5 V references require at least a minimum operating supply of 4 V. The problem is exacerbated when the minimum operating supply voltage is 3 V. The circuit illustrated in Figure 13 is an example of a 2.5 V reference that operates from a single 3 V supply. The circuit takes advantage of the OP284's rail-to-rail input/output voltage ranges to amplify an AD589's 1.235 V output to 2.5 V. The OP284's low TCV $_{\rm OS}$  of 1.5  $\mu V/^{\circ} C$  helps maintain an output voltage temperature coefficient that is dominated by the temperature coefficients of R2 and R3. In this circuit with 100 ppm/ $^{\circ} C$  TCR resistors, the output voltage exhibits a temperature coefficient of 200 ppm/ $^{\circ} C$ . Lower tempco resistors are recommended for more accurate performance over temperature.

One measure of the performance of a voltage reference is its capacity to recover from sudden changes in load current. While sourcing a steady-state load current of 1 mA, this circuit recovers to 0.01% of the programmed output voltage in 1.5  $\mu$ s for a total change in load current of  $\pm 1$  mA.

Figure 13. A 2.5 V Reference that Operates on a Single 3 V Supply

REV. B –13–

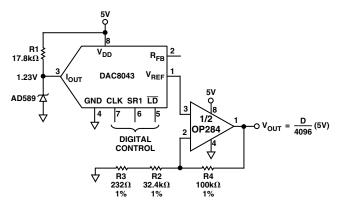

#### A 5 V Only, 12-Bit DAC Swings Rail-to-Rail

The OP284 is ideal for use with a CMOS DAC to generate a digitally controlled voltage with a wide output range. Figure 14 shows a DAC8043 used in conjunction with the AD589 to generate a voltage output from 0 V to 1.23 V. The DAC is actually operating in "voltage switching" mode where the reference is connected to the current output,  $I_{OUT}$ , and the output voltage is taken from the  $V_{REF}$  pin. This topology is inherently noninverting as opposed to the classic current output mode, which is inverting and not usable in single-supply applications.

Figure 14. A 5 V Only, 12-Bit DAC Swings Rail-to-Rail

In this application the OP284 serves two functions. First, it buffers the high output impedance of the DAC's  $V_{REF}$  pin, which is on the order of  $10~k\Omega$ . The op amp provides a low impedance output to drive any following circuitry. Second, the op amp amplifies the output signal to provide a rail-to-rail output swing. In this particular case, the gain is set to 4.1 so that the circuit generates a 5 V output when the DAC output is at full scale. If other output voltage ranges are needed, such as 0 V  $\leq$  V\_OUT  $\leq$  4.095 V, the gain can be easily changed by adjusting the values of R2 and R3.

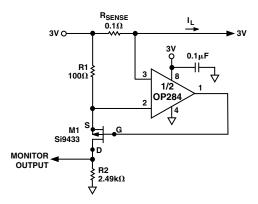

#### A High-Side Current Monitor

In the design of power supply control circuits, a great deal of design effort is focused on ensuring a pass transistor's long-term reliability over a wide range of load current conditions. As a result, monitoring and limiting device power dissipation is of prime importance in these designs. The circuit illustrated in Figure 15 is an example of a 3 V, single-supply high-side current monitor that can be incorporated into the design of a voltage regulator with fold-back current limiting or a high current power supply with crowbar protection. This design uses an OP284's rail-to-rail input voltage range to sense the voltage drop across a 0.1  $\Omega$  current shunt. A p-channel MOSFET used as the feedback element in the circuit converts the op amp's differential input voltage into a current. This current is applied to R2 to generate a voltage that is a linear representation of the load current. The transfer equation for the current monitor is given by:

$$Monitor\ Output = R2 \times \left(\frac{R_{SENSE}}{R1}\right) \times I_{L}$$

For the element values shown, the Monitor Output's transfer characteristic is 2.5 V/A.

Figure 15. A High-Side Load Current Monitor

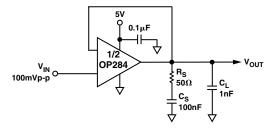

#### Capacitive Load Drive Capability

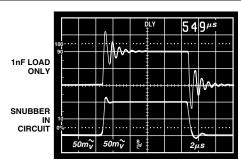

The OP284 exhibits excellent capacitive load driving capabilities. It can drive up to 1 nF as shown in TPC 24. Even though the device is stable, a capacitive load does not come without penalty in bandwidth. The bandwidth is reduced to under 1 MHz for loads greater than 2 nF. A "snubber" network on the output does not increase the bandwidth, but it does significantly reduce the amount of overshoot for a given capacitive load. A snubber consists of a series R-C network (R<sub>S</sub>, C<sub>S</sub>), as shown in Figure 16, connected from the output of the device to ground. This network operates in parallel with the load capacitor, C<sub>L</sub>, to provide the necessary phase lag compensation. The value of the resistor and capacitor is best determined empirically.

Figure 16. Snubber Network Compensates for Capacitive Load

The first step is to determine the value of the resistor  $R_S$ . A good starting value is  $100~\Omega$  (typically, the optimum value will be less than  $100~\Omega$ ). This value is reduced until the small-signal transient response is optimized. Next,  $C_S$  is determined—10  $\mu F$  is a good starting point. This value is reduced to the smallest value for acceptable performance (typically, 1  $\mu F$ ). For the case of a 10 nF load capacitor on the OP284, the optimal snubber network is a 20  $\Omega$  in series with 1  $\mu F$ . The benefit is immediately apparent as shown in the scope photo in Figure 17. The top trace was taken with a 1 nF load, and the bottom trace was taken with the 50  $\Omega$ , 100 nF snubber network in place. The amount of overshoot and ringing is dramatically reduced. Table I below illustrates a few sample snubber networks for large load capacitors.

REV. B

-14-

Figure 17. Overshoot and Ringing Is Reduced by Adding a "Snubber" Network in Parallel with the 1 nF Load

Table I. Snubber Networks for Large Capacitive Loads

| Load Capacitance (C <sub>L</sub> ) | Snubber Network (R <sub>S</sub> , C <sub>S</sub> ) |

|------------------------------------|----------------------------------------------------|

| 1 nF                               | 50 Ω, 100 nF                                       |

| 10 nF                              | 20 Ω, 1 μF                                         |

| 100 nF                             | 5 Ω, 10 μF                                         |

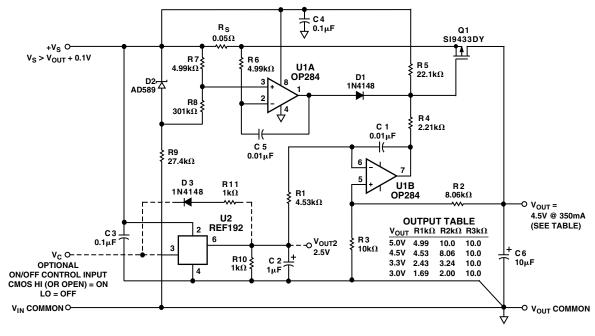

#### A Low Dropout Regulator with Current Limiting

Many circuits require stable regulated voltages relatively close, in potential to an unregulated input source. This "low dropout" type of regulator is readily implemented with a rail-to-rail output op amp such as the OP284 because the wide output swing allows easy drive to a low saturation voltage pass device. Furthermore, it is particularly useful when the op amp also enjoys a rail-to-rail input feature, as this factor allows it to perform high-side current sensing for positive rail current limiting. Typical examples are voltages developed from 3 V to 9 V range system sources or anywhere where low dropout performance is required for power efficiency. The 4.5 V case here works from 5 V nominal sources with worst-case levels down to 4.6 V or less.

Figure 18 shows such a regulator set up using an OP284 plus a low  $R_{\rm DS(ON)},$  P-channel MOSFET pass device. Part of the low dropout performance of this circuit is provided by Q1, which has a rating of 0.11  $\Omega$  with a gate drive voltage of only 2.7 V. This relatively low gate drive threshold allows operation of the regulator on supplies as low as 3 V without compromising overall performance.

The circuit's main voltage control loop operation is provided by U1B, half of the OP284. This voltage control amplifier amplifies the 2.5 V reference voltage produced by three terminal U2, a REF192. The regulated output voltage  $V_{OUT}$  is then:

$$V_{OUT} = V_{OUT2} \left( 1 + \frac{R2}{R3} \right)$$

For this example, since  $V_{OUT}$  of 4.5 V with  $V_{OUT2}$  = 2.5 V requires a U1B gain of 1.8 times, R3 and R2 are chosen for a ratio of 1.2:1 or 10.0 k $\Omega$ :8.06 k $\Omega$  (using closest 1% values). Note that for the lowest  $V_{OUT}$  dc error, R2|R3 should be maintained equal to R1 (as here), and the R2-R3 resistors should be stable, close tolerance metal film types. The table in Figure 18 summarizes R1-R3 values for some popular voltages. However, note that, in general, the output can be anywhere between  $V_{OUT2}$  and the 12 V maximum rating of Q1.

While the low voltage saturation characteristic of Q1 is a key part of the low dropout, another component is a low current sense comparison threshold with good dc accuracy. Here, this is provided by current sense amplifier U1A, which is provided by a 20 mV reference from the 1.235 V AD589 reference diode D2 and the R7-R8 divider. When the product of the output current and the  $R_{\rm S}$  value match this voltage threshold, the current control loop is activated, and U1A drives Q1's gate through D1. This causes the overall circuit operation to enter current mode control with a current limit  $I_{\rm LIMIT}$  defined as:

$$I_{LIMIT} = \left(\frac{V_{R(D2)}}{R_{S}}\right) \left(\frac{R7}{R7 + R8}\right)$$

Figure 18. A Low Dropout Regulator with Current Limiting

REV. B –15–

Obviously, it is desirable to keep this comparison voltage small, since it becomes a significant portion of the overall dropout voltage. Here, the 20 mV reference is higher than the typical offset of the OP284 but still reasonably low as a percentage of  $V_{\rm OUT}$  (< 0.5%). In adapting the limiter for other  $I_{\rm LIMIT}$  levels, sense resistor  $R_{\rm S}$  should be adjusted along with R7-R8, to maintain this threshold voltage between 20 mV and 50 mV.

Performance of the circuit is excellent. For the 4.5 V output version, the measured dc output change for a 225 mA load change was on the order of a few microvolts while the dropout voltage at this same current level was about 30 mV. The current limit as shown is 400 mA, which allows the circuit to be used at levels up to 300 mA or more. While the Q1 device can actually support currents of several amperes, a practical current rating takes into account the SO-8 device's 2.5 W, 25°C dissipation. Because a short circuit current of 400 mA at an input level of 5 V will cause a 2 W dissipation in Q1, other input conditions should be considered carefully in terms of Q1's potential overheating. Of course, if higher powered devices are used for Q1, this circuit can support outputs of tens of amperes as well as the higher V<sub>OUT</sub> levels noted above.

The circuit shown can be used either as a standard low dropout regulator, or it can be used with ON/OFF control. By driving Pin 3 of U1 with the optional logic control signal  $V_C$ , the output is switched between ON and OFF. Note that when the output is OFF in this circuit, it is still active (i.e., not an open circuit). This is because the OFF state simply reduces the voltage input to R1, leaving the U1A/B amplifiers and Q1 still active.

When ON/OFF control is used, resistor R10 should be used with U1 to speed ON-OFF switching and to allow the output of the circuit to settle to a nominal zero voltage. Components D3 and R11 also aid in speeding up the ON-OFF transition by providing a dynamic discharge path for C2. OFF-ON transition time is less than 1 ms, while the ON-OFF transition is longer but under 10 ms.

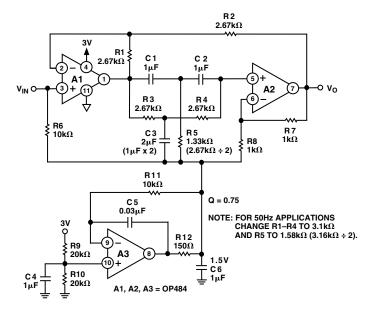

#### A 3 V, 50 Hz/60 Hz Active Notch Filter with False Ground

To process signals in a single-supply system, it is often best to use a false ground biasing scheme. A circuit that uses this approach is illustrated in Figure 19. In this circuit, a false-ground circuit biases an active notch filter used to reject 50 Hz/60 Hz power line interference in portable patient monitoring equipment. Notch filters are quite commonly used to reject power line frequency interference that often obscures low frequency physiological signals, such as heart rates, blood pressure read-

ings, EEGs, EKGs, etc. This notch filter effectively squelches 60 Hz pickup at a filter Q of 0.75. Substituting 3.16 k $\Omega$  resistors for the 2.67 k $\Omega$  in the twin-T section (R1 through R5) configures the active filter to reject 50 Hz interference.

Figure 19. A 3 V Single Supply, 50/60 Hz Active Notch Filter with False Ground

Amplifier A3 is the heart of the false-ground bias circuit. It simply buffers the voltage developed at R9 and R10 and is the reference for the active notch filter. Since the OP484 exhibits a rail-to-rail input common-mode range, R9 and R10 are chosen to split the 3 V supply symmetrically. An in-the-loop compensation scheme is used around the OP484 that allows the op amp to drive C6, a 1  $\mu F$  capacitor, without oscillation. C6 maintains a low impedance ac ground over the operating frequency range of the filter.

The filter section uses a OP484 in a twin-T configuration whose frequency selectivity is very sensitive to the relative matching of the capacitors and resistors in the twin-T section. Mylar is the material of choice for the capacitors, and the relative matching of the capacitors and resistors determines the filter's pass band symmetry. Using 1% resistors and 5% capacitors produces satisfactory results.

REV. B

-16-

| *OP284 SPICE Macro-model 9/94 / Rev. A<br>* ARG/ADI                       |          |          |              |                                        | DN5<br>DN6 | 19<br>23          | 23<br>24 | DIN<br>DIN                              |

|---------------------------------------------------------------------------|----------|----------|--------------|----------------------------------------|------------|-------------------|----------|-----------------------------------------|

| * ARG/ADI                                                                 |          |          |              |                                        | *          |                   |          |                                         |

| * Copyright 1995 by Analog Devices<br>*                                   |          |          | * GAII<br>*  | N STA                                  | GE         |                   |          |                                         |

| * Refer to "README.DOC" file for License Statement. Use of                |          |          |              |                                        | EREF       | 98                | 0        | POLY(2) (99,0) (50,0) 0 0.5 0.5         |

| this model * indicates your acceptance of the terms and provisions in the |          |          |              |                                        | G1<br>R9   | 98<br>20          | 20<br>98 | POLY(2) (6,5) (8,7) 0 0.5E-3 0.5E-3 1E3 |

| License                                                                   |          | ur acce  | ptance       | of the terms and provisions in the     | *          | 20                | 90       | TE3                                     |

| * State                                                                   |          |          |              |                                        | * CON      | MON               | I MOD    | DE STAGE WITH ZERO AT 100Hz             |

| * Node                                                                    | assign   | ments    |              |                                        | ECM        | 98                | 21       | POLY(2) (1,98) (2,98) 0 0.5 0.5         |

| *                                                                         | Ü        |          |              | noninverting input                     | R10        | 21                | 22       | 1                                       |

| *                                                                         |          |          |              | inverting input                        | R11        | 22                | 98       | 100E-6                                  |

| *                                                                         |          |          |              | positive supply<br>    negative supply | C4<br>*    | 21                | 22       | 1.592E-3                                |

| *                                                                         |          |          |              | negative supply<br>      output        | * NEG      | ATIV              | E ZER    | O AT 20MHz                              |

| *                                                                         |          |          |              |                                        | *          |                   |          |                                         |

| .SUBC                                                                     | KT O     | P284     |              | 1 2 99 50 45                           | E1         | 27                | 98       | (20,98) 1E6                             |

| * 12.101                                                                  | TEL OF   | A 0.E    |              |                                        | R17<br>R18 | 27                | 28       | 1                                       |

| * INPU<br>*                                                               | JT ST.   | AGE      |              |                                        | C8         | 28<br>25          | 98<br>26 | 1E-6<br>7.958E-9                        |

| Q1                                                                        | 5        | 2        | 3            | QIN 1                                  | ENZ        | 25                | 98       | (27,28) 1                               |

| Q2                                                                        | 6        | 11       | 3            | QIN 1                                  | VNZ        | 26                | 98       | DC 0                                    |

| Q3                                                                        | 7        | 2        | 4            | QIP 1                                  | FNZ        | 27                | 28       | VNZ -1                                  |

| Q4                                                                        | 8        | 11       | 4            | QIP 1                                  | * 201      | C                 | 403.577  |                                         |

| DC1<br>DC2                                                                | 2        | 11       | DC           |                                        | * POL      | EAL               | 40MH2    | Z                                       |

| Q5                                                                        | 11<br>4  | 2<br>9   | DC<br>99     | QIP 1                                  | G4         | 98                | 29       | (28,98) 1                               |

| Q6                                                                        | 9        | 9        | 99           | QIP 1                                  | R19        | 29                | 98       | 1                                       |

| Q7                                                                        | 3        | 10       | 50           | QIN 1                                  | C9         | 29                | 98       | 3.979E-9                                |

| Q8                                                                        | 10       | 10       | 50           | QIN 1                                  | *          |                   |          |                                         |

| R1                                                                        | 99       | 5        | 4E3          |                                        | * POL      | EAT               | 40MHz    | Z                                       |

| R2<br>R3                                                                  | 99<br>7  | 6<br>50  | 4E3<br>4E3   |                                        | G5         | 98                | 30       | (29,98) 1                               |

| R4                                                                        | 8        | 50       | 4E3          |                                        | R20        | 30                | 98       | 1                                       |

| <b>IREF</b>                                                               | 9        | 10       | 50.5E        | E-6                                    | C10        | 30                | 98       | 3.979E-9                                |

| EOS                                                                       | 1        | 11       |              | Y(2) (22,98) (14,98) -25E-6 1E-2 1     | *          |                   |          | _                                       |

| IOS                                                                       | 2        | 1        | 5E-9         | 2                                      | * OUT<br>* | PUT               | STAG     | E .                                     |

| CIN<br>GN1                                                                | 1<br>98  | 2<br>1   | 2E-12        | 2<br>8) 1E-3                           | ISY        | 99                | 50       | 0.276E-3                                |

| GN2                                                                       | 98       | 2        |              | 8) 1E-3                                | GIN        | 50                | 31       | POLY(1) (30,98) .862574E-6 505.879E-6   |

| *                                                                         |          |          | (==)-        | -,                                     | RIN        | 31                | 50       | 2.75E6                                  |

|                                                                           | TAGE     | NOIS     | E SOU        | RCE WITH FLICKER NOISE                 | VB         | 99                | 32       | 0.7                                     |

| *                                                                         | 10       | 0.0      | DC 4         |                                        | Q11        | 32                | 31       | 33 QON 1                                |

| VN1<br>VN2                                                                | 13<br>98 | 98<br>15 | DC 2<br>DC 2 |                                        | R21<br>I1  | 33<br>34          | 34<br>50 | 4.5E3<br>50E-6                          |

| DN1                                                                       | 13       | 14       | DEN          |                                        | R22        | 99                | 35       | 6E3                                     |

| DN2                                                                       | 14       | 15       | DEN          |                                        | Q12        | 36                | 36       | 35 QOP 1                                |

| *                                                                         |          |          |              |                                        | I2         | 36                | 50       | 50E-6                                   |

| * CUR                                                                     | RENT     | NOIS     | E SOU        | RCE WITH FLICKER NOISE                 | R23        | 99                | 37       | 2.6E3                                   |

| *<br>VN3                                                                  | 16       | 98       | DC 2         | ,                                      | R24<br>Q13 | 34<br>39          | 38<br>36 | 5E3<br>37 QOP 1                         |

| VN3<br>VN4                                                                | 98       | 98<br>18 | DC 2         |                                        | Q13        | 39                | 38       | 40 QON 1.5                              |

| DN3                                                                       | 16       | 17       | DIN          |                                        | R25        | 40                | 50       | 40                                      |

| DN4                                                                       | 17       | 18       | DIN          |                                        | Q15        | 39                | 39       | 41 QON 1                                |

| *                                                                         | 0        |          |              |                                        | R26        | 41                | 42       | 1E3                                     |

| * 2ND CURRENT NOISE SOURCE WITH FLICKER                                   |          |          | R27<br>Q16   | 99<br>44                               | 43<br>44   | 220<br>43 QOP 1.5 |          |                                         |

| NOISE<br>*                                                                | 2        |          |              |                                        | Q16<br>Q17 | 44<br>44          | 39       | 43 QOF 1.5<br>42 QON 1                  |

| VN5                                                                       | 19       | 98       | DC 2         | 2                                      | R28        | 42                | 50       | 2E3                                     |

| VN6                                                                       | 98       | 24       | DC 2         |                                        | VSCP       | 99                | 97       | DC 0                                    |

REV. B -17-

```

FSCP

46

99

VSCP 1

RSCP

46

99

40

Q20

44

46

99

QOP 1

Q18

45

44

97

QOP 4.5

Q19

45

34

51

QON 4.5

VSCN

51

50

DC 0

FSCN

50

47

VSCN 1

RSCN 47

50

40

Q21

34

47

50

QON 1

CC2

31

45

20E-12

CF1

31

34

15E-12

CF2

31

42

15E-12

CO1

34

45

15E-12

CO<sub>2</sub>

42

45

5E-12

D3

45

99

DX

D4

50

45

DX

.MODEL DC D(IS=130E-21)

.MODEL DX D()

.MODEL DEN D(RS=100 KF=12E-15 AF=1)

.MODEL DIN D(RS=5.358 KF=56E-15 AF=1)

.MODEL QIN NPN(BF=200 VA=200 IS=0.5E-16)

.MODEL QIP PNP(BF=100 VA=60 IS=0.5E-16)

.MODEL QON NPN(BF=200 VA=200 IS=0.5E-16 RC=50)

.MODEL QOP PNP(BF=200 VA=200 IS=0.5E-16 RC=160)

.ENDS

```

–18– REV. B

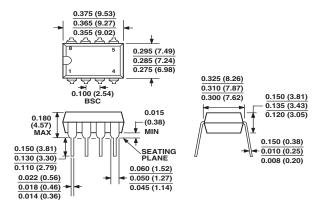

#### **OUTLINE DIMENSIONS**

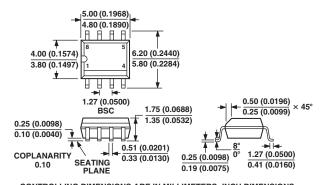

# 8-Lead Plastic Dual-in-Line Package [PDIP] (N-8)

Dimensions shown in inches and (millimeters)

COMPLIANT TO JEDEC STANDARDS MO-095AA

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS

(IN PARENTHESES)

# 8-Lead Standard Small Outline Package [SOIC] Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN COMPLIANT TO JEDEC STANDARDS MS-012AA

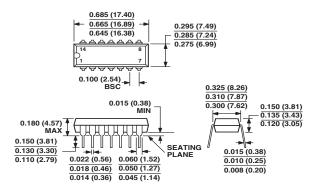

# 14-Lead Plastic Dual-in-Line Package [PDIP] (N-14)

Dimensions shown in inches and (millimeters)

COMPLIANT TO JEDEC STANDARDS MO-095-AB

CONTROLLING DIMENSIONS ARE IN INCH; MILLIMETERS DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

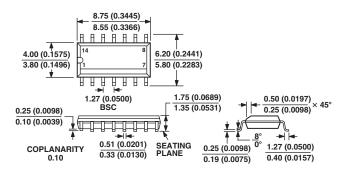

#### 14-Lead Standard Small Outline Package [SOIC] Narrow Body

(R-14)

Dimensions shown in millimeters and (inches)

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

# **Revision History**

REV. B –19–