# SX-Key/Blitz Development System Manual Version 2.0

PARALLAX www.parallax.com

#### WARRANTY

Parallax warrants its products against defects in materials and workmanship for a period of 90 days from receipt of product. If you discover a defect, Parallax will, at its option, repair or replace the merchandise, or refund the purchase price. Before returning the product to Parallax, call for a Return Merchandise Authorization (RMA) number. Write the RMA number on the outside of the box used to return the merchandise to Parallax. Please enclose the following along with the returned merchandise: your name, telephone number, shipping address, and a description of the problem. Parallax will return your product or its replacement using the same shipping method used to ship the product to Parallax.

#### 14-DAY MONEY BACK GUARANTEE

If, within 14 days of having received your product, you find that it does not suit your needs, you may return it for a full refund. Parallax will refund the purchase price of the product, excluding shipping/handling costs. This guarantee is void if the product has been altered or damaged. See the Warranty section above for instructions on returning a product to Parallax.

#### **COPYRIGHTS AND TRADEMARKS**

This documentation is Copyright 2003 by Parallax, Inc. By downloading or obtaining a printed copy of this documentation or software you agree that it is to be used exclusively with Parallax products. Any other uses are not permitted and may represent a violation of Parallax copyrights, legally punishable according to Federal copyright or intellectual property laws. Any duplication of this documentation for commercial uses is expressly prohibited by Parallax, Inc. Check with Parallax for approval prior to duplicating any of our documentation in part or whole for any use.

SX-Key is a registered trademark of Parallax, Inc. If you decide to use the name SX-Key on your web page or in printed material, you must state that "SX-Key is a registered trademark of Parallax, Inc." Other brand and product names are trademarks or registered trademarks of their respective holders

#### ISBN 1-928982-01-8

#### DISCLAIMER OF LIABILITY

Parallax, Inc. is not responsible for special, incidental, or consequential damages resulting from any breach of warranty, or under any legal theory, including lost profits, downtime, goodwill, damage to or replacement of equipment or property, or any costs of recovering, reprogramming, or reproducing any data stored in or used with Parallax products. Parallax is also not responsible for any personal damage, including that to life and health, resulting from use of any of our products. You take full responsibility for your SX-Key/Blitz and SX chip application, no matter how life-threatening it may be.

#### WEB SITE AND DISCUSSION LISTS

The Parallax web site (www.parallax.com) has many downloads, products, customer applications and on-line ordering for the components used in this text. We also maintain several e-mail discussion lists for people interested in using Parallax products. These lists are accessible from www.parallax.com via the Support? Discussion Groups menu. These are the lists that we operate:

- SX Tech Discussion of programming the SX microcontroller with Parallax assembly language tools and 3<sup>rd</sup> party BASIC and C compilers. Approximately 600 members.

- BASIC Stamps With over 2,500 subscribers, this list is widely utilized by engineers, hobbyists and students who share their BASIC Stamp projects and ask questions.

- Stamps in Class Created for educators and students, this list has 500 subscribers who discuss the use of the Stamps in Class curriculum in their courses. The list provides an opportunity for both students and educators to ask questions and get answers.

- <u>Parallax Educators</u> This focus group of 100 members consists exclusively of educators and those who contribute to the

development of Stamps in Class. Parallax created this group to obtain feedback on our curricula and to provide a forum

for educators to develop Teacher's Guides.

- Parallax Translators Consisting of less than 10 people, the purpose of this list is to provide a conduit between Parallax

and those who translate our documentation to languages other than English. Parallax provides editable Word

documents to our translating partners and attempts to time the translations to coordinate with our publications.

- <u>Toddler Robot</u> A customer created this discussion list to discuss applications and programming of the Parallax Toddler robot.

- <u>Javelin Stamp</u> Discussion of application and design using the Javelin Stamp, a Parallax module that is programmed using a subset of Sun Microsystems' Java® programming language. Approximately 250 members.

This manual is valid with the following software and firmware versions:

IDE:

SXKey.exe software version 2.0

Firmware:

SX-Key rev. F and SX-Blitz rev. A

The information herein will usually apply to newer versions but may not apply to older versions. New software can be obtained free on our web site (www.parallax.com). If you have any questions about what you need to upgrade your product, please contact Parallax.

### Welcome

Thank you for purchasing the Parallax SX-Key®/Blitz development system. We have done our best to produce a full-featured, yet easy to use development system for the SX microcontrollers. The result is the SX-Key and the SX-Blitz; very tiny, full-featured development tools with a Windows® 95 and higher versions interface. We hope you will find this system as enjoyable to use as we do.

This manual is written for the SX20/28 chips with a date code of AB9921AA or later, and SX48/52 chips with a date code of AB0001A or later.

Older chips are not supported by this manual or the SX-Key development system.

| 1 | Intro | duction t  | to the SX-Key/Blitz Hardware               | 13 |

|---|-------|------------|--------------------------------------------|----|

| 2 | Insta | lling the  | SX-Key/Blitz Software                      | 15 |

| 3 | Quic  | k Start In | ntroduction                                | 17 |

|   | 3.1   | Connec     | cting and Downloading to the SX Tech Board | 17 |

| 4 | The S | SX-Key/I   | Blitz Interface                            | 19 |

|   | 4.1   | Starting   | g the SX-Key/Blitz Software                | 19 |

|   |       | 4.1.1      | Command Line Switches                      | 19 |

|   | 4.2   | The SX     | Editor                                     | 20 |

|   | 4.3   | The Me     | enus                                       | 21 |

|   |       | 4.3.1      | The File Menu                              | 21 |

|   |       | 4.3.2      | The Edit Menu                              | 22 |

|   |       | 4.3.3      | The Run Menu                               | 23 |

|   |       | 4.3.4      | The Help Menu                              | 25 |

|   | 4.4   | The Wi     | indows                                     | 25 |

|   |       | 4.4.1      | Print Window                               | 25 |

|   |       | 4.4.2      | Find Window                                | 26 |

|   |       | 4.4.3      | Find/Replace Window                        |    |

|   |       | 4.4.4      | Goto Line Number Window                    | 27 |

|   |       | 4.4.5      | Configure Window                           |    |

| 5 | The S |            | Debugger                                   |    |

|   | 5.1   | The De     | bugger Windows                             |    |

|   |       | 5.1.1      | The Registers Window                       |    |

|   |       | 5.1.2      | The Debug Window                           |    |

|   |       | 5.1.3      | The Watch Window                           |    |

|   |       | 5.1.4      | The Code/List File Window                  |    |

|   |       | 5.1.5      | Modifying registers during debugging       |    |

|   |       | 5.1.6      | Breakpoints and the Current Instruction    |    |

|   |       | 5.1.7      | Setting the Program Counter                |    |

| 6 |       |            | /indow                                     |    |

| 7 |       |            | ssembler                                   |    |

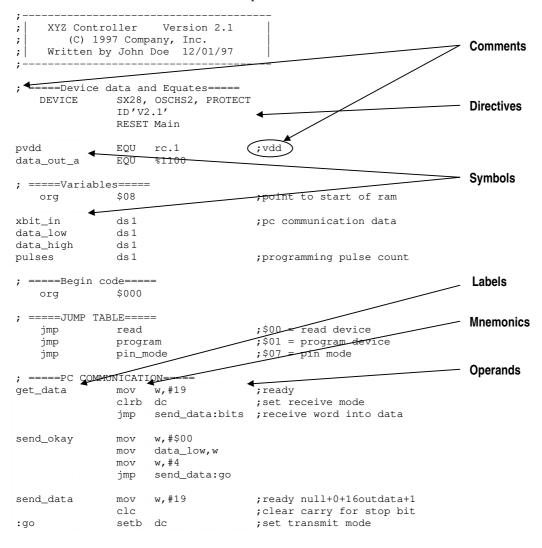

|   | 7.1   |            | ructure of an SX Assembly Program          |    |

|   | 7.2   |            | ents                                       |    |

|   | 7.3   |            | bler Directives                            |    |

|   |       | 7.3.1      | The EQU and = Directives                   |    |

|   |       | 7.3.2      | The BREAK Directive                        |    |

|   |       | 7.3.3      | The CASE and NOCASE Directives             |    |

|   |       | 7.3.4      | The DEVICE Directive                       |    |

|   |       | 7.3.5      | The DS Directive                           |    |

|   |       | 7.3.6      | The DW Directive                           |    |

|   |       | 7.3.7      | The END Directive                          |    |

|   |       | 7.3.8      | The ERROR Directive                        |    |

|   |       | 7.3.9      | The FREQ Directive                         |    |

|   |       | 7.3.10     | TheFUSE andFUSEX Directives                | 52 |

|   |       |            |                                            |    |

|   |       | 7.3.11  | The ID Directive                          | 53 |

|---|-------|---------|-------------------------------------------|----|

|   |       | 7.3.12  | The IFELSEENDIF Directive                 | 53 |

|   |       | 7.3.13  | The IF{N}DEFELSEENDIF Directives          | 54 |

|   |       | 7.3.14  | The INCLUDE Directive                     | 55 |

|   |       | 7.3.15  | The IRC_CAL Directive                     | 56 |

|   |       | 7.3.16  | The LIST Directive                        | 56 |

|   |       | 7.3.17  | The LPAGE Directive                       | 57 |

|   |       | 7.3.18  | The ORG (Origin) Directive                | 57 |

|   |       | 7.3.19  | The RADIX Directive                       | 58 |

|   |       | 7.3.20  | The REPT Directive                        |    |

|   |       | 7.3.21  | The RESET Directive                       | 59 |

|   |       | 7.3.22  | The SPAC Directive                        | 59 |

|   |       | 7.3.23  | The TITLE and STITLE Directives           | 60 |

|   |       | 7.3.24  | The WATCH Directive                       | 60 |

|   | 7.4   | Macros  | 3                                         | 62 |

|   |       | 7.4.1   | The MACRO Directive                       | 62 |

|   |       | 7.4.2   | The ENDM Directive                        |    |

|   |       | 7.4.3   | The EXITM Directive                       |    |

|   |       | 7.4.4   | The LOCAL Directive                       |    |

|   |       | 7.4.5   | The EXPAND and NOEXPAND Directives        |    |

|   |       | 7.4.6   | Formal Parameters                         |    |

|   |       | 7.4.7   | Macro Invocation                          | 65 |

|   |       | 7.4.8   | Actual Values of Parameters               |    |

|   |       | 7.4.9   | Token Pasting                             | 65 |

|   |       | 7.4.10  | Quoting                                   | 65 |

|   |       | 7.4.11  | Macro Examples                            | 66 |

|   |       |         | 7.4.11.1 Simple Macros with no Parameters | 66 |

|   |       | 7.4.12  | Macros with Formal Parameters by Count    |    |

|   |       | 7.4.13  | Macros with Formal Parameters by Name     |    |

|   | 7.5   | Symbol  | ls                                        | 68 |

|   | 7.6   | Labels. |                                           | 69 |

|   | 7.7   | Express | sions                                     | 70 |

|   | 7.8   |         | ypes                                      |    |

|   | 7.9   | TheS    | SASM Pre-Defined Constant                 | 72 |

|   | 7.10  |         | eated by SASM                             |    |

|   | 7.11  |         | Warning and Error Messages                |    |

|   | 7.12  |         | ed Words and Symbols                      |    |

| 8 | The I |         | Assembler                                 |    |

|   | 8.1   |         | ructure of an SX Assembly Program         |    |

|   | 8.2   |         | bler Directives                           |    |

|   |       | 8.2.1   | The Device Directive                      |    |

|   | 8.3   | _       | ls                                        |    |

|   | 8.4   |         |                                           |    |

|   | 8.5   |         | sions                                     |    |

|   | 8.6   | Error M | Messages                                  | 81 |

|    | 8.7   | Data Types                                   | 83  |

|----|-------|----------------------------------------------|-----|

|    | 8.8   | Reserved Words and Symbols                   |     |

| 9  | Upgr  | rading Existing Code for SASM                |     |

| 10 | SX Sp | pecial Features and Coding Tips              | 87  |

|    |       | Introduction                                 |     |

|    | 10.2  | Port Configuration and Usage                 | 87  |

|    |       | 10.2.1 Port Direction                        |     |

|    |       | 10.2.2 Pull-Up Resistors                     | 89  |

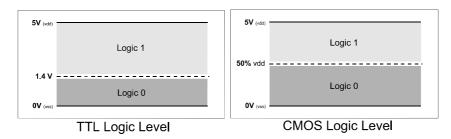

|    |       | 10.2.3 Logic Level                           | 90  |

|    |       | 10.2.4 Schmitt-Trigger                       |     |

|    |       | 10.2.5 Edge Detection                        |     |

|    |       | 10.2.6 Wakeup (Interrupt) on Edge Detection  | 93  |

|    |       | 10.2.7 Comparator                            | 95  |

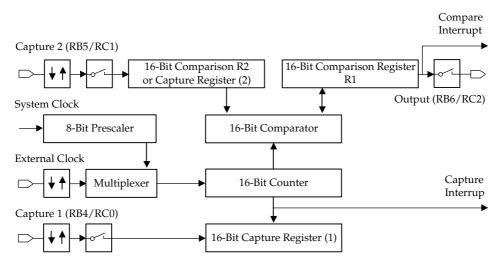

|    | 10.3  | The SX48/52 Multi-Function Timers            | 96  |

|    |       | 10.3.1 PWM Mode                              | 97  |

|    |       | 10.3.2 Software Timer Mode                   | 98  |

|    |       | 10.3.3 External Event Counter                | 98  |

|    |       | 10.3.4 Capture/Compare Mode                  | 98  |

|    | 10.4  | All About Interrupts                         | 99  |

|    |       | 10.4.1 RTCC Rollover Interrupts              | 100 |

|    | 10.5  | Creating Tables                              | 103 |

|    |       | 10.5.1 Data Tables                           |     |

|    | 10.6  | Dealing with Code Pages                      |     |

|    |       | 10.6.1 Branching Across Pages                |     |

|    |       | 10.6.2 Calling Across Pages with Jump Tables |     |

| 11 |       | endix A: SX Features                         |     |

|    |       | Introduction                                 |     |

|    |       | CPU Features                                 |     |

|    |       | Peripheral and I/O Features                  |     |

| 12 | Appe  | endix B: Instruction Set Overview            |     |

|    | 12.1  | Introduction                                 |     |

|    | 12.2  | Instruction Set Summary                      |     |

|    | 12.3  | Single Word Instructions                     |     |

|    | 12.4  | Multi-Word Instructions                      |     |

|    | 12.5  | Instruction Set Quick Reference              |     |

| 13 |       | endix C: SX Instruction Set                  |     |

|    |       | Introduction                                 |     |

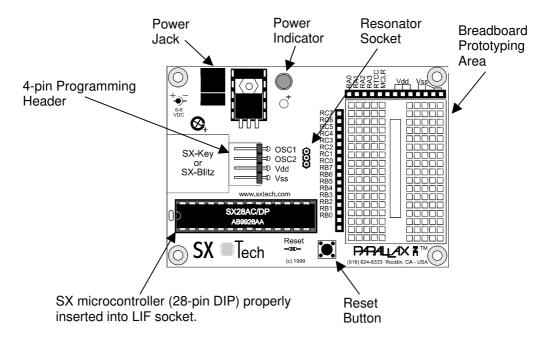

| 14 |       | endix D: The SX Tech Board                   |     |

|    | 14.1  | SX Tech Board Features                       |     |

|    | 14.2  | Connecting and Downloading                   |     |

|    |       |                                              |     |

| 15 | Appe  | endix E: SX Data Sheet                       |     |

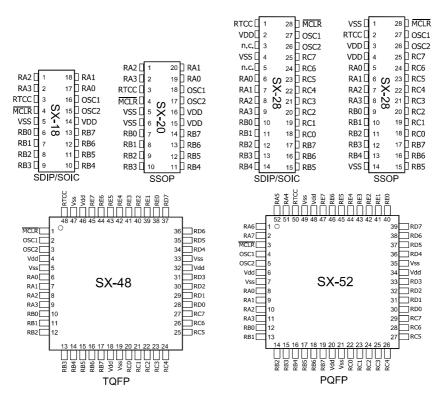

|    | 15.1  | Pinout Information and Descriptions          |     |

|    | 15.2  | Architecture                                 |     |

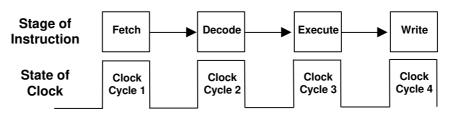

|    |       | 15.2.1 Instruction Pipeline                  | 151 |

|      | 15.2.2  | Read-Modify-Write Considerations                  | 151 |

|------|---------|---------------------------------------------------|-----|

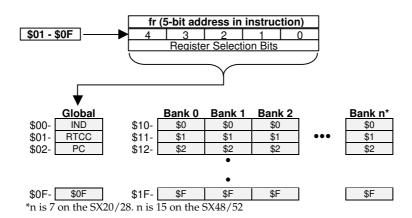

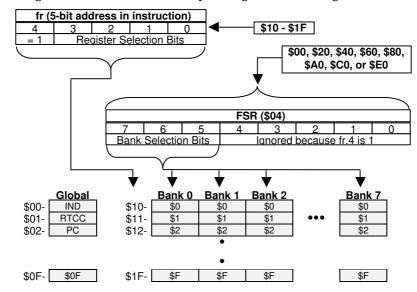

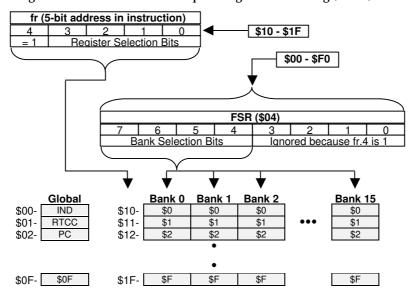

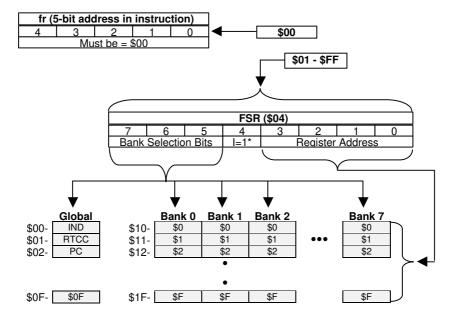

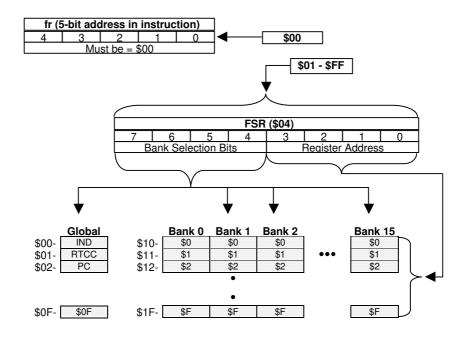

|      | 15.2.3  | Register Map Structure                            | 151 |

|      | 15.2.4  | Special Function Registers                        | 153 |

|      | 15.2.5  | IND – The Indirect Register (\$00)                |     |

|      | 15.2.6  | Real Time Clock/Counter, WREG (\$01)              | 153 |

|      | 15.2.7  | PC – Program Counter (\$02)                       | 153 |

|      | 15.2.8  | STATUS Register (\$03)                            |     |

|      | 15.2.9  | The FSR – File Select Register (\$04)             |     |

|      | 15.2.10 | Direct Addressing                                 |     |

|      | 15.2.11 | Indirect Addressing                               |     |

|      | 15.2.12 | The Bank Instruction                              |     |

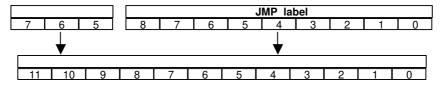

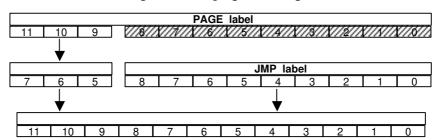

|      | 15.2.13 | The Jump Instruction                              |     |

|      | 15.2.14 | Jumping Across Pages                              | 163 |

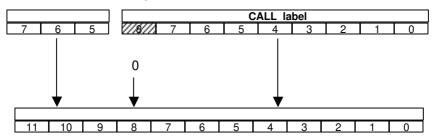

|      | 15.2.15 | The Call Instruction                              |     |

|      | 15.2.16 | Calling Across Pages                              |     |

|      | 15.2.17 | Returning from a subroutine                       | 164 |

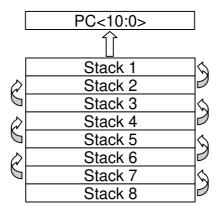

|      | 15.2.18 | The Stack                                         |     |

|      | 15.2.19 | The Push                                          |     |

|      | 15.2.20 | The Pop                                           | 166 |

|      | 15.2.21 | Stack Overflow                                    |     |

|      | 15.2.22 |                                                   |     |

|      | 15.2.23 | Returns                                           |     |

| 15.3 | Port Co | nfiguration Registers                             | 167 |

|      | 15.3.1  | Port A Registers                                  |     |

|      |         | 15.3.1.1 TRIS_A – Data Direction Register         |     |

|      |         | 15.3.1.2 LVL_A - TTL/CMOS Select Register         | 167 |

|      |         | 15.3.1.3 PLP_A – Pull-Up Resistor Enable Register | 167 |

|      | 15.3.2  | Port B Registers                                  |     |

|      |         | 15.3.2.1 TRIS_B – Data Direction Register         | 168 |

|      |         | 15.3.2.2 LVL_B - TTL/CMOS Select Register         | 168 |

|      |         | 15.3.2.3 PLP_B – Pull-Up Resistor Enable Register | 168 |

|      |         | 15.3.2.4 ST_B – Schmitt-Trigger Enable Register   | 169 |

|      |         | 15.3.2.5 WKEN_B – Wake Up Enable Register         |     |

|      |         | 15.3.2.6 WKED_B – Wake Up Edge Select Register    | 169 |

|      |         | 15.3.2.7 WKPND_B – MIWU Pending Register          |     |

|      |         | 15.3.2.8 CMP_B – Comparator Enable Register       | 170 |

|      | 15.3.3  | Port C Registers                                  | 170 |

|      |         | 15.3.3.1 TRIS_C – Data Direction Register         | 170 |

|      |         | 15.3.3.2 LVL_C - TTL/CMOS Select Register         | 170 |

|      |         | 15.3.3.3 PLP_C – Pull-Up Resistor Enable Register | 171 |

|      |         | 15.3.3.4 ST_C – Schmitt-Trigger Enable Register   | 171 |

|      | 15.3.4  | Port D and E Registers (SX48/52)                  | 171 |

| 15.4 | Control | registers                                         |     |

|      | 15.4.1  | Mode register (SX20/28)                           | 171 |

|      | 15.4.2  | Mode register (SX48/52)                           | 173 |

|      |         |                                                   |     |

|    |       | 15.4.3  | Option                      | 174 |

|----|-------|---------|-----------------------------|-----|

|    |       | 15.4.4  | Fuse Registers              | 174 |

|    | 15.5  | Interru | pts                         | 175 |

|    |       | 15.5.1  | Description                 | 175 |

|    |       | 15.5.2  | The Specifics               | 175 |

|    |       |         | RTCC Interrupt              |     |

|    |       | 15.5.4  | RB0-RB7 Interrupt           | 176 |

|    | 15.6  | Periphe | erals                       | 176 |

|    |       | 15.6.1  | Oscillator Driver           | 176 |

|    |       |         | 15.6.1.1 LP, XT and HS Mode | 176 |

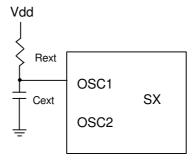

|    |       |         | 15.6.1.2 External RC Mode   | 178 |

|    |       |         | 15.6.1.3 Internal RC Mode.  |     |

| 16 | Index | ζ       |                             |     |

|    |       |         |                             |     |

# Figures

| Figure 1 - Connecting the SX-Key/Blitz                           | 13  |

|------------------------------------------------------------------|-----|

| Figure 2 - First Time Running Window                             | 16  |

| Figure 3 - Configure Window                                      | 16  |

| Figure 4 - SX Tech Board with SX chip inserted                   |     |

| Figure 5 - The SX-Key Icon                                       | 19  |

| Figure 6 - The SX Editor                                         | 20  |

| Figure 7 - The Find Window                                       | 26  |

| Figure 8 - The Find/Replace Window                               | 26  |

| Figure 9 - The Goto Line Number Window                           | 27  |

| Figure 10 - The Configure Window                                 | 28  |

| Figure 11 - The Debugger Windows                                 |     |

| Figure 12 - The Device Window                                    |     |

| Figure 13 - The Watch Window                                     | 61  |

| Figure 14 - TTL and CMOS Levels                                  | 90  |

| Figure 15 - Schmitt Trigger Characteristics                      |     |

| Figure 16 - SX48/52 Multi-Function Timers                        | 97  |

| Figure 17 - The SX Tech Board                                    | 145 |

| Figure 18 - SX Tech Board Schematic                              |     |

| Figure 19 - SX Pinouts                                           |     |

| Figure 20 - Instruction Pipeline                                 |     |

| Figure 21 - SX20/28 Register Map                                 |     |

| Figure 22 - SX48/52 Register Map                                 |     |

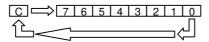

| Figure 23 - Rotate Right                                         |     |

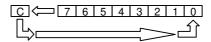

| Figure 24 - Rotate Left                                          |     |

| Figure 25 - Global Register Addressing SX20/28/48/52 (direct)    |     |

| Figure 26 - SX20/28 General Purpose Register Addressing (direct) | 157 |

| Figure 27 - SX48/52 General-Purpose Register addressing (direct) |     |

| Figure 28- SX20/28 Indirect register addressing                  |     |

| Figure 29 - SX48/52 Indirect register addressing                 |     |

| Figure 30 - The Jump Instruction                                 |     |

| Figure 31 - Jumping Across Pages                                 |     |

| Figure 32 - The Call Instruction                                 |     |

| Figure 33 - Calling Across Pages                                 |     |

| Figure 34 - The Push                                             |     |

| Figure 35 - The Pop                                              |     |

| Figure 36 - Prescaler Division Ratios                            |     |

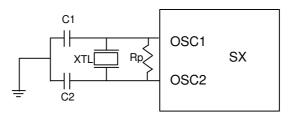

| Figure 37 - SX with External Crystal                             |     |

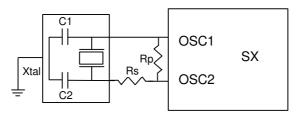

| Figure 38 - SX with External Ceramic Resonator                   |     |

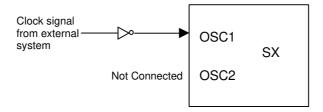

| Figure 39 - SX with External System Clock                        |     |

| Figure 40 - External RC Mode                                     |     |

### **Tables**

| Table 1 - Editor Shortcut Keys                                             | 21  |

|----------------------------------------------------------------------------|-----|

| Table 2 - Debugger Buttons and Shortcut Keys                               | 35  |

| Table 3 – Register Editing Keys                                            | 36  |

| Table 4 - SX Clock Options                                                 | 40  |

| Table 5 - SASM Directives                                                  | 46  |

| Table 6 - SX20/28 DEVICE Settings                                          | 49  |

| Table 7 - SX48/52 DEVICE Settings                                          | 50  |

| Table 8 – Comparison Operators                                             | 53  |

| Table 9 - LIST Directive Options                                           | 57  |

| Table 10 - WATCH Display Formats                                           | 60  |

| Table 11 - Unary Operators                                                 | 71  |

| Table 12 - Binary Operators                                                | 71  |

| Table 13 - Data Types                                                      | 72  |

| Table 14 - SASM Error and Warning Messages                                 | 75  |

| Table 15 - SASM Reserved Words                                             | 78  |

| Table 16 - Parallax Assembler DEVICE Options                               | 80  |

| Table 17 - Parallax Assembler Error Messages                               |     |

| Table 18 - Parallax Assembler Reserved Words                               | 84  |

| Table 19 - Port Configuration Options                                      | 87  |

| Table 20 - MODE Register Settings                                          | 88  |

| Table 21 - Interrupt Timing                                                | 102 |

| Table 22 - SX Instruction Mnemonics                                        | 112 |

| Table 23 - SX Single-Word Instructions                                     | 114 |

| Table 24 - SX Multi-Word Instructions                                      |     |

| Table 25 - SX Instruction Set Quick Reference                              | 118 |

| Table 26 - Symbol and Value Operands                                       | 121 |

| Table 27 - Flags and Registers                                             | 122 |

| Table 28 - Binary Symbols                                                  |     |

| Table 29 - SX Pins                                                         |     |

| Table 30 - Special Function Registers                                      |     |

| Table 31 - Bank Addresses and FSR Values                                   |     |

| Table 32 – SX20/28 Mode Register                                           | 172 |

| Table 33 - SX48/52 Mode Register                                           |     |

| Table 34 – External Component Selection for Crystals (Vdd = 5V)            | 177 |

| Table 35 - Component Selection for Murata Ceramic Resonators (Vdd = 5.0 V) | 177 |

| Table of Contents |  |  |  |

|-------------------|--|--|--|

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

|                   |  |  |  |

### 1 Introduction to the SX-Key/Blitz Hardware

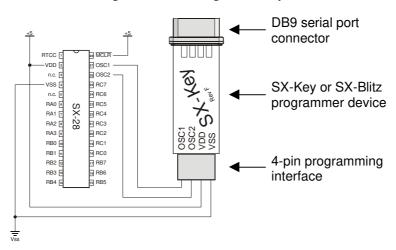

The SX-Key/Blitz hardware consists of the programmer unit, a four-pin programming interface and a standard, female serial port connector (DB9). The serial port connector should be plugged into an available standard, straight-through serial cable on an IBM-compatible PC. The four-pin connector on the SX-Key/Blitz board should be connected to four pins (VSS, VDD, OSC2 and OSC1) of the SX chip. Take care to connect it in the right orientation because this connector is not indexed.

Figure 1 - Connecting the SX-Key/Blitz

The SX-Key/Blitz is powered by the target circuit's power supply and programming and debugging takes place over the oscillator pins. The power supply to the SX-Key/Blitz must be +5 V DC. If an external crystal, resonator or RC circuit is used, the SX-Key/Blitz can usually remain connected to the SX chip for programming purposes, without affecting the operation of the circuit. When debugging, the SX chip must not have an external clock source since the SX-Key's internal programmable oscillator must be used. *The SX-Blitz can only program SX chips, it cannot debug them.*

Each SX microcontroller contains the necessary debugger hooks required to perform SX in-circuit debugging. No other supporting chips are necessary for the debugging process. During debugging, the SX-Key provides the oscillator signal to drive the SX microcontroller until such time that a breakpoint is hit or a single step or stop mode is initiated.

**Figure 1 - Connecting the SX-Key/Blitz** shows all the connections necessary to program, debug and run the SX microcontroller. An external resonator or crystal should be connected to the OSC1 and OSC2 pins to run the SX if the SX-Blitz is used, or if the SX-Key's internal clock oscillator is not used.

# 1 Introduction the SX-Key/Blitz Hardware

The SX-Blitz is designed to be a lower-cost device for programming the SX chips only (no debugging features are available). The SX-Blitz and SX-Key use the same interface software for programming, however, debugging features will not work with the SX-Blitz.

NOTE: Since the SX-Blitz and SX-Key function almost identically, they will be referred to as the SX-Key/Blitz, except where there are distinct differences.

## 2 Installing the SX-Key/Blitz Software

### 2 Installing the SX-Key/Blitz Software

Before following the steps in the next chapter, you should first install the SX-Key/Blitz interface on your computer's hard disk.

The SX-Key/Blitz Interface consists of the integrated editor, programmer, and debugger software. The following system requirements are a minimum for using the SX-Key/Blitz Interface:

- 80486 (or higher) IBM or compatible PC;

- Windows 95 or higher operating system;

- 64 Mb of RAM;

- 3 Mb of available hard drive space;

- CD-ROM drive, or access to the Internet;

- 1 available serial port.

To install the SX-Key/Blitz Interface:

- 1. Insert the Parallax CD-ROM in an available CD-ROM drive.

- 2. Use the CD's automatic browser to navigate to the Software section.

- 3. Expand the SX-Key & SX-Blitz folder.

- 4. Select the 18/28/48/52-pin SX chips (SXKey.exe) item.

- 5. Click on the Install button.

- 6. When prompted for the type of installation, select "Typical" in order to have the software installed in the "Programs\Parallax Inc\SX-Key v2.0" folder. Select "Custom" when you want to change the default installation options, like the installation folder.

- 7. After the setup has finished, you will find a shortcut on the desktop, and a new "Parallax Inc" program group in the Start menu.

You may also download the software from the Parallax web site. There are two different file versions available. One has a size of about 1.2 MB, and the other one of 4.6 MB. When you use the smaller one, it is necessary to have an Internet connection active while installing the software. Select any folder where the downloaded file shall be stored, and then run "Setup\_SX-Key\_Editor.exe" from this folder.

After you have successfully installed the SX-Key Editor and start it the first time, the dialog shown below opens:

# 2 Installing the SX-Key/Blitz Software

Figure 2 - First Time Running Window

This is to remind you that you should review some basic configuration settings first. Click the OK button, and press Ctrl-U to open the Configuration dialog shown to the right.

The only setting that is important for now is the selection of the serial port to which you have connected the SX-Key/Blitz.

X Configure Serial Port C COM1 ○ СОМЗ C COM4 Create backup (.bak) files Assembler Options ▼ Use SASM SASM files to "SASM Dutput" dir. ▼ Local Labels Must Start In Col. 1 ▼ Use New Editor Enhanced Editor Options ◆ Font size: 12 ■ Tab size: 4 Colored Code Keywords ▼ Boldface Code Keywords ▼ Colored Comments Error BG Color ▼ Jump To Assembly Error Line

Figure 3 - Configure Window

The configuration dialog allows you to select COM1, COM2, COM3, or COM4.

Click the radio button in the "Serial Port" section that matches your installation.

Make sure that the remaining options are set to the defaults as shown here, and then click "Okay" to close the configuration dialog window.

You may keep the SX-Key Editor active because you will need it to perform the next steps below.

#### 3 Quick Start Introduction

This chapter is a quick start guide to connecting the SX-Key/Blitz and programming the SX microcontroller. Without even knowing how the SX-Key/Blitz and the SX chip work, you should be able to obtain satisfactory results from the steps that follow.

### 3.1 Connecting and Downloading to the SX Tech Board

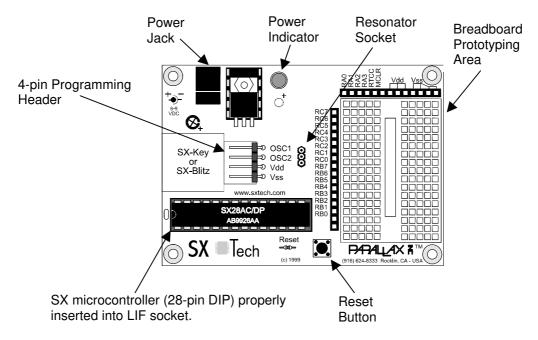

In order to get familiar with how the SX-Key/Blitz Development System works, we'll use the SX Tech Board to program and run a 28-pin SX chip.

Keep in mind that the SX Tech Board is not a programmer; rather the SX-Key/Blitz is the programmer/debugger device while the SX Tech board is a type of prototyping board. Follow these steps to connect and download a program:

Figure 4 - SX Tech Board with SX chip inserted

1) Plug an SX28AC/DP into the 28-pin LIF socket on the SX Tech board as shown in Figure 4 - SX Tech Board with SX chip inserted. Make sure it is oriented so that the half-moon notch in the chip faces away from the "Reset" button.

### 3 Quick Start Instruction

- 2) Connect the SX-Key/Blitz to a serial cable, and the serial cable to the serial (COM) port on the PC that you have selected in the "Configure" dialog of the SX-Key/Blitz software.

- 3) Connect the SX-Key/Blitz to the 4-pin programming header with the VSS, VDD, OSC2 and OSC1 indicators lining up with the same indicators on the board Note that the programming header is not indexed. Therefore, double-check the correct orientation of the SX-Key/Blitz.

- 4) Insert one end of a 470 ohm resister into the RC7 socket (next to the upper left side of the breadboard). Insert the other end of the resister into any hole in the breadboard.

- 5) Insert the shorter leg of an LED into the breadboard hole that is closest (horizontally) to the resister leg. Insert the other leg of the LED into one of the VDD sockets (next to the top side of the breadboard).

- 6) Plug the power supply into the SX Tech board and into an available wall outlet. (The power indicator should light up).

- 7) If it is not still active, start the SX-Key Editor now.

- 8) In the SX-Key Editor window, pull down the File menu and select "Open" (or press Ctrl-O). In the browser window that appears, select and open the led28.src file. (The led28.src source code should appear in the SX-Key code window).

- 9) Pull down the Run menu and select Run (or press Ctrl-R). (The SX-Key software should assemble the code and begin the programming process).

Congratulations! You have just programmed the SX microcontroller with the SX-Key/Blitz Development System. The program in the SX microcontroller should start running. The LED should flash on and off (if wired correctly).

In case you get an error message after you have selected the "Run" option, make sure that you did not modify the source code text in the editor window. If you did, simply re-load the original text by opening it again, and then repeat the steps described above.

Should an error message like "SX-Key not found on COMx" appear, check that you have selected the right serial port for communication with the SX-Key/Blitz, and that the serial cable is correctly connected to the PC, and to the SX-Key/Blitz on the other end. Also make sure that the SX-Key/Blitz is correctly placed on the 4-pin programming header, and that the SX Tech board is powered, i.e. the power indicator LED is active.

The SX-Key/Blitz interface is an integrated editor, programmer, and debugger. All the functions of the SX-Key and the SX-Blitz are available through this single software interface.

Throughout the rest of this manual, the SX-Key/Blitz interface will be referred to as the SX editor, or more simply, the editor.

### 4.1 Starting the SX-Key/Blitz Software

Figure 5 - The SX-Key Icon

During installation, a shortcut was automatically placed on the Windows desktop. Double-click on the SX-Key icon to launch the SX-Key/Blitz interface. In case, the Icon has been deleted from the desktop, you can also start the software via the Windows Start button. Navigate to the Parallax Inc. program group and select "SX-Key v2.0" there.

#### 4.1.1 Command Line Switches

It is also possible to start the SX-Keys software together with parameters from a command line, e.g. using the Windows "Run..." option, or from the DOS command line. The Syntax is:

When you specify a file name with a ".src" extension, the editor window will open, displaying the contents of the source code file. When you specify an ".sxh" extension instead, the hex file will be opened into the device window.

The /r switch is used to open a file in read-only mode, i.e. it can be displayed but not modified in the editor or in the device window.

For example

SxKey /r test.src

opens the source file named "test", and displays it in the editor window and

SxKey /r test.sxh

opens the hex file named "test", and displays the device window. In both examples, the files are opened read-only, i.e. they cannot be modified.

In addition to the /r switch, the switches /1, /2, /3 and /4 are also defined. They are used to select the COM port where the SX-Key/Blitz is attached. This will override the setting that has been recently

made in the Configure window. It is recommended **not** to use these switches; they have been implemented for compatibility reasons only.

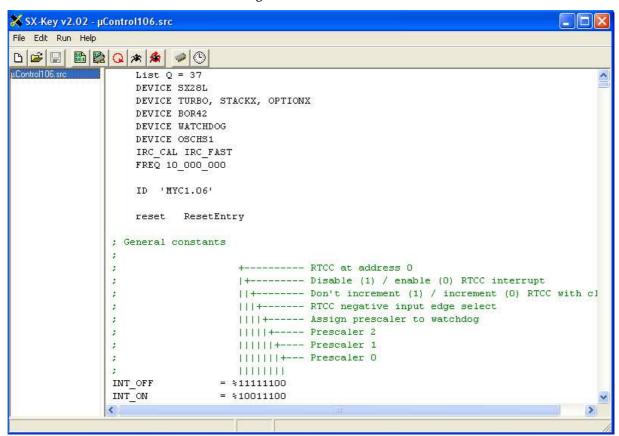

#### 4.2 The SX Editor

Figure 6 - The SX Editor

The SX editor (see Figure 6 – **The SX Editor**, above) consists of a window containing a menu at the top, several shortcut buttons in a tool bar, a list of files that are currently open to the left, and a large text area to the right. In the status bar at the bottom, there is the row/column indicator, telling you at which row and column the cursor is currently located. The editor window is where your SX source code will be entered and edited. Standard Windows editing shortcut keys listed in **Table 1 – Editor Shortcut Keys**, below, may be used in addition to the commands in the Edit menu and the tool bar buttons to manipulate the source code.

Table 1 - Editor Shortcut Keys

| Function      | Shortcut  | Function Description                                                                            |

|---------------|-----------|-------------------------------------------------------------------------------------------------|

| Name          | Keys      |                                                                                                 |

| Copy          | Ctrl-C    | Copies selected text to the clipboard.                                                          |

| Cut           | Ctrl-X    | Cuts selected text to the clipboard.                                                            |

| Paste         | Ctrl-V    | Pastes clipboard contents.                                                                      |

| Page Up       | PgUp      | Moves editor window one page up.                                                                |

| Page Down     | PgDn      | Move editor window one page down.                                                               |

| Begin of Line | Home      | Move the cursor to column 1 in the current line                                                 |

| End of Line   | End       | Move the cursor behind the last character in the line.                                          |

| Begin of Text | Ctrl-Home | Moves the cursor to row 1, column 1 in the editor window.                                       |

| End of Text   | Ctrl-End  | Moves the cursor behind the last character of the text in the editor.                           |

| Tab           | Tab       | Moves cursor to the next tab position. The tab position can be set in the configuration dialog. |

#### 4.3 The Menus

The SX editor menu bar contains four menus: *File, Edit, Run* and *Help*. These menus and their associated menu items are each described below. The most important functions can be also selected with one of the shortcut buttons in the tool bar that are also shown below. You will find details to some of the functions that can be selected via the menus later in this manual.

#### 4.3.1 The File Menu

New

Creates a new, empty edit window. Use this item to start a new source code editing session. You may also click the shortcut button to create a new file. When you start the editor software, a blank session will be opened automatically, called "Blank 1".

When you select "New" while another editing session is already open, it will be moved to the "background" but it will still remain open. The open files list to the left displays the names of all open sessions.

Opens a browse window to locate and load source code files. As an alternative, click the shortcut button, or type Ctrl-O to open an existing file.

Again, if there is another session already open, it will be moved to the background.

The names of all currently open files are listed in the open files list to the left of the editor window. To switch between the sessions, left-click on the name of the file you want to see in the foreground.

Open...

Closes the source code file currently displayed in the editor window. You may

also right-click on the file name in the open files list, and then left-click on the

prompt that is displayed to close a file.

When the file to be closed has been modified since the last save, a dialog box will open allowing you to select whether or not to save the file or abort the close

operation; i.e. keep the file open in the editor.

Save Saves the source code file currently displayed in the editor window. The shortcut

button or Ctrl-S can also be used to save the file.

Save As... Opens a Save As dialog box to save the source code currently displayed in the

editor window with a designated name.

Reopen Displays a list of the files that were most recently edited. You may then click on

one of the list items to open any of these files directly.

*Print...* Opens a print dialog box to print the source code currently displayed in the

editor window.

Exit Terminates the SX-Key/Blitz editor.

4.3.2 The Edit Menu

Undo This menu selection remains inactive until you make a change to the text in the

editor window. You can then revert the recent changes you have made to the

text. Ctrl-Z also activates the Undo function.

Redo This is the opposite of the Undo function. It allows you to restore any changes

that were reverted by previous Undo actions. This selection remains inactive until you have used the Undo function at least once. Ctrl-Y also does a redo.

After you have re-done an operation, you may undo it again.

Cuts the selected text from the editor window and stores it in the Windows

clipboard. Ctrl-X is the equivalent keyboard entry.

To select text, use one of the standard Windows methods, like moving the mouse pointer across the text to be marked with the left mouse button pressed, or move

the cursor with the cursor keys while the Shift key is held down.

In order to select complete lines in the text, move the mouse cursor to the left margin of the text area until it turns into an arrow, and then click the left mouse button. To mark two or more lines, mark the first line, and then drag the mouse

up or down.

Copy Copies the selected text from the editor window and stores it in the Windows

clipboard. Ctrl-C is the equivalent keyboard entry.

Paste Pastes the text from the Windows clipboard into the editor window starting at

the current cursor location. Alternatively, type Ctrl-V to paste text.

Find Opens the Find dialog box. Ctrl-F is the shortcut key for this function. Enter the

text (or part of it) you are looking for. If necessary, you may select the options to search for whole words only, or to match upper- and lower-case characters. You can also specify the search direction, i.e. if the search shall be performed begin-

ning at the current cursor position towards the beginning or end of the text.

Find Next Finds the next occurrence of the specified text from the most recent Find

operation. F3 also performs this function.

Find/Replace... Opens the standard Windows replace dialog box. Ctrl-H is the shortcut key for

this function. Again, you have the options to search for whole words only, or to

match upper- and lower-case characters.

Go to Line Number Opens a dialog box where you can enter a line number. Ctrl-G is the shortcut key

for this function. Click "Ok" to close the dialog, and to position the cursor to

column 1 in the specified line.

Clear Errors When errors are encountered while assembling a source code file with the "new"

default SASM assembler, the lines with errors are highlighted, and the errors found are displayed in the status area. Use this menu selection to clear all error

information.

#### 4.3.3 The Run Menu

Assemble

Assembles the code. You may also press Ctrl-A, or click the shortcut button to start the assembly. When the code in the editor window could be assembled without errors, the message "Assembly Successful" will show up in the status bar.

When you use the default "new" SASM assembler and if there are any errors encountered in the code, a message box will open, telling you that errors were found. Click "Ok" to close the box. At the bottom of the editor window, you will notice a new area that contains a list of all errors found during assembly. The first error message line is highlighted, and the offending line in the source code is also automatically highlighted.

When there are two or more error lines, double-click on a line in order to jump to the offending line in the source code.

Make the necessary corrections to the source code, and assemble the code again, until no more errors are reported.

The assembler may also generate warning messages that are shown in the same area, together with any errors. With warnings, the code will be assembled, but it is a good idea to make the necessary corrections to the source code in order to avoid warnings.

*NOTE:* Before assembly, the current file will be saved automatically. If you have entered code into a new blank editor window, use the Save function to save the window contents under a specific name before starting the assembler.

Assembles the source code and programs the SX microcontroller (when the assembly was successful). Ctrl-P also starts programming.

Program

Run

Assembles the source code, programs the SX and generates a clock signal. Ctrl-R also runs a program.

Debug

Assembles the source code, programs the SX, generates a clock signal and initiates the debug mode. (Not used on the SX-Blitz). Ctrl-D also starts the debugging mode.

Debug (reenter)

Assembles the source code, assumes that the SX device is already programmed with the recent code to be debugged (i.e. does not program the SX again), generates a clock signal and enters the debug mode. (Not used on the SX-Blitz). Ctrl-Alt-D also re-enters the debugger.

This option is handy when you have previously terminated a debug session that you want to continue later without having made changes to the source code in the meantime.

As long as you add, remove or change WATCH or BREAK directives in the source code, you may still use this function to reenter the debugging session without downloading the program to the SX.

Any other changes to the source code require a new download, i.e. you must use the Debug option instead, to start the debugger.

View List Assembles the source code, and then opens another window that shows the

contents of the list file generated by the assembler. Ctrl-L also displays the list file. The list file will be described in detail later in this manual (see **Chapter 7.10** –

Files Created by SASM).

Clock... Opens the clock control dialog box to allow the modification of the clock activity

and frequency. (Not used on the SX-Blitz). Ctrl-K also opens the clock dialog. With this function, the SX device's clock is supplied by the SX-Key, and you may

test the functionality of an application at various clock rates.

Device... Opens the device dialog box to allow modification of the SX microcontroller pa-

rameters. Ctrl-I also opens the device dialog box.

Configure... Opens the configuration dialog box to allow modification of the SX-Key/Blitz

programming interface. See **Chapter 4.4.5 – Configure Window** for configuration

details. Ctrl-U also performs this operation.

4.3.4 The Help Menu

Contents Displays information on how to use the WATCH and BREAK directives.

About Displays the SX-Key/Blitz Development System information box.

#### 4.4 The Windows

Many menu items open up a separate window for further configuration or monitoring. These windows are described below.

#### 4.4.1 Print Window

The print window is accessed via the Print... item on the File menu. It is the standard Windows Print dialog box that you know from other applications. It allows you to select which printer shall be used, and depending on the printer type, various options can be selected.

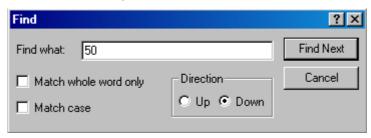

#### 4.4.2 Find Window

Figure 7 - The Find Window

The Find window is accessed via the Find item on the Edit menu. Enter the text to be searched for in the "Find what" field. By default, the search direction is from the current cursor position to the bottom of the text. You may change this direction by clicking the "Up" radio button in the "Direction" group.

You may also specify if the search shall match whole words only and if upper/lower case characters shall be distinguished.

Click the "Find Next" button to start the search. When the pattern you have entered was found in the text, it will be highlighted.

Clicking "Find Next" again continues the search, and the next match will be selected in the text (if any). The Find window remains open, until you click the "Cancel" button.

After you have closed the Find window, you may still continue searching for the pattern most recently entered by selecting "Find Next" in the Edit menu, or simply hit the F3 key to continue the search.

#### 4.4.3 Find/Replace Window

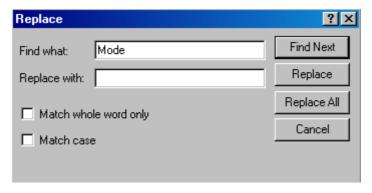

Figure 8 - The Find/Replace Window

This window is similar to the Find window. Again, you can enter the text pattern to be searched for. In addition, you also can enter the replacement text.

Also, you may select if only whole words should be found and if the search shall be case-sensitive, or not.

Click the "Find Next" button to start the first search. When the pattern was found, it will be highlighted in the text.

Click the "Replace" button to replace the highlighted text with the replacement you have entered, or click "Find Next" to not alter the text, and to continue the search for the next matching pattern in the text.

When wish to replace all occurrences of the search pattern, click the "Replace All" button. You should use the replace all feature with extra caution because it replaces the search pattern in the whole text without further confirmation. You might consider activating the "whole words only" option to avoid unwanted replacements. Also note that "Replace All" always performs the search from the top of the text down to the bottom, where the find next always continues towards the bottom of the text.

#### 4.4.4 Goto Line Number Window

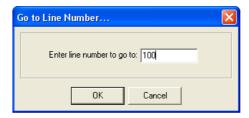

Figure 9 - The Goto Line Number Window

This window is accessed via the Goto Line Number item on the Edit menu. Enter the line number where the cursor shall be positioned and click Ok. If necessary, the text in the editor window will be scrolled so that the line you have addressed will be visible and the cursor is placed in column 1 of this line.

#### 4.4.5 Configure Window

Figure 10 - The Configure Window

This window is accessed via the Configure item on the Run menu and allows you to setup various properties of the software.

We have already addressed the *Serial Port* section at the top of the window. Click one of the radio buttons to select the COM port where your SX-Key/Blitz is connected.

When the option *Create backup (.bak) files* is selected, the editor will save a copy of the previous version whenever a modified source code file is saved.

The group Assembler Options allows you to configure the SASM assembler.

When *Use SASM* is selected, the editor will call SASM to translate the source code in the editor window into SX machine code. SASM is an enhanced version of Ubicom's SASM assembler that has been adapted to the SX-Key Version 2 software. When you un-check this option, the original Parallax assembler will be invoked instead. Because there are some differences in language syntax between the two assemblers, it might be necessary to use the Parallax Assembler with older, legacy, source code (see **Chapter 7 – The SASM Assembler** and **Chapter 8 – The Parallax Assembler** for the differences between the assemblers).

Nevertheless, we strongly recommend that you use the SASM assembler for all new, or recently revised, source code. There are only a few modifications necessary to make legacy source code compatible with SASM (see Chapter 9 – Upgrading Existing Code for SASM).

When you choose to use the Parallax Assembler, by un-checking the "Use SASM" box, you will notice that a new group is shown at the top of the Options window, called *IRC Calibration*. Since the Parallax Assembler does not accept directives in the source code to set the value for IRC calibration, it is necessary to do this "outside" of the source code (see **Chapter 15.6.1.3 – Internal RC Mode** for details on IRC calibration).

When the option *SASM files to "SASM Output dir"* is selected, the files generated by SASM will be stored in the folder named "SASM Output" that is located in the folder where the SX-Key software has been installed. When the option is de-selected, the files will be stored in the folder where the source code files are located. See **Chapter 7.10 – Files Generated by SASM** for an explanation of the output files generated by SASM.

The option *Local Labels Must Start In Col. 1* controls how SASM searches the source code for local labels (see **Chapter 7.6 - Labels** for more details on local labels). When the option is selected, local labels must start in the first column of a source code line. Otherwise, local labels may be indented.

When the *Use New Editor* option is un-checked, the text editor will change its style into the editor format that was part of earlier versions of the SX-Key software. As this "old" editor has much less features, it is recommended to always use the "new" editor. You will notice that the remaining selections in the Configure window will become invisible when you select the "old" editor.

The Enhanced Editor Options group contains various selections that allow you to configure the "new" editor.

Use the upper left and right arrow buttons to change the *Font size* of the text displayed in the editor window between 6 and 32 points.

The left and right arrow buttons below let you define the *Tab size*, i.e. by how many columns text shall be indented on TAB characters in the text (2, 4, 6, or 8 columns).

When *Colored Code Keywords* is checked, the editor will perform "syntax highlighting", i.e. keywords in the source code text are displayed in color. Click on the colored button to the right of this option to open the Color dialog box. Here you can select the color that shall be used to highlight the keywords.

The *Boldface Code Keywords* gives you the option to let the editor display keywords in boldface. Boldfacing and color highlighting may also be combined.

When the *Colored Comments* option is checked, any comments in the source code text, i.e. text that starts with a semicolon, will be displayed in the color indicated to the right of this option. The color can be changed by clicking on the colored button.

The next option, *Error BG Color*, allows you to select the background color that shall be used to highlight any lines with errors after assembly. Again, click on the colored button to open the Color dialog box.

When the *Jump To Assembly Error Line* option is checked, the cursor will be positioned on the first line in the source code text after assembly, when errors were encountered. In addition, this line will be highlighted with the background color you have selected for the previous option.

After you have selected the required options, click "Okay" to accept them and to close the Configure window. Click "Cancel" instead, when you want to keep the options unchanged.

### 5 The SX-Key Debugger

The following is required to use the debug features:

- SX-Key Rev. E (or greater) The SX-Blitz cannot be used for debugging.

- SX chip date code 9825 or later.

- No external clock source connected to the SX chip. This includes oscillator packs, crystals, resonators and RC circuits.

- The SX-Key connected to the 4-pin programming header of the SX system to be debugged.

- The SX system must be powered.

Source code to be debugged must include the RESET directive (see Chapter 7.3.21), must have WATCHDOG set to off, and must have 2 free words in the first page of code and 136 free words near the end of the last page of code (from 177 to 1FE, 377 to 3FE, 577 to 5FE, 777 to 7FE, 977 to 9FE, B77 to BFE, D77 to DFE, F77 to FFE), depending on the number of E²Flash pages. If an oscillator frequency of other than 50 MHz (the default) is desired, the source code should contain a FREQ directive (see Chapter 7.3.9) stating the frequency. When the FREQ directive is missing, the assembler will generate a warning message, indicating that 50 MHz is used by default.

NOTE: On some machines, it is necessary to close background software (graphics, screen savers, etc.), for proper operation of the DEBUG windows.

In order to invoke the debugger, select "Debug" from the "Run" menu, press Ctrl-D, or click the debug shortcut button in the tool bar.

The source code that is currently displayed in the editor window will be assembled, and if no errors were found, the program is automatically transferred into the program memory of the SX device.

If the transfer was successful, and if an IRC Calibration setting of 4 MHz was chosen, a small window with IRC information is displayed. You may ignore this information for now, and click "Okay" to close the window (see **Chapter 15.6.1.3 – Internal RC Mode** for details on IRC calibration).

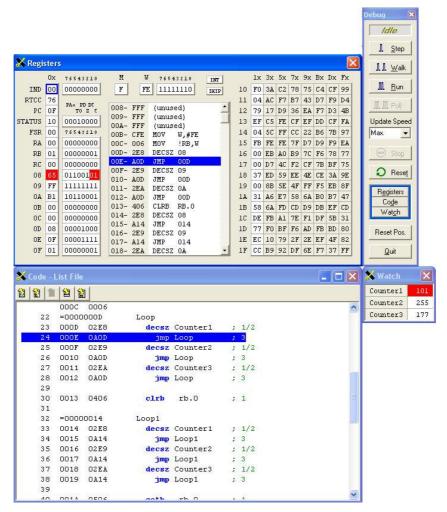

Next, the debugger will start, and the windows will be displayed as shown in **Figure 11 – The Debugger Windows**.

### 5.1 The Debugger Windows

#### 5.1.1 The Registers Window

This window contains all the data and describes the current state of the SX chip. The leftmost column within the Registers window displays the hexadecimal contents of global registers \$00 through \$0F.

### 5 The SX-Key Debugger

Registers \$10 through \$1F of all other banks are shown in the columns on the far right of the window. The bank offsets are labeled at the top of each column and the current bank is highlighted in white. These columns will expand or contract to fit the number of RAM banks available in the SX. In this example, eight banks are shown.

The blue outline, shown here on the IND register, indicates the location that the FSR (file select register) is currently pointing at.

The second column, just to the right of the first sixteen registers, displays a binary representation of some of the registers, namely IND, Status, RA, RB, RC and 08 through 0F.

At the top center of the Registers window are the contents of the M register (hexadecimal) and the W register (both hexadecimal and binary) and the Interrupt and Skip flags. The Interrupt and Skip flags turn blue when set and white when cleared. The interrupt flag is set when an interrupt has occurred and cleared after the interrupt has been serviced. The Skip flag is set when the compare condition evaluates to true, i.e. when the skip will be performed. It is cleared when the condition evaluates to false, or after the skip has been performed.

Figure 11 - The Debugger Windows

The assembly code box under the M and W register display in the center of the Registers window lists several contiguous instructions at once. The first three digits on each line is the hexadecimal address in program memory, followed by the opcode and finally the assembly mnemonic and operand(s). This window normally shows the active section of code, around which the program counter (PC) points, however, the scroll bar allows movement of the window's field of view to any section of code.

### 5 The SX-Key Debugger

#### 5.1.2 The Debug Window

The Debug window contains buttons for debugging functions. Each button has an associated shortcut key, as described in **Table 2 – Debugger Buttons and Shortcut Keys**, below.

- The Step button (or Alt-S) will execute one machine instruction and update all registers.

- The *Walk* button (or Alt-W) will execute one machine instruction after another in "slow motion", updating the display automatically and continuing until the Stop button is pressed, or a breakpoint is encountered. The delay time between instruction executions can be selected from the *Update Speed* drop-down list; with the range being from 1 (about one second) to Max (as fast as the computer can process it).

- The *Run* button (or Alt-R) will initiate a full-speed execution of the program, and will continue until a breakpoint is hit or the Stop or Reset buttons are pressed. The displayed registers will not update until the Poll button is pressed or execution is stopped.

- The *Poll* button (or Alt-L) operates in one of two modes. If a breakpoint exists, the Poll button runs the code at full speed halting execution at the break just long enough to update the display and then continues running. If a breakpoint is not set, the Poll button can be pressed only during run mode to get an instant update of the register displays.

- The *Stop* button (or Alt-P) halts execution of a walk, run or poll operation and updates the display.

- The *Reset* button (or Alt-T) returns the SX chip to its initial state and sets the program counter (PC) to the location containing the reset vector.

- The *Registers, Code* and *Watch* buttons (or Alt-E, Alt-D, Alt-C) bring the associated windows into view if they were hidden. (The Debug window always stays on top).

- The *Reset Pos.* button brings all windows into view, places them at their default positions, and resizes them to the defaults.

- The Quit button (or Alt-Q) closes the Debug windows and exits debug mode.

| Button     | Shortcut | Function                                                                               |

|------------|----------|----------------------------------------------------------------------------------------|

| Step       | Alt-S    | Executes one machine instruction.                                                      |

| Walk       | Alt-W    | Executes multiple machine instructions in "slow motion".                               |

| Run        | Alt-R    | Executes instructions in full speed.                                                   |

| Poll       | Alt-L    | Updates display then continues execution. Can be used synchronously or asynchronously. |

| Stop       | Alt-P    | Halts execution of a walk or run operation.                                            |

| Reset      | Alt-T    | Resets the SX chip.                                                                    |

| Registers  | Alt-E    | Brings Registers window into view.                                                     |

| Code       | Alt-D    | Brings Code window into view.                                                          |

| Watch      | Alt-C    | Brings Watch window into view.                                                         |

| Reset Pos. | none     | Resets all debugger windows to their defaults.                                         |

| Quit       | Alt-Q    | Closes the Debug Windows and exits debug mode.                                         |

Table 2 - Debugger Buttons and Shortcut Keys

The Debug windows are highly active and interactive displays. Every time the display is updated (after a step, walk, poll or stop operation), each register that was modified since the previous update is highlighted in red. This provides a clear indication of what the last instruction accomplished. Similarly, each bit that was changed is marked in red within all registers shown in binary. Additionally, the assembly code box and Code window highlights the instruction pointed to by the program counter (PC) in blue, and a breakpoint in red.

#### 5.1.3 The Watch Window

The Watch window displays the contents of selected registers in a user-defined format. The values in the Watch window can be modified using the same methods described in **Section 5.1.5 – Modifying registers during debugging**, below. In addition, the numerical values in the Watch window can be modified in any format (binary, hexadecimal or decimal) regardless of the displayed format. Simply precede the input value with a %, \$, or nothing, respectively. String values can only be modified by entering new strings. See the Watch directive section in **Chapter 7.3.23 – The Watch Directive** for information of defining watches.

#### 5.1.4 The Code/List File Window

This window displays the contents of the list file generated by the assembler (see **Chapter 7.10 – Files Created by SASM** for more information about the list file). While a program is executed in single steps, or in walk mode, the instruction that is currently executed is highlighted with a blue background.

If a breakpoint is defined, this line is highlighted with a red background.

The Code/List File window has a toolbar with several shortcut buttons. These buttons have the following meanings:

### 5 The SX-Key Debugger

*Jump to Code:* Scrolls the window to display the first line that assembles into CPU instructions.

*Jump to Reset Line:* Scrolls the window to display the line of code that will be executed upon reset. This line will be highlighted blue.

*Jump to Breakpoint:* Scrolls the window to display the line with the breakpoint. This line will be highlighted red. When no breakpoint is defined, this button is inactive.

*Jump to "Next Run" Line:* Scrolls the window to display the next line of code that will be executed. The line will be highlighted blue.

Jump to Main: Scrolls the window to display the label called "Main", if there is one.

#### 5.1.5 Modifying registers during debugging

Any register, bits within registers, or flags can be modified using the mouse and keyboard (see **Table 3** – **Register Editing Keys** for a summary of the editing keys). To modify a register (in hexadecimal), first click on it or use the tab and cursor keys to move the focus to that register. (The focus is indicated by a blinking, black highlight within the register). Next, type in the new hexadecimal value on the keyboard and press the enter, space, backspace or arrow keys to write the value to the register. The new value will appear in the selected register, highlighted in red to indicate a change.

To change a bit or flag in the binary registers, simply click the mouse on the appropriate bit. The bit will toggle to the opposite state and will be highlighted in red to indicate a change. Click on the INT or SKIP flags to toggle their state. The INT and SKIP flags, unlike registers, do not indicate a change with a red highlight. Instead, a blue color indicates the flag is set, while a white color indicates the flag is cleared.

If a register's contents are changed by accident, press the ESC (escape) key to restore its previous value.

| Key                                                                              | Function                                                                                                                                                                |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAB Move focus to new control block and ignore any changes to previous register. |                                                                                                                                                                         |

| Cursor Keys                                                                      | Move focus to new register within control and write any changes to previous register.                                                                                   |

| Space                                                                            | Same as cursor down.                                                                                                                                                    |

| Backspace                                                                        | Same as cursor up.                                                                                                                                                      |

| Enter                                                                            | Write changes to register.                                                                                                                                              |

| ESC                                                                              | Changes register value to previous value, if it has been changed by the user. This will not work if the enter, space, backspace or cursor keys have been pressed first. |

Table 3 – Register Editing Keys

### 5.1.6 Breakpoints and the Current Instruction

The assembly code box and Code/List File window display a breakpoint as a red highlighted line and the next instruction to be executed as a blue highlighted line.

The breakpoint can be set to a new line by clicking the mouse button once on the desired line in either the assembly code box, or in the Code/List File window. Clicking the mouse button again will remove the breakpoint. Only one breakpoint can be set at a time.

### 5.1.7 Setting the Program Counter

The next instruction to execute can be set to a new line by double-clicking the mouse button on the desired line in the assembly code box or the Code/List File window. Additionally, the program counter (PC) register's contents can be manually modified via the keyboard to set the next instruction to execute.

If a breakpoint and the program counter should both be on the same line, it will become multicolored. The first third of the line will be highlighted in red (to indicate the breakpoint) and the last two thirds of the line will be highlighted in blue (to indicate the next line to execute).

| 5 The SX-Key Debugger |  |  |

|-----------------------|--|--|

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

|                       |  |  |

### 6 The Device Window

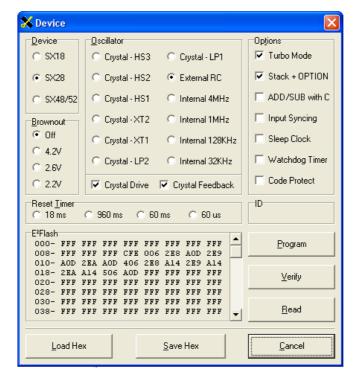

The Device window is accessed via the Device item on the Run menu, or by pressing Ctrl-I. You may also click the Device shortcut button in the editor's toolbar. This window allows you to specify all the device settings for the SX microcontroller you are using, program and verify or read the contents of the device and load or save object files for the SX.

Figure 12 - The Device Window

All data shown in this window reflect the settings specified in the DEVICE line(s) of the source code (if it had been assembled just before opening this window), the settings in the loaded object code or the settings read out of the device itself. You may modify these settings manually and program or reprogram the chip, however, those modifications will not be reflected in the source code.

The *Device* section (SX18, SX28 or SX48/52) should be set to the SX microcontroller that is currently used. It is important to make this selection first because depending on the device selected, some other options become active or inactive.

## 6 The Device Window

*NOTE:* To select an SX20 device, click on the SX18 selection. SX18 devices are no longer manufactured by Ubicom

The *Oscillator* section specifies the fuse settings for the various clock sources, and oscillator modes that are available in the SX devices, similar to the directives that can be given in the source code. Please note that any fuse settings defined in the source code will be overwritten by the options selected here when the SX controller is programmed from the Device window. See **Table 4 - SX Clock Options**, below, for a summary of the available clock options.

| Setting                 | Description                                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| HS13<br>XT12<br>LP12    | Specifies the oscillator drive capacity for high speed, medium speed crystal/resonator, and low power crystal/resonator clocks. |

| External RC             | Specifies special drive for external resistor-capacitor clock circuits.                                                         |

| Internal<br>32 KHz4 MHz | Specifies internal clock at indicated frequency.                                                                                |

**Table 4 - SX Clock Options**

In the *Brownout* section, you can specify the threshold voltage for a brownout reset or you may also turn off brownout detection completely.

The *Reset Timer* section (SX48/52 devices only) should be set to the desired reset delay. The reset delay is the amount of time the SX48/52 waits after a reset condition before executing the first program instruction. This setting is useful for enabling a faster response after a sleep operation. It is critical to test this with your final circuit since the reset delay is intended to make sure the external oscillator (crystal, resonator, R/C circuit, etc) is running and stabilized before the first instruction executes.

The *Options* section allows you to set various fuse options. *Turbo* mode and enhanced *Stack* + *OPTION* can only be selected for SX20/28 devices because SX48/52 devices always have these options active, whereas the *Sleep Clock* option can only be selected for SX48/52 devices.

When you activate the Code Protect feature, the contents of the SX chip (except for the ID) cannot be read back once it is programmed. Actually, when you read a code-protected device, meaningless data will be read back instead.

The ID and  $E^2Flash$  sections display the values contained in the ID and  $E^2Flash$  memory (the program memory) respectively.

The *Program* button initiates programming the SX chip with the assembled source code or the object code loaded into the Device window.

Use the *Verify* and *Read* buttons to verify the code in the SX against that shown in the Device window or to simply read the SX's code into the Device window. These options are valuable should the code in an SX chip be questionable or unknown. Note that verifies will fail and reads will not reveal the true code

or fuse settings if the SX chip was programmed with the code-protect fuse on. The ID field will always read properly, however.