DESCRIPTION

MP7751 is an analog input Class D Audio Amplifier which can drive stereo speakers in bridge-tied-load configuration. It is one of MPS' products of fully integrated audio amplifiers which dramatically reduce solution size by integrating the following:

$240m\Omega$  power MOSFETs

Startup / Shutdown pop elimination

Short circuit protection circuits

Advanced EMI performance

The MP7751 utilizes a stereo BTL structure capable of delivering 20W per channel into  $8\Omega$  speakers at 18V power supply. MPS Class D Audio Amplifiers exhibit the high fidelity of a Class AB amplifier at high efficiencies.

The MP7751 includes an internal circuit which allows the system automatic shutdown after the absence of the audio signal. This feature is used for energy-using products and for battery operated applications.

It also has an adjustable power limit function. The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to fixed maximum value. This limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC.

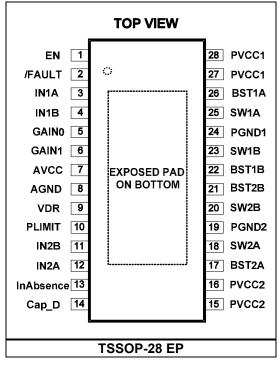

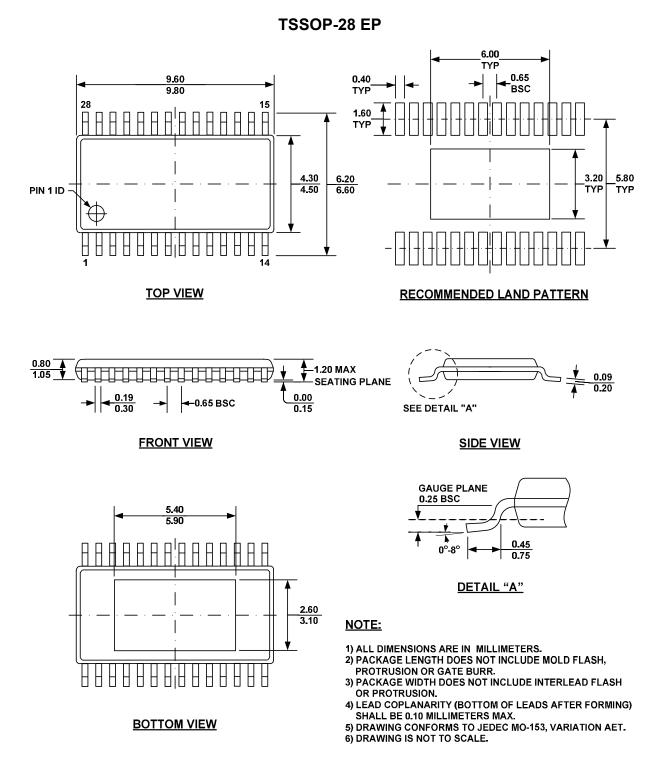

The MP7751 is available in TSSOP-28 EP package.

### **FEATURES**

- 5V to 26V Operation from a Single Supply

- $\pm$  5A Peak Current Output

- Output Power: 9.5W/channel at 12V, 8Ω Load, 10%THD 15W/Channel at 16V, 8Ω Load, 10%THD 20W/Channel at 18V, 8Ω Load, 10%THD

- 92% Efficiency with 8Ω Load, 10%THD, 1kHz, 12V Supply Voltage

- 240mΩ power MOSFETs

- Startup / Shutdown pop elimination

- Short circuit protection circuits

- Advanced EMI performance

- All Switches Current limited

- Internal Under Voltage Protection

- Internal Thermal Protection

- TSSOP-28 EP package

- Adjustable power limiter

- Automatic shutdown with zero input signal detect

- Fault Output Flag

## APPLICATIONS

- TV

- DVD Receiver

- Active Speaker

- Home Theaters

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

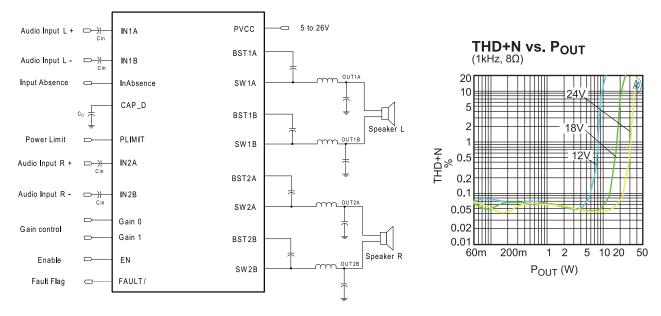

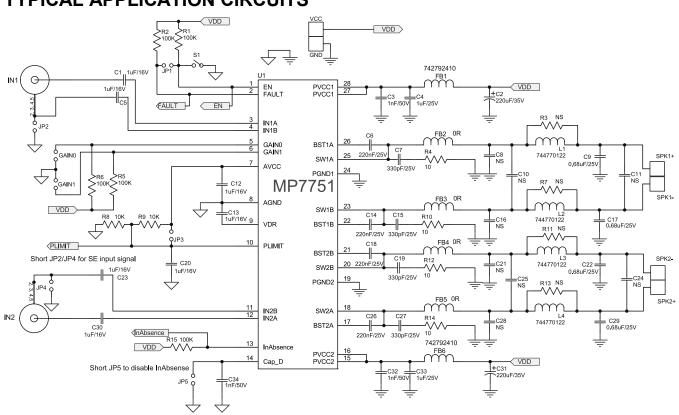

## **TYPICAL APPLICATION**

| Part Number* | Package     | Top Marking |  |  |

|--------------|-------------|-------------|--|--|

| MP7751GF     | TSSOP-28 EP | MP7751      |  |  |

### **ORDERING INFORMATION**

\* For Tape & Reel, add suffix –Z (e.g. MP7751GF–Z)

## PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$     |

|-----------------------------------------------------------|

| AGND to PGND $-0.3V$ to $+0.3V$                           |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ |

|                                                           |

| Junction Temperature                                      |

| Storage Temperature65°C to +150°C                         |

### Recommended Operating Conditions <sup>(3)</sup>

Thermal Resistance $\boldsymbol{\theta}_{JA}$  $\boldsymbol{\theta}_{JC}$ TSSOP-28 EP326°C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## ELECTRICAL CHARACTERISTICS (5,6)

| Parameters Symbol Condition              |                    | Condition                                          | Min | Тур  | Max | Units |  |

|------------------------------------------|--------------------|----------------------------------------------------|-----|------|-----|-------|--|

| Standby Current                          | I <sub>QSTBY</sub> | V <sub>EN</sub> = 0V,NIN=PIN=Float                 |     | 130  | 200 | μA    |  |

| Quiescent Current                        | Ι <sub>Q</sub>     | $V_{EN}$ = 5V, no load, no LC filter               |     | 20   | 40  | mA    |  |

| Output Offset Voltage                    | V <sub>os</sub>    | $V_i = 0 V$ , Gain = 36 dB,<br>$T_j = 25^{\circ}C$ |     | 20   | 65  | mV    |  |

| SW On Resistance                         | R <sub>dsON</sub>  | I <sub>O</sub> = 500mA, T <sub>i</sub> = 25°C      |     | 0.24 |     | Ω     |  |

| Short Circuit Current                    |                    | Sourcing and Sinking, $T_j = 25^{\circ}C$          | 4   | 5    | 6   | A     |  |

|                                          |                    | GAIN0 = L, GAIN1 = L                               | 19  | 20   | 21  |       |  |

| Closed Loop Cain                         | G                  | GAIN0 = H, GAIN1 = L                               | 25  | 26   | 27  |       |  |

| Closed Loop Gain                         | G                  | GAIN0 = L, GAIN1 = H                               | 31  | 32   | 33  | 33 dB |  |

|                                          |                    | GAIN0 = H, GAIN1 = H                               |     |      | 37  | 1     |  |

| EN Enable Threshold Voltage              |                    | V <sub>EN</sub> Rising                             |     | 1.3  | 2.0 | V     |  |

| EN ENABle Threshold Voltage              |                    | V <sub>EN</sub> Falling                            | 0.4 | 0.9  |     | V     |  |

| EN Enable Input Current                  |                    | V <sub>EN</sub> = 5V                               |     | 12   | 25  | μA    |  |

| Under Voltage Protection                 |                    | V <sub>UVP</sub> Rising                            |     | 4.6  | 5   | V     |  |

| Bilder voltage Frotection                |                    | V <sub>UVP</sub> Falling                           | 4   | 4.3  |     | V     |  |

| AVCC Operating Voltage                   |                    |                                                    | 5   | 5.5  | 6   | V     |  |

| VDR Operating Voltage                    |                    |                                                    | 5   | 5.5  | 6   | V     |  |

| V <sub>INN/INP</sub> Common Mode Voltage |                    |                                                    | 2.3 | 2.5  | 2.7 | V     |  |

| CAINO/CAINA Threehold                    |                    | V <sub>GAIN</sub> Rising                           |     | 1.6  | 2   | V     |  |

| GAIN0/GAIN1 Threshold                    |                    | V <sub>GAIN</sub> Falling                          | 0.6 | 1.1  |     | V     |  |

| Turn-on Time                             | t <sub>on</sub>    |                                                    |     | 13   |     | ms    |  |

| Turn-off Time                            | t <sub>OFF</sub>   |                                                    |     | 0.2  |     | us    |  |

| Switching frequency                      |                    |                                                    | 260 | 325  | 360 | kHz   |  |

| Input signal absence sensitivity         |                    |                                                    | 2   | 5    | 8   | mV    |  |

| Thermal Shutdown Trip Point              |                    | T <sub>J</sub> Rising                              |     | 150  |     | °C    |  |

| Thermal Shutdown Hysteresis              |                    |                                                    |     | 20   |     | °C    |  |

### $V_{cc}$ = 24V, $V_{EN}$ = 5V, $T_j$ = -40°C to 125°C, unless otherwise noted.

Note:

5) The device is not guaranteed to function outside its operating rating.

6) Electrical Characteristics are for the IC only with no external components except bypass capacitors.

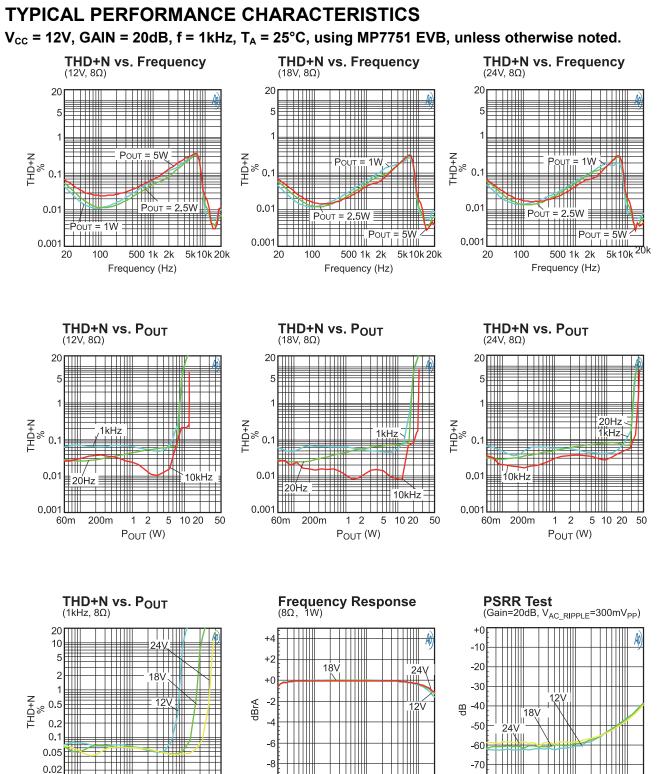

### **OPERATING SPECIFICATIONS**<sup>(7)</sup>

Circuit of figure 5,  $V_{CC}$  = 24V, Gain=20dB,  $V_{EN}$  = 5V,  $R_{LOAD}$  = 8 $\Omega$ ,  $T_A$  = +25°C, unless otherwise noted.

| Parameters             | Symbol | Condition                                                                  | Min                      | Тур  | Max  | Units |    |

|------------------------|--------|----------------------------------------------------------------------------|--------------------------|------|------|-------|----|

|                        |        | f = 1kHz, THD+N = $2$                                                      |                          | 36   |      |       |    |

| Power Output           |        | f = 1kHz, THD+N = 10%, V <sub>CC</sub> = 18V                               |                          |      | 20   |       | W  |

|                        |        | f = 1kHz, THD+N = 7                                                        |                          | 9.5  |      |       |    |

| THD+ Noise             |        | $P_{OUT} = 5W, f = 1kHz, V_{CC} = 12V$                                     |                          |      | 0.08 |       | %  |

|                        |        | P <sub>OUT</sub> = 18W, f = 1kH                                            | z, V <sub>CC</sub> = 24V |      | 0.08 |       | %  |

| Efficiency             |        | P <sub>OUT</sub> = 9.5W + 9.5W<br>V <sub>CC</sub> = 12 V, 1kHz, R          |                          | 92   |      | %     |    |

| Deadtime               |        | I <sub>0</sub> =0.5A                                                       |                          | 28   |      | nS    |    |

| Cross Talk             |        | V <sub>o</sub> = 1 Vrms, f = 217                                           |                          | -100 |      | dB    |    |

| Noise Floor            |        | A-Weighted, 22 Hz t                                                        |                          | 120  |      | μV    |    |

| Signal-to-noise ratio  |        | f = 1kHz, THD+N = 2                                                        |                          | -96  |      | dB    |    |

| Power Supply Rejection |        | V <sub>RIPPLE</sub> =200mV <sub>PP</sub> ,<br>Inputs ac-coupled<br>to AGND | f = 1kHz                 |      | -60  |       | dB |

|                        |        |                                                                            | f = 217Hz                |      | -60  |       | dB |

Note:

7) Operating Specifications are for the IC in Typical Application circuit. Not production tested.

0.01

I

60m

200m

2

1

P<sub>OUT</sub> (W)

5 10 20

50

500 1k 2k

Frequency (Hz)

5k10k20k

-10

20

100

#### MP7751 Rev. 1.0 5/23/2014

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2014 MPS. All Rights Reserved.

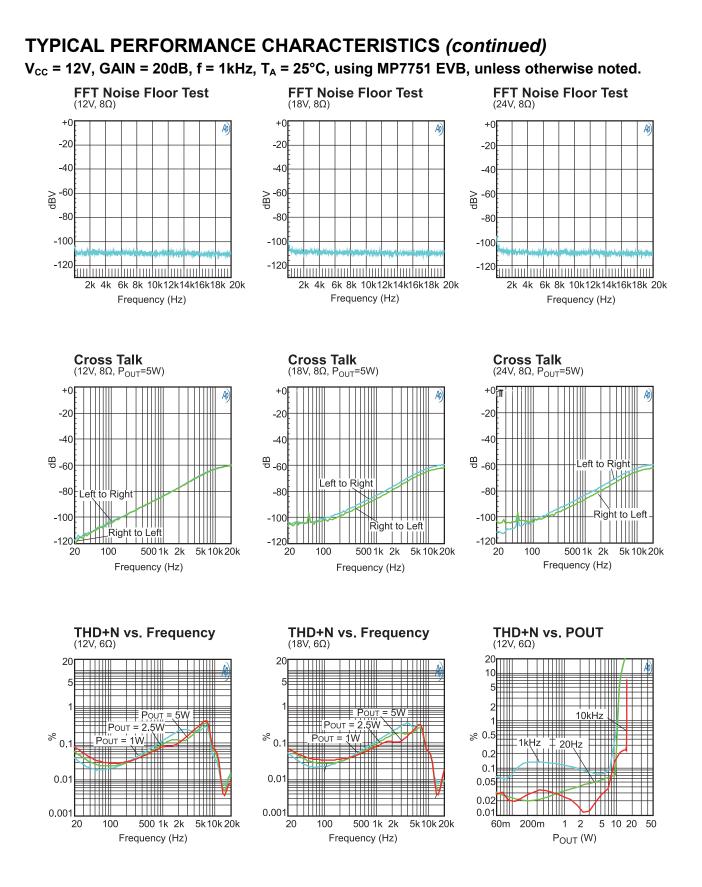

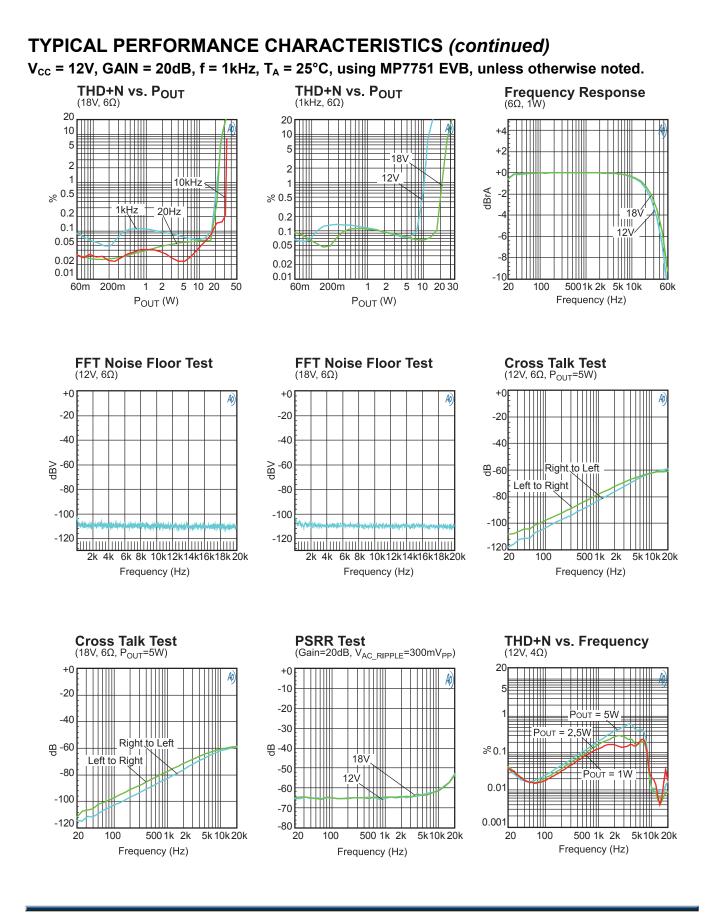

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

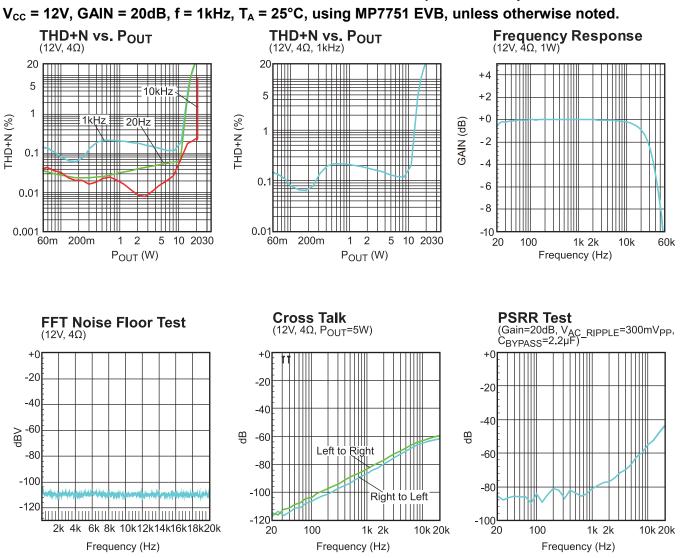

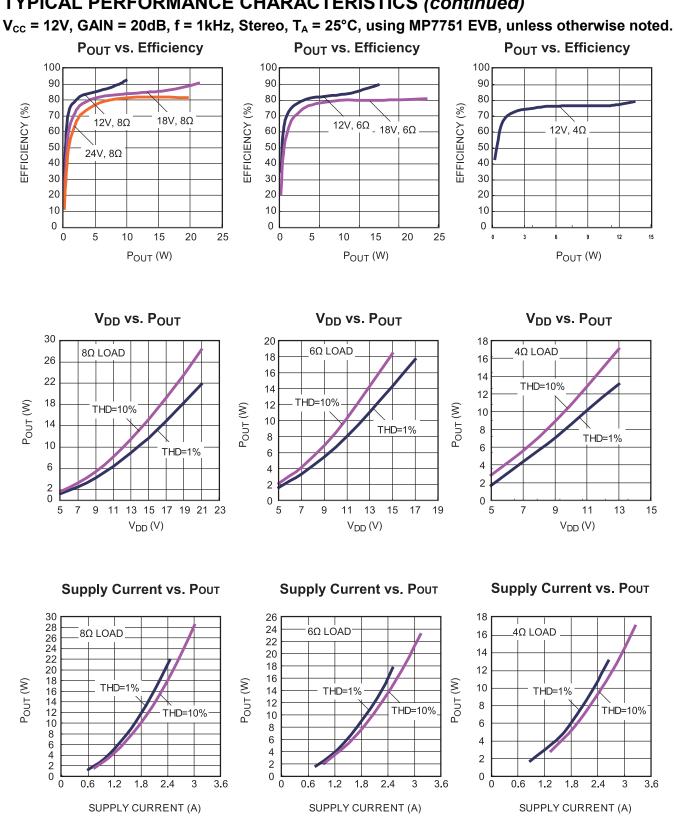

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

MP7751 Rev. 1.0 5/23/2014

## **PIN FUNCTIONS**

| Pin #  | Name      | Description                                                                                                                                                                                                     |  |  |  |  |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | EN        | Enable input. Drive EN high to turn on the Amplifier 1A/1B/2A/2B, low to turn them off.                                                                                                                         |  |  |  |  |

| 2      | /FAULT    | ault Output. A low output at FAULT indicates that the IC has detected an ove emperature or over current condition. This output is open drain.                                                                   |  |  |  |  |

| 3      | IN1A      | Positive audio input for channel 1. Biased at 2.5V.                                                                                                                                                             |  |  |  |  |

| 4      | IN1B      | egative audio input for channel 1. Biased at 2.5V.                                                                                                                                                              |  |  |  |  |

| 5      | GAIN0     | Gain selection bit.                                                                                                                                                                                             |  |  |  |  |

| 6      | GAIN1     | Gain selection bit.                                                                                                                                                                                             |  |  |  |  |

| 7      | AVCC      | Internal analog reference, 5.5V, need connect a bypass capacitor from AVCC to AGND.                                                                                                                             |  |  |  |  |

| 8      | AGND      | Analog ground.                                                                                                                                                                                                  |  |  |  |  |

| 9      | VDR       | Gate Drive Supply Bypass. VDR powers the internal circuitry, internal MOSFET gate drive. Bypass VDR to AGND with a $0.1\mu$ F to $10\mu$ F capacitor.                                                           |  |  |  |  |

| 10     | PLIMIT    | Power limit and anti-clipping feature control.<br>Connect a resistor divider from AVCC to GND to set power limit. Connect directly to<br>AVCC for no power limit.                                               |  |  |  |  |

| 11     | IN2B      | Negative audio input for channel 2. Biased at 2.5V.                                                                                                                                                             |  |  |  |  |

| 12     | IN2A      | Positive audio input for channel 2. Biased at 2.5V.                                                                                                                                                             |  |  |  |  |

| 13     | InAbsence | Open drain output used to report the input signal absence.                                                                                                                                                      |  |  |  |  |

| 14     | Cap_D     | Delay Time control for input signal absence report function. This holding time can be adjusted with external capacitor. Connect this pin to AGND to disable automatic shutdown with zero signal input function. |  |  |  |  |

| 15, 16 | PVCC2     | Power supply input for channel 2. Bypass PVCC2 to PGND2 with a $1\mu$ F X7R capacitor (in addition to the main bulk capacitor), placed close to the PVCC2 and PGND2 pins.                                       |  |  |  |  |

| 17     | BST2A     | High-side MOSFET bootstrap input for Amplifier 2A. A capacitor from BST2A to SW2A supplies the gate drive current to the internal high-side MOSFET.                                                             |  |  |  |  |

| 18     | SW2A      | Switched power output for Amplifier 2A (the positive output of channel 2).                                                                                                                                      |  |  |  |  |

| 19     | PGND2     | Power ground for Amplifier 2A/2B.                                                                                                                                                                               |  |  |  |  |

| 20     | SW2B      | Switched power output for Amplifier 2B (the negative output of channel 2).                                                                                                                                      |  |  |  |  |

| 21     | BST2B     | High-side MOSFET bootstrap input for Amplifier 2B. A capacitor from BST2B to SW2B supplies the gate drive current to the internal high-side MOSFET.                                                             |  |  |  |  |

| 22     | BST1B     | High-side MOSFET bootstrap input for Amplifier 1B. A capacitor from BST1B to SW <sup>2</sup> supplies the gate drive current to the internal high-side MOSFET.                                                  |  |  |  |  |

| 23     | SW1B      | Switched power output for Amplifier 1B (the negative output of channel 1).                                                                                                                                      |  |  |  |  |

| 24     | PGND1     | Power ground for Amplifier 1A/1B.                                                                                                                                                                               |  |  |  |  |

| 25     | SW1A      | Switched power output for Amplifier 1A (the positive output of channel 1).                                                                                                                                      |  |  |  |  |

| 26     | BST1A     | High-side MOSFET bootstrap input for Amplifier 1A. A capacitor from BST1A to SW1A supplies the gate drive current to the internal high-side MOSFET.                                                             |  |  |  |  |

| 27, 28 | PVCC1     | Power supply input for channel 1. Bypass PVCC1 to PGND1 with a 1µF X7R capacitor (ir addition to the main bulk capacitor), placed close to the PVCC1 and PGND1 pins.                                            |  |  |  |  |

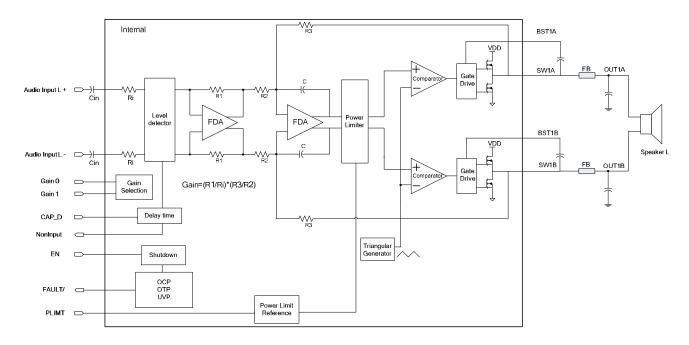

# FUNCTIONAL BLOCK DIAGRAM

Functional Block Diagram (only one channel)

## **OPERATION**

The MP7751 is a fully integrated Class D stereo BTL audio amplifier. Because of the switching Class D output stage, power dissipation in the amplifier is drastically reduced when compared to Class A, B or A/B amplifiers while maintaining high fidelity and low distortion.

The amplifier has fully differential outputs and inputs. The differential input is useful to minimize the common-mode noise (any noise that appears on both input lines of the channel). This device can still be used with a single-ended input.

MP7751 The includes eiaht high-power MOSFETs wherein for each half-bridge channel the output driver stage uses two N-Channel MOSFETs to deliver the pulses to the LC output filter which in turn drives the load. To fully enhance the high-side MOSFET, the gate is driven to a voltage higher than the source by the bootstrap capacitor between OUTxx and BSTxx pins. While the output is driven low, the bootstrap capacitor is charged from power supply through an internal circuit. The gate of the high-side MOSFET is driven high from the voltage at Bootstrap Supply, forcing the MOSFET gate to a voltage higher than power supply voltage and allowing the MOSFET to fully turn on, reducing power loss in the amplifier.

The gain of the MP7751 is set by the input terminals, GAIN0 and GAIN1. The actual gain settings are controlled by ratios of the input and feedback resistors

### **Enable Function**

The MP7751 EN input is an active high enable control. To enable the MP7751, drive EN with a 2.0V or higher voltage. To disable the amplifier, drive it below 0.4V. While the MP7751 is disabled, the PVCC operating current is around  $250\mu$ A and the output driver MOSFETs are turned off.

### Input signal Absence detect

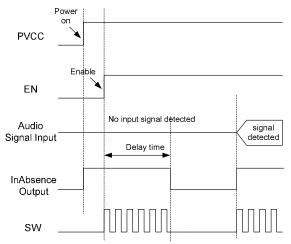

The MP7751 includes an internal circuit which allows the system automatic shutdown after the absence of the audio signal. This feature is used for energy-using products and for battery operated applications. The MP7751 includes a delay circuit which allows the IC continues to hold the flag after the absence of the audio signal. This holding time can be adjusted with external capacitor.

The input absence flag will be high initially when power on. After device enabled, the internal circuit start to detect the input signal. MP7751 will then hold the output report and normal operation for a delay time which can be adjusted by the Capacitor value @ pin 14. Then MP7751 will turn off the all MOSFETs and pull low the input absence output, until the input signal detected again.

#### Figure 1a: enable on with no signal detected

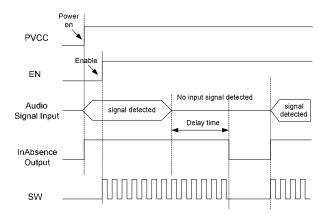

2. The input absence flag output will be or maintain high when input signal is detected. The delay circuit will only be activated when the input signal absence. MP7751 will then hold the output report for a delay time which can be adjusted by the Capacitor value @ pin 14. Then MP7751 will turn off the all MOSFETs and pull low the input absence output, until the input signal detected again.

Figure 1b: enable on with audio signal present

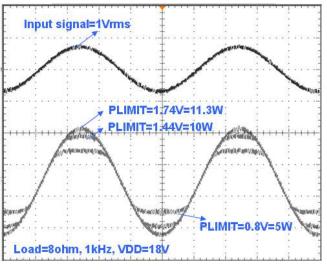

### Adjustable Power Limit

Power limit and anti-clipping feature control. The voltage at pin 10 can used to limit the power to levels below that which is possible based on the supply rail.

Connect a resistor divider from AVCC to GND to set power limit. Connect directly to AVCC for no power limit.

An external reference may also be used if tighter tolerance is required. Also add a  $1\mu$ F capacitor from pin 10 to ground.

Figure 2. PLIMT Circuit Operation)

The PLIMIT circuit sets a limit on the output peak-to-peak voltage. The limiting is done by limiting the duty cycle to fixed maximum value. This limit can be thought of as a "virtual" voltage rail which is lower than the supply connected to PVCC. This "virtual" rail is 8 times the voltage at the PLIMIT pin. This output voltage can be used to calculate the maximum output power for a given maximum input voltage and speaker impedance.

$$P_{\text{OUT}} = \frac{\left( \left( \frac{R_{\text{L}}}{R_{\text{L}} + 2 \times R_{\text{S}}} \right) \times V_{\text{P}} \right)^2}{2 \times R_{\text{L}}}$$

for unclipped power

Where:

${\sf R}_{\sf S}$  is the total output series resistance (including Rdson and the resistance of output filter.

$R_L$  is the load resistance.

$V_{\mathsf{P}}$  is the peak amplifier of the output voltage.  $V_{\mathsf{P}}$  = 8 x PLIMIT voltage if 8 x PLIMIT < PVCC And

$P_{\text{out}}$  @10%THD  $\approx$  1.25 × unclipped  $P_{\text{out}}$

Table 1: Power Limit Typical Operation

| Test<br>Condition                               | PLIMIT<br>Voltage | Output<br>Voltage<br>(Vp-p) | Output Power<br>(~10% THD) |

|-------------------------------------------------|-------------------|-----------------------------|----------------------------|

| VDD=12V,<br>Vin=1Vrms,<br>Load=8Ω,<br>Gain=20dB | 0.80V             | 14.9                        | 5.0W                       |

| VDD=18V,<br>Vin=1Vrms,<br>Load=8Ω,<br>Gain=20dB | 0.80V             | 14.9                        | 5.0W                       |

| VDD=18V,<br>Vin=1Vrms,<br>Load=8Ω,<br>Gain=20dB | 1.44V             | 23.6                        | 10.0W                      |

| VDD=24V,<br>Vin=1Vrms,<br>Load=8Ω,<br>Gain=20dB | 1.44V             | 23.6                        | 10.0W                      |

### **Gain Setting**

The gain of the MP7751 is set by the input terminals, GAIN0 and GAIN1. The actual gain settings are controlled by ratios of the internal input and feedback resistors, details please see the below table.

| GAIN0 | GAIN1 | Typ. GAIN<br>(dB) | Typ. Input Impedance<br>(kΩ) |

|-------|-------|-------------------|------------------------------|

| 0     | 0     | 20                | 75                           |

| 1     | 0     | 26                | 50                           |

| 0     | 1     | 32                | 30                           |

| 1     | 1     | 36                | 20                           |

#### Table 2: Gain Setting

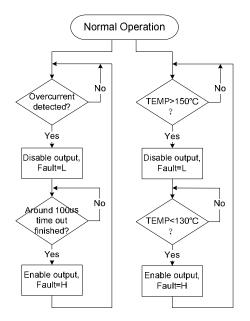

#### **Over-Temperature Shutdown**

Thermal monitoring is also integrated into the MP7751. If the die temperature rises above 150°C, all switches turn off. The temperature must fall below 130°C before normal operation resumes, with the same power-up sequence used to prevent popping noise.

#### **Short Circuit Performance**

The MP7751 has internal overload and short circuit protection. The currents in both the highside and low-side MOSFETs are measured. Upon detection of short circuit, all MOSFETs of the over current full bridge channel will go into high impedance for a fixed duration before resuming normal operation. After the fixed duration and the short circuit condition is removed, the MP7751 will restart with the start up sequence that is used for normal starting to prevent a pop from occurring.

### Fault Output

The MP7751 includes an open drain, active low fault indicator output on the /FAULT pin. A fault triggers if either the current limit or thermal shutdown is tripped.

A fault on any channel will cause the FAULTB pin to pull low. A fault on either channel will cause the all outputs to go into high impedance. When the fault goes away, the MP7751 will resume normal operation.

Figure 3: Fault Timing Chart

## APPLICATION INFORMATION COMPONENT SELECTION

**Delay time for input signal absence report** The Recovery time is defined as follows.

$$T_{delay} = 1.6 \times 10^8 \times C_{R} [sec]$$

### **Choosing the Output LC Filter**

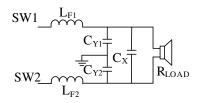

The inductor-capacitor (LC) filter converts the pulses at SW to the output voltage that drives the speaker. There are two kinds of LC filter structure depending on the output configuration.

Figure 4: BTL Filter Configuration

Where:

$$\begin{split} L_{F} &= L_{F1} + L_{F2} , \\ C_{F} &= C_{\chi} + \frac{C_{\gamma_{1}} \times C_{\gamma_{2}}}{C_{\gamma_{1}} + C_{\gamma_{2}}} , \\ L_{F1} &= L_{F2} ; \\ C_{\gamma_{1}} &= C_{\gamma_{2}} \end{split}$$

The characteristic frequency of the LC filter needs to be high enough to allow high frequency audio to the output, yet needs to be low enough to filter out high frequency products of the pulses from the SW pin. The characteristic frequency of the LC filter is:

$$\mathbf{f}_{0} = \frac{1}{2 \times \pi \times \sqrt{\mathbf{L}_{\mathsf{F}} \times \mathbf{C}_{\mathsf{F}}}}$$

The quality factor (Q) of the LC filter is important: If this is too low, output noise will increase; if this is too high, then peaking may occur at high frequencies and reduce the passband flatness. The circuit Q is set by the load resistance (speaker resistance, typically  $4\Omega$  or  $8\Omega$ ). Q is calculated as:

$$Q = \frac{R_{LOAD}}{\omega_0 \times L_F} = \frac{R_{LOAD}}{2\pi \times f_0 \times L_F}$$

$\omega_0$  is the characteristic frequency in radians/second and f<sub>0</sub> is in Hz. Use an LC filter with Q between 0.7 and 1.4.

The type of inductor and capacitor used in the LC filter greatly affects the output ripple and noise. Use a film capacitor and an inductor with sufficient power rating to supply the output current to the load. The inductor must exhibit soft saturation characteristics: If the inductor exhibits hard saturation, it should operate well below the saturation current. Use toroidal cores made of gapped ferrite, MPP, powdered iron, or similar materials. If using either an open or shielded bobbin ferrite core for multi-channel designs, make sure that the start windings of each inductor align (all starting toward the SW pin, or all starting toward the output) to prevent channel-to-channel crosstalk or other interference.

### Input Coupling Capacitor

The input coupling capacitor transmits the AC signal from the source to the MP7751 while blocking the DC voltage. Choose an input coupling capacitor such that the corner frequency ( $f_{\rm IN}$ ) is less than the passband frequency. The corner frequency is calculated as:

$$f_{IN} = \frac{1}{2 \times \pi \times R_{IN} \times C_{IN}}$$

The impedance of the input resister is different with the different gain setting. At the same gain setting, the input impedance from part-to-part may shift by  $\pm 20\%$  due to shifts in the actual resistance of the input resistors. But please note that the gain variation from part-to-part is small.

For design purposes, the input network should be designed assuming an input impedance of 16 k $\Omega$ , which is the absolute minimum input impedance of the MP7751. At the lower gain settings, the input impedance could increase as high as 90 k $\Omega$ .

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2014 MPS. All Rights Reserved.

### **Power Source**

For maximum output power, the amplifier circuit requires a regulated external power source. A high power-supply voltage can deliver more power to a given load resistance, but a power-source voltage exceeding the maximum voltage of 26V can damage the MP7751. The MP7751's power supply rejection is excellent, though power-supply noise can pass to the output, so care must be taken to minimize power supply noise within the pass-band frequencies. Bypass the power supply with a large capacitor (typically aluminum electrolytic) along with two smaller  $1\mu$ F and 1nF ceramic capacitors at the MP7751 VCC supply pins.

### PCB Layout

Circuit layout is critical for optimal performance, low output distortion, and noise. Duplicate the EVB layout for best results. For layout changes, follow these guidelines and use Figure 7 and Figure 8 as references.

1) Place the following components as close to the MP7751 as possible:

#### **Bootstrap Capacitors**

$C_{BS}$  supply the gate drive current to the internal HS-FET. Place  $C_{BS}$  as close to BST pin and SW pin as possible.

### Power Supply Bypass Capacitors

$C_{BYP}$  carry the transient current for the switching power stage. To avoid overstressing the MP7751 and excessive output noise, place  $C_{BYP}$  as close to the PVCC pins as possible.

2) The Inductor-Capacitor (LC) filter converts the pulse train at SW to the output voltage that drives the speaker. Please keep the filter capacitor close to the inductor.

3) Make sure that any traces carrying the switch node (SW) voltages are routed far from any input signal traces. If the trace must run near the SW trace near the input, shield the input with a ground plane between the traces. Physically separate each channel to prevent crosstalk. Make sure that all inductors used on a single circuit board have the same orientation.

Route each power supply from the source to each channel individually, not serially. This

prevents channel-to-channel coupling through the power supply input.

#### Electro-Magnetic Interference (EMI) Considerations

Due to the switching nature of Class D amplifiers, care must be taken to minimize the effects of electromagnetic interference from the amplifier. However, proper component selection and careful attention to circuit layout can minimize the effects of the EMI due to the amplifier switching.

The power inductors are a potential source of radiated emissions. For the best EMI performance, use toroidal inductors, since the magnetic field is well-contained inside the core. However toroidal inductors can be expensive to wind. For a more economical solution, use shielded-gapped-ferrite or shielded-ferritebobbin-core inductors. These inductors typically do not contain the EM field as well toroidal inductors, but can achieve a better balance between good EMI performance with low cost.

The size of high-current loops that carry rapidly changing currents must be minimized: Make sure that the  $V_{CC}$  bypass capacitors are as close to the MP7751 as possible.

Nodes that carry rapidly changing voltage, such as SW, need to be made as small as possible. If sensitive traces run near a trace connected to SW, place a ground shield between the traces.

## **TYPICAL APPLICATION CIRCUITS**

Figure 5: Typical Application Circuit

## PACKAGE INFORMATION

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.