# 5A, 36V, 500kHz Current Mode Asynchronous Step-Down Converter

## **General Description**

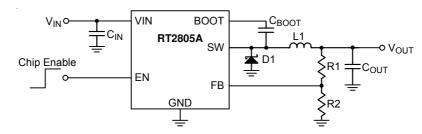

The RT2805A is a current mode asynchronous step-down converter that achieves excellent load and line regulation. Over a wide input voltage range from 5.5V to 36V and supports output current up to 5A. The Current mode operation provides fast transient response and eases loop stabilization.

An adjustable soft-start reduces the stress on the input source at startup. In shutdown mode, the regulator draws only 25µA of supply current. The RT2805A requires a minimum number of readily available external components, providing a compact solution. The RT2805A provides protection functions inducing input under voltage lockout, cycle-by-cycle current limit, short circuit protection and thermal shutdown protection.

The RT2805A is available in the SOP-8 (Exposed Pad) package.

## **Ordering Information**

RT2805A

-Package Type SP : SOP-8 (Exposed Pad-Option 2)

Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

## Features

- 5A Output Current

- Wide Operating Input Range 5.5V to 36V

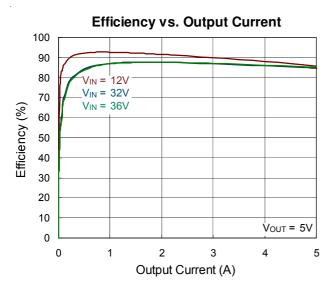

- Adjustable Output Voltage from 1.222V to 26V

- High Efficiency up to 90%

- Internal Compensation Minimizes External Parts Count

- Internal Soft-Start

- 110mΩ Internal Power MOSFET Switch

- 25µA Shutdown Mode

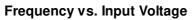

- Fixed 500kHz Frequency

- Thermal Shutdown

- Cycle-by-Cycle Current Limit

- Available In an SOP-8 (Exposed Pad) Package

- RoHS Compliant and Halogen Free

## Applications

- Distributive Power Systems

- Battery Charger

- DSL Modems

- Pre-regulator for Linear Regulators

## **Marking Information**

RT2805A GSPYMDNN RT2805AGSP : Product Number YMDNN : Date Code

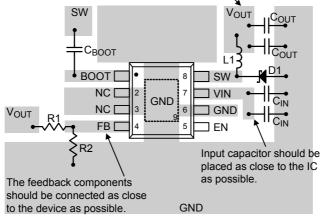

## **Simplified Application Circuit**

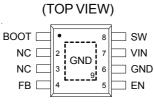

## **Pin Configurations**

SOP-8 (Exposed Pad)

## **Functional Pin Description**

| Pin No.               | Pin Name | Pin Function                                                                                                                                                                                             |

|-----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | BOOT     | Bootstrap Input for High Side Gate Driver. Connect a 10nF or greater capacitor from SW to BOOT to power the high side switch.                                                                            |

| 2, 3                  | NC       | No Internal Connection.                                                                                                                                                                                  |

| 4                     | FB       | Feedback Input. The feedback threshold is 1.222V.                                                                                                                                                        |

| 5                     | EN       | Enable Input. EN is a digital input that turns the regulator on or off. Drive EN higher than 1.4V to turn on the regulator, lower than 0.4V to turn it off. For automatic startup, leave EN unconnected. |

| 6,<br>9 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                              |

| 7                     | VIN      | Power Input. A suitable large capacitor should be connected from the VIN to GND to eliminate noise on the input to the IC.                                                                               |

| 8                     | SW       | Switch Node. Note that a capacitor is required from SW to BOOT to power the high side switch.                                                                                                            |

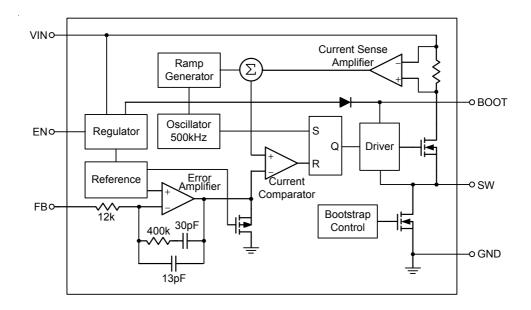

## **Function Block Diagram**

## Operation

The RT2805A is a constant frequency, current mode asynchronous step-down converter. In normal operation, the high side N-MOSFET is turned on when the S-R latch is set by the oscillator and is turned off when the current comparator resets the S-R latch. While the N-MOSFET is turned off, the inductor current conducts through the external diode.

#### **Error Amplifier**

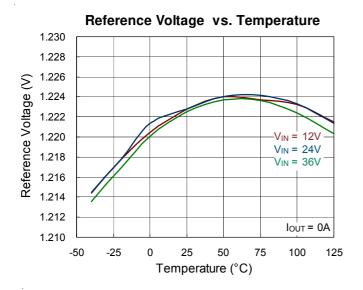

The error amplifier adjusts its output voltage by comparing the feedback signal ( $V_{FB}$ ) with the internal 1.222V reference. When the load current increases, it causes a drop in the feedback voltage relative to the reference, the error amplifier's output voltage then rises to allow higher inductor current to match the load current.

#### Oscillator

The internal oscillator runs at fixed frequency 500kHz. In short circuit condition, the frequency is reduced to 150kHz for low power consumption.

#### **Internal Regulator**

The regulator provides low voltage power to supply the internal control circuits and the bootstrap power for high side gate driver.

#### Enable

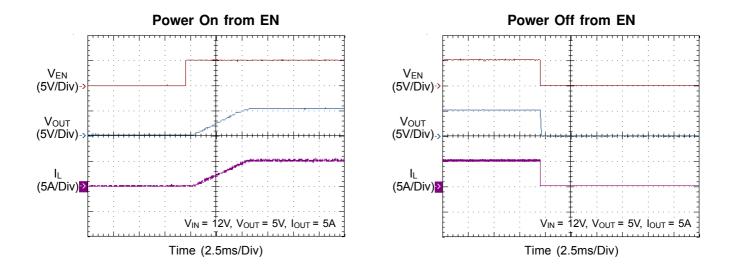

The converter is turned on when the EN pin is higher than 1.4V and turned off when the EN pin is lower than 0.4V. When the EN pin is open, it will be pulled up to logic-high by  $1\mu$ A current internally.

## Soft-Start (SS)

An internal current source charges an internal capacitor to build a soft-start ramp voltage. The FB voltage will track the internal ramp voltage during soft-start interval. The typical soft-start time is 5ms.

### Thermal Shutdown

The over temperature protection function will shut down the switching operation when the junction temperature exceeds 150°C. Once the junction temperature cools down by approximately 30°C, the converter will automatically resume switching.

## Absolute Maximum Ratings (Note 1)

| Supply Voltage, VIN                            | –0.3V to 40V                         |

|------------------------------------------------|--------------------------------------|

| Switching Voltage, SW                          | -0.3V to (V <sub>IN</sub> + 0.3V)    |

| BOOT Voltage                                   | $(V_{SW} - 0.3V)$ to $(V_{SW} + 6V)$ |

| Other Pins                                     | –0.3V to 6V                          |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                      |

| SOP-8 (Exposed Pad)                            | 2.04W                                |

| Package Thermal Resistance (Note 2)            |                                      |

| SOP-8 (Exposed Pad), $\theta_{JA}$             | 49°C/W                               |

| SOP-8 (Exposed Pad), $\theta_{JC}$             | 15°C/W                               |

| Junction Temperature                           | 150°C                                |

| Lead Temperature (Soldering, 10 sec.)          | 260°C                                |

| Storage Temperature Range                      | –65°C to 150°C                       |

| ESD Susceptibility (Note 3)                    |                                      |

| HBM (Human Body Model)                         | 2kV                                  |

## Recommended Operating Conditions (Note 4)

| Supply Voltage, VIN        | - 5.5V to 36V |

|----------------------------|---------------|

| Junction Temperature Range | 40°C to 125°C |

| Ambient Temperature Range  | 40°C to 85°C  |

## **Electrical Characteristics**

(V<sub>IN</sub> = 12V,  $T_A = -40^{\circ}C$  to 85°C unless otherwise specified)

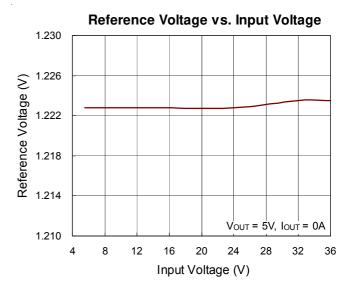

| Parameter                                 |                | Symbol               | Test Conditions                              | Min   | Тур   | Мах   | Unit    |  |

|-------------------------------------------|----------------|----------------------|----------------------------------------------|-------|-------|-------|---------|--|

|                                           |                |                      | T <sub>A</sub> = 25°C                        | 1.202 | 1.222 | 1.239 | 1.239 V |  |

| Reference Voltage                         |                | V <sub>REF</sub>     | I <sub>OUT</sub> = 0A to 5A                  | 1.196 | 1.222 | 1.245 | v       |  |

| High Side Switch-C                        | n Resistance   | R <sub>DS(ON)1</sub> | Bias Gate Driver at V <sub>IN</sub> = 5.5V   |       | 110   | 230   | mΩ      |  |

| Low Side Switch-O                         | n Resistance   | R <sub>DS(ON)2</sub> | Bias Gate Driver at V <sub>IN</sub> = 5.5V   |       | 10    | 15    | Ω       |  |

| Current Limit                             |                | I <sub>LIM</sub>     | Voltage Mode Test                            | 6     | 7.5   | 9     | Α       |  |

| Oscillator Frequence                      | су —           | fosc                 | V <sub>FB</sub> = 0.8V                       | 400   | 500   | 600   | kHz     |  |

| Short Circuit Frequ                       | ency           |                      | V <sub>FB</sub> = 0V                         |       | 150   |       | kHz     |  |

| Maximum Duty Cycle                        |                | D <sub>MAX</sub>     | V <sub>FB</sub> = 0.8V                       | 85    | 90    | 95    | %       |  |

| Minimum On-Time                           |                | t <sub>ON</sub>      | Come from Maximum Duty Cycle                 |       | 100   | 150   | ns      |  |

| Under Voltage Lockout Threshold<br>Rising |                |                      | V <sub>IN</sub> Rising, Check Switching      |       | 5.2   | 5.5   | V       |  |

| Under Voltage Lock<br>Hysteresis          | cout Threshold |                      | V <sub>IN</sub> Falling, Check Switching     |       | 700   |       | mV      |  |

| EN Threshold                              | Logic-High     | V <sub>IH</sub>      | Let EN = 1.4V, Check I <sub>Q</sub>          | 1.4   |       |       | v       |  |

| Voltage                                   | Logic-Low      | V <sub>IL</sub>      | Let EN = 0.4V, Check $I_Q$                   |       |       | 0.4   |         |  |

| Enable Pull Up Cur                        | rent           |                      |                                              |       | 1     |       | μA      |  |

| Shutdown Current                          |                | I <sub>SHDN</sub>    | V <sub>EN</sub> = 0V                         |       | 25    |       | μA      |  |

| Quiescent Current                         |                | IQ                   | V <sub>EN</sub> = 2V, V <sub>FB</sub> = 1.5V |       | 0.6   | 1     | mA      |  |

| Soft-Start Period                         |                |                      |                                              | 3     | 5     | 10    | ms      |  |

| Thermal Shutdown                          |                | T <sub>SD</sub>      |                                              |       | 160   |       | °C      |  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package. The EVB board copper area is 70mm<sup>2</sup>.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

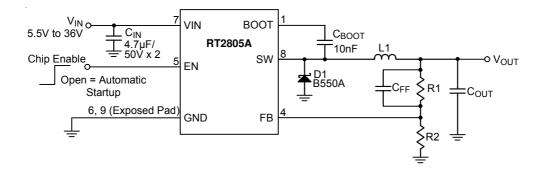

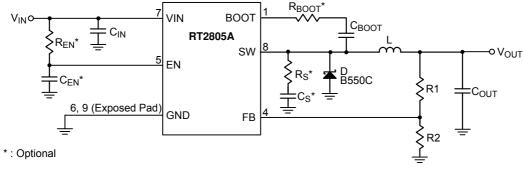

## **Typical Application Circuit**

| V <sub>OUT</sub> (V) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) | C <sub>FF</sub> (pF) | <b>L (μΗ)</b> | <b>C<sub>OUT</sub> (μF)</b> |

|----------------------|-----------------|-----------------|----------------------|---------------|-----------------------------|

| 2.5                  | 100             | 100             | 82                   | 6.8           | 22 x 2                      |

| 3.3                  | 100             | 58.6            | 82                   | 10            | 22 x 2                      |

| 5                    | 100             | 31.6            | 82                   | 15            | 22 x 2                      |

| 8                    | 100             | 18              | 82                   | 22            | 22 x 2                      |

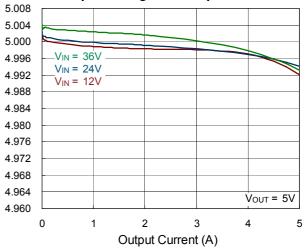

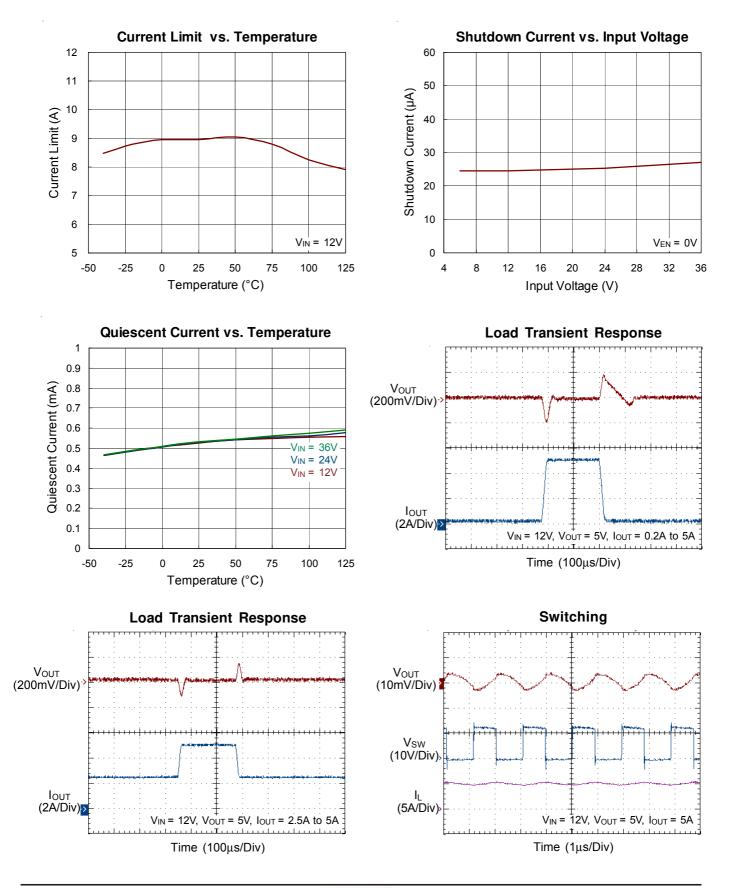

## **Typical Operating Characteristics**

Output Voltage vs. Output Current

Frequency vs. Temperature 540 530 520 510 Frequency (kHz) 500 490 480 V<sub>IN</sub> = 12V 470  $V_{IN} = 24V$ 460 VIN = 36V 450 Vout = 5V 440 0 -50 -25 25 50 75 100 125 Temperature (°C)

Copyright ©2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

Output Voltage (V)

DS2805A-03 August 2015

# RT2805A

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

8

# RT2805A

## **Application Information**

The RT2805A is an asynchronous high voltage buck converter that can support the input voltage range from 5.5V to 32V and the output current can be up to 5A.

### **Output Voltage Setting**

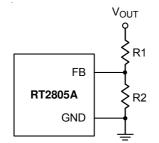

The resistive divider allows the FB pin to sense the output voltage as shown in Figure 1.

Figure 1. Output Voltage Setting

The output voltage is set by an external resistive divider according to the following equation :

$$V_{OUT} = V_{REF} \left( 1 + \frac{R1}{R2} \right)$$

Where  $V_{REF}$  is the reference voltage (1.222V typ.).

Where R1 =  $100k\Omega$ .

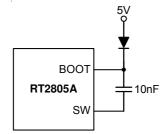

#### **External Bootstrap Diode**

Connect a 10nF low ESR ceramic capacitor between the BOOT pin and SW pin. This capacitor provides the gate driver voltage for the high side MOSFET.

It is recommended to add an external bootstrap diode between an external 5V and BOOT pin for efficiency improvement when input voltage is lower than 5.5V or duty ratio is higher than 65% .The bootstrap diode can be a low cost one such as IN4148 or BAT54. The external 5V can be a 5V fixed input from system or a 5V output of the RT2805A.

Figure 2. External Bootstrap Diode

#### Soft-Start

The RT2805A contains an internal soft-start clamp that gradually raises the output voltage. The typical soft-start time is 5ms.

#### **Chip Enable Operation**

The EN pin is the chip enable input. Pull the EN pin low (<0.4V) will shutdown the device. During shutdown mode, the RT2805A quiescent current drops to lower than 25 $\mu$ A. Drive the EN pin to high (>1.4V, <5.5V) will turn on the device again. If the EN pin is open, it will be pulled to high by internal circuit. For external timing control (e.g.RC), the EN pin can also be externally pulled to High by adding a 100k $\Omega$  or greater resistor from the VIN pin (see Figure 3).

#### **Inductor Selection**

The inductor value and operating frequency determine the ripple current according to a specific input and output voltage. The ripple current  $\Delta I_L$  increases with higher  $V_{IN}$  and decreases with higher inductance.

| ۸h | _[ | Vout<br>f×L |  | -<br>1_ | Vout |  |

|----|----|-------------|--|---------|------|--|

|    |    | f×L         |  | -       | Vin  |  |

Having a lower ripple current reduces not only the ESR losses in the output capacitors but also the output voltage ripple. High frequency with small ripple current can achieve highest efficiency operation. However, it requires a large inductor to achieve this goal.

For the ripple current selection, the value of  $\Delta I_L = 0.2(I_{MAX})$  will be a reasonable starting point. The largest ripple current occurs at the highest V<sub>IN</sub>. To guarantee that the ripple current stays below the specified maximum, the inductor value should be chosen according to the following equation :

$$L = \left[\frac{V_{OUT}}{f \times \Delta I_{L(MAX)}}\right] \times \left[1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right]$$

The inductor's current rating (caused a 40°C temperature rising from 25°C ambient) should be greater than the maximum load current and its saturation current should be greater than the short circuit peak current limit. Please see Table 2 for the inductor selection reference.

| Copyright ©2015 Richtek Technology Corporation. All rights reserved. | <b>RICHTEK</b> is a registered trademark of Richtek Technology Corporation. |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|

| www.richtek.com                                                      | DS2805A-03 August 2015                                                      |

Table 2. Suggested Inductors for Typical Application Circuit

| Component<br>Supplier | Series   | Dimensions<br>(mm) |  |  |

|-----------------------|----------|--------------------|--|--|

| TAIYO<br>YUDEN        | NR10050  | 10 x 9.8 x 5       |  |  |

| TDK                   | SLF12565 | 12.5 x 12.5 x 6.5  |  |  |

#### **Diode Selection**

When the power switch turns off, the path for the current is through the diode connected between the switch output and ground. This forward biased diode must have a minimum voltage drop and recovery times. Schottky diode is recommended and it should be able to handle those current. The reverse voltage rating of the diode should be greater than the maximum input voltage, and current rating should be greater than the maximum load current. For more detail please refer to Table 4.

#### $\textbf{C}_{\text{IN}}$ and $\textbf{C}_{\text{OUT}}$ Selection

The input capacitance,  $C_{IN}$ , is needed to filter the trapezoidal current at the source of the high side MOSFET. To prevent large ripple current, a low ESR input capacitor sized for the maximum RMS current should be used. The RMS current is given by :

$I_{RMS} = I_{OUT}(MAX) \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT} / 2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief.

Choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet size or height requirements in the design.

For the input capacitor, two  $4.7\mu$ F low ESR ceramic capacitors are recommended. For the recommended capacitor, please refer to table 3 for more detail.

The selection of  $C_{OUT}$  is determined by the required ESR to minimize voltage ripple.

Moreover, the amount of bulk capacitance is also a key for  $C_{OUT}$  selection to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response as described in a later section. The output ripple,  $\Delta V_{\text{OUT}}$  , is determined by :

$$\Delta V_{OUT} \leq \Delta I_L \left[ ESR + \frac{1}{8 f C_{OUT}} \right]$$

The output ripple will be highest at the maximum input voltage since  $\Delta I_L$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirement. Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR value. However, it provides lower capacitance density than other types. Although Tantalum capacitors have the highest capacitance density, it is important to only use types that pass the surge test for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR. However, it can be used in cost-sensitive applications for ripple current rating and long term reliability considerations. Ceramic capacitors have excellent low ESR characteristics but can have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can also lead to significant ringing.

Higher values, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. However, care must be taken when these capacitors are used at input and output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input,  $V_{IN}$ . A sudden inrush of current through the long wires can potentially cause a voltage spike at  $V_{IN}$  large enough to damage the part.

#### **Checking Transient Response**

The regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in load current. When a load step occurs,  $V_{OUT}$  immediately shifts by an amount equal to  $\Delta I_{LOAD}$  (ESR) also begins to charge or discharge  $C_{OUT}$  generating a feedback error signal for the regulator to return  $V_{OUT}$  to its steady-state value. During this recovery time,  $V_{OUT}$  can be monitored for overshoot or ringing that would indicate a stability problem.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

#### **EMI** Consideration

Since parasitic inductance and capacitance effects in PCB circuitry would cause a spike voltage on SW pin when high side MOSFET is turned-on/off, this spike voltage on SW may impact on EMI performance in the system. In order to enhance EMI performance, there are two methods to suppress the spike voltage. One is to place an R-C snubber between SW and GND and make them as close as possible to the SW pin (see Figure 3). Another method

is to add a resistor in series with the bootstrap capacitor,  $C_{BOOT}$ . But this method will decrease the driving capability to the high side MOSFET. It is strongly recommended to reserve the R-C snubber during PCB layout for EMI improvement. Moreover, reducing the SW trace area and keeping the main power in a small loop will be helpful on EMI performance. For detailed PCB layout guide, please refer to the section of Layout Consideration.

Figure 3. Reference Circuit with Snubber and Enable Timing Control

#### **Thermal Considerations**

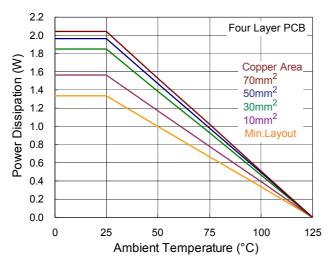

For continuous operation, do not exceed the maximum operation junction temperature. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula :

#### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance  $\theta_{JA}$  is layout dependent. For PSOP-8 package, the thermal resistance  $\theta_{JA}$  is 75°C/W on the standard JEDEC 51-7 four-layers thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by following formula :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (75^{\circ}C/W) = 1.333W$ (min.copper area PCB layout)

$$\label{eq:PDMAX} \begin{split} \mathsf{P}_{\mathsf{D}(\mathsf{MAX})} &= (125^\circ C - 25^\circ C) \ / \ (49^\circ C/W) = 2.04W \ (70 \text{mm}^2 \text{ copper area PCB layout}) \end{split}$$

The thermal resistance  $\theta_{JA}$  of SOP-8 (Exposed Pad) is determined by the package architecture design and the PCB layout design. However, the package architecture design had been designed. If possible, it's useful to increase thermal performance by the PCB layout copper design. The thermal resistance  $\theta_{JA}$  can be decreased by adding copper area under the exposed pad of SOP-8 (Exposed Pad) package.

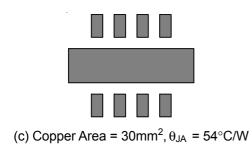

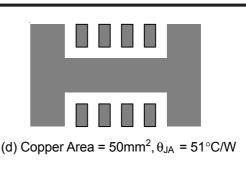

As shown in Figure 4, the amount of copper area to which the SOP-8 (Exposed Pad) is mounted affects thermal performance. When mounted to the standard SOP-8 (Exposed Pad) pad (Figure 4a),  $\theta_{JA}$  is 75°C/W. Adding copper area of pad under the SOP-8 (Exposed Pad) (Figure 4.b) reduces the  $\theta_{JA}$  to 64°C/W. Even further, increasing the copper area of pad to 70mm<sup>2</sup> (Figure 4.e) reduces the  $\theta_{JA}$  to 49°C/W.

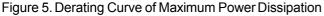

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 5 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power dissipation allowed.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

(a) Copper Area =  $(2.3 \times 2.3) \text{ mm}^2$ ,  $\theta_{JA} = 75^{\circ}\text{C/W}$

(b) Copper Area =  $10 \text{mm}^2$ ,  $\theta_{\text{JA}} = 64^{\circ}\text{C/W}$

RT2805

(e) Copper Area =  $70 \text{ mm}^2$ ,  $\theta_{\text{JA}} = 49^{\circ} \text{C/W}$

Figure 4. Thermal Resistance vs. Copper Area Layout Design

#### Layout Consideration

Follow the PCB layout guidelines for optimal performance of the RT2805A.

- Keep the traces of the main current paths as short and wide as possible.

- Put the input capacitor as close as possible to the device pins (VIN and GND).

- SW node is with high frequency voltage swing and should be kept at small area. Keep analog components away from the SW node to prevent stray capacitive noise pickup.

- Connect feedback network behind the output capacitors.

Keep the loop area small. Place the feedback components near the RT2805A.

- Connect all analog grounds to a common node and then connect the common node to the power ground behind the output capacitors.

- An example of PCB layout guide is shown in Figure 6 for reference.

SW should be connected to inductor by wide and short trace. Keep sensitive components away from this trace.

Figure 6. PCB Layout Guide

| Table 3. Suggested | Capacitors | for | C <sub>IN</sub> | and | COUT |

|--------------------|------------|-----|-----------------|-----|------|

|--------------------|------------|-----|-----------------|-----|------|

| Location | Component Supplier | Part No.        | Capacitance | Case Size |

|----------|--------------------|-----------------|-------------|-----------|

| CIN      | MURATA             | GRM32ER71H475K  | 4.7         | 1206      |

| CIN      | TAIYO YUDEN        | UMK325BJ475MM-T | 4.7         | 1206      |

#### Table 4. Suggested Diode

| Component Supplier | Series | V <sub>RRM</sub> (V) | I <sub>OUT</sub> (A) | Package |

|--------------------|--------|----------------------|----------------------|---------|

| DIODES             | B550C  | 50                   | 5                    | SMC     |

| PANJIT             | SK55   | 50                   | 5                    | SMC     |

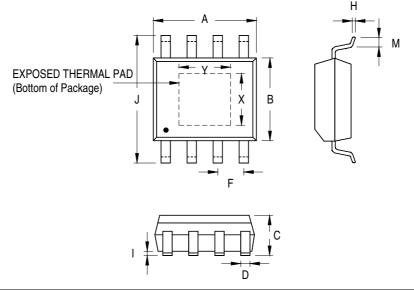

## **Outline Dimension**

| Symbol   |   | Dimensions In Millimeters |       | Dimensions In Inches |       |

|----------|---|---------------------------|-------|----------------------|-------|

|          |   | Min                       | Max   | Min                  | Max   |

| А        |   | 4.801                     | 5.004 | 0.189                | 0.197 |

| В        |   | 3.810                     | 4.000 | 0.150                | 0.157 |

| С        |   | 1.346                     | 1.753 | 0.053                | 0.069 |

| D        |   | 0.330                     | 0.510 | 0.013                | 0.020 |

| F        |   | 1.194                     | 1.346 | 0.047                | 0.053 |

| Н        |   | 0.170                     | 0.254 | 0.007                | 0.010 |

| I        |   | 0.000                     | 0.152 | 0.000                | 0.006 |

| J        |   | 5.791                     | 6.200 | 0.228                | 0.244 |

| М        |   | 0.406                     | 1.270 | 0.016                | 0.050 |

| Option 1 | Х | 2.000                     | 2.300 | 0.079                | 0.091 |

|          | Y | 2.000                     | 2.300 | 0.079                | 0.091 |

| Option 2 | Х | 2.100                     | 2.500 | 0.083                | 0.098 |

|          | Y | 3.000                     | 3.500 | 0.118                | 0.138 |

8-Lead SOP (Exposed Pad) Plastic Package

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.