# CYWB0124AB, CYWB0125AB

# West Bridge<sup>®</sup> Antioch<sup>™</sup> USB/Mass Storage Peripheral Controller

### Features

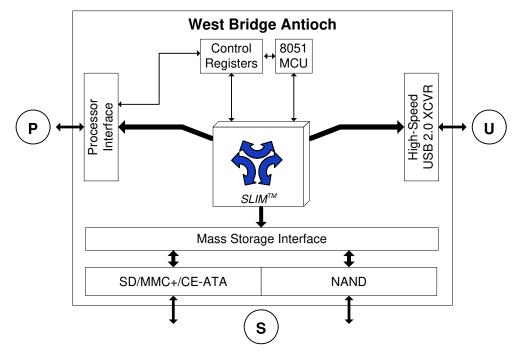

- SLIM <sup>TM</sup> architecture, enabling simultaneous and independent data paths between processor and USB, and between USB and mass storage

- High speed USB at 480 Mbps

- □ USB-2.0 compliant

- Integrated USB 2.0 transceiver, smart serial interface engine

16 programmable endpoints

- Mass storage device support

- □ MMC/MMC+/SD/CE-ATA

- □ NAND flash: x8 or x16, SLC

- □ Full NAND management (ECC, wear leveling)

- Memory mapped interface to main processor

- DMA slave support

- Supports Microsoft<sup>®</sup> media transfer protocol (MTP) with optimized data throughput

- Ultra low power, 1.8 V core operation

- Low power modes

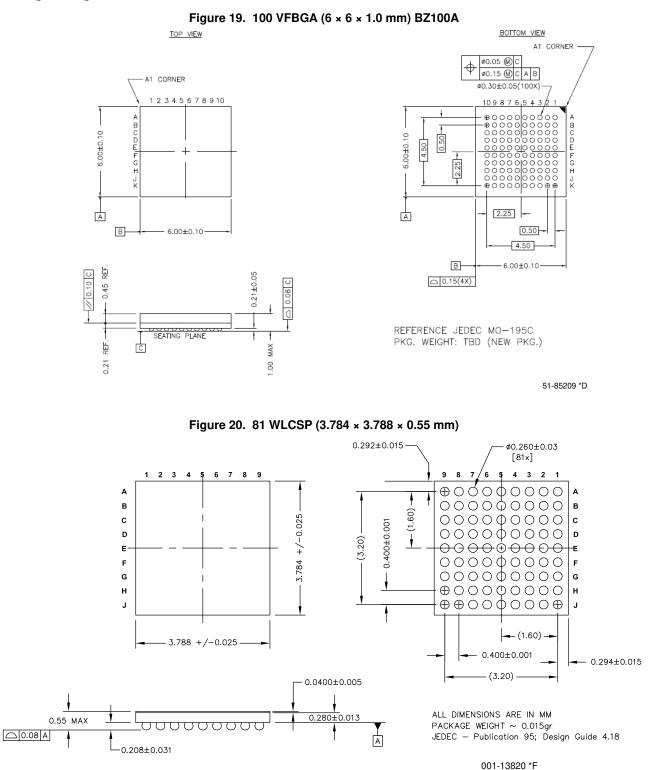

- Small footprint, 6 × 6 mm VFBGA, and less than 4 × 4 mm WLCSP

- Selectable clock input frequencies

19.2 MHz, 24 MHz, 26 MHz, and 48 MHz

### Logic Block Diagram

### Applications

- Cellular phones

- Portable media players

- Personal digital assistants

- Digital cameras

- Portable video recorder

**Cypress Semiconductor Corporation** Document Number: 001-07978 Rev. \*L

# CYWB0124AB, CYWB0125AB

### Contents

| Functional Overview                | 3 |

|------------------------------------|---|

| SLIM <sup>™</sup> Architecture     | 3 |

| Turbo-MTP Support                  | 3 |

| 8051 Microprocessor                |   |

| Configuration and Status Registers | 3 |

| Processor Interface (P-port)       |   |

| USB Interface (U-Port)             | 3 |

| Mass Storage Support (S-Port)      | 3 |

| Clocking                           |   |

| Power Domains                      | 5 |

| Power Modes                        | 5 |

| Antioch in WLCSP                   | 6 |

| Absolute Maximum Ratings           |   |

| Operating Conditions               |   |

| DC Characteristics                 |   |

| USB Transceiver                    |   |

| AC Characteristics                      | 14 |

|-----------------------------------------|----|

| USB Transceiver                         | 14 |

| P-Port Interface                        | 14 |

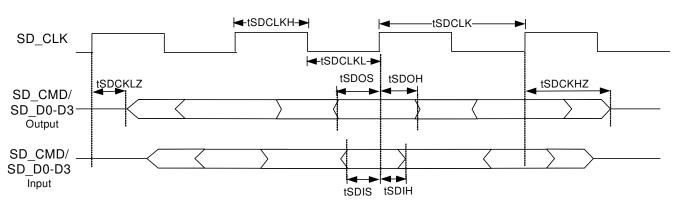

| SD/MMC Parameters                       | 21 |

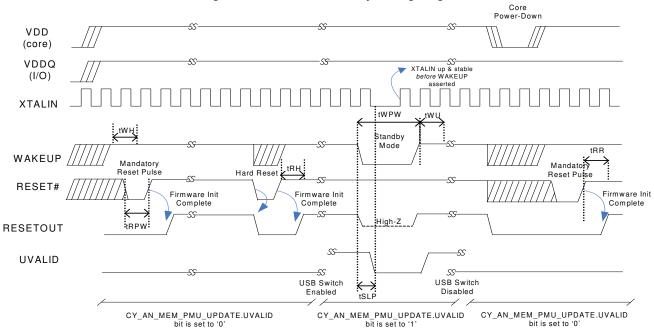

| Reset and Standby Timing Parameters     | 22 |

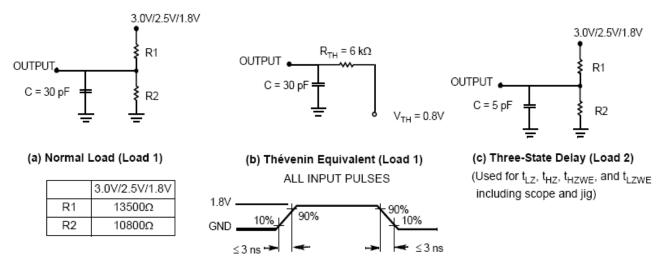

| Ordering Information                    | 23 |

| Ordering Code Definitions               | 23 |

| Package Diagrams                        | 24 |

| Acronyms                                | 25 |

| Document Conventions                    | 25 |

| Units of Measure                        | 25 |

| Document History Page                   | 26 |

| Sales, Solutions, and Legal Information | 29 |

| Worldwide Sales and Design Support      | 29 |

| Products                                | 29 |

| PSoC Solutions                          | 29 |

### **Functional Overview**

### SLIM<sup>™</sup> Architecture

The Simultaneous Link to Independent Multimedia (SLIM) architecture allows three different interfaces (the P-port, the S-port, and the U-port) to connect to one another independently.

With this architecture, using Antioch<sup>™</sup> to connect a device to a PC through an USB does not disturb the functions of the device. It still accesses mass storage at the same time the PC is synchronizing with the main processor.

The SLIM architecture enables new usage models, in which a PC accesses a mass storage device independent of the main processor, or enumerates access to both the mass storage and the main processor at the same time.

In a handset, this typically enables the user to use the phone as a thumb drive or download media files to the phone while still having full functionality available on the phone. The same phone even functions as a modem to connect the PC to the web.

### **Turbo-MTP Support**

Turbo-MTP is an implementation of Microsoft's Media Transfer Protocol (MTP) enabled by West Bridge® Antioch<sup>™</sup>. In the current generation of MTP-enabled mobile phones, all protocol packets need to be handled by the main processor. West Bridge Turbo-MTP switches these packet types and sends only control packets to the processor, while data payloads are written directly to mass storage. This brings the high performance of West Bridge to MTP. For more information on Turbo-MTP, refer to the application note AN48864 "Performance Optimization by West Bridge Controllers with Turbo-MTP".

### 8051 Microprocessor

The 8051 microprocessor embedded in Antioch does basic transaction management for all the transactions between the P-port, the S-port, and the U-port. The 8051 does not reside in the data path; it manages the path. The data path is optimized for performance. The 8051 executes firmware that supports NAND, SD, and MMC devices at the S-port. For the NAND device, the 8051 firmware follows the Smart Media algorithm to support:

- Physical to Logical Management

- ECC Correction

- Wear Leveling

- NAND Flash Bad Block Handling

### **Configuration and Status Registers**

The West Bridge Antioch device includes Configuration and Status registers that are accessible as memory mapped registers through the processor interface. The Configuration registers allow the system to specify certain behavior from Antioch. For example, it masks certain Status registers from raising an interrupt. The Status registers convey the status of different parameters of Antioch, such as the addresses of buffers for read operations.

### Processor Interface (P-port)

Communication with the external processor is realized through a dedicated processor interface. This interface supports both synchronous and asynchronous SRAM mapped memory accesses. This ensures straightforward electrical communications with the processor that also has other devices connected on a shared memory bus. Asynchronous accesses reach a bandwidth of up to 66.7 MBps. Synchronous accesses are performed at 33 MHz across 16 bits for up to 66.7 MBps bandwidth.

The memory address is decoded to access any of the multiple endpoint buffers inside Antioch. These endpoints serve as buffers for data between each pair of ports, for example, between the processor port and the USB port. The processor writes and reads into these buffers through the memory interface.

Access to these buffers is controlled by using either a DMA protocol or an interrupt to the main processor. These two modes are configured by the external processor.

As a DMA slave, Antioch generates a DMA request signal to signify to the main processor that it is ready to read from or write to a specific buffer. The external processor monitors this signal and polls Antioch for the specific buffers ready for read or write. It then performs the appropriate read or write operations on the buffer through the processor interface. This way, the external processor only deals with the buffers to access a multitude of storage devices connected to Antioch.

In the Interrupt mode, Antioch communicates important buffer status changes to the external processor using an interrupt signal. The external processor then polls Antioch for the specific buffers ready for read or write and performs the appropriate read or write operations through the processor interface.

### **USB Interface (U-Port)**

In accordance with the USB 2.0 specification, Antioch operates in Full Speed USB mode in addition to High Speed USB mode. The USB interface consists of the USB transceiver. The USB interface accesses and also is accessed by both the P-port and the S-port.

The Antioch USB interface supports programmable CONTROL/BULK/INTERRUPT/ISOCHRONOUS endpoints.

### Mass Storage Support (S-Port)

The S-port is configured in two different modes, either simultaneously supporting an SD/MMC+ port and a x8 NAND port or supporting a unique x16 NAND access port. The NANDCFG Ball is used to set the configuration of the S-port as either 16-bit NAND or 8-bit NAND and SD/MMC. The 16-bit interface is only used when there is no other mass storage device connected to the S-port. Note that in the WLCSP option, the S-port is not configurable; it only supports a single SD/MMC+ port with no NAND port.

Antioch also includes two chip enables, NAND\_CE# and NAND\_CE2#, that enable to access two different NANDs alternately.

### NAND Port (S-Port)

Antioch, as part of its mass storage management functions, fully manages a NAND device. The embedded 8051 manages the actual reading and writing of the NAND along with its required protocols. It performs standard NAND management functions such as ECC and wear leveling.

SLC NAND devices are supported on all devices in the Antioch family. The write performance for connecting to a single SLC NAND is up to 9 MBps, while read performance is up to 13 MBps.

#### SD/MMC/CE-ATA Port (S-Port)

When Antioch is configured through NANDCFG to support MMC/SD/CE-ATA, this interface supports:

- The MultiMediaCard System Specification, MMCA Technical Committee, Version 4.1

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 1.10, October 15, 2004, and Version 2.0, November 9, 2005

- CE-ATA Digital Protocol, Rev 1.1, 28 September, 2005 and CE-ATA Host Design Guidance, Rev 1.0, 29 September, 2005

West Bridge Antioch provides support for 1-bit and 4-bit SD cards: 1-bit, 4-bit, and 8-bit MMC, and MMC+. For the SD, MMC/MMC Plus card, this block supports one card for one physical bus interface.

Antioch supports SD commands including the multisector program command that is handled by the API.

Compatibility with specific CE-ATA HDD is subject to confirmation with drive vendors.

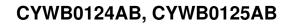

### Clocking

Antioch allows either to connect a crystal between the XTALIN and XTALOUT balls or connect an external clock at the XTALIN ball. The power supply level at the crystal supply XVDDQ determines whether a crystal or a clock is provided. If XVDDQ is detected as 1.8 V, Antioch assumes that a clock input is provided. This clock input must be a 1.8 V square wave. To connect a crystal, XVDDQ must be 3.3 V. Note that the clock inputs at 3.3 V level are not supported.

CYWB0124AB supports crystals only at 19.2, 24, and 26 MHz. At 48 MHz, only clock inputs are supported. Clock inputs are supported at all frequencies.

Antioch has an on-chip oscillator circuit that uses an external 19.2/24/26 MHz (±150 ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 1 mW drive level

- 12 pF (5% tolerance) load capacitors<sup>[1]</sup>

#### Figure 1. Capacitor

12 pF capacitor values assumes a trace capacitance of 3 pF per side on a four-layer FR4 PCA

| Parameter | Description                         | Specif | Specification |        |  |  |

|-----------|-------------------------------------|--------|---------------|--------|--|--|

| Farameter | Description                         | Min    | Мах           | – Unit |  |  |

| PN_100Hz  | Input Phase Noise at 100 Hz Offset  |        | -75           | dBc/Hz |  |  |

| PN_1k     | Input Phase Noise at 1 kHz Offset   |        | -104          | dBc/Hz |  |  |

| PN_10k    | Input Phase Noise at 10 kHz Offset  |        | -120          | dBc/Hz |  |  |

| PN_100k   | Input Phase Noise at 100 kHz Offset |        | -128          | dBc/Hz |  |  |

| PN_1M     | Input Phase Noise at 1 MHz Offset   |        | -130          | dBc/Hz |  |  |

|           | Duty Cycle                          | 30     | 70            | %      |  |  |

|           | Maximum Frequency Deviation         |        | 150           | ppm    |  |  |

|           | Overshoot                           |        | 3             | %      |  |  |

|           | Undershoot                          |        | -3            | %      |  |  |

#### Table 1. External Clock Requirements

#### Note

1. Specified as typical for 24 MHz frequency. Load capacitance varies with crystal vendor specifications and frequency used.

This on-chip PLL multiplies the 19.2/24/26/48 MHz frequency up to 480 MHz, as required by the transceiver/PHY. The internal counters divide it down for use as the 8051 clock. The 8051 clock frequency is 48 MHz. The XTALIN frequency is independent of the clock/data rate of the 8051 microprocessor or any of the device interfaces (including P-port and S-port). The internal PLL applies the proper clock multiply option depending on the input frequency.

For applications that use an external clock source to drive XTALIN, the XTALOUT Ball is left floating. The external clock is a square wave that conforms to high and low voltage levels mentioned in Table 3 on page 12 and the rise and fall time specifications in Figure 18 on page 23. The external clock source also stops high or low and is not toggling to achieve the lowest possible current consumption. The requirements for an external clock source are shown in Table 4 on page 13.

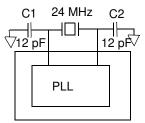

#### **Power Domains**

Antioch has multiple power domains that serve different purposes within the chip.

\*VDDQ. This refers to a group of five independent supply domains for the digital I/Os. The nominal voltage level on these supplies are 1.8 V, 2.5 V, or 3.3 V. Specifically, the four separate I/O power domains are:

- PVDDQ P-port processor interface I/O

- SNVDDQ S-port NAND interface I/O

- SSVDDQ S-port SD interface I/O

- GVDDQ Other miscellaneous I/O

**UVDDQ**. This is the 3.3 V nominal supply for the USB I/O and some analog circuits. It also supplies power to the USB transceiver.

**VDD33.** This supply is required for the power sequence control circuits. For more information, see Table 2 on page 7.

$V_{DD}$ . This is the supply voltage for the logic core. The nominal supply voltage level is 1.8 V. This supplies the core logic circuits. The same supply is also used for AVDDQ.

**AVDDQ**. This is the 1.8 V supply for PLL and USB serializer analog components. The same supply is also used for  $V_{DD}$ . Maximum permitted noise on AVDDQ is 20 mV p-p.

**XVDDQ**. This is the clock I/O supply. 3.3 V for XTAL or 1.8 V for an external clock.

#### Figure 2. Antioch Power Supply Domains

Noise guideline for all supplies except AVDDQ is a maximum of 100 mV p-p. All I/O supplies of Antioch are ON when a system is active, even if Antioch is not used. The core V<sub>DD</sub> is also deactivated at any time to preserve power, provided that there is a minimum impedance of 1 k $\Omega$  between the V<sub>DD</sub> Ball and ground. All I/Os tri-state when the core is disabled.

#### Power Supply Sequence

The power supplies are independently sequenced without damaging the part. All power supplies are up and stable before the device operates. If all supplies are not stable, the remaining domains are in low power (standby) mode.

#### Flexible I/Os

Each of Antioch's ports operate between 1.8 V and 3.3 V with adjustable slew rate for each port and adjustable drive strength for each port for the I/Os. The slew rate and drive strength are controlled by registers.

#### **Power Modes**

In addition to the normal operating mode, Antioch contains several low power modes when normal operation is not required.

#### Normal Mode

In this mode, Antioch is fully functional. This is the mode in which the data transfer functions described in this datasheet are performed.

#### Suspend Mode

This mode is entered internally by 8051 (external processor only initiates entry into this mode through Mailbox commands). This mode is exited by the D+ bus going low, GPIO[0] going to a predetermined state, or by asserting CE# LOW.

- In Suspend mode of Antioch:

- The clocks are shut off.

- All I/Os maintain their previous state.

- Core power supply are retained.

- The states of the Configuration registers, endpoint buffers, and the program RAM are maintained. All transactions are completed before Antioch enters Suspend mode (state of outstanding transactions are not preserved).

- The firmware resumes its operation from where it has suspended, because the program counter is not reset.

- The only inputs that are sensed are RESET#, GPIO[0], D+, and CE#. The last three are wakeup sources (each is individually enabled or disabled).

- Hard reset is performed by asserting the RESET# input and Antioch performs initialization.

### Standby Mode

Standby mode is a low power state. This is the lowest power mode of Antioch while still maintaining external supply levels. This mode is entered through the deassertion of the WAKEUP input ball or through internal register settings. It is exited by asserting the WAKEUP Ball if the mode is entered by deasserting the WAKEUP Ball. Exiting Standby mode is also accomplished by asserting CE# LOW or processor writes to Internal registers.

In this mode, the following characteristics apply:

- All Configuration register settings and program RAM contents are preserved. However, data in the buffers or other parts of the data path, if any, is not guaranteed in values. Therefore, the external processor ensures that the required data is read before Antioch is moved into this Standby mode.

- The program counter is reset upon waking up from Standby mode.

- All outputs are tri-stated (except UVALID), and I/O is placed in input only configuration. Values of I/Os in Standby mode are listed in the Table 2 on page 7.

- □ Core power supply is retained.

- Hard reset is performed by asserting the RESET# input, and Antioch performs initialization.

- PLL is disabled.

### Core Power Down Mode

The core power supply  $V_{DD}$  is powered down in this mode. AVDDQ is tied to the same supply as  $V_{DD}$  and as a result, is also powered down. The endpoint buffers, configuration registers, and the program RAM do not maintain state. It is necessary to reload the firmware upon exiting from this mode. It is required that all VDDQ power supplies (except AVDDQ) are on and not powered down in this mode. VDD33 must remain ON and the requirement of a minimum impedance of 1 k $\Omega$  between the V<sub>DD</sub> ball and ground remains unchanged.

In the WLCSP option, AVDDQ is internally tied to XVDDQ. As a result, the clock input at XTALIN must be brought to a steady LOW level before entry into Core Power Down mode.

### Antioch in WLCSP

Antioch is available in a Wafer Level Chip Scale Package (WLCSP) with 81 balls. The WLCSP differs from the VFBGA in the following ways:

- The XTALIN input only accepts clock inputs and no crystals. The XTALOUT ball and the XVDDQ power domain do not exist in this package. The XVDDQ power domain is internally combined with AVDDQ.

- Since AVDDQ and as a result, XVDDQ, are OFF in the Core Power Down mode, the clock input at XTALIN must be brought to a steady LOW level before entry into Core Power Down mode.

- NAND functionality is not available. SNVDDQ does not exist as a separate power domain. It is internally combined with SSVDDQ.

- The P-port CLK ball and the P-port synchronous mode operation are not available. The P-port is operated only in asynchronous mode.

- GVDDQ is not a separate power domain in the WLCSP package. It is internally combined with PVDDQ.

- Availability of specific signals on the WLCSP option is detailed in Table 2 on page 7.

The Ball Assignment table for CYWB0124AB, CYWB0125AB follows.<sup>[2, 3, 4]</sup>

#### Table 2. Ball Assignment

|        | VFBGA | WLCSP | Ball Name | I/O | Ball Description                                                                                                                                                                                                                           | Standby | Reset <sup>[5]</sup> | Power Domain |  |

|--------|-------|-------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|--------------|--|

|        | J2    | N/A   | CLK       | 1   | Clock for P-port                                                                                                                                                                                                                           | -       | -                    |              |  |

|        | G1    | G8    | CE#       | I   | Chip Select for P-port. Active LOW                                                                                                                                                                                                         | -       | -                    |              |  |

|        | H3    | J6    | A[7]      | 1   | Bit 7 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | H2    | J7    | A[6]      | I   | Bit 6 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | H1    | J8    | A[5]      | I   | Bit 5 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | J3    | H6    | A[4]      | 1   | Bit 4 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | J1    | H7    | A[3]      | I   | Bit 3 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | K3    | J9    | A[2]      | I   | Bit 2 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | K2    | H8    | A[1]      | I   | Bit 1 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | K1    | H9    | A[0]      |     | Bit 0 of Address Bus for P-port                                                                                                                                                                                                            | -       | -                    |              |  |

|        | G2    | G9    | DQ[15]    | I/O | Bit 15 of Data Bus for P-port                                                                                                                                                                                                              | Z       | Z                    |              |  |

|        | G3    | G7    | DQ[14]    | I/O | Bit 14 of Data Bus for P-port                                                                                                                                                                                                              | Z       | Z                    |              |  |

|        | F1    | F8    | DQ[13]    | I/O | Bit 13 of Data Bus for P-port                                                                                                                                                                                                              | Z       | Z                    |              |  |

|        | F2    | F9    | DQ[12]    | I/O | Bit 12 of Data Bus for P-port                                                                                                                                                                                                              | Z       | Z                    |              |  |

|        | F3    | F7    | DQ[11]    | I/O | Bit 11 of Data Bus for P-port                                                                                                                                                                                                              | Z       | Z                    |              |  |

|        | E1    | E9    | DQ[10]    | I/O | Bit 10 of Data Bus for P-port                                                                                                                                                                                                              | Z       | Z                    |              |  |

|        | E2    | E8    | DQ[9]     | I/O | Bit 9 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | E3    | E7    | DQ[8]     | I/O | Bit 8 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | D1    | D9    | DQ[7]     | I/O | Bit 7 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | D2    | D8    | DQ[6]     | I/O | Bit 6 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

| D D    | D3    | D7    | DQ[5]     | I/O | Bit 5 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    | PVDDQ        |  |

| P Port | C1    | C9    | DQ[4]     | I/O | Bit 4 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    | VGND         |  |

|        | C2    | C8    | DQ[3]     | I/O | Bit 3 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | C3    | C7    | DQ[2]     | I/O | Bit 2 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | B1    | B9    | DQ[1]     | I/O | Bit 1 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | B2    | B8    | DQ[0]     | I/O | Bit 0 of Data Bus for P-port                                                                                                                                                                                                               | Z       | Z                    |              |  |

|        | A1    | A9    | ADV#      | I   | Address Valid for P-port. Valid during<br>asynchronous mode. ADV# deassertion<br>causes to latch the address.                                                                                                                              | -       | -                    |              |  |

|        | B3    | A8    | OE#       | I   | Output Enable. Controls the data bus output drive. Ignored during write cycle. Active LOW.                                                                                                                                                 | -       | -                    |              |  |

|        | A2    | B7    | WE#       | I   | Write Enable. Signals a read (HIGH) or write (LOW) access cycle.                                                                                                                                                                           | -       | -                    |              |  |

|        | A3    | A7    | INT#      | 0   | Interrupt Request. Assertion indicates that an interrupt event has occurred. Active LOW.                                                                                                                                                   | Z       | Z                    |              |  |

|        | A4    | C6    | DRQ#      | 0   | DMA Request. Assertion indicates to<br>Processor that it is ready to read or write one<br>or more endpoints. It reflects register<br>CY_AN_MEM_P0_DRQ EPnDRQ assertions.<br>Active LOW or HIGH (programmable).                             | Z       | Z                    |              |  |

|        | B4    | C5    | DACK#     | Ι   | DMA Acknowledgement. Assertion indicates<br>DMA acknowledgement from processor. Is<br>configured in ACK mode (asserted throughout<br>DMA transfer) or EOB mode (pulsed at end of<br>DMA transfer). Active LOW or HIGH (program-<br>mable). | -       | -                    |              |  |

Notes

Unused inputs: Must be connected to HIGH/V<sub>DD</sub> or LOW/GND (negligible difference in current drawn) logic level, through a single 10 K pull-up resistor. The only exceptions are WAKEUP, NANDCFG and CLK. WAKEUP is tied HIGH for normal operation and NANDCFG is tied LOW for unused NAND with SD or tied HIGH for 16-bit NAND with no SD. CLK is tied LOW for asynchronous P-port operation.

Unused I/Os: For lowest leakage, unused I/Os must be connected to a HIGH logic level. It is recommended that connection to the power supply is through a single 10k ohm pull-up resistor for all unused I/Os.

No Anticch balls have internal pull-up or pull-down resistors. Input/output balls may require external pull-up or pull-down resistors depending on the application. The pull-up resistors used to indicate speed capability on the USB are included in Antioch and need not be connected externally.

The Reset column indicates the state of signals during reset (RESET# asserted). The Standby column indicates signal state during Standby (low power operating mode through WAKEUP deassertion) or core V<sub>DD</sub> deactivation. 5.

### Table 2. Ball Assignment (continued)

|        | VFBGA WLCSP Ball Name |            | I/O                                   | Ball Description             | Standby    | Reset <sup>[5]</sup>                                                                                                                                              | Power Domain |          |                |  |  |  |

|--------|-----------------------|------------|---------------------------------------|------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|----------------|--|--|--|

|        |                       |            | SD and<br>8-bit NAND<br>Configuration | 16-bit NAND<br>Configuration |            |                                                                                                                                                                   |              |          |                |  |  |  |

|        | G9                    | H2         | SD_D[7]                               | NAND_IO[15]                  | I/O        | Serve as SD_D[7] for SD port or NAND_IO[15] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.        | Z            | Z        |                |  |  |  |

|        | G10                   | H1         | SD_D[6]                               | NAND_IO[14]                  | I/O        | Serve as SD_D[6] for SD port or NAND_IO[14] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.        | Z            | Z        |                |  |  |  |

|        | F9                    | G3         | SD_D[5]                               | NAND_IO[13]                  | I/O        | Serve as SD_D[5] for SD port or NAND_IO[13] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.        | Z            | Z        |                |  |  |  |

|        | F10                   | G2         | SD_D[4]                               | NAND_IO[12]                  | I/O        | Serve as SD_D[4] for SD port or NAND_IO[12] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.        | Z            | Z        |                |  |  |  |

|        | E9                    | F2         | SD_D[3]                               | NAND_IO[11]                  | I/O        | Serve as SD_D[3] for SD port or NAND_IO[11] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.        | Z            | Z        |                |  |  |  |

|        | E10                   | E3         | SD_D[2]                               | NAND_IO[10]                  | I/O        | Serve as SD_D[2] for SD port or NAND_IO[10] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.        | Z            | Z        | SSVDDQ<br>VGND |  |  |  |

|        | D9                    | E2         | SD_D[1]                               | NAND_IO[9]                   | I/O        | Serve as SD_D[1] for SD port or NAND_IO[9] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.         | Z            | Z        |                |  |  |  |

| S Port | D10                   | E1         | SD_D[0]                               | NAND_IO[8]                   | I/O        | Serve as SD_D[0] for SD port or NAND_IO[8] for<br>NAND Upper I/O port depending on NANDCFG<br>selection. NAND configuration is not available in<br>WLCSP.         | Z            | Z        |                |  |  |  |

|        | F8                    | G1         | SD_CLK                                | N/A                          | 0          | Clock output for the SD interface. Frequency is<br>changed and clock is disabled through firmware<br>control.                                                     | Z            | Z        |                |  |  |  |

|        | G8                    | H3         | SD_CMD                                | N/A                          | I/O        | SD Command/Response Ball.                                                                                                                                         | Z            | Z        |                |  |  |  |

|        | H8                    | G4         | SD_POW                                | N/A                          | 0          | SD Power Control. This GPIO is used to control<br>SD/MMC card power FET if present. HIGH indicates<br>on, LOW indicates off.                                      | Z            | Z        |                |  |  |  |

|        | H10                   | D1         | SD_WP                                 | N/A                          | Ι          | SD Write Protection Detection. Connected to GPIO for<br>firmware detection. HIGH indicates that the device<br>connected to the SD port has write protect enabled. |              | -        |                |  |  |  |

|        | K7                    | N/A        | NAND_IO[7]                            | NAND_IO[7]                   | I/O        | NAND_IO[7] for NAND Upper I/O port                                                                                                                                | Z            | Z        |                |  |  |  |

|        | K8                    | N/A        | NAND_IO[6]                            | NAND_IO[6]                   | I/O        | NAND_IO[6] for NAND Upper I/O port                                                                                                                                |              |          | 4              |  |  |  |

|        | J8                    | N/A        | NAND_IO[5]                            | NAND_IO[5]                   | I/O        | NAND_IO[5] for NAND Upper I/O port                                                                                                                                |              |          | 4              |  |  |  |

|        | K9<br>J9              | N/A<br>N/A | NAND_IO[4]<br>NAND_IO[3]              | NAND_IO[4]<br>NAND_IO[3]     | 1/O<br>1/O | NAND_IO[4] for NAND Upper I/O port NAND IO[3] for NAND Upper I/O port                                                                                             |              |          | -              |  |  |  |

|        | - J9<br>- H9          | N/A<br>N/A | NAND_IO[3]                            | NAND_IO[3]                   | 1/0        | NAND_IO[3] for NAND Upper I/O port                                                                                                                                |              |          | 4              |  |  |  |

|        | K10                   | N/A<br>N/A |                                       | NAND IO[2]                   | 1/0        | NAND_IO[2] for NAND Upper I/O port                                                                                                                                |              | <u> </u> | 1              |  |  |  |

|        | J10                   | N/A        | NAND_IO[1]                            |                              | I/O        | NAND_IO[0] for NAND Upper I/O port                                                                                                                                |              |          | 1              |  |  |  |

|        | K6                    | N/A        |                                       | NAND_CLE                     | 0          | NAND Command Latch Enable <sup>[6]</sup>                                                                                                                          | Z            | Z        | SNVDDQ         |  |  |  |

|        | J6                    | N/A        | NAND ALE                              | NAND ALE                     | 0          | NAND Address Latch Enable <sup>[6]</sup>                                                                                                                          | Z            | Z        | VGND           |  |  |  |

|        | J5                    | N/A        | NAND CE#                              | NAND CE#                     | 0          | NAND Chip Enable. Active LOW. <sup>[6]</sup>                                                                                                                      | Z            | Z        | 1              |  |  |  |

|        | K4                    | N/A        | NAND RE#                              | NAND RE#                     | 0          | NAND Read Enable. Active LOW.                                                                                                                                     | Z            | Z        | 1              |  |  |  |

|        | H6                    | N/A        | NAND_WE#                              | NAND WE#                     | 0          | NAND Write Enable. Active LOW.                                                                                                                                    | Z            | Z        | 1              |  |  |  |

|        | J7                    | N/A        | NAND_WP#                              | NAND_WP#                     | 0          | NAND Write Protect. Active LOW. <sup>[6]</sup>                                                                                                                    | Z            | Z        | 1              |  |  |  |

|        | J4                    | N/A        | NAND_R/B#                             | NAND_R/B#                    | I          | NAND Ready/Busy. NAND output is Open Drain.<br>Active LOW.                                                                                                        | -            | -        |                |  |  |  |

|        | K5                    | N/A        | NAND_CE2#                             | NAND_CE2#                    | 0          | NAND Chip Enable 2. Allows to access the second NAND device. Active LOW. <sup>[6]</sup>                                                                           | Z            | Z        |                |  |  |  |

Note

6. The NAND\_CE#, NAND\_CE2#, NAND\_WP#, NAND\_CLE, and NAND\_ALE pins are used as General Purpose Outputs if NAND functionality is not used.

### Table 2. Ball Assignment (continued)

|        | VFBGA                               | WLCSP                                              | Ball Name              | I/O   | Ball Description                                                                                                                                                        | Standby | Reset <sup>[5]</sup> | Power Domain  |  |

|--------|-------------------------------------|----------------------------------------------------|------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|---------------|--|

|        | A5                                  | A4                                                 | D+                     | I/O/Z | USB D+                                                                                                                                                                  | Z       | Z                    |               |  |

| U-port | A6                                  | A5                                                 | D-                     | I/O/Z | USB D-                                                                                                                                                                  | Z       | Z                    | UVDDQ         |  |

| 0-port | A7                                  | B4                                                 | UVALID                 | 0     | External USB Switch Control. Reflects value of register CY_AN_MEM_PMU_UPDATE.UVALID.                                                                                    | Low     | Low                  | UVSSQ         |  |

|        | A8                                  | A2                                                 | XTALIN                 | I     | Input for either crystal or clock signal. XVDDQ is 3.3 V for crystal input; XVDDQ is 1.8 V for clock input.                                                             | -       | -                    | XVDDQ         |  |

|        | B8                                  | N/A                                                | XTALOUT <sup>[8]</sup> | 0     | Output to connect to feedback input of crystal. Is left floating when external clock at XTALIN.                                                                         | Z       | Z                    | VGND          |  |

|        | C10                                 | C2                                                 | RESET#                 | Ι     | Reset. Asserted to place Antioch into reset mode and subsequent initialization. Active LOW.                                                                             | -       | -                    |               |  |

| Others | B10                                 | N/A                                                | RESETOUT               | 0     | Reset Out. Deasserted LOW when RESET# is<br>asserted LOW. Asserted HIGH after RESET# is<br>deasserted and initialization is complete. Reflects<br>value of RSTCMPT bit. | Z       | Low                  |               |  |

|        | C9                                  | D3                                                 | GPIO[1]                | I/O   | General purpose input/output.                                                                                                                                           | Z       | Z                    |               |  |

|        | D8                                  | D2                                                 | GPIO[0]                | I/O   | General purpose input/output.GPIO[0] is used for SD<br>Card Detect with firmware detection. LOW indicates<br>card is inserted.                                          | Z       | Z                    |               |  |

|        | C7                                  | C1                                                 | WAKEUP <sup>[7]</sup>  | I     | Wake Up Signal. 1 = normal operation, 0 = low power<br>"sleep" mode. Is asserted for Antioch to initialize.                                                             | -       | -                    |               |  |

|        | C5                                  | C3                                                 | XTALSLC[1]             | I     | Clock Select. For CYWB0124AB, XTALSLC[1:0] is decoded as: 00 = 19.2 MHz, 01 = 24 MHz, 10 = 48 MHz, 11 = 26 MHz.                                                         | -       | -                    | GVDDQ<br>VGND |  |

|        | C4                                  | C4                                                 | XTALSLC[0]             | i     | Clock Select. For CYWB0124AB, XTALSLC[1:0] is<br>decoded as: 00 = 19.2 MHz, 01 = 24 MHz, 10 = 48<br>MHz, 11 = 26 MHz.                                                   | -       | -                    |               |  |

| Config | C6                                  | N/A                                                | NANDCFG                | I     | S-port Configuration. '0' selects 8-bit NAND and SD/MMC configuration. '1' selects 16-bit NAND configuration.                                                           | -       | -                    |               |  |

|        | E8                                  | B1                                                 | TEST[2]                | I     | Test mode selection. Is tied to VGND for normal operation (CMOS level inputs).                                                                                          | -       | -                    |               |  |

|        | C8                                  | D4                                                 | TEST[1]                | I     | Test mode selection. Is tied to VGND for normal operation (CMOS level inputs).                                                                                          | -       | -                    |               |  |

|        | D7                                  | A1                                                 | TEST[0]                | I     | Test mode selection. Is tied to VGND for normal operation (CMOS level inputs).                                                                                          | -       | -                    |               |  |

|        | D4, H4                              | E5, A6                                             | PVDDQ                  | Power | Power for P-port I/O. 1.8 V, 2.5 V, or 3.3 V nominal.                                                                                                                   | -       | -                    |               |  |

|        | H5                                  | N/A                                                | SNVDDQ                 | Power | Power for NAND port I/O. 1.8 V, 2.5 V, or 3.3 V nominal.                                                                                                                | -       | -                    |               |  |

|        | B5                                  | B5                                                 | UVDDQ                  | Power | Power for USB I/O. 3.3 V nominal.                                                                                                                                       | -       | -                    |               |  |

|        | H7                                  | F1, F3,<br>F4, G5,<br>H4, H5,<br>J2, J3,<br>J4, J5 | SSVDDQ                 | Power | Power for SD port, is connected to SNVDDQ if using 16-bit NAND. 1.8 V, 2.5 V, or 3.3 V nominal.                                                                         | -       | -                    |               |  |

|        | D6                                  | N/A                                                | GVDDQ                  | Power | Power for miscellaneous I/O. 1.8 V, 2.5 V, or 3.3 V nominal.                                                                                                            | -       | -                    |               |  |

| Power  | B9                                  | B3                                                 | AVDDQ                  | Power | Power for internal PLL and USB serializer. 1.8 V nominal.                                                                                                               | -       | -                    |               |  |

|        | B7                                  | N/A                                                | XVDDQ                  | Power | Power for crystal or clock I/O. 1.8 V (clock) or 3.3 V (crystal) nominal.                                                                                               | -       | -                    |               |  |

|        | D5, G4,<br>G5, G6,<br>G7, F7        | D6, F6,<br>G6, J1                                  | V <sub>DD</sub>        | Power | Power for core. 1.8 V nominal.                                                                                                                                          | -       | -                    |               |  |

|        | A10                                 | N/A                                                | VDD33 <sup>[9]</sup>   | Power | Power sequence control supply. 3.3 V nominal.                                                                                                                           | -       | -                    |               |  |

|        | B6                                  | A3                                                 | UVSSQ                  | Power | Ground for all USB.                                                                                                                                                     | -       | -                    |               |  |

|        | A9                                  | B2                                                 | AVSSQ                  | Power | Ground for PLL.                                                                                                                                                         | -       | -                    |               |  |

|        | E4, E5,<br>E6, E7,<br>F4, F5,<br>F6 | B6, D5,<br>E4, E6,<br>F5                           | VGND                   | Power | Ground for core.                                                                                                                                                        | -       | -                    |               |  |

#### Notes

- When RESET# is asserted, the device enters reset state and WAKEUP is ignored

XTALOUT is driven HIGH during Standby mode. XTALOUT operates the same during RESET# assertion and Normal mode: fixed HIGH when XVDDQ is 1.8 V (ext clock) and actively toggles when XVDDQ is 3.3 V (crystal).

VDD33: In CYWB0124AB, the Ball is no-connect internally. It handles power sequence control in future West Bridge products. When migrating to Astoria, it is connected to the highest supply to the device. If USB is used, for example, then VDD33 is connected to nominal 3.3 V (because 3.3 V is required for USB). VDD33 is always supplied in Astoria.

|   |        |        |        | •          | Тор        | View     | •          |            |            |            |   |

|---|--------|--------|--------|------------|------------|----------|------------|------------|------------|------------|---|

|   | 1      | 2      | 3      | 4          | 5          | 6        | 7          | 8          | 9          | 10         |   |

| A | ADV#   | WE#    | INT#   | DRQ#       | D+         | D-       | UVALID     | XTALIN     | AVSSQ      | VDD33      | А |

| В | DQ[1]  | DQ[0]  | OE#    | DACK#      | UVDDQ      | UVSSQ    | XVDDQ      | XTALOUT    | AVDDQ      | RESETOUT   | в |

| С | DQ[4]  | DQ[3]  | DQ[2]  | XTALSLC[0] | XTALSLC[1] | NANDCFG  | WAKEUP     | TEST[1]    | GPIO[1]    | RESET#     | с |

| D | DQ[7]  | DQ[6]  | DQ[5]  | PVDDQ      | VDD        | GVDDQ    | TEST[0]    | GPIO[0]    | SD_D[1]    | SD_D[0]    | D |

| Е | DQ[10] | DQ[9]  | DQ[8]  | VGND       | VGND       | VGND     | VGND       | TEST[2]    | SD_D[3]    | SD_D[2]    | Е |

| F | DQ[13] | DQ[12] | DQ[11] | VGND       | VGND       | VGND     | VDD        | SD_CLK     | SD_D[5]    | SD_D[4]    | F |

| G | CE#    | DQ[15] | DQ[14] | VDD        | VDD        | VDD      | VDD        | SD_CMD     | SD_D[7]    | SD_D[6]    | G |

| н | A[5]   | A[6]   | A[7]   | PVDDQ      | SNVDDQ     | NAND_WE# | SSVDDQ     | SD_POW     | NAND_IO[2] | SD_WP      | н |

| J | A[3]   | CLK    | A[4]   | NAND_R/B#  | NAND_CE#   | NAND_ALE | NAND_WP#   | NAND_IO[5] | NAND_IO[3] | NAND_IO[0] | J |

| к | A[0]   | A[1]   | A[2]   | NAND_RE#   | NAND_CE2#  | NAND_CLE | NAND_IO[7] | NAND_IO[6] | NAND_IO[4] | NAND_IO[1] | к |

|   | 1      | 2      | 3      | 4          | 5          | 6        | 7          | 8          | 9          | 10         |   |

### Figure 3. CYWB0124AB 100 VFBGA – Top View

| POWER DO | POWER DOMAIN KEY |  |  |  |  |  |

|----------|------------------|--|--|--|--|--|

|          | UVDDQ            |  |  |  |  |  |

|          | GVDDQ            |  |  |  |  |  |

|          | SSVDDQ           |  |  |  |  |  |

|          | VGND             |  |  |  |  |  |

|          | PVDDQ            |  |  |  |  |  |

|          | SNVDDQ           |  |  |  |  |  |

|   | 1       | 2       | 3          | 4          | 5      | 6     | 7      | 8      | 9      |   |

|---|---------|---------|------------|------------|--------|-------|--------|--------|--------|---|

| А | TEST[0] | XTALIN  | UVSSQ      | D+         | D-     | PVDDQ | INT#   | OE#    | ADV#   | A |

| в | TEST[2] | AVSSQ   | AVDDQ      | UVALID     | UVDDQ  | VGND  | WE#    | DQ[0]  | DQ[1]  | В |

| С | WAKEUP  | RESET#  | XTALSLC[1] | XTALSLC[0] | DACK#  | DRQ#  | DQ[2]  | DQ[3]  | DQ[4]  | С |

| D | SD_WP   | GPIO[0] | GPIO[1]    | TEST[1]    | VGND   | VDD   | DQ[5]  | DQ[6]  | DQ[7]  | D |

| Е | SD_D[0] | SD_D[1] | SD_D[2]    | VGND       | PVDDQ  | VGND  | DQ[8]  | DQ[9]  | DQ[10] | Е |

| F | SSVDDQ  | SD_D[3] | SSVDDQ     | SSVDDQ     | VGND   | VDD   | DQ[11] | DQ[13] | DQ[12] | F |

| G | SD_CLK  | SD_D[4] | SD_D[5]    | SD_POW     | SSVDDQ | VDD   | DQ[14] | CE#    | DQ[15] | G |

| Н | SD_D[6] | SD_D[7] | SD_CMD     | SSVDDQ     | SSVDDQ | A[4]  | A[3]   | A[1]   | A[0]   | Н |

| J | VDD     | SSVDDQ  | SSVDDQ     | SSVDDQ     | SSVDDQ | A[7]  | A[6]   | A[5]   | A[2]   | J |

|   | 1       | 2       | 3          | 4          | 5      | 6     | 7      | 8      | 9      |   |

### Figure 4. CYWB0124AB 81 WLCSP – Top View

| POWER DOMAIN KEY |            |  |  |  |  |

|------------------|------------|--|--|--|--|

|                  | UVDDQ      |  |  |  |  |

|                  | AVDDQ, VDD |  |  |  |  |

|                  | SSVDDQ     |  |  |  |  |

|                  | VGND       |  |  |  |  |

|                  | PVDDQ      |  |  |  |  |

### Absolute Maximum Ratings

Operating range specifies temperature and voltage boundary conditions for safe operation of the device. Operation outside these boundaries may affect the performance and life of the device. These user guidelines are not tested.

| Storage temperature65 °C to +150 °C                                    |

|------------------------------------------------------------------------|

| Ambient temperature with power supplied (Industrial)40 °C to +85 °C    |

| Supply voltage to ground potential                                     |

| $V_{DD},AVDDQ0.5$ V to +2.0 V                                          |

| GVDDQ, PVDDQ, SSVDDQ, SNVDDQ, UVDDQ and VDD33 and XVDDQ0.5 V to +4.0 V |

| DC input voltage to any input ball1.89 V to 3.6 V                      |

| (Depende on I/O supply veltage, Inputs are not over veltage            |

(Depends on I/O supply voltage. Inputs are not over voltage tolerant.)

### **DC Characteristics**

#### Table 3. DC Specifications for All Voltage Supplies

DC voltage applied to

| outputs in High Z State                                                               | –0.5 V to VDDQ+0.5 V                |

|---------------------------------------------------------------------------------------|-------------------------------------|

| Static discharge voltage (ESD) fro                                                    | m JESD22-A114 > 2000 V              |

| Latch-up current                                                                      | > 200 mA                            |

| Maximum output short circuit curre<br>for all I/O configurations. (V <sub>OUT</sub> = | ∍nt<br>0 V) <sup>[10]</sup> –100 mA |

### **Operating Conditions**

| T <sub>A</sub> (Ambient temperature under bias)<br>Industrial                                     | –40 °C to +85 °C |

|---------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$ , $AV_{DDQ}$ supply voltage                                                              | 1.7 V to 1.9 V   |

| UV <sub>DDQ</sub> supply voltage                                                                  | 3.0 V to 3.6 V   |

| PV <sub>DDQ</sub> , GV <sub>DDQ</sub> , SNV <sub>DDQ</sub> , SSV <sub>DDQ</sub><br>supply voltage | 1.7 V to 3.6 V   |

| XVDDQ (Crystal I/O) supply voltage                                                                |                  |

| XVDDQ (Ext. clock I/O) supply voltage                                                             | 1.7 V to 1.9 V   |

| Parameter                        | Description                                                 | Conditions                             |                    | Min                        | Тур           | Max                       | Unit |

|----------------------------------|-------------------------------------------------------------|----------------------------------------|--------------------|----------------------------|---------------|---------------------------|------|

| V <sub>DD</sub>                  | Core voltage supply                                         |                                        |                    | 1.7                        | 1.8           | 1.9                       | V    |

| AVDDQ                            | Analog voltage supply                                       |                                        |                    | 1.7                        | 1.8           | 1.9                       | V    |

| XVDDQ                            | Crystal voltage supply                                      |                                        |                    | 3.0                        | 3.3           | 3.6                       | V    |

| XVDDQ                            | Clock voltage supply                                        |                                        |                    | 1.7                        | 1.8           | 1.9                       | V    |

| PVDDQ <sup>[12]</sup>            | Processor interface I/O                                     |                                        |                    | 1.7                        | 1.8, 2.5, 3.3 | 3.6                       | V    |

| GVDDQ <sup>[12]</sup>            | Miscellaneous I/O voltage<br>supply                         |                                        |                    | 1.7                        | 1.8, 2.5, 3.3 | 3.6                       | V    |

| SNVDDQ <sup>[12]</sup>           | S-port NAND I/O voltage supply                              |                                        |                    | 1.7                        | 1.8, 2.5, 3.3 | 3.6                       | V    |

| SSVDDQ <sup>[11,12]</sup>        | S-port SD I/O voltage supply                                |                                        |                    | 1.7                        | 1.8, 2.5, 3.3 | 3.6                       | V    |

| UVDDQ <sup>[14]</sup>            | USB voltage supply                                          |                                        |                    | 3.0                        | 3.3           | 3.6                       | V    |

| VDD33                            | Power sequence control supply                               |                                        |                    | 3.0                        | 3.3           | 3.6                       | V    |

| V <sub>IH1</sub> <sup>[13]</sup> | Input HIGH voltage 1                                        | All ports except USB, 2.0 V ≤<br>3.6 V | $\leq V_{CC} \leq$ | 0.625 ×<br>V <sub>CC</sub> |               | V <sub>CC</sub> + 0.3     | V    |

| V <sub>IH2</sub> <sup>[13]</sup> | Input HIGH voltage 2                                        | All ports except USB, 1.7 V ≤<br>2.0 V | ≦V <sub>CC</sub> < | $V_{CC} - 0.4$             |               | V <sub>CC</sub> + 0.3     |      |

| V <sub>IL</sub>                  | Input LOW voltage                                           |                                        |                    | -0.3                       |               | 0.25 ×<br>V <sub>CC</sub> | V    |

| V <sub>OH</sub>                  | Output HIGH voltage                                         | $I_{OH}(MAX) = -0.1 \text{ mA}$        |                    | $0.9 \times V_{CC}$        |               |                           | V    |

| V <sub>OL</sub>                  | Output LOW voltage                                          | $I_{OL}(MIN) = 0.1 \text{ mA}$         |                    |                            |               | $0.1 \times V_{CC}$       | V    |

| I <sub>IX</sub>                  | Input leakage current                                       | All I/O signals held at VDDQ           |                    | -1                         |               | 1                         | μA   |

| I <sub>OZ</sub>                  | Output leakage current                                      | All I/O signals held at VDDQ           |                    | -1                         |               | 1                         | μA   |

| I <sub>CC</sub> Core             | Operating current of core voltage                           | Outputs tri-stated                     | VFBGA              |                            |               | 110                       | mA   |

|                                  | supply (V <sub>DD</sub> ) and analog voltage supply (AVDDQ) |                                        | WLCSP              |                            |               | 115                       |      |

Notes

The SSVDDQ I/O voltage is dynamically changed (for example, from high range to low range) as long as the supply voltage undershoot does not surpass the lower minimum voltage limit. SSVDDQ levels for SD modes: 2.0 V–3.6 V, MMC modes: 1.7 V–3.6 V.

Interfaces with a voltage range are adjustable with respect to the I/O voltage and thus support multiple I/O voltages.

V<sub>CC</sub> = pertinent V<sub>DDQ</sub> value.

When U-port is in a disabled state, UVDDQ goes down to 2.4 V, provided UVDDQ is still the highest supply voltage level.

<sup>10.</sup> Do not test more than one output at a time. Duration of the short circuit does not exceed 1 second. Tested initially, and after any redesign or process changes, may affect these parameters.

### Table 3. DC Specifications for All Voltage Supplies (continued)

| Parameter               | Description                                                                   | Conditions                                                                                                                                                                                                       |                       | Min | Тур                 | Max       | Unit |

|-------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|---------------------|-----------|------|

| I <sub>CC</sub> Crystal | Operating current of crystal voltage supply (XVDDQ) <sup>[17]</sup>           | XTALOUT floating                                                                                                                                                                                                 | VFBGA<br>WLCSP        |     |                     | 5<br>N/A  | mA   |

| I <sub>CC</sub> USB     | Operating current of USB voltage supply (UVDDQ) <sup>[17]</sup>               | Operating and terminated for<br>speed mode                                                                                                                                                                       | <sup>·</sup> high     |     |                     | 25        | mA   |

| I <sub>SB1</sub>        | Total standby current of Antioch<br>when device is in suspend mode            | <ul> <li>Floating<sup>[10]</sup></li> <li>3. XTALOUT Floating</li> <li>4. D+ Floating (no current dr<br/>through internal 1.5 kohm<br/>D– Grounded, UVALID Dr</li> <li>5. Device in Suspend Mode</li> </ul>      | r<br>awn<br>pull-up), |     | 250 <sup>[15]</sup> | 2500      | μΑ   |

| I <sub>SB2</sub>        | Total standby current of Antioch<br>when device is in standby mode            | <ol> <li>*VDDQ = 3.3 V Nominal<br/>(3.0–3.6 V)</li> <li>Outputs and Bidirs High<br/>or Floating<sup>[16]</sup></li> <li>XTALOUT Floating</li> <li>D+ Floating, D–<br/>Grounded, UVALID<br/>Driven LOW</li> </ol> | 25 °C<br>85 °C        |     |                     | 45<br>290 | μΑ   |

| I <sub>SB3</sub>        | Total standby current of Antioch<br>when device is in core power<br>down mode | <ol> <li>Outputs and Bidirs High<br/>or Floating<sup>[16]</sup></li> <li>XTALOUT Floating</li> <li>D+ Floating, D–<br/>Grounded, UVALID<br/>Driven LOW</li> <li>Core Powered Down</li> </ol>                     | 25 °C<br>85 °C        |     |                     | 25<br>139 | μΑ   |

### Table 4. Capacitance

| Parameter        | Description                          | Conditions                         | Тур | Max | Unit |

|------------------|--------------------------------------|------------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input ball capacitance, Except D+/D- | T <sub>A</sub> = 25 °C, f = 1 MHz, |     | 9   | pF   |

|                  | Input ball capacitance, D+/D-        | $V_{CC} = V_{CCIO}$                |     | 15  |      |

| C <sub>OUT</sub> | Output ball capacitance              |                                    |     | 10  | pF   |

### **USB Transceiver**

USB 2.0 compliant in full speed and high speed modes.

#### Notes

15. Isb1 typical value is not a maximum specification but a typical value. Isb1 maximum current value specified for 85 °C.

16. The Outputs/Bidirs that are forced low in Standby mode increases I/O supply standby current beyond specified value.

17. Active Current Conditions:

-UVDDQ: USB transmitting 50% of the time, receiving 50% of the time. -PVDDQ/SNVDDQ/SSVDDQ/GVDDQ: Active Current Depends on I/O activity, bus load, and supply level. -XVDDQ: Assume highest frequency clock (48 MHz) or crystal (26 MHz).

### **AC Characteristics**

### **USB** Transceiver

USB 2.0 compliant in full speed and high speed modes.

### **P-Port Interface**

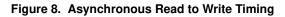

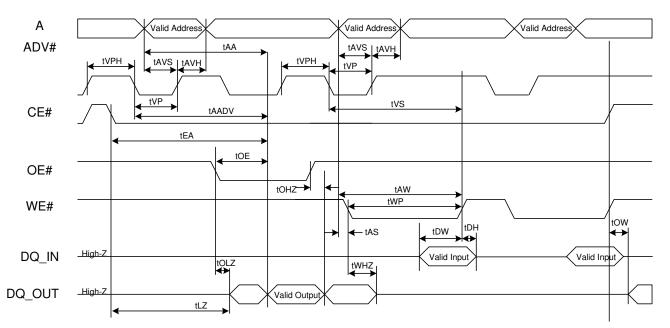

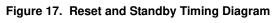

Asynchronous Mode Timing Parameters

### Table 5. Asynchronous Mode Timing Parameters

| Parameter    | ter Description                      |                    | Max  | Unit |

|--------------|--------------------------------------|--------------------|------|------|

| Read Timing  | Parameters                           |                    |      |      |

| tAA          | Address to data valid                |                    | 30   | ns   |

| tOH          | Data output hold from address change | 3                  |      | ns   |

| tEA          | Chip enable to data valid            |                    | 30   | ns   |

| tAADV        | ADV# to data valid access time       |                    | 30   | ns   |

| tAVS         | Address valid to ADV# HIGH           | 5                  |      | ns   |

| tAVH         | ADV# HIGH to address hold            | 2 <sup>[19]</sup>  |      | ns   |

| tCVS         | CE# low setup time to ADV# HIGH      | 5                  |      | ns   |

| tVPH         | ADV# HIGH time                       | 15 <sup>[18]</sup> |      | ns   |

| tVP          | ADV# pulse width LOW                 | 7.5                |      | ns   |

| tOE          | OE# LOW to data valid                |                    | 22.5 | ns   |

| tOLZ         | OE# LOW to Low Z                     | 3                  |      | ns   |

| tOHZ         | OE# HIGH to High Z                   | 0                  | 22.5 | ns   |

| tLZ          | CE# LOW to Low Z                     | 3                  |      | ns   |

| tHZ          | CE# HIGH to High Z                   |                    | 22.5 | ns   |

| Write Timing | Parameters                           | •                  |      |      |

| tCW          | CE# LOW to write end                 | 30                 |      | ns   |

| tAW          | Address valid to write end           | 30                 |      | ns   |

| tAS          | Address setup to write start         | 0                  |      | ns   |

| tADVS        | ADV# setup to write start            | 0                  |      | ns   |

| tWP          | WE# pulse width                      | 22                 |      | ns   |

| tWPH         | WE# HIGH time                        | 10                 |      | ns   |

| tCPH         | CE# HIGH time                        | 10                 |      | ns   |

| tAVS         | Address valid to ADV# HIGH           | 5                  |      | ns   |

| tAVH         | ADV# HIGH to address hold            | 2 <sup>[18]</sup>  |      | ns   |

| tCVS         | CE# LOW setup time to ADV# HIGH      | 5                  |      | ns   |

| tVPH         | ADV# HIGH time                       | 15 <sup>[18]</sup> |      | ns   |

| tVP          | ADV# pulse width LOW                 | 7.5                |      | ns   |

| tVS          | ADV# LOW to end of write             | 30                 |      | ns   |

| tDW          | Data setup to write end              | 18                 |      | ns   |

| tDH          | Data hold from write end             | 0                  |      | ns   |

| tWHZ         | WE# low to DQ High Z output          |                    | 22.5 | ns   |

| tWLZ         | WE# high to DQ Low Z output          | 3                  |      | ns   |

Notes 18. In applications where access cycle time is at least 60 ns, t<sub>VPH</sub> is relaxed to 12 ns. 19. In applications where back-to-back accesses are not performed on different endpoint addresses, the minimum t<sub>AVH</sub> specification is relaxed to 0 ns.

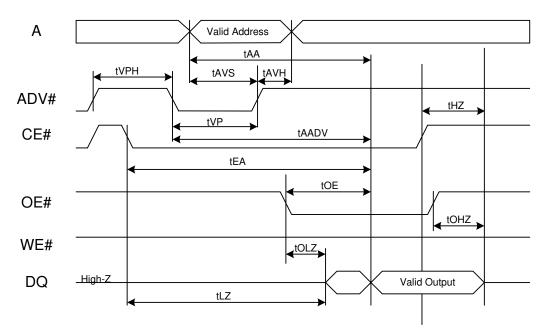

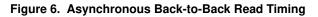

Figure 5. Asynchronous Single Read Timing

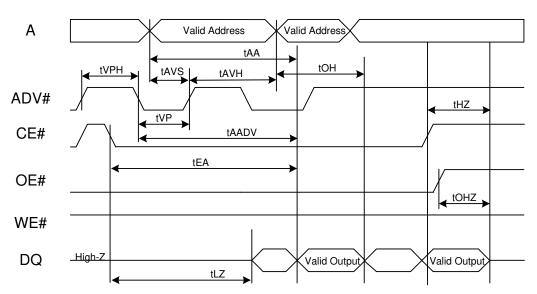

Figure 7. Asynchronous Back-to-Back Write Timing

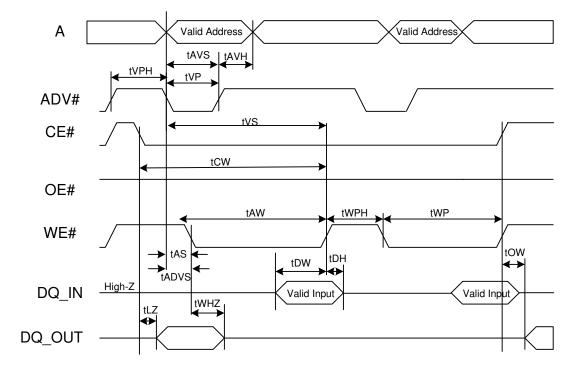

Figure 9. Asynchronous Write to Read Timing

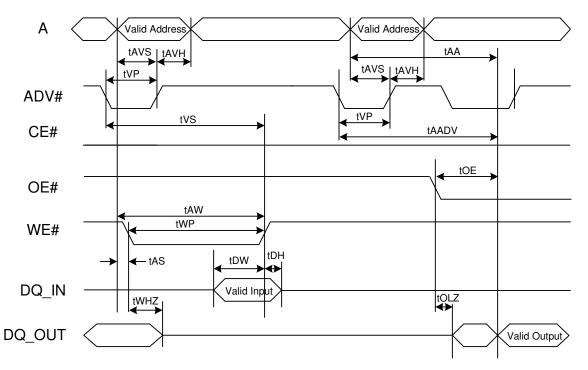

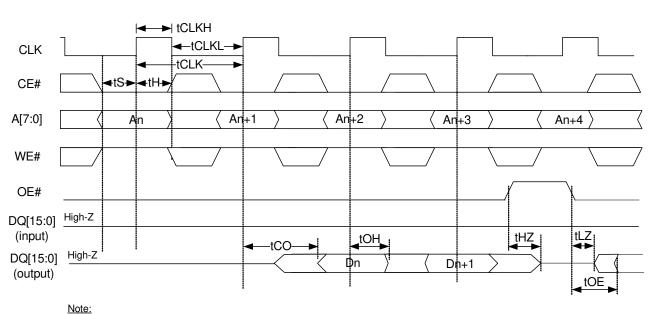

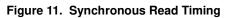

### Synchronous Mode Timing Parameters

### Table 6. Synchronous Mode Timing Parameters

| Parameter | Description                                 | Conditions                                                                                                                 | Min | Max  | Unit |

|-----------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| FREQ      | Interface Clock Frequency                   |                                                                                                                            |     | 33   | MHz  |

| tCLK      | Clock Period                                |                                                                                                                            | 30  |      | ns   |

| tCLKH     | Clock HIGH Time                             |                                                                                                                            | 12  |      | ns   |

| tCLKL     | Clock LOW Time                              |                                                                                                                            | 12  |      | ns   |

| tS        | CE#/WE#/ADDR/DQ Setup Time                  |                                                                                                                            | 7.5 |      | ns   |

| tH        | CE#/WE#/ADDR/DQ Hold Time                   |                                                                                                                            | 1.5 |      | ns   |

| tCO       | Clock to Valid Data                         |                                                                                                                            |     | 18   | ns   |

| tOH       | Clock to Data Hold Time                     |                                                                                                                            | 2   |      | ns   |

| tHZ       | OE# HIGH to Data High Z                     |                                                                                                                            |     | 22.5 | ns   |

| tLZ       | OE# LOW to Data Low Z                       |                                                                                                                            | 3   |      | ns   |

| tOE       | OE# LOW to Data Valid                       |                                                                                                                            |     | 22.5 | ns   |

| tWHZ      | WE# Low to DQ High Z Output                 |                                                                                                                            |     | 22.5 | ns   |

| tWLZ      | WE# High to DQ Low Z Output                 |                                                                                                                            | 3   |      | ns   |

| tCKHZ     | Clock to Data High Z (Figure 13 on page 19) | Measured from the rising edge of the second clock after the deassertion of CE# is latched by the rising edge of the clock. |     | 18   | ns   |

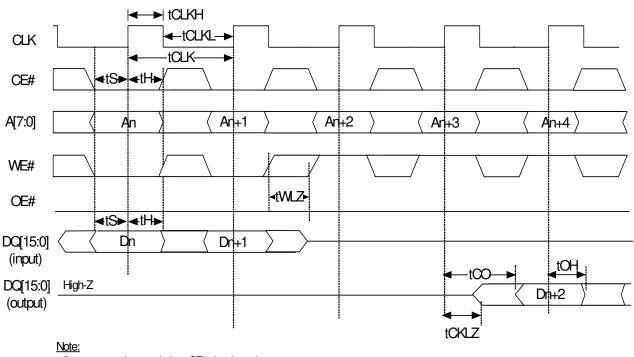

| tCKLZ     | Clock to Data Low Z (Figure 15 on page 20)  |                                                                                                                            | 3   |      | ns   |

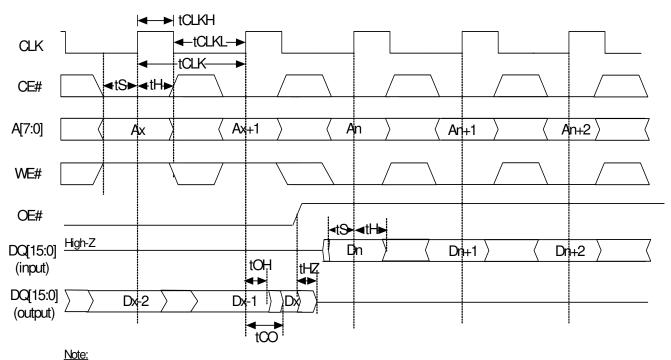

Figure 10. Synchronous Write Timing

Note: - Assumes previous cycle had CE# deselected - OE# is don't care during write operations

- Assumes previous cycle had CE# deselected

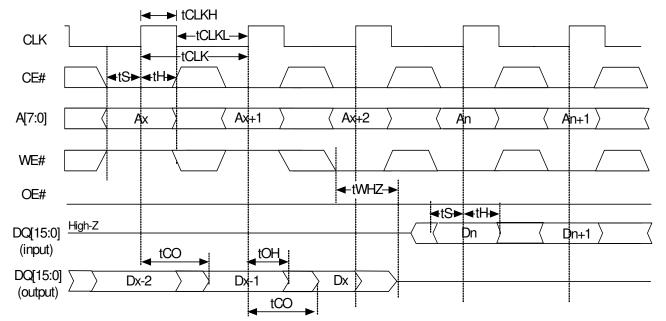

Figure 12. Synchronous Read (OE# Fixed LOW) Timing

- Assumes previous several cycles were Read