## **Datasheet**

DS000587

# **AS6031**

## **SoC for Ultrasonic Flow Meters**

v1-00 • 2020-May-06

# **Content Guide**

| 1                                      | General Description                                                                                    | 4                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------|

| 1.1<br>1.2<br>1.3                      | Key Benefits & Features<br>Applications<br>Block Diagram                                               | 5                            |

| 2                                      | Ordering Information                                                                                   | 7                            |

| 3                                      | Pin Assignment                                                                                         | 8                            |

| 3.1<br>3.2                             | Pin Diagram<br>Pin Description                                                                         |                              |

| 4                                      | Absolute Maximum Ratings                                                                               | 11                           |

| 5                                      | Electrical Characteristics                                                                             | 13                           |

| 5.1<br>5.2<br>5.3<br>5.4               | Ultrasonic Frontend Time-to-Digital Converter Temperature Measuring Unit Supply Voltage Measuring Unit | . 16<br>. 16                 |

| 6                                      | Timing Characteristics                                                                                 | 18                           |

| 6.1<br>6.2                             | SPI Interface2-wire Master Interface                                                                   |                              |

| 7                                      | Typical Operating Characteristic                                                                       |                              |

| _                                      |                                                                                                        |                              |

| 8                                      | Functional Description                                                                                 |                              |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | System Concept                                                                                         | . 24<br>. 26<br>. 38<br>. 41 |

| 9                                      | Special Functions                                                                                      | 69                           |

| 9.1<br>9.2                             | Time Stamp (RTC)                                                                                       |                              |

| 9.3<br>9.4<br>9.5<br>9.6               | Backup                                                                                                 | . 70<br>. 71<br>. 71         |

| 9.4<br>9.5                             | WatchdogSupply Voltage MeasurementError Handling                                                       | . 70<br>. 71<br>. 71<br>. 73 |

| 11                                           | CPU                                                                                                                                                                | 85                              |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6 | Registers and Accumulators CPU Flags Arithmetic Operations Instruction Set Libraries and pre-defined routines CPU Handling Assembler                               | 86<br>86<br>87<br>88            |

| 12                                           | Memory and Register Descripti                                                                                                                                      |                                 |

| 12.1<br>12.2<br>12.3                         | Program AreaRandom Access Area (RAA) Detailed Register Description                                                                                                 | 101<br>102                      |

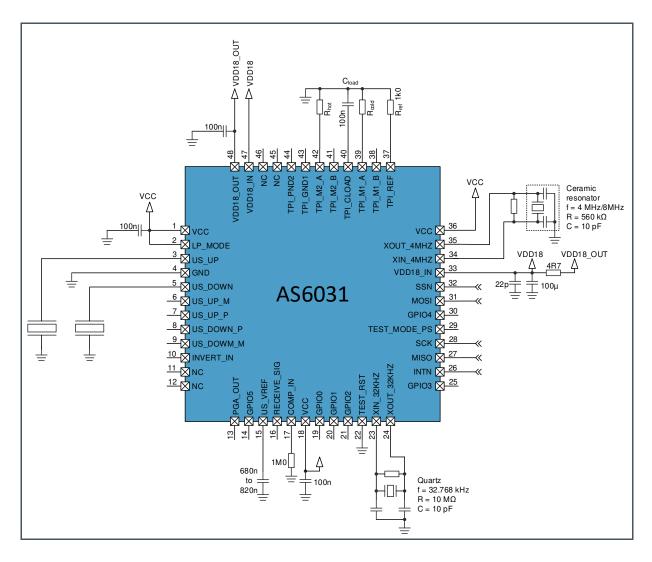

| 13                                           | Application Information                                                                                                                                            | . 144                           |

| 13.1<br>13.2                                 | Schematic<br>External Components                                                                                                                                   |                                 |

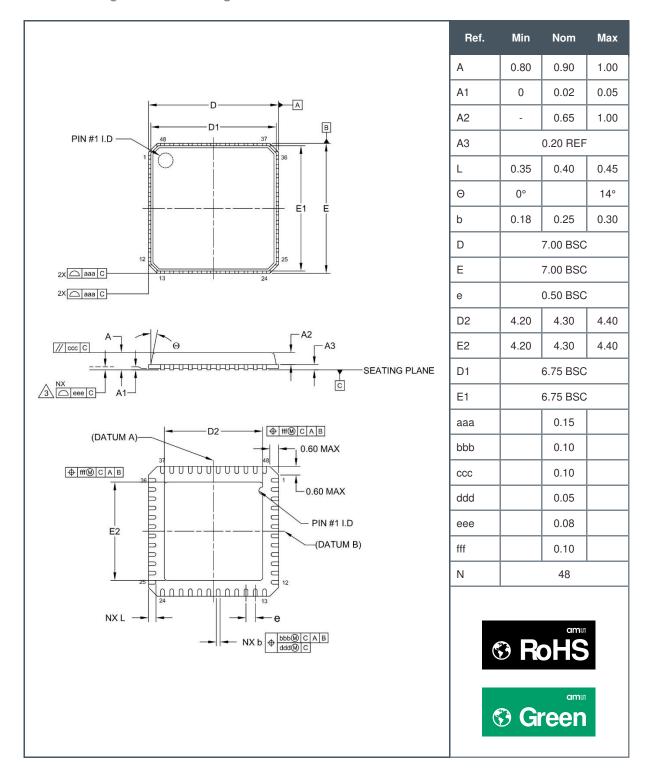

| 14                                           | Package Drawings & Markings                                                                                                                                        | . 146                           |

| 15                                           | Appendix                                                                                                                                                           | . 148                           |

| 15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6 | Notational Conventions  Abbreviations  Glossary  CPU Commands in Detail  ROM Routines in Detail  Amplitude Calculation  Measurement Start in Time Conversion  Mode | 148<br>150<br>155<br>179<br>194 |

| 16                                           | Known Errors                                                                                                                                                       | . 203                           |

| 16.1                                         | Amplitude Measurement                                                                                                                                              |                                 |

| 17                                           | Revision Information                                                                                                                                               | . 204                           |

| 18                                           | Legal Information                                                                                                                                                  | . 205                           |

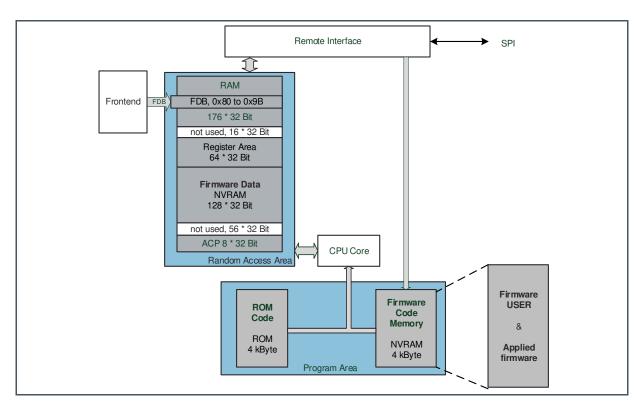

# 1 General Description

AS6031 is an ultrasonic flow converter for the next generations of ultrasonic water and heat meters. It is highly integrated and is based on the TDC-GP30 platform. It uses the same high-performant frontend for driving the transducers and processing the receive signal to extract the time of flight information. An additional programmable amplifier allows handling weaker receive amplitudes. Additional features for phase-modulated hit identification give even more robustness to the first hit level detection. The integrated low-power CPU can use 4k of NVRAM and 4k of ROM code to do the flow calculation on chip.

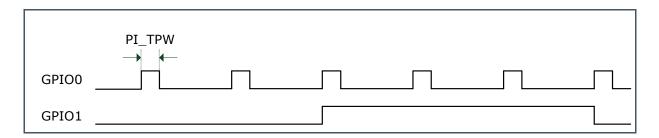

AS6031 simplifies the design of ultrasonic water and heat meters, combining the precise measurement and the complex flow calculation. It provides outstanding low-flow detection capability due to excellent zero-flow drift. Users can apply any of-the-shelf  $\mu P$  for handling all other tasks like display management or wireless communication and a complete meter device. The integrated standard pulse interface enables one-to-one replacement of mechanical meters by AS6031 based single-chip heat and water meters – customer  $\mu P$  and software remains unchanged.

The ultra-low-current capabilities allow the use of standard AA batteries at 6-8 Hz measuring frequency even in the water meter version. The chip comes in a compact QFN48 package and allows compact designs thanks to a small number of external components.

## 1.1 Key Benefits & Features

The benefits and features of AS6031, SoC for Ultrasonic Flow Meters are listed below:

Figure 1: Added Value of Using AS6031

| Benefits                                                                                                                                                                                             | Features                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Single-chip solution provides ready flow information  System design compatible with mechanical meters  High flexibility in choice for external µP handling communication and further data management | High performance + ultra-low power 32-Bit CPU                                                                          |

|                                                                                                                                                                                                      | 120 * 32-bit NVRAM (non-volatile RAM) for user firmware parameter & data                                               |

|                                                                                                                                                                                                      | 3968 * 8-bit NVRAM (non-volatile RAM) for user firmware program code                                                   |

|                                                                                                                                                                                                      | 4k * 8-bit ROM for system task code and special flow library code                                                      |

| Precision down to low flow rates                                                                                                                                                                     | Advanced high-precision analog front-end for transducer frequencies of 50 kHz to 4 MHz at 2.5 V to 3.6 V drive voltage |

| Leakage detection                                                                                                                                                                                    | Integrated PGA, gain 2 to 17 V/V @ 1 MHz                                                                               |

| Benefits                                                            | Features                                                                                                                  |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Handles weak signals for small transducers and multiple reflections | First hit level and phase detection                                                                                       |

| multiple relications                                                | Amplitude measurement                                                                                                     |

|                                                                     | Up to 31 zero crossing measurements                                                                                       |

|                                                                     | Precision time-to-digital converter and low-noise front-end with < 50 ps single shot with good 1MHz transducers on a DN20 |

|                                                                     | Ultra-low power consumption                                                                                               |

|                                                                     | SPI serial interface                                                                                                      |

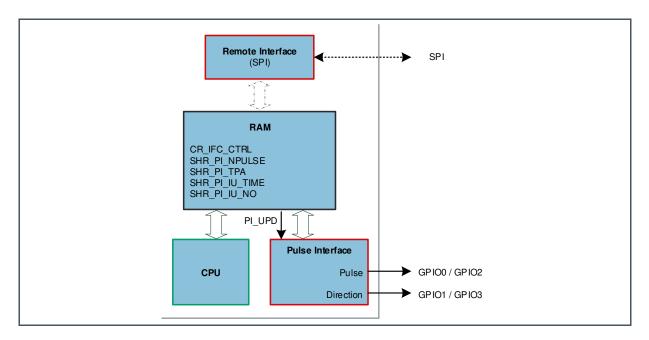

| Compact design                                                      | General Purpose I/O Unit incl. pulse interface and 2-wire master interface (I2C like)                                     |

| Low BOM                                                             | Supply voltage 2.5 <sup>(1)</sup> to 3.6 V                                                                                |

|                                                                     | 3.0 to 3.6 V NVRAM store only                                                                                             |

|                                                                     | Operating temperature -40 <sup>(1)</sup> to 85°C                                                                          |

|                                                                     | QFN48 package (7 x 7mm²)                                                                                                  |

(1) With workaround or limitation in combinations

# 1.2 Applications

- Water meters for utilities

- Industrial water meters

- Heat meters

- Gas meters

- Volume counters

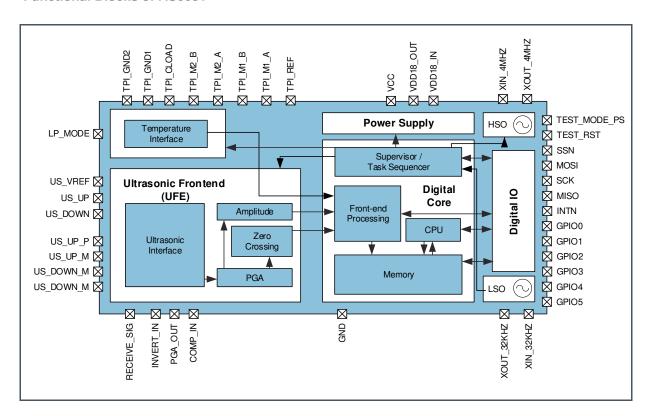

## 1.3 Block Diagram

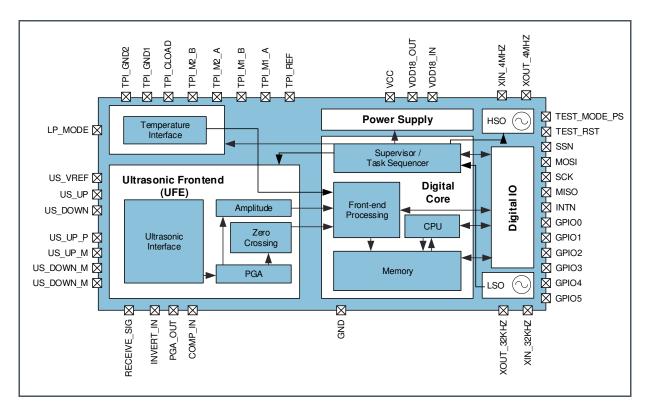

The functional blocks of this device are shown below:

Figure 2 : Functional Blocks of AS6031

# 2 Ordering Information

| Ordering Code | Package | Marking    | Delivery Form | Delivery Quantity |

|---------------|---------|------------|---------------|-------------------|

| AS6031-BQFM   | QFN48   | AS6031-BQF | Tape & Reel   | 500 pcs/reel      |

# 3 Pin Assignment

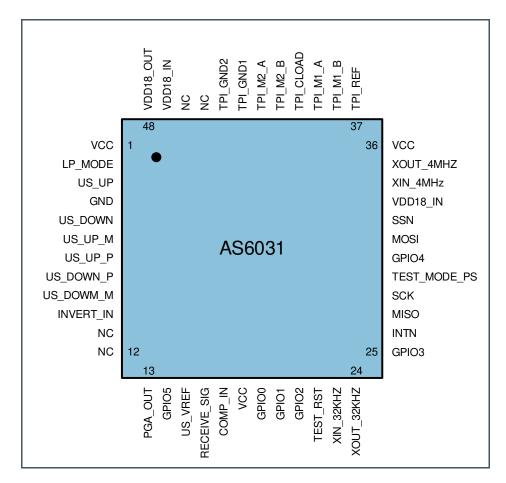

## 3.1 Pin Diagram

Figure 3: AS6031 Pin Diagram

## 3.2 Pin Description

Figure 4: Pin Description of AS6031

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                          |

|------------|----------|-------------------------|--------------------------------------|

| 1          | VCC      | S                       | IO & Analog Supply                   |

| 2          | LP_MODE  | DI                      | Low Power Mode, fix internal pull-up |

| Pin Number | Pin Name     | Pin Type <sup>(1)</sup> | Description                                   |

|------------|--------------|-------------------------|-----------------------------------------------|

| 3          | US_UP        | AIO                     | Transducer Port LV interface                  |

| 4          | GND          | S                       | Ground                                        |

| 5          | US_DOWN      | AIO                     | Transducer Port LV interface                  |

| 6          | US_UP_M      | AIO                     | Not used                                      |

| 7          | US_UP_P      | AIO                     | Not used                                      |

| 8          | US_DOWN_P    | AIO                     | Not used                                      |

| 9          | US_DOWN_M    | AIO                     | Not used                                      |

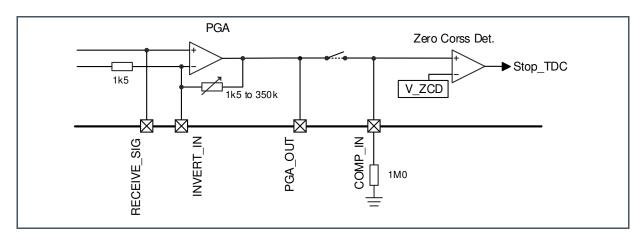

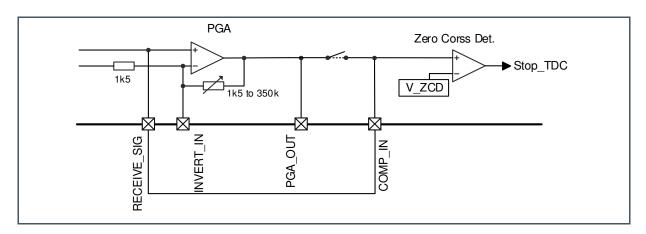

| 10         | INVERT_IN    | AIO                     | Inverting Input PGA                           |

| 11         | NC           |                         |                                               |

| 12         | NC           |                         |                                               |

| 13         | PGA_OUT      | AIO                     | Output PGA                                    |

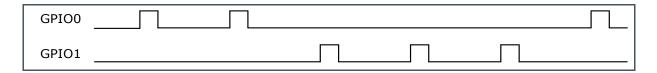

| 14         | GPIO5        | DIO                     | General Purpose 5, optional pull-up/pull-down |

| 15         | US_VREF      | AIO                     | Ultrasonic Reference Voltage                  |

| 16         | RECEIVE_SIG  | AIO                     | Receive Signal                                |

| 17         | COMP_IN      | AIO                     | Comparator Input                              |

| 18         | VCC          |                         | IO & Analog Supply                            |

| 19         | GPIO0        | DIO                     | General Purpose 0, optional pull-up/pull-down |

| 20         | GPIO1        | DIO                     | General Purpose 1, optional pull-up/pull-down |

| 21         | GPIO2        | DIO                     | General Purpose 2, optional pull-up/pull-down |

| 22         | TEST_RST     | DI                      | Test Reset, must be connected to GND          |

| 23         | XIN_32KHZ    | AIO                     | Low Speed Oscillator                          |

| 24         | XOUT_32KHZ   | AIO                     | Low Speed Oscillator                          |

| 25         | GPIO3        | DIO                     | General purpose 3, optional pull-up/pull-down |

| 26         | INTN         | DO                      | Interrupt, low active                         |

| 27         | MISO         | DO                      | SPI: Slave Out with tristate                  |

| 28         | SCK          | DI <sup>(2)</sup>       | SPI: Serial Clock                             |

| 29         | TEST_MODE_PS | DI                      | Test Mode, fix internal pull-down             |

| 30         | GPIO4        | DIO                     | General Purpose 4, optional pull-up/pull-down |

| 31         | MOSI         | DI <sup>(2)</sup>       | SPI: Slave In                                 |

| 32         | SSN          | DI <sup>(2)</sup>       | SPI: Slave Select, low active                 |

| 33         | VDD18_IN     | S                       | VDD18 Digital Core Supply                     |

| 34         | XIN_4MHZ     | AIO                     | High Speed Oscillator                         |

| 35         | XOUT_4MHZ    | AIO                     | High Speed Oscillator                         |

| 36         | VCC          | S                       | IO & Analog Supply                            |

| 37         | TPI_REF      | AIO                     | Temperature Interface: Ref. Port              |

|            |              |                         |                                               |

| Pin Number | Pin Name  | Pin Type <sup>(1)</sup> | Description                       |

|------------|-----------|-------------------------|-----------------------------------|

| 38         | TPI_M1_B  | AIO                     | Temperature Interface: Port M1 B  |

| 39         | TPI_M1_A  | AIO                     | Temperature Interface: Port M1 A  |

| 40         | TPI_CLOAD | AIO                     | Temperature Interface: Port CLOAD |

| 41         | TPI_M2_B  | AIO                     | Temperature Interface: Port M2 B  |

| 42         | TPI_M2_A  | AIO                     | Temperature Interface: Port M2 A  |

| 43         | TPI_GND1  |                         | Temperature Interface: Ground1    |

| 44         | TPI_GND2  |                         | Temperature Interface: Ground2    |

| 45         | NC        |                         |                                   |

| 46         | NC        |                         |                                   |

| 47         | VDD18_IN  | S                       | VDD18 Digital Core Supply         |

| 48         | VDD18_OUT | S                       | VDD18 Voltage Regulator Output    |

(1) Explanation of abbreviations:

DI Digital Input AIO Analog Input/Output

DO Digital Output S Supply

DIO Digital Input/Output

For standalone operation without exteri

(2) For standalone operation without external controller, the unconnected inputs should be configured with internal pull up by SPI\_INPORT\_CFG in CR\_IFC\_CTRL.

# 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5

Absolute Maximum Ratings of AS6031

| Symbol                   | Parameter                                                               | Min      | Max            | Unit   | Comments                                                                                 |

|--------------------------|-------------------------------------------------------------------------|----------|----------------|--------|------------------------------------------------------------------------------------------|

| Electrical Par           | ameters                                                                 |          |                |        |                                                                                          |

| V <sub>CC</sub>          | Supply Voltage to Ground                                                | -0.3     | 4.0            | V      |                                                                                          |

| V <sub>oth</sub>         | All other Pins Voltage to Ground                                        | -0.3     | $V_{CC} + 0.6$ | V      |                                                                                          |

| Electrostatic            | Discharge                                                               |          |                |        |                                                                                          |

| ESD <sub>HBM</sub>       | Electrostatic Discharge HBM                                             | <u>+</u> | : 1k           | V      | JS-001-2017                                                                              |

| ESD <sub>CDM</sub>       | Electrostatic Discharge CDM                                             | ±        | 0.5k           | V      | JS-002-2018                                                                              |

| Temperature              | Ranges and Storage Conditions                                           |          |                |        |                                                                                          |

| T <sub>STRG</sub>        | Storage Temperature Range                                               | - 55     | 150            | °C     |                                                                                          |

| T <sub>BODY</sub>        | Package Body Temperature                                                |          | 260            | °C     | IPC/JEDEC J-STD-020 (1)                                                                  |

| RH <sub>NC</sub>         | Relative Humidity (non-<br>condensing)                                  | 5        | 85             | %      |                                                                                          |

| MSL                      | Moisture Sensitivity Level                                              |          | 1              |        | Maximum floor lifetime of 168h                                                           |

| tstrg_dof                | Storage Time for DOF/Die or<br>Wafers on Foil                           |          | 3              | months | Refers to indicated date of packing                                                      |

| T <sub>STRG_DOF</sub>    | Storage Temperature for DOF/Die or Wafers on Foil                       | 17       | 28             | °C     |                                                                                          |

| RH <sub>OPEN_DOF</sub>   | Relative Humidity for DOF/Die or Wafers on Foil in Open Package         |          | 15             | %      | Opened package                                                                           |

| RH <sub>UNOPEN_DOF</sub> | Relative Humidity for DOF/Die<br>or Wafers on Foil in Sealed<br>Package | 40       | 60             | %      | Sealed bag                                                                               |

| t <sub>STRG_WP</sub>     | Storage Time for WP/Wafers or Die in Waffle Pack                        |          | 6              | months | 17 °C – 28 °C<br>40 % – 60 % relative<br>humidity storage in<br>original Ultrapack boxes |

| t <sub>STRG_WP</sub>     | Storage Time for WP/Wafers or Die in Waffle Pack                        |          | 2              | years  | 19 °C – 25 °C<br><15 % relative humidity<br>storage in closed cabinet<br>with dry air    |

| t <sub>STRG_WP</sub>     | Storage Time for WP/Wafers or Die in Waffle Pack                        |          | 5              | years  | 19 °C – 25 °C<br><5 % relative humidity<br>storage in closed cabinet<br>with dry air     |

| Symbol               | Parameter                                        | Min | Max | Unit  | Comments                                                                                                                                   |

|----------------------|--------------------------------------------------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>STRG_WP</sub> | Storage Time for WP/Wafers or Die in Waffle Pack |     | 10  | years | 19 °C – 25 °C<br><5 % relative humidity<br>storage in closed cabinet<br>and closed Ultrapak box<br>with safeguarded Nitrogen<br>atmosphere |

| Bump Temp            | erature (soldering)                              |     |     |       |                                                                                                                                            |

| T <sub>PEAK</sub>    | Peak Temperature                                 | 235 | 245 | °C    | Solder Profile                                                                                                                             |

| twell                | Well Time above 217 °C                           | 30  | 45  | S     |                                                                                                                                            |

<sup>(1)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid-State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100 % Sn)

# 5 Electrical Characteristics

Electrical characteristics and operating conditions indicate conditions for which the device is functional, but do not guarantee specific performance limits. Test conditions for guaranteed specification are expressly denoted.

All data given at  $V_{CC} = 3.0 \text{ V} \pm 0.3 \text{ V}$ , ambient temperature -10 °C to 85 °C unless otherwise specified.

Notes (a) to (e) that describe the test levels are valid for the whole sections 5 and 6.

Figure 6: Recommended operating conditions of AS6031

| Symbol             | Parameter                                            | Conditions                                                                | Min          | Тур            | Max               | Unit     |

|--------------------|------------------------------------------------------|---------------------------------------------------------------------------|--------------|----------------|-------------------|----------|

| Power Supply       |                                                      |                                                                           |              |                |                   |          |

| V <sub>CC</sub>    | Supply Voltage to Ground <sup>(a)</sup>              | All operations besides<br>NVRAM store                                     | 2.5          | 3.0            | 3.6               | V        |

|                    |                                                      | Only for NVRAM store                                                      | 3.0          | 3.0            | 3.6               | V        |

| $V_{DD18}$         | Core Voltage to<br>Ground <sup>(a)</sup>             |                                                                           | 1.71         | 1.8            | 1.89              | V        |

| T <sub>A</sub>     | Operating ambient temperature                        |                                                                           | -40          |                | +85               | °C       |

| Oscillators        |                                                      |                                                                           |              |                |                   |          |

| f <sub>LSO</sub>   | Low speed oscillator (LSO) frequency <sup>(e)</sup>  |                                                                           |              | 32.768         |                   | kHz      |

|                    | High-speed oscillator (HSO) frequency <sup>(e)</sup> | For standard transducers, max. 2 MHz,                                     |              | 4              |                   | MHz      |

| $f_{\text{HSO}}$   |                                                      | For max. 4 MHz transducers                                                |              | 8              |                   | MHz      |

|                    | (rise) inequality                                    | Other frequencies in the range limitations                                | e from 2 MHz | z to 8.8 MHz r | nay be possil     | ble with |

| f <sub>SPI</sub>   | SPI Interface<br>Clock Frequency <sup>(d)</sup>      |                                                                           |              |                | 8                 | MHz      |

| f <sub>TOF</sub>   | TOF measurement frequency <sup>(e)</sup>             | $f_{TOF} = \frac{1}{(TOF\_RATE * t_{cycle})}$                             | 0.004        | 1 to 8         | 80 <sup>(1)</sup> | Hz       |

| t <sub>cycle</sub> | Measurement rate cycle time <sup>(d)</sup>           | Measurement cycle time 1 LSB = LP_MODE = 0: 1 ms LP_MODE = 1: 976.5625 μs |              |                | 1024<br>1000      | ms       |

| f <sub>CPU</sub>   | CPU clock frequency <sup>(c)</sup>                   | T <sub>a</sub> = 25 °C, V <sub>DD</sub> = 1.8 V                           |              | 13             |                   | MHz      |

<sup>(</sup>a) 100% production tested

<sup>(</sup>b) 100% production tested at 85°C wafer sort and guaranteed by design and characterization at specified temperatures.

<sup>(</sup>c) Sample tested only

<sup>(</sup>d) Parameter is guaranteed by design and characterization testing

<sup>(</sup>e) Parameter is a typical value only

<sup>(1)</sup> Maximum value with limited functionality only, e.g. no 20 ms delay between up and down measurements.

Figure 7: DC Characteristics (Vcc = 3.0 V,  $T_j$  = -40 to +85 °C) of AS6031

| Symbol           | Parameter                                                                              | Conditions                                                                     | Min                                                  | Тур | Max                             | Unit |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------|-----|---------------------------------|------|

| L                | Supply current only<br>32 kHz, Standby                                                 | only 32 kHz oscillator running @ 25 °C,                                        |                                                      |     |                                 |      |

| Standby          | mode <sup>(e)</sup>                                                                    | VCC = 3.6 V                                                                    |                                                      | 3.6 |                                 | μΑ   |

|                  |                                                                                        | = 3.0 V                                                                        |                                                      | 2.2 |                                 | μΑ   |

|                  | Operation current 4                                                                    | VCC = 3.6 V                                                                    |                                                      | 80  |                                 | μΑ   |

| I <sub>hs</sub>  | MHz oscillator <sup>(e)</sup>                                                          | = 3.0 V                                                                        |                                                      | 65  |                                 | μΑ   |

|                  |                                                                                        | off                                                                            |                                                      | <1  |                                 | μΑ   |

| I <sub>tmu</sub> | Current into time<br>measuring unit<br>including ultrasonic<br>frontend <sup>(e)</sup> | Only during active TOF time measurement                                        |                                                      | 1.7 |                                 | mA   |

| I <sub>PGA</sub> | Current into PGA <sup>(e)</sup>                                                        | When active                                                                    |                                                      | 0.9 |                                 | mA   |

| I <sub>UFE</sub> | Average operating current ultrasonic front end only <sup>(e)</sup>                     | TOF_UP+DOWN, 8Hz<br>3V, 75μs ToF<br>See also section 7                         |                                                      | 5.5 |                                 | μΑ   |

| Io               | Average operating current <sup>(e)</sup> incl. CPU processing current                  | TOF_UP+DOWN, 8 Hz<br>3V, 75µs ToF,<br>phase detection FW<br>see also section 7 |                                                      | 9.2 |                                 | μΑ   |

| $V_{oh}$         | High level output voltage <sup>(a)</sup>                                               | I <sub>oh</sub> = 4 mA                                                         | V <sub>CC</sub> - 0.4                                |     |                                 | V    |

| V <sub>ol</sub>  | Low level output voltage <sup>(a)</sup>                                                | I <sub>oh</sub> = 4 mA                                                         |                                                      |     | 0.4                             | V    |

| $V_{ih}$         | Logic high level input voltage <sup>(a)</sup>                                          | for proper logic function for low leakage current                              | 0.7 *<br>V <sub>CC</sub><br>V <sub>CC</sub> -<br>0.2 |     |                                 | V    |

| V <sub>il</sub>  | Logic low level input voltage <sup>(a)</sup>                                           | for proper logic function for low leakage current                              |                                                      |     | 0.3 *<br>V <sub>CC</sub><br>0.2 | V    |

Figure 8: Terminal Capacitance

| Symbol          | Terminal                      | Conditions                           | Min | Тур | Max | Unit |

|-----------------|-------------------------------|--------------------------------------|-----|-----|-----|------|

| Ci              | Digital input(e)              | measured @ VCC = 3.0 V<br>f = 1 MHz, |     | 7   |     |      |

| C <sub>o</sub>  | Digital output <sup>(e)</sup> |                                      |     | 7   |     | pF   |

| C <sub>io</sub> | Bidirectional <sup>(e)</sup>  | Ta = 25 °C                           |     | 7   |     |      |

Figure 9: NVRAM

| Symbol | Parameter                     | Conditions                                             | Min | Тур             | Max | Unit   |

|--------|-------------------------------|--------------------------------------------------------|-----|-----------------|-----|--------|

|        | Data Retention <sup>(d)</sup> | @ 85 °C, V <sub>CC</sub> = 3.0 <sup>(1)</sup> to 3.6 V |     | 20              |     | Years  |

|        | Endurance <sup>(d)</sup>      | @ 25 °C, $V_{CC}$ = 3.0 <sup>(1)</sup> to 3.6 V        |     | 10 <sup>5</sup> |     | Cycles |

|        |                               | @ 85 °C, V <sub>CC</sub> = 3.0 <sup>(1)</sup> to 3.6 V |     | 10 <sup>4</sup> |     | Cycles |

<sup>(1)</sup> Lower limit of 3.0V is valid only for STORE. Can be lower during operation without store.

## 5.1 Ultrasonic Frontend

Figure 10: Ultrasonic Frontend

| Symbol                 | Parameter                                                             | Conditions                     |                 | Min  | Тур                  | Max                            | Unit          |

|------------------------|-----------------------------------------------------------------------|--------------------------------|-----------------|------|----------------------|--------------------------------|---------------|

|                        | Output Voltage<br>High <sup>(d)</sup>                                 | Signal Offset = 1/2            | V <sub>CC</sub> |      | ±1/4 V <sub>CC</sub> | $\pm \frac{1}{2} V_{CC}^{(1)}$ | V             |

|                        | Received Signal<br>Amplitude at<br>COMP_IN w/o PGA <sup>(d)</sup>     | Signal Offset = V <sub>R</sub> | EF              | ±100 | ±400                 | $\pm V_{REF}$                  | mV            |

|                        | Received Signal<br>Amplitude at<br>COMP_IN with<br>PGA <sup>(d)</sup> | Signal Offset = V <sub>R</sub> | EF              | ±100 | ±400                 | ±600                           | mV            |

|                        | Accuracy, Amplitude<br>Measurement <sup>(e)</sup>                     |                                |                 |      | ±10 <sup>(2)</sup>   |                                | mV            |

| V <sub>FHL_STEP</sub>  | Input Offset/Level<br>Step size (e)                                   | At COMP_IN                     |                 |      | 0.879                |                                | mV            |

| V <sub>FHL_LEVEL</sub> | Limits <sup>(d)</sup>                                                 | At COMP_IN                     |                 | 0    |                      | 175                            | mV            |

| V <sub>REF</sub>       | Reference Voltage <sup>(e)</sup>                                      |                                |                 |      | 0.7                  |                                | V             |

|                        | Transducer Interface                                                  | TI_PATH_SEL = (                | )1              |      | 550                  |                                | Ω             |

|                        | Impedance (selectable by                                              | TI_PATH_SEL =                  | 10              |      | 350                  |                                | Ω             |

|                        | TI_PATH_SEL) <sup>(e)</sup>                                           | TI_PATH_SEL =                  | 11              |      | 214                  |                                | Ω             |

| f <sub>fire</sub>      | Typical Fire buffer frequency <sup>(d)</sup>                          |                                |                 | 0,04 |                      | 4                              | MHz           |

| <b>G</b> PGA           | PGA gain                                                              |                                | 1MHz            | 2.0  |                      | 17.3                           |               |

|                        | (selectable by                                                        | @ 25 °C                        | 2MHz            | 2.1  |                      | 14.4                           | V/V           |

|                        | PGA_TRIM) <sup>(d)</sup>                                              |                                | 4MHz            | 2.2  |                      | 8.4                            |               |

| e <sub>n</sub>         | PGA Noise, referred to input <sup>(e)</sup>                           | 10kHz to 500MHz                |                 |      | 70                   |                                | $\mu V_{rms}$ |

| V <sub>os</sub>        | PGA output offset voltage <sup>(e)</sup>                              | After auto-zero                |                 |      |                      | 1                              | mV            |

| Symbol | Parameter                                                                                      | Conditions | Min | Тур | Max   | Unit |

|--------|------------------------------------------------------------------------------------------------|------------|-----|-----|-------|------|

|        | Comparator input<br>offset voltage<br>(calibrated by Zero <sup>(e)</sup><br>Cross Calibration) |            |     |     | < 1.6 | mV   |

<sup>(1)</sup> Without external load

## 5.2 Time-to-Digital Converter

Figure 11: Time Measuring Unit (Vcc = 3.0 V, T<sub>j</sub> = 25 °C)

| Symbol         | Parameter                        | Conditions                        | Min | Тур    | Max  | Unit |

|----------------|----------------------------------|-----------------------------------|-----|--------|------|------|

| LSB            | TDC Resolution <sup>(e)</sup>    | Single-shot                       |     | 22     |      |      |

|                | LSB (output format)              | @ 4 MHz HSO<br>@ 8 MHz HSO        |     | 4<br>2 |      | ps   |

| t <sub>m</sub> | Measurement range <sup>(d)</sup> | TOF measurement                   | 10  |        | 1000 | μs   |

| t <sub>m</sub> | Measurement range <sup>(d)</sup> | Temperature interface measurement | 10  |        | 1024 | μs   |

## 5.3 Temperature Measuring Unit

Figure 12: Temperature Measuring Unit ( $V_{CC}$  = 3.0 V,  $T_j$  = 25 °C)<sup>(1)</sup>

| Symbol | Parameter                                                                                                                                   | Conditions      | Min | Тур          | Max | Unit  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|--------------|-----|-------|--|

|        | Resolution RMS <sup>(e)</sup>                                                                                                               | PT500, PT1000   |     | 17           |     | Bit   |  |

|        | Gain-Drift <sup>(2)</sup> vs. V <sub>CC</sub>                                                                                               | PT500, PT1000   |     | 0.01         |     | %/V   |  |

|        | Gain-Drift <sup>(2)</sup> vs.<br>Temperature <sup>(e)</sup>                                                                                 | PT500<br>PT1000 |     | < 4<br>< 2   |     | ppm/K |  |

|        | $ \begin{aligned} & \text{Initial Zero Offset}^{(e)} \\ & T_{\text{ref}} < \rightarrow \ (T_{\text{cold}},  T_{\text{hot}}) \end{aligned} $ | PT500<br>PT1000 |     | < 40<br>< 20 |     | mK    |  |

<sup>(1) 2-</sup>Wire measurement with compensation of Rds(on) and gain (Schmitt trigger). All values measured at Cload = 100 nF for PT1000 and 200 nF for PT500 (C0G-type)

<sup>(2)</sup> Only for measurements on settled maximum of amplitude plateau

<sup>(2)</sup> Compared to an ideal gain of 1.0

# 5.4 Supply Voltage Measuring Unit

Figure 13: Supply Voltage Measuring Unit

| Symbol | Parameter                           | Conditions                                                 | Min  | Тур           | Max   | Unit |

|--------|-------------------------------------|------------------------------------------------------------|------|---------------|-------|------|

|        | Measurement<br>Range <sup>(d)</sup> |                                                            | 2.15 |               | 3.725 | V    |

|        | Resolution <sup>(e)</sup>           | 1 LSB                                                      |      | 25            |       | mV   |

|        | Accuracy <sup>(d)</sup>             | $T_a = 25  ^{\circ}\text{C}$<br>$T_a = \text{whole range}$ |      | ± 50<br>± 150 |       | mV   |

# **6** Timing Characteristics

At  $V_{CC}$  = 3.0 V  $\pm$  0.3 V, ambient temperature -40 °C to 85 °C unless otherwise specified.

Figure 14: Oscillator specifications

| Symbol                      | Parameter                                                                               | Min | Тур    | Max | Unit |

|-----------------------------|-----------------------------------------------------------------------------------------|-----|--------|-----|------|

| f <sub>LSO</sub> (e)        | 32 kHz reference oscillator at frequency f <sub>LSO</sub>                               |     | 32.768 |     | kHz  |

| t <sub>LSO_ST</sub> (e)     | 32 kHz oscillator start-up time after power-up                                          |     | < 1    |     | Sec. |

| f <sub>HSO</sub> (e)        | High-speed reference oscillator at frequency f <sub>HSO</sub>                           |     | 4 (8)  | 8   | MHz  |

| t <sub>HSO_CER_ST</sub> (e) | Oscillator start-up time with ceramic resonator                                         |     | < 100  |     | μs   |

| thso_cry_st (e)             | Oscillator start-up time with crystal oscillator (not recommended)                      |     | 3      |     | ms   |

| f <sub>PS_CLK</sub> (e)     | Power supply clock. Used during power on to release cyclic measurement and for watchdog |     | 8.7    |     | kHz  |

### Information

We strongly recommend using a ceramic oscillator for HSO\_CLK, because a quartz oscillator needs much longer time to settle than a ceramic oscillator. This consumes a lot of current, but using a quartz oscillator has no advantage when high speed clock calibration is done as supported by AS6031.

Figure 15: Power-on Timings

| Symbol                     | Parameter                                                                                                              |        | Min | Тур  | Max  | Unit |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|--------|-----|------|------|------|

| t <sub>VDD18_STB</sub> (d) | Time when VDD18 is stable after power on of $V_{\text{CC}}$ ( $C_L \! = \! 100 \mu F$ on VDD18_OUT)                    |        |     |      | 20   | ms   |

| t <sub>RC_RLS</sub> (d)    | Time when remote communication is released after power on of $V_{\text{CC}}$ (POR in analog and digital part finished) |        |     | 37   | 94   | ms   |

| t <sub>MC_RLS</sub> (d)    | Start-up time after power-on. Time before cycle                                                                        | 85 °C  |     |      | 1.63 | S    |

|                            | measurements are released                                                                                              | 25 °C  |     | 1.42 | 2.09 |      |

|                            |                                                                                                                        | -40 °C |     |      | 3.63 |      |

## Information

During Power-on time, excess currents in the mA-range have to be considered. VCC and VDD18 have to be 0V before applying the supply voltage (e.g. in case of battery change).

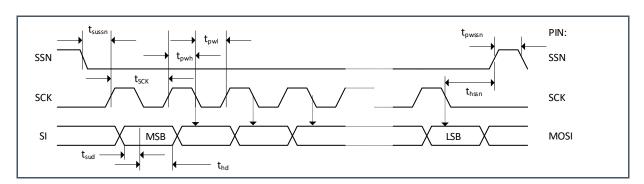

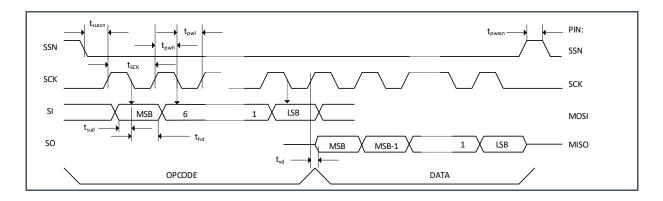

## 6.1 SPI Interface

Figure 16: SPI Timings

| Symbol             | Parameter                             | Min                     | Тур | Max | Unit |

|--------------------|---------------------------------------|-------------------------|-----|-----|------|

| f <sub>SCK</sub>   | Serial clock frequency                |                         |     | 8   | MHz  |

| t <sub>SCK</sub>   | Serial clock time period              | 125                     |     |     | ns   |

| t <sub>pwh</sub>   | Serial clock, pulse width high        | 0.45 * t <sub>SCK</sub> |     |     | ns   |

| t <sub>pwl</sub>   | Serial clock, pulse width low         | 0.45 * t <sub>SCK</sub> |     |     | ns   |

| t <sub>sussn</sub> | SSN enable to valid latch clock       | 0.5 * t <sub>SCK</sub>  |     |     | ns   |

| t <sub>hssn</sub>  | SSN hold time after SCK falling       | 0.5 * t <sub>SCK</sub>  |     |     | ns   |

| t <sub>pwssn</sub> | SSN pulse width between two cycles    | tscк                    |     |     | ns   |

| t <sub>sud</sub>   | Data set-up time prior to SCK falling | 5                       |     |     | ns   |

| t <sub>hd</sub>    | Data hold time before SCK falling     | 5                       |     |     | ns   |

| t <sub>vd</sub>    | Data valid after SCK rising           |                         |     | 25  | ns   |

The serial interface is SPI compatible, with clock phase bit =1 and clock polarity bit =0. It's strongly recommended to keep SSN = HIGH when SPI interface is in IDLE state.

Figure 17: SPI Write

Figure 18: SPI Read

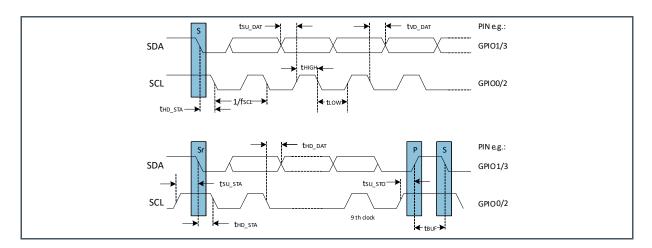

## 6.2 2-wire Master Interface

The integrated 2-wire master interface is very similar to  $I^2C$ , but not following the full  $I^2C$  specification. It can be used to communicate with an external EEPROM, but also any other external device like e.g. a pressure sensor.

Figure 19: 2-wire Master Timings (f<sub>HSO</sub> = 4 MHz)

| Symbol              | Parameter                | Min  | Тур  | Max | Unit |

|---------------------|--------------------------|------|------|-----|------|

| f <sub>SCL</sub>    | SCL clock frequency      |      |      | 400 | kHz  |

| t <sub>LOW</sub>    | Low period of SCL clock  | 1300 | 1500 |     | ns   |

| t <sub>HIGH</sub>   | High period of SCL clock | 600  | 1000 |     | ns   |

| t <sub>HD_STA</sub> | Hold time for (repeated) | 600  | 1000 |     | ns   |

| t <sub>SU_STA</sub> | START condition (S & Sr) | 600  | 750  |     | ns   |

| t <sub>SU_DAT</sub> | Setup time for repeated  | 100  | 750  |     | ns   |

| t <sub>HD_DAT</sub> | START condition (Sr)     | 0    | 750  |     | ns   |

| t <sub>VD_DAT</sub> | Setup time data          |      | 750  | 900 | ns   |

| t <sub>SU_STO</sub> | Hold time data           | 600  | 1750 |     | ns   |

| t <sub>BUF</sub>    | Valid time data          | 1300 |      |     | ns   |

Figure 20: 2-wire Master Interface Timing

A detailed description of the 2-wire interface is given in section 10.4 2-wire Master Interface.

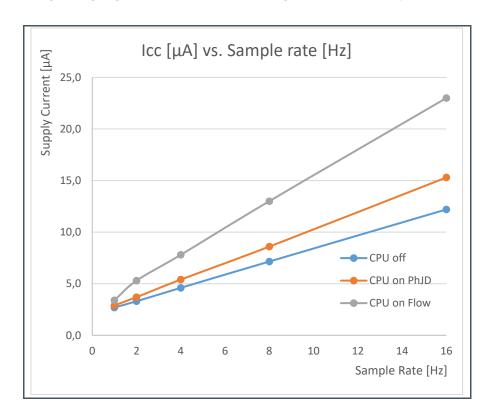

# 7 Typical Operating Characteristics

Figure 21: Typical Current Consumption vs. Sample Rate (VCC = 3.0V, PGA gain 2V/V, TOF  $75\mu s$ , no CPU, CPU w. simple FW for phase jump detection, CPU with complex flow firmware)

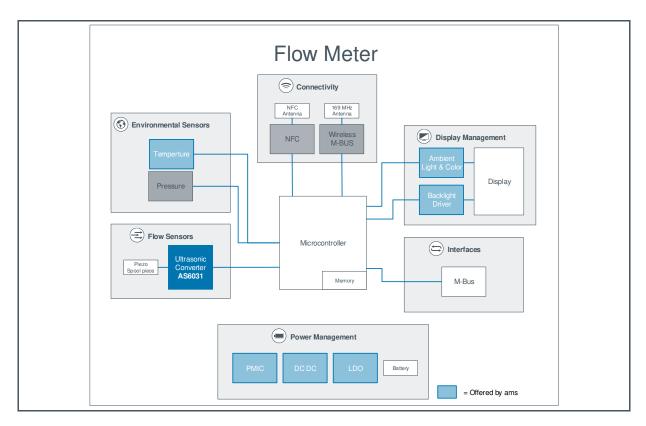

# 8 Functional Description

## 8.1 System Concept

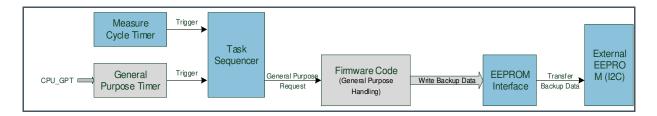

AS6031 is a complete ultrasonic flow converter (UFC) to measure and calculate the flow in a time-of-flight based ultrasonic water or heat meter. This includes the driver for the piezoelectric transducers, the analog switches, the programmable gain amplifier and the offset stabilized comparator, the CPU to calculate the flow, the clock control unit and, above all, the measure rate control and task sequencer unit. AS6031 is an autonomous system, with the task sequencer managing the complete measurement sequence independently from an external CPU. It can be used as a pure font-end with time of flight information as an output. But by means of the internal CPU the time information can be converted into a flow calibrated information already.

A major reason to go with this concept is that the AS6031 covers the complete ultrasonic flow measurement task, but doesn't touch all the other tasks of the central microcontroller. The user therefore has high flexibility in the choice of the central microcontroller and can even go with the same used e.g. for mechanical meters. On the other hand, the user does not need to step into design of electronics for ultrasonic flow but can setup a meter in a short period of time.

Figure 22:

Application Diagram Flow Meter

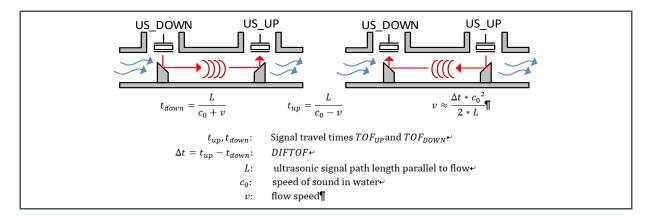

## 8.1.1 Measuring Principle

The **AS6031** measures flow by measuring the difference in time-of-flight (TOF) of ultrasonic pulses which travel with the flow (downstream) and opposite to the flow (upstream). For water meters, water temperature can be calculated from the time-of-flight data, too. For heat meters, a high-precision temperature measurement unit is integrated.

Figure 23: Principle of Ultrasonic ToF Flow Measurement

The flow speed v at a given cross section area is a measure for the actual flow through the spool piece and integrating the flow over time yields the flow volume.

The task of AS6031 is to handle complete process, driving the transmitting piezoelectric transducer, that generate the ultrasonic burst, measuring the receiving transducer with respect to time-of-flight and amplitude, eventually doing a temperature measurement, and optionally do the complete post-processing for flow calculation.

## 8.2 Functional Blocks Overview

The AS6031 is made of the following major blocks:

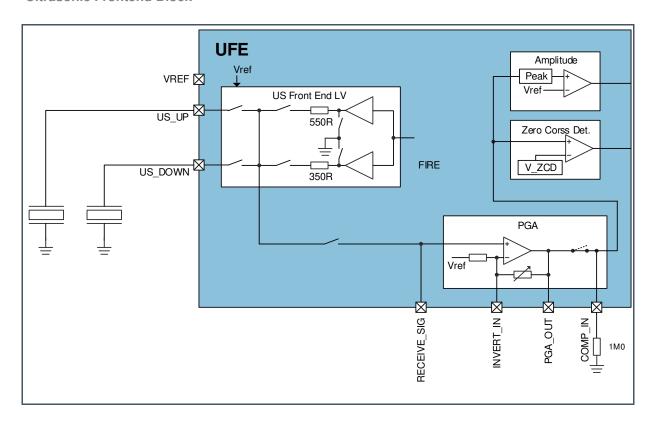

- Ultrasonic frontend (UFE) for ultrasonic flow measurement and temperature measurement including programable gain amplifier

- Digital core with the supervisor and task sequencer, the frontend processing unit, the CPU and memory.

- Digital I/O section

- Power supply

- Oscillator drivers

Figure 24:

Major Functional Blocks of AS6031

## 8.2.1 Operating Modes

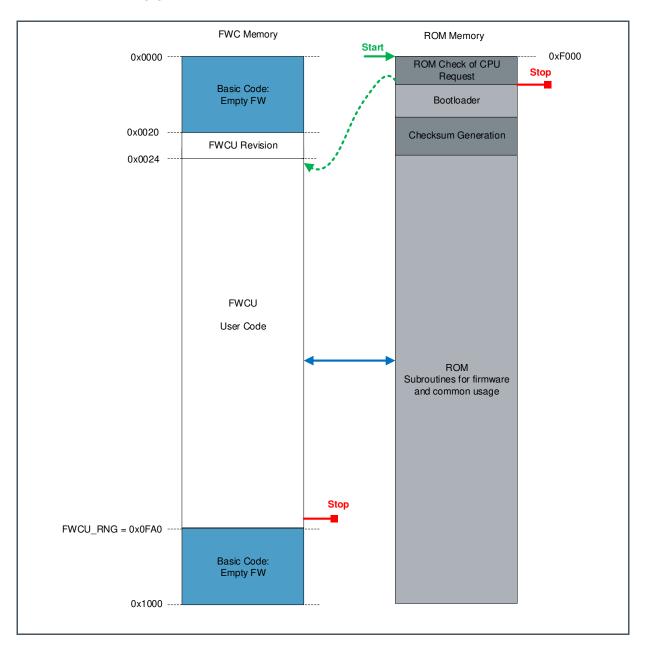

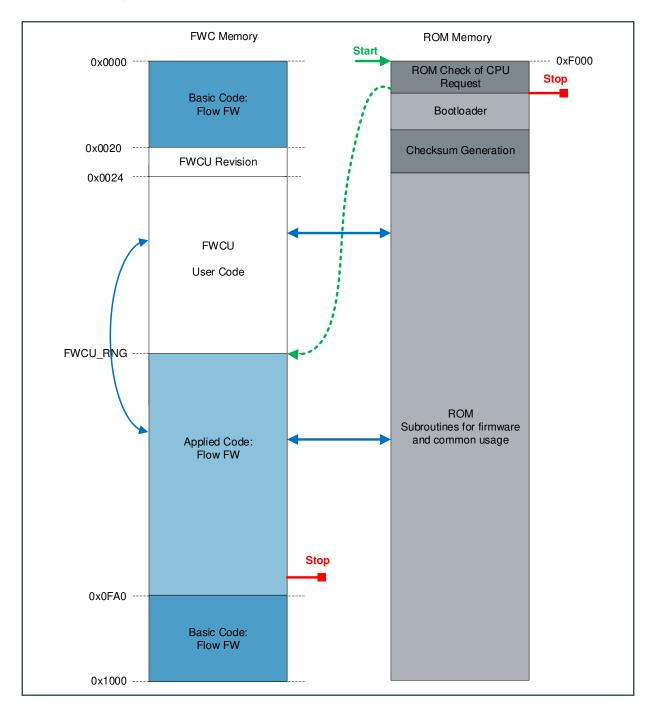

The AS6031 is designed for autonomous operation, with all processes, including flow calculation, being managed by the AS6031. But it may be used as pure front end, too.

- Flow Meter Mode: In the self-controlled flow meter mode, the supervisor triggers all measurements and the CPU does data processing to deliver processed results, independent from any external control. A bootloader, executed in the ROM of the integrated CPU, takes care of the application setup. A programmed firmware, also executed in the integrated CPU, defines the post processing. The interrupt may wake up an external microcontroller, so that it can read out the data.

- **Time Conversion Mode**: Alternatively, the AS6031 can act as a pure converter that controls the measurement, but provides pure time-of-flight data, without any data processing (time conversion mode, self-controlled). The external microcontroller takes care of the application setup and post processing.

For debugging, an external microcontroller can trigger individual tasks remotely by SPI interface commands (time conversion mode, remote controlled).

## **Application Setup**

The application setup of AS6031 hardware is defined by two sections in the register area:

- Configuration registers (CR) (0x0C0 0x0CE)

- System handling registers (SHR) (0x0D0 0x0DD)

Both register sections will be reset after the execution of a "System Reset".

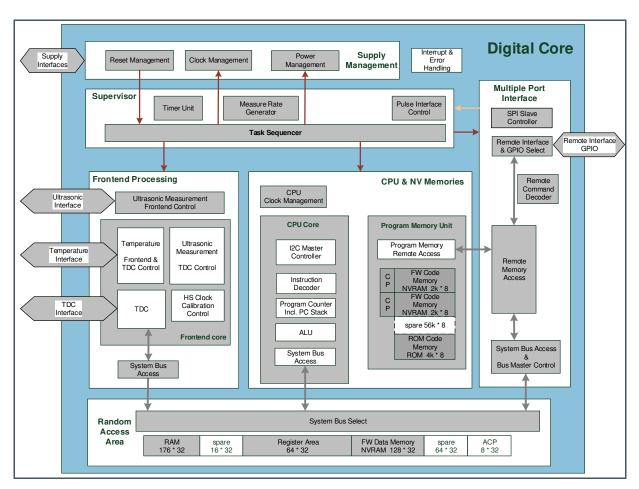

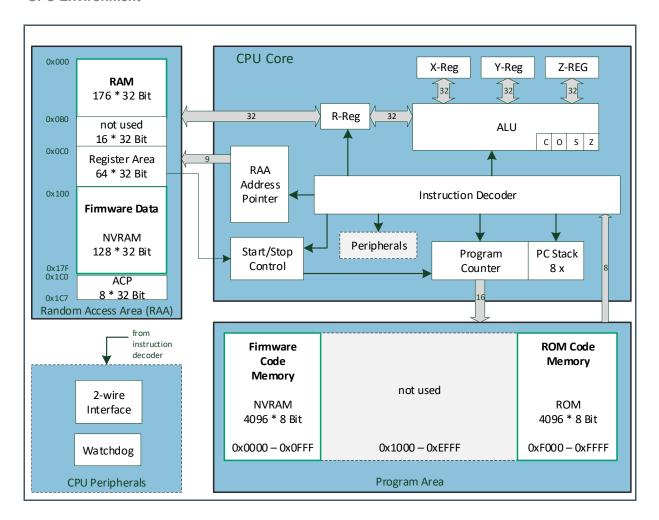

## 8.3 Digital Core

The digital core is made of the following sub-blocks:

- Supervisor with task sequencer, timer unit, measure rate generator and pulse interface control

- Frontend processing with control of the ultrasonic and temperature frontends, the TDC and the high-speed clock calibration

- CPU and memories for optional post-processing

- The multiple port interface for SPI communication, 2-wire master interface and pulse interfaces

- Supply management with reset management, clock management and power management

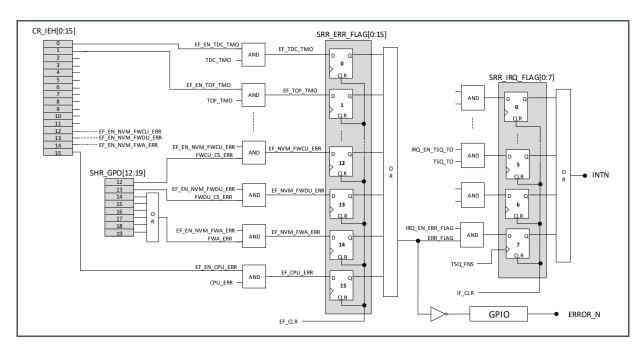

- Interrupt and error handling

- Common system bus

Figure 25: Digital Core

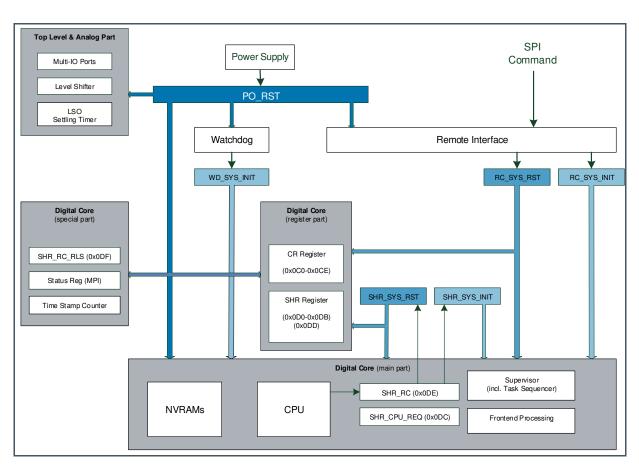

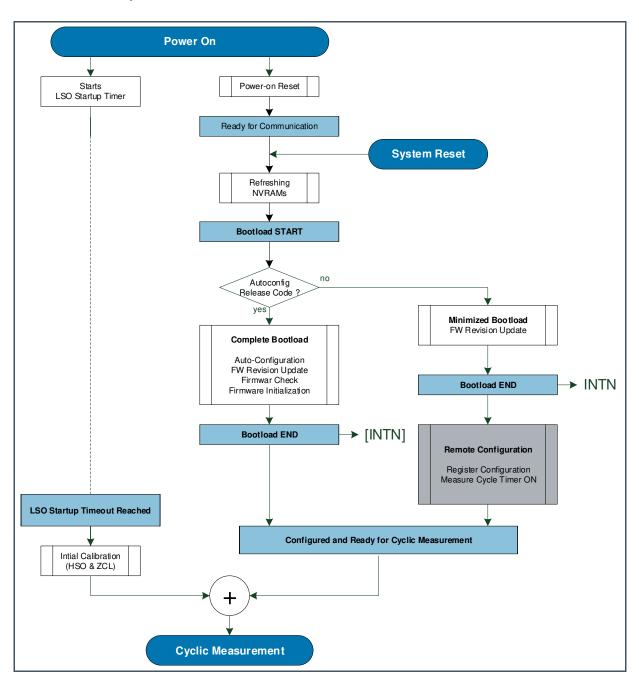

## 8.3.1 Reset Management

#### **Reset Distribution**

Resets in AS6031 are initiated by turning on the power supply, by the watchdog or via remote interface commands.

Figure 26: Reset Distribution

Following resets can be distinguished:

PO\_RST

Power-On Reset of AS6031, generated by power supply. Only performed after VDD33 is switched on. Resets complete AS6031 including digital IOs. After a PO\_RESET, the measurement cycle timer is disabled for typically 2s until the settling time for the LSO has expired.

RC SYS RST

Remote Command System Reset, performed after sending a remote command 0x99. Resets the complete digital part of AS6031.

Note: Applicable only during debugging, not for application

SHR SYS RST

System Reset performed by writing a '1' to **SHR\_RC**[14] (Address 0x0DE) if appropriate release code is written before to **SHR\_RC\_RLS** (Address 0x0DF). Preferably initiated by CPU to allow a system reset by FW execution.

Resets main & register part of digital core.

Resetting only the main part of the digital core, without configuration registers, is done the following way:

WD SYS RST

Watchdog System Reset, performed after the watchdog timer expired. Triggers a SYS\_INIT but leaves registers and memory unchanged.

RC SYS INIT

System Init by remote command, performed after sending the SPI remote command 0x9A. Preferred remote action if register part of digital core is wanted to be untouched.

The different parts of AS6031 are reset as follows:

- Top Level and Analog Part:

- PO RST

- Digital Core (special part):

- PO\_RST

- Digital Core (register part):

- PO\_RST

- RC\_SYS\_RST

- SHR\_SYS\_RST if SHR\_RC\_RLS == hAF0A\_4735

- Digital Core (main part):

- PO RST

- RC\_SYS\_RST

- SHR\_SYS\_RST if SHR\_RC\_RLS = hAF0A\_4735

- WD\_SYS\_INIT

- RC\_SYS\_INIT

Following registers are separated from register part with different reset behavior

SHR\_RC\_RLS (0x0DF): only by PO\_RST

SHR\_RC (0x0DE): additionally by WD\_SYS\_INIT & RC\_SYS\_INIT

SHR\_CPU\_REQ (0x0DC): additionally by WD\_SYS\_INIT & RC\_SYS\_INIT

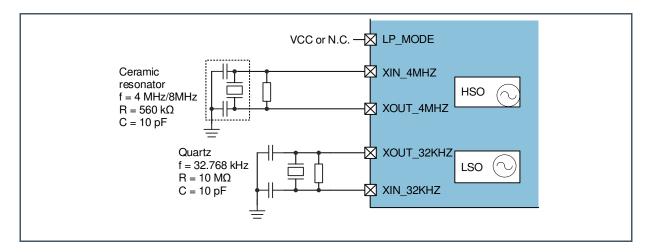

## 8.3.2 Clock Management

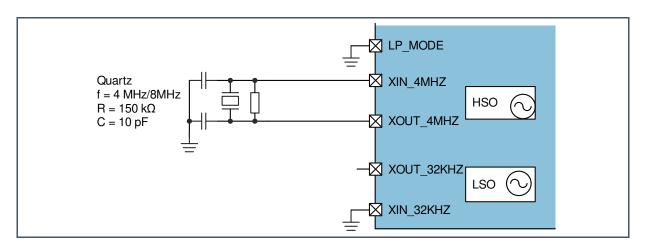

AS6031 normally uses two external clocks and is equipped with pins for two external clock sources.

#### LSO

A low-speed clock (typically 32.768 kHz), connecting a quartz crystal at pins XIN\_32KHZ & XOUT\_32KHZ. This clock is the basis for the supervisor, including measure rate generator and task sequencer. It is running all the time when using normal low power mode.

#### HSO

A high-speed clock (typically 4 or 8 MHz), connecting ceramic resonator to pins XIN\_4MHZ & XOUT\_4MHZ. It is used for the frontend processing and is activated only when needed. Compared to a quartz, a ceramic resonator has the benefit of a short settling time which saves power consumption. On the other hand, the clock needs to be calibrated periodically versus the LSO quartz.

• Alternatively, active external clock can be fed into the XOUT pins (XIN pins need to be grounded then).

**Note**: In addition, there is an internal low speed oscillator PS\_CLK of typ. 8.7 kHz which is used for the power-up timing to release measurements and for the watchdog.

We distinguish the following clock operation modes:

#### **Low Power Mode**

AS6031 is sourced by the external low-speed oscillator (LSO). This is the standard in typical applications.

Figure 27:

Connecting Oscillators in Low Power Mode

## **Single-source Clocking Mode**

No external low-speed source is needed. The internal low-speed clock is derived from high-speed clock, which in this case needs to be a quartz. The internal LSO frequency is then 32 kHz. The high-speed clock needs to run all the time. As the HSO needs about 80  $\mu$ A, this mode is not recommended for applications where low power is needed.

Figure 28:

Connecting Oscillator in Single-source Clocking Mode

## **Clock Divider Options**

Following table shows recommended settings for the clock dividers.

Figure 29: Useful Caption

| HS_CLK                                       | 4 MHz          | 8 MHz            |

|----------------------------------------------|----------------|------------------|

| Fire Burst Frequency                         | 40 kHz - 1 MHz | 62.5 kHz - 4 MHz |

| HSC_DIV_MODE                                 | 0              | 1                |

| HSC_DIV                                      | 0              | 1                |

| TDC Result Resolution (* 1/2 <sup>16</sup> ) | 250 ns         | 125 ns           |

The recommended HS clock frequency and derived clock divider settings are mainly defined by required fire burst frequency.

#### **Clock Calibration**

The HSO frequency will vary from device to device but also with temperature. Therefore, it needs to be calibrated frequently. During calibration, four periods of the LSO (122.0703125  $\mu$ s) are measured by means of the HSO.

The register SRR\_HCC\_VAL (High-Speed Clock Calibration Value) is updated. The value is eight times the real frequency at the TDC:  $8 * f_{HSO} / Hz$ .

Nominal value with 250ns period: 32,000,000 (0x1E84800) Nominal value with 125ns period: 64,000,000 (0x3D09000)

Example with real value from SRR\_HCC\_VAL, e.g. 249.9579ns: 32,005,389 (0x1E85D0D)

Correction factor: 32,000,000/32,005,389 = 0.999832, to be used for all further timing calculations in any post processing.

The status flag **HCC\_UPD** in SRR\_FEP\_STF (Frontend Processing Status Flags) indicates whether the content is updated or not.

## **Relevant Registers**

The table below lists most important registers and parameters for setting the clock management.

Figure 30: Clock Control & Status Registers

| Register                                          | Parameter     | Description                                                                                                                                                                  |

|---------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | HSC_CLK_ST    | High-speed clock settling time (77μs, 107μ,, 5ms) 135μs is a good value for ceramic oscillators.                                                                             |

| CR_CPM (Clock- & Power-<br>Management)            | HSC_RATE      | Sets the calibration rate of HSO versus LSO (off, every 2 <sup>nd</sup> ,, every 100 <sup>th</sup> ).                                                                        |

|                                                   | HSC_DIV       | High-Speed Clock Divider  0: HSC_CLK not divided  1: HSC_CLK divided by 2  Optionally with HSC_DIV_MODE = 1:  Only applied to low speed clocking & frontend control          |

|                                                   | HSC_DIV_MODE  | High speed clock divider mode  0: all HSC clock dividers controlled commonly by HSC_DIV  1: HSC clock dividers individually configurable (bit 8:5)                           |

| SHR_EXC (Executables)                             | HSO_CLR       | Clears the high-speed oscillator (typically used by firmware code for I2C handling)                                                                                          |

|                                                   | HSO_REQ       | Requests the high-speed oscillator (typically used by firmware code for I2C handling)                                                                                        |

| SHR_RC (Remote Control)                           | HSO_MODE      | High Speed Oscillator Mode (for debugging only) 00: No change of HSO_MODE state (WO) 01: HSO controlled as configured 10: HSO always on 11: No change of HSO_MODE state (WO) |

|                                                   | HSC_DIV_STATE | Info only, set by HSC_DIV in CR_CPM  00, 11; not possible  01: HSC_DIV = 0  10: HSC_DIV = 1                                                                                  |

| SRR_FEP_STF (Frontend<br>Processing Status Flags) | HCC_UPD       | Indicates whether the clock calibration value is updated or not.                                                                                                             |

| Register                                         | Parameter               | Description                                                                                                                                                                                                                     |

|--------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRR_HCC_VAL (High-Speed Clock Calibration Value) | HCC_VAL                 | High-speed clock calibration value.<br>= 122.0703125/T <sub>HSO</sub> *2 <sup>16</sup>                                                                                                                                          |

| SRR_MSC_STF<br>(Miscellaneous Status Flags)      | HSO_STABLE              | Flag for the end of the high-speed oscillator settling time, indicating that high-speed oscillator is settled and stable. For CPU handling the flag CPU_SFLAG_HSO_ST_TO is preferred.                                           |

| SHR_CPU_REQ                                      | CPU_SFLAG_HSO_ST<br>_TO | O: High speed oscillator not in timeout condition  1: High speed oscillator in timeout condition  Cleared by HSO_CLR in SHR_EXC  Same as HSO_STABLE but updated and valid only while CPU is running (synchronized by CPU clock) |

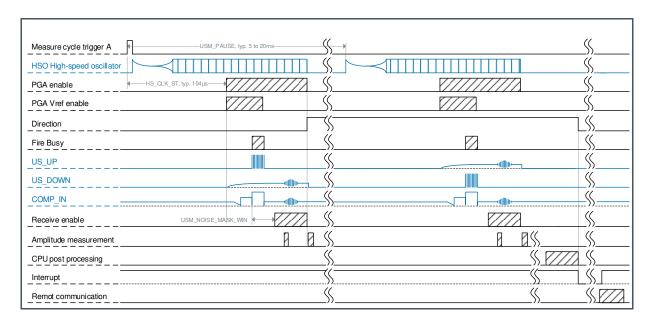

## 8.3.3 Measure Rate Generator

The measure rate generator supplies up to 8 different measure task requests, which can trigger the task sequencer. The task sequencer is a state machine and then manages the processing of the measurement tasks, based on the measure cycle timer and the measure rates. The measure rate cycle time (MR\_CT) is the central clock in the measure rate generator.

Figure 31:

Cycle Times for Tasks (example)

| Task  | Cycle Time <sup>(1)</sup>                                | Typical setting |     | Comment                                                               |

|-------|----------------------------------------------------------|-----------------|-----|-----------------------------------------------------------------------|

| MR_CT |                                                          |                 | 125 | 8 Hz base frequency                                                   |

| TOF   | TOF_RATE × MR_CT × T <sub>MCT</sub>                      | TOF_RATE        | 1   | 8 Hz flow measurement                                                 |

| AM    | AM_RATE × TOF_RATE × MR_CT × T <sub>MCT</sub>            | AM_RATE         | 1   | Amplitude measurement performed with every time of flight measurement |

| AMC   | AMC_RATE × AM_RATE × TOF_RATE × MR_CT × T <sub>MCT</sub> | AMC_RATE        | 50  | Amplitude measurement calibration rate                                |

| VM    | VM_RATE × MR_CT × T <sub>MCT</sub>                       | VM_RATE         | 100 | Voltage measurement every 12.5s                                       |

| TM    | TM_RATE × MR_CT × T <sub>MCT</sub>                       | TM_RATE         | 240 | Temperature measurement every 30s                                     |

| HSC   | HSC_RATE × MR_CT × T <sub>MCT</sub>                      | HSC_RATE        | 100 | High-speed clock calibration every 12.5s                              |

| ZCC   | ZCC_RATE × MR_CT × T <sub>MCT</sub>                      | ZCC_RATE        | 100 | Zero-cross calibration every 12.5s                                    |

(1) LP\_MODE = 1:  $T_{MCT} = 976.5625 \mu s$

## **Relevant Registers**

The following table lists the most important registers and parameters for setting the measure rates.

Figure 32: Measure Rate Settings

| Register                                                    | Parameter     | Description                                                                                               |  |

|-------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------|--|

| CR_CPM (Clock-<br>& Power-<br>Management)                   | HSC_RATE      | High-speed clock calibration rate                                                                         |  |

| CR_TPM<br>(Temperature<br>Measurement)                      | TM_RATE       | Defines the number of sequence cycle triggers between sensor temperature measurements [0=off, 1 to 1023]. |  |

| CR_USM_PRC<br>(Ultrasonic<br>Measurement<br>Processing)     | ZCC_RATE      | Zero-cross calibration rate [0=off, 1, 2, 5, 10, 20, 50, 100].                                            |  |

| CR_USM_TOF<br>(Ultrasonic<br>Measurement<br>Time of Flight) | TOF_RATE_INIT | Initial value of TOF rate after autoconfiguration of bootload                                             |  |

| CR_USM_AM                                                   | AM_RATE       | Amplitude measurement rate [0=off, 1, 2, 5, 10, 20, 50, 100].                                             |  |

| (Ultrasonic<br>Amplitude<br>Measurement)                    | AMC_RATE      | Amplitude measurement calibration rate [0=off, 1, 2, 5, 10, 20, 50, 100].                                 |  |

| SHR_TOF_RATE<br>(Time Of Flight<br>Rate)                    |               |                                                                                                           |  |

## 8.3.4 Task Sequencer

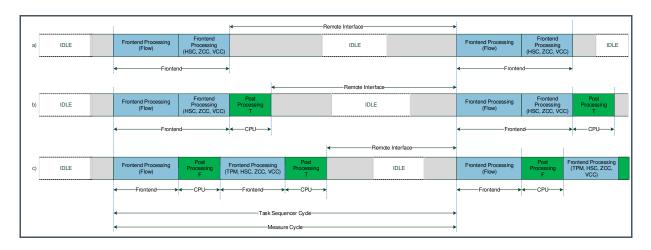

The task sequencer triggers the various measurement tasks and calibration tasks. It also triggers the post processing. The task sequencer has two operation modes:

- 1-phase mode: All measurements follow the same trigger. Post-processing can be triggered by the flow measurement and the other measurements.

- 2-phase mode: Flow measurement and temperature measurement are triggered by separate triggers, called A and B.

The 1-phase mode is the preferred one when working with CPU post processing or when no temperature measurement is done. The idle time for communication with an external partner is maximized.

The 2-phase mode is needed in time conversion mode (no CPU post processing) with temperature measurement active. The reason is that for flow and temperature the same frontend data buffer is used.

## 1-Phase Mode

All measurements tasks are triggered by the same single trigger. Following applications are covered:

Figure 33: 1-phase Mode

- a) Time conversion mode without temperature measurement (TPM)

- TS\_MCM = 0 / TS\_PP\_T\_EN = 0 / TS\_PP\_F\_EN = 0

- b) Flow meter mode without temperature measurement TS\_MCM = 0 / TS\_PP\_T\_EN = 1 / TS\_PP\_F\_EN = 0

- c) Flow meter mode with temperature measurement

TS\_MCM = 0 / TS\_PP\_T\_EN = 1 / TS\_PP\_F\_EN = 1

In this mode all measure tasks can be performed in one task sequencer cycle. Doing this, the IDLE time which can be used for remote communication is as large as possible.

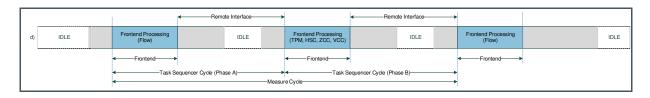

### 2-phase Mode

This mode is needed for

D) Time Conversion Mode with Temperature Measurement (TPM)

TS\_MCM = 1 / TS\_PP\_T\_EN = 0 / TS\_PP\_F\_EN = 0

In this mode the measure cycle is divided into two task sequencer cycles. So, it is possible to read out flow and temperature results subsequently via the serial interface. The idle time is split and reduced.

Figure 34: 2-phase Mode

## **Relevant Registers**

The following table lists the most important registers and parameters for setting the measure rates.

Figure 35: Useful Caption

| Register                                                     | Parameter  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR_MRG_TS<br>(Measure Rate<br>Generator & Task<br>Sequencer) | MR_CT      | Task sequencer cycle time. The actual physical measure rate cycle time is $t_{\text{cycle}} = MR\_CT^*$ 976.5625 µs [0, 18191]. The measurement rate generator triggers measurements in two alternating channels, one (A) triggering the flow and amplitude measurement, the other one (B) triggering temperature and voltage measurement as well as the high-speed clock (HSO) and the comparator offset calibration. Optionally (TS\_MCM = 1), channel B triggers a half cycle time after channel A, to avoid mutual influences among the measurements. |

|                                                              | TS_MCM     | Task sequencer measure cycle mode: 0: Trigger A (flow) and Trigger B (temperature) follow sequentially 1: Trigger A (flow) and Trigger B (temperature) are separated by t <sub>cycle</sub> /2                                                                                                                                                                                                                                                                                                                                                             |

|                                                              | TS_PP_MODE | Post processing mode (only if post processing is enabled) 0: Post processing requested with every task sequencer trigger 1: Post processing only requested if a measurement task is requested 1 is the recommended setting                                                                                                                                                                                                                                                                                                                                |

|                                                              | TS_PP_F_EN | Enables Post Processing F (after USM flow and amplitude measurement task) 0: Post Processing F disabled 1: Post Processing F enabled 0 is the recommended setting                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                              | TS_PP_T_EN | Enables Post Processing T (final one after temperature, voltage and calibration measurement tasks or post processing F) 0: Post Processing T disabled 1: Post Processing T enabled                                                                                                                                                                                                                                                                                                                                                                        |

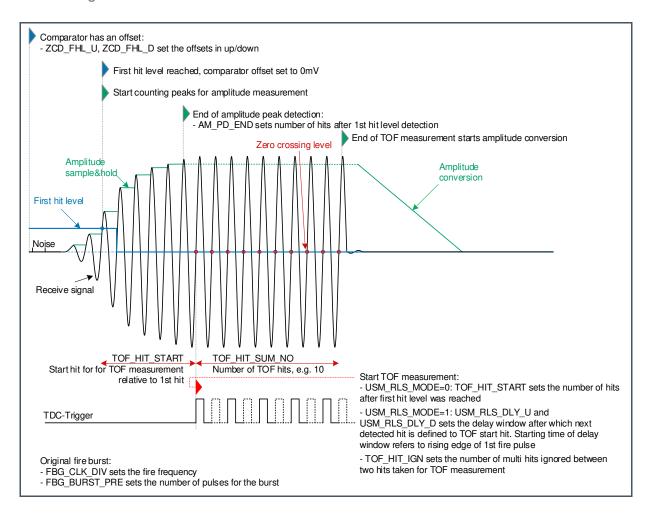

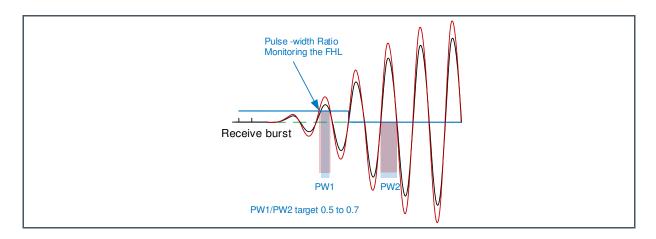

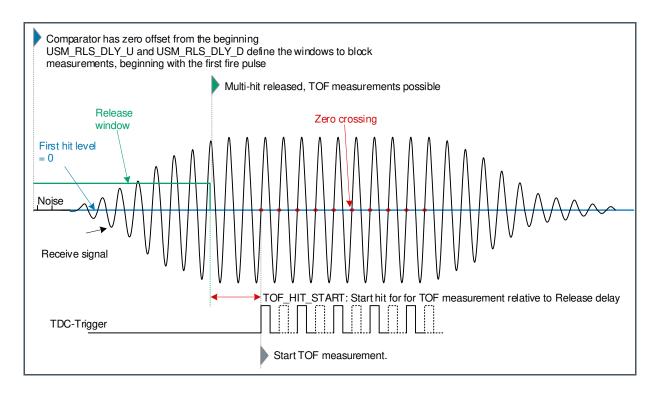

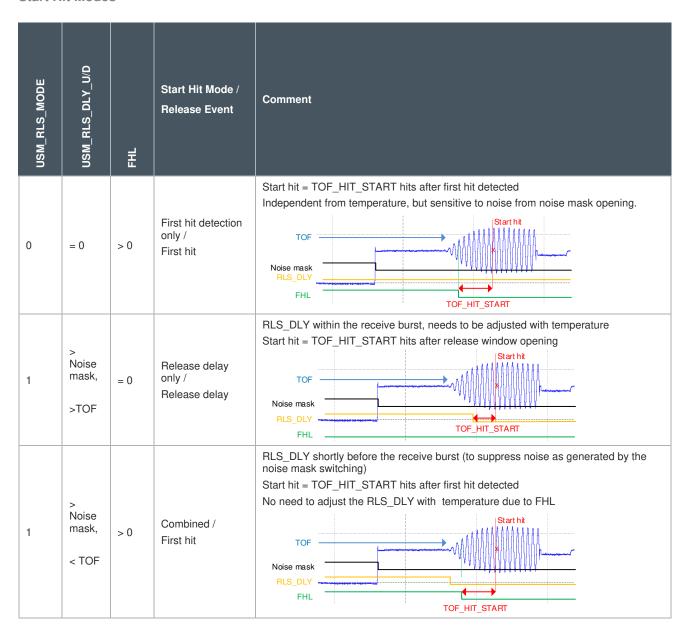

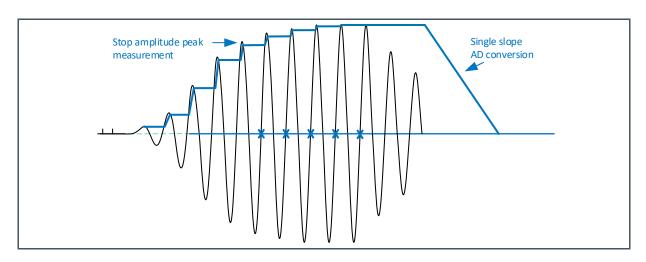

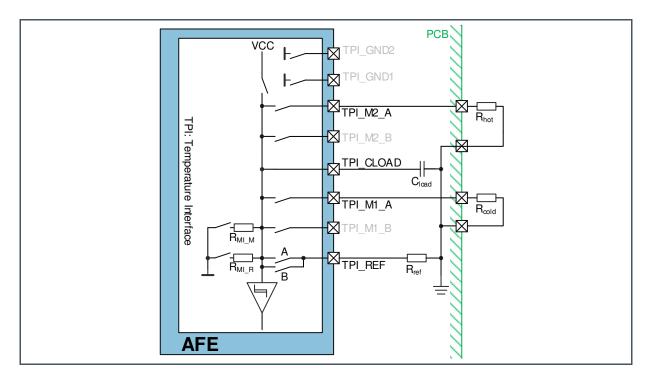

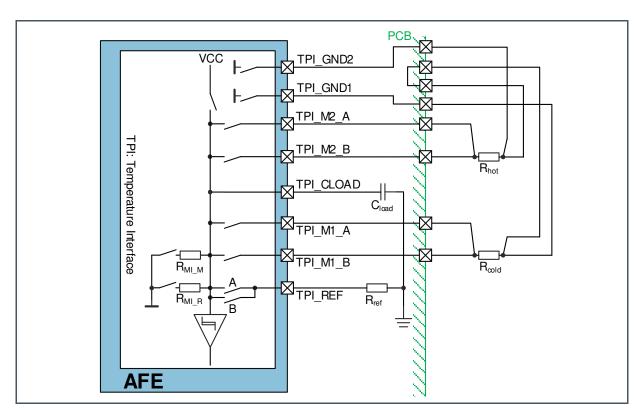

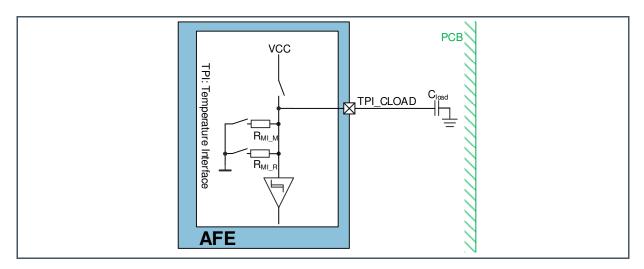

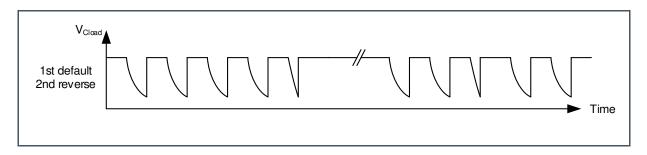

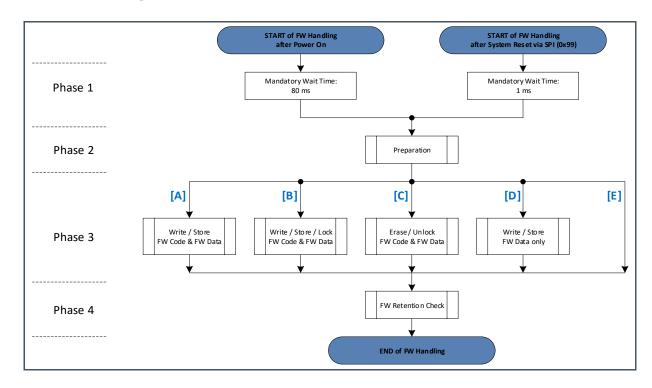

## **Task Processing Times**