# NHD-3.5-320240MF-22 Controller Board

# **TFT Controller Evaluation Board**

| NHD-    | Newhaven Display                  |

|---------|-----------------------------------|

| 3.5-    | 3.5" Diagonal                     |

| 320240- | 320xRGBx240 pixels                |

| MF-     | Model                             |

| 22-     | 22-POS FFC interface (8-bit data) |

|         | SSD1963 Controller                |

Newhaven Display International, Inc.

2661 Galvin Ct. Elgin IL, 60124 Ph: 847-844-8795 Fax: 847-844-8796

### **Document Revision History**

| Revision | Date       | Description                                            | Changed by |

|----------|------------|--------------------------------------------------------|------------|

| 0        | 11/20/2012 | Initial Release                                        | AK         |

| 1        | 1/25/2013  | J2 Pin description updated                             | AK         |

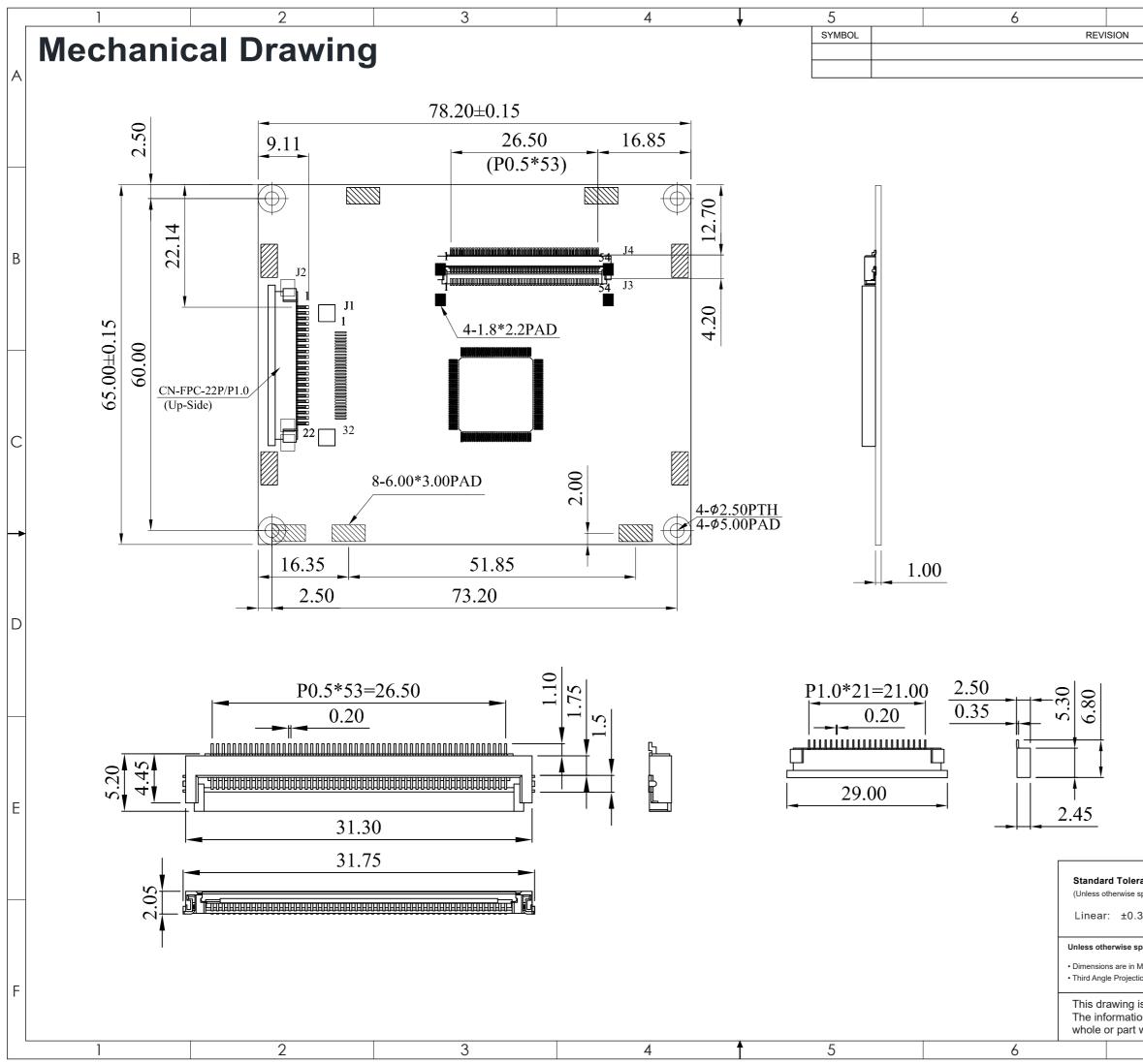

| 2        | 3/3/21     | 2D Mechanical Drawing Redesign;                        | AS         |

|          |            | Revised Compatibility to NHD-3.5-320240MF-ATXL# Models |            |

#### **Functions and Features**

• To use for testing, evaluating, or in final production with NHD-3.5-320240MF-ATXL# displays.

| 7 |     |     | 0         |   |

|---|-----|-----|-----------|---|

| 7 |     |     | 8<br>DATE | ר |

|   |     |     |           |   |

|   |     |     |           | A |

|   |     |     |           |   |

|   |     |     |           |   |

|   |     |     |           |   |

|   |     |     |           | - |

|   |     |     |           |   |

|   | 10  |     |           |   |

|   | J2  |     |           |   |

|   | PIN | NO. | SYMBOL    | B |

|   |     | 1   | GND       |   |

|   |     | 2   | VDD       |   |

|   |     | 3   | BL_E      |   |

|   |     | 4   | D/C       |   |

|   |     | 5   | WR        |   |

|   |     | 6   | RD        | С |

|   |     | 7   | DB0       |   |

|   |     | 8   | DB1       |   |

|   |     | 9   | DB2       |   |

|   | 1   | 0   | DB3       | - |

11

12

13

14

15

16

17

18

19

20

21

DB4

DB5

DB6

DB7

CS

RES

NC

XL

NC

YU

XR

E

|                                         |                                                                             | 22            | 2                   | Y          | D            |   |

|-----------------------------------------|-----------------------------------------------------------------------------|---------------|---------------------|------------|--------------|---|

| ance:<br>pecified)                      | NEW                                                                         | HAVEN<br>ERNA | <b>р</b>            | SPI<br>N A |              |   |

| 3mm                                     | Drawing/Part Number:                                                        |               |                     |            | Revision:    | 1 |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | NHD-3.5-320240M                                                             | 1.0           |                     |            |              |   |

| pecified:                               | Drawn By: A. Shah                                                           | Approved By:  | A. Sh               |            | Size:<br>A3  |   |

| /illimeters                             | Drawn Date: 3/4/2021                                                        | Approved Date | <sup>:</sup> 3/4/20 | 021        | Scale:<br>NS |   |

| on 🕀 🖯                                  | Do Not Scale Dra                                                            | awing         | S                   | Sheet 1    | of 1         | F |

| on it conta                             | he property of Newhay<br>ins is not to be disclos<br>ritten approval from N | sed, reprodu  | iced c              | or copi    |              |   |

|                                         | 7                                                                           |               |                     | Q          |              | - |

## Pin Description

### J2 (SSD1963 input from user's MPU):

| Pin No. | Symbol     | External     | Function Description                       |

|---------|------------|--------------|--------------------------------------------|

|         |            | Connection   |                                            |

| 1       | VSS        | Power Supply | Ground                                     |

| 2       | VDD        | Power Supply | Power supply for LCD and logic (3.3V)      |

| 3       | B/L Enable | Power Supply | Backlight Enable                           |

| 4       | RS         | MPU          | Register Select. RS=0: Command, RS=1: Data |

| 5       | /WR        | MPU          | 8080 mode: Active LOW Write                |

| 6       | /RD        | MPU          | 8080 mode: Active LOW Read                 |

| 7-14    | DB0-DB7    | MPU          | 8-bit bidirectional data bus               |

| 15      | /CS        | MPU          | Active LOW Chip Select                     |

| 16      | /RST       | MPU          | Active LOW Reset                           |

| 17      | NC         | -            | No Connect                                 |

| 18      | NC         | -            | No Connect                                 |

| 19      | NC         | -            | No Connect                                 |

| 20      | NC         | -            | No Connect                                 |

| 21      | NC         | -            | No Connect                                 |

| 22      | NC         | -            | No Connect                                 |

### J3, J4 (SSD1963 output to display panel):

| Pin No. | Symbol  | External         | Function Description                       |

|---------|---------|------------------|--------------------------------------------|

|         |         | Connection       |                                            |

| 1       | LED-    | LED Power Supply | Ground for backlight                       |

| 2       | LED-    | LED Power Supply | Ground for backlight                       |

| 3       | LED+    | LED Power Supply | Power for backlight                        |

| 4       | LED+    | LED Power Supply | Power for backlight                        |

| 5-7     | NC      | -                | No Connect                                 |

| 8       | /RST    | MPU              | Active LOW Reset                           |

| 9       | /CS     | -                | Active LOW Serial Chip Select (No Connect) |

| 10      | SCL     | -                | Serial Clock (No Connect)                  |

| 11      | SDA     | -                | Serial Data (No Connect)                   |

| 12-19   | [BO-B7] | MPU              | Blue Data                                  |

| 20-27   | [G0-G7] | MPU              | Green Data                                 |

| 28-35   | [R0-R7] | MPU              | Red Data                                   |

| 36      | HSYNC   | MPU              | Horizontal (Line) Sync                     |

| 37      | VSYNC   | MPU              | Vertical (Frame) Sync                      |

| 38      | DCLK    | MPU              | Dot Clock                                  |

| 39-40   | NC      | -                | No Connect                                 |

| 41      | VDD     | Power Supply     | Power supply for LCD and logic (3.3V)      |

| 42      | VDD     | Power Supply     | Power supply for LCD and logic (3.3V)      |

| 43-51   | NC      | -                | No Connect                                 |

| 52      | DE      | -                | Data Enable (No Connect)                   |

| 53      | VSS     | Power Supply     | Ground                                     |

| 54      | VSS     | Power Supply     | Ground                                     |

#### **Electrical Characteristics**

| Item                        | Symbol | Condition    | Min.    | Тур. | Max.    | Unit |

|-----------------------------|--------|--------------|---------|------|---------|------|

| Operating Temperature Range | Тор    | Absolute Max | -20     | -    | +70     | °C   |

| Storage Temperature Range   | Tst    | Absolute Max | -30     | -    | +80     | °C   |

| Supply Voltage              | VDD    |              | 3.0     | 3.3  | 3.6     | V    |

| Supply Current              | IDD    |              | -       | 25   | -       | mA   |

| Input High Voltage          | VIH    |              | 0.8*VDD | -    | VDD     | V    |

| Input Low Voltage           | VIL    |              | VSS     | -    | 0.2*VDD | V    |

|                             |        |              |         |      |         |      |

| Backlight Voltage           | VLED   | ILED=20mA    | 18      | 19.2 | 20.4    | V    |

| Backlight Current           | ILED   |              | -       | 18   | 20      | mA   |

#### **Controller Information**

Built-in SSD1963 controller Please download specification at <u>http://www.newhavendisplay.com/app\_notes/SSD1963.pdf</u>

#### **MCU Interface**

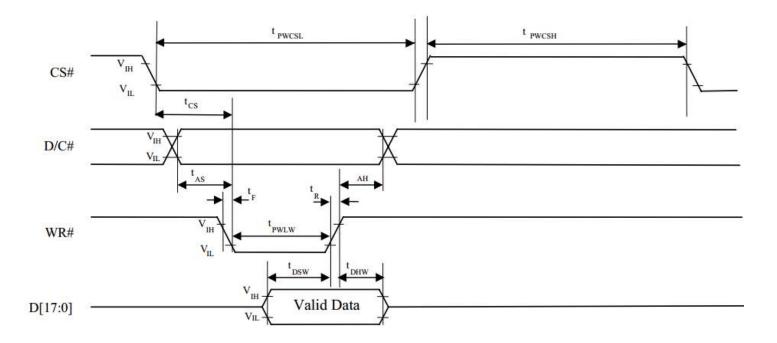

The controller board operates in 8080 mode. This interface uses /WR to define a write cycle and /RD for read cycle. If /WR goes low when the /CS signal is low, the data or command will be latched into the system at the rising edge of /WR. Similarly, the read cycle will start when /RD goes low and end at the rising edge of /RD.

#### **Pixel Data Format**

| Interface            | Cycle           | D[23] | D[22] | D[21] | D[20] | D[19] | D[18] | D[17] | D[16] | D[15] | D[14] | D[13] | D[12] | D[11] | D[10] | D[9] | D[8] | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0]      |

|----------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|-----------|

| 24 bits              | 1 <sup>st</sup> | R7    | R6    | R5    | R4    | R3    | R2    | R1    | R0    | G7    | G6    | G5    | G4    | G3    | G2    | G1   | G0   | B7   | B6   | B5   | B4   | B3   | B2   | B1   | <b>B0</b> |

| 18 bits              | 1 <sup>st</sup> |       |       |       |       |       |       | R5    | R4    | R3    | R2    | R1    | R0    | G5    | G4    | G3   | G2   | G1   | G0   | B5   | B4   | B3   | B2   | B1   | <b>B0</b> |

| 16 bits (565 format) | 1 <sup>st</sup> |       |       |       |       |       |       |       |       | R5    | R4    | R3    | R2    | R1    | G5    | G4   | G3   | G2   | G1   | G0   | B5   | B4   | B3   | B2   | B1        |

|                      | 1 <sup>st</sup> |       |       |       |       |       |       |       |       | R7    | R6    | R5    | R4    | R3    | R2    | R1   | R0   | G7   | G6   | G5   | G4   | G3   | G2   | G1   | G0        |

| 16 bits              | 2 <sup>nd</sup> |       |       |       |       |       |       |       |       | B7    | B6    | B5    | B4    | B3    | B2    | B1   | B0   | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0        |

|                      | 3 <sup>rd</sup> |       |       |       |       |       |       |       |       | G7    | G6    | G5    | G4    | G3    | G2    | G1   | G0   | B7   | B6   | B5   | B4   | B3   | B2   | B1   | B0        |

| 12 bits              | 1 <sup>st</sup> |       |       |       |       |       |       |       |       |       |       |       |       | R7    | R6    | R5   | R4   | R3   | R2   | R1   | R0   | G7   | G6   | G5   | G4        |

| 12 Dits              | 2 <sup>nd</sup> |       |       |       |       |       |       |       |       |       |       |       |       | G3    | G2    | G1   | G0   | B7   | B6   | B5   | B4   | B3   | B2   | B1   | B0        |

| 9 bits               | 1 <sup>st</sup> |       |       |       |       |       |       |       |       |       |       |       |       |       |       |      | R5   | R4   | R3   | R2   | R1   | R0   | G5   | G4   | G3        |

| 9 bits               | 2 <sup>nd</sup> |       |       |       |       |       |       |       |       |       |       |       |       |       |       |      | G2   | G1   | G0   | B5   | B4   | B3   | B2   | B1   | B0        |

| 8 bits               | 1 <sup>st</sup> |       |       |       |       |       |       |       |       |       |       |       |       |       |       |      |      | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0        |

|                      | 2 <sup>nd</sup> |       |       |       |       |       |       |       |       |       |       |       |       |       |       |      |      | G7   | G6   | G5   | G4   | G3   | G2   | G1   | G0        |

|                      | 3 <sup>rd</sup> |       |       |       |       |       |       |       |       |       |       |       |       |       |       |      |      | B7   | B6   | B5   | B4   | B3   | B2   | B1   | B0        |

## **Timing Characteristics**

| Symbol             | Para                         | meter                                                       | Min                  | Тур                                                                    | Max     | Unit |

|--------------------|------------------------------|-------------------------------------------------------------|----------------------|------------------------------------------------------------------------|---------|------|

| f <sub>MCLK</sub>  | System Clock Frequency*      |                                                             | 1                    | -                                                                      | 110     | MHz  |

| t <sub>MCLK</sub>  | System Clock Period*         |                                                             | 1/ f <sub>MCLK</sub> | -                                                                      |         | ns   |

| t <sub>PWCSL</sub> | Control Pulse High Width     | Write<br>Read                                               | 13<br>30             | 1.5* t <sub>MCLK</sub><br>3.5* t <sub>MCLK</sub>                       | <u></u> | ns   |

| t <sub>PWCSH</sub> | Control Pulse Low Width      | Write (next write cycle)<br>Write (next read cycle)<br>Read | 13<br>80<br>80       | 1.5* t <sub>MCLK</sub><br>9* t <sub>MCLK</sub><br>9* t <sub>MCLK</sub> | -       | ns   |

| t <sub>AS</sub>    | Address Setup Time           |                                                             | 1                    | -                                                                      | -       | ns   |

| t <sub>AH</sub>    | Address Hold Time            |                                                             | 2                    | -                                                                      | -       | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time        |                                                             | 4                    | -                                                                      | -       | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time         |                                                             | 1                    | -                                                                      | -       | ns   |

| t <sub>PWLW</sub>  | Write Low Time               |                                                             | 12                   | -                                                                      | -       | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time          |                                                             | 1                    | -                                                                      | -       | ns   |

| t <sub>ACC</sub>   | Access Time                  |                                                             | 32                   | -                                                                      | 2       | ns   |

| t <sub>PWLR</sub>  | Read Low Time                |                                                             | 36                   | -                                                                      | -       | ns   |

| t <sub>R</sub>     | Rise Time                    |                                                             | -                    | -                                                                      | 0.5     | ns   |

| t <sub>F</sub>     | Fall Time                    |                                                             | -                    | -                                                                      | 0.5     | ns   |

| t <sub>CS</sub>    | Chip select setup time       |                                                             | 2                    | -                                                                      | -       | ns   |

| t <sub>CSH</sub>   | Chip select hold time to rea | ad signal                                                   | 3                    | -                                                                      | -       | ns   |

#### Parallel 8080-series Interface Timing

\* System Clock denotes external input clock (PLL-bypass) or internal generated clock (PLL-enabled)

### **Quality Information**

| Test Item                | Content of Test                             | Test Condition                 | Note |

|--------------------------|---------------------------------------------|--------------------------------|------|

| High Temperature storage | Endurance test applying the high            | +80°C , 200hrs                 | 2    |

|                          | storage temperature for a long time.        |                                |      |

| Low Temperature storage  | Endurance test applying the low storage     | -30°C , 200hrs                 | 1,2  |

|                          | temperature for a long time.                |                                |      |

| High Temperature         | Endurance test applying the electric stress | +70°C 200hrs                   | 2    |

| Operation                | (voltage & current) and the high thermal    |                                |      |

|                          | stress for a long time.                     |                                |      |

| Low Temperature          | Endurance test applying the electric stress | -20°C , 200hrs                 | 1,2  |

| Operation                | (voltage & current) and the low thermal     |                                |      |

|                          | stress for a long time.                     |                                |      |

| High Temperature /       | Endurance test applying the electric stress | +60°C , 90% RH , 96hrs         | 1,2  |

| Humidity Storage         | (voltage & current) and the high thermal    |                                |      |

|                          | with high humidity stress for a long time.  |                                |      |

| Thermal Shock resistance | Endurance test applying the electric stress | -20°C,30min -> 25°C,5min ->    |      |

|                          | (voltage & current) during a cycle of low   | 70°C,30min = 1 cycle           |      |

|                          | and high thermal stress.                    | 10 cycles                      |      |

| Vibration test           | Endurance test applying vibration to        | 10-55Hz , 15mm amplitude.      | 3    |

|                          | simulate transportation and use.            | 60 sec in each of 3 directions |      |

|                          |                                             | X,Y,Z                          |      |

|                          |                                             | For 15 minutes                 |      |

| Static electricity test  | Endurance test applying electric static     | VS=800V, RS=1.5kΩ, CS=100pF    |      |

|                          | discharge.                                  | One time                       |      |

Note 1: No condensation to be observed.

Note 2: Conducted after 4 hours of storage at 25°C, 0%RH.

Note 3: Test performed on product itself, not inside a container.

## Precautions for using LCDs/LCMs

See Precautions at <a href="http://www.newhavendisplay.com/specs/precautions.pdf">www.newhavendisplay.com/specs/precautions.pdf</a>

#### Warranty Information and Terms & Conditions

http://www.newhavendisplay.com/index.php?main\_page=terms