# FOUR-CHANNEL AUTOMOTIVE DIGITAL AMPLIFIERS

## FEATURES

- TAS5414 Single-Ended Input

- TAS5424 Differential Input

- Four-Channel Digital Power Amplifier

- Four Analog Inputs, Four BTL Power Outputs

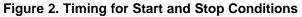

- Typical Output Power per Channel at 10% THD+N

- 28 W/Ch Into 4  $\Omega$  at 14.4 Vdc

- 45 W/Ch Into 2  $\Omega$  at 14.4 Vdc

- 58 W/Ch Into 4  $\Omega$  at 21 Vdc

- 116 W/Ch Into 2  $\Omega$  at 21 Vdc PBTL

- Channels Can Be Paralleled (PBTL) for 1-Ω Applications

- THD+N < 0.02%, 1 kHz, 1 W Into 4 Ω

- Patented Pop- and Click-Reduction Technology

- Soft Muting With Gain Ramp Control

- Common-Mode Ramping

- Patented AM Interference Avoidance

- Patented Cycle-by-Cycle Current Limit

- 75-dB PSRR

- Four-Address I<sup>2</sup>C Serial Interface for Device Configuration and Control

- Configurable Channel Gains: 12-dB, 20-dB, 26-dB, 32-dB

- Load Diagnostic Functions:

- Output Open and Shorted Load

- Output-to-Power and -to-Ground Shorts

- Patented Tweeter Detection

- Protection and Monitoring Functions:

- Short-Circuit Protection

- Load-Dump Protection to 50 V

- Fortuitous Open Ground and Power Tolerant

- Patented Output DC Level Detection While Music Playing

- Overtemperature Protection

- Over- and Undervoltage Conditions

- Clip Detection

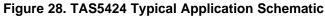

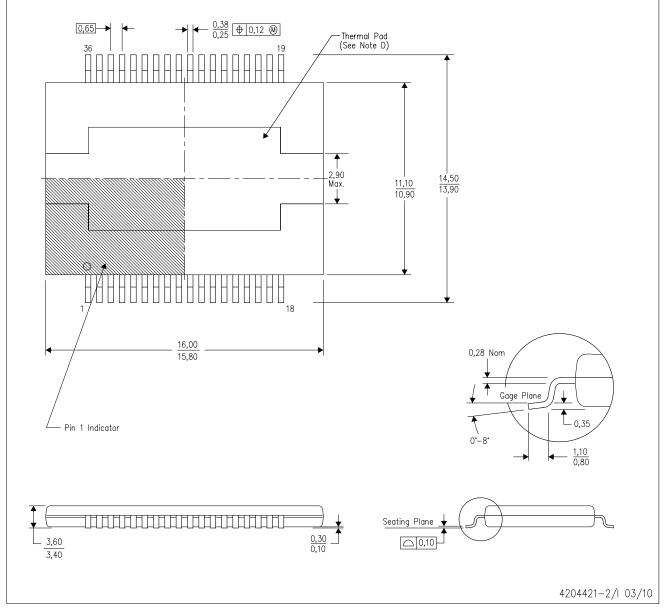

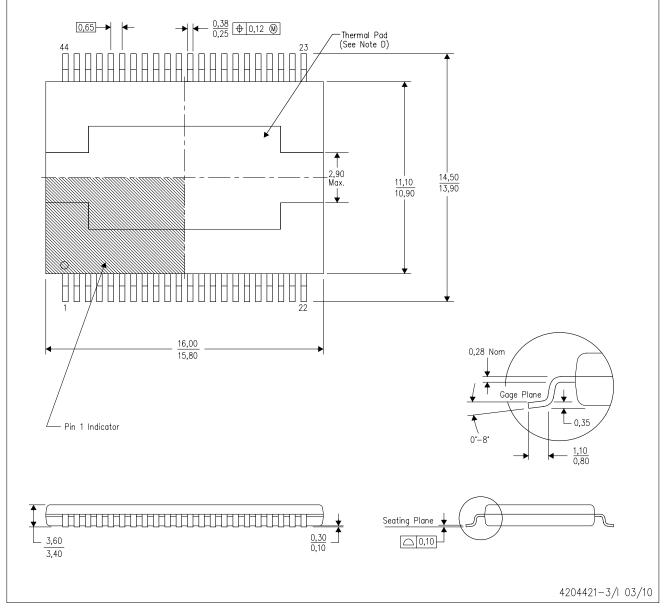

- 36-Pin PSOP3 (DKD) Power SOP Package

With Heat Slug Up for the TAS5414

- 44-Pin PSOP3 (DKD) Power SOP Package With Heat Slug Up for the TAS5424

- Designed for Automotive EMC Requirements

- Pb-Free Soldering Supported

- AECQ100 Compliant

- ISO9000:2002 TS16949 Certified

- -40°C to 105°C Ambient Temperature Range

## APPLICATIONS

High-power OEM/retail head units and amplifier modules where feature densities and system configurations require reduction in heat from the audio power amplifier

## DESCRIPTION

The TAS5414 and TAS5424 are four-channel digital audio amplifiers designed for use in automotive head units and external amplifier modules. The TAS5414 and TAS5424 provide four channels at 23 W continuously into 4  $\Omega$  at less than 1% THD+N from a 14.4-V supply. Each channel can also deliver 38 W into 2  $\Omega$  at 1% THD+N. The TAS5414 uses single-ended analog inputs, while the TAS5424 employs differential inputs for increased immunity to common-mode system noise. The digital PWM topology of the TAS5414 and TAS5424 provides dramatic improvements in efficiency over traditional linear amplifier solutions. This reduces the power dissipated by the amplifier by a factor of ten under typical music playback conditions. High efficiency is accomplished without the need for complicated power-supply schemes. Multiple TAS5414s or TAS5424s be synchronized to can meet high-channel-count applications.

The TAS5414 and TAS5424 incorporate all the functionality needed to perform in the demanding OEM applications area. They have built-in load diagnostic functions for detecting and diagnosing misconnected outputs to help to reduce test time during the manufacturing process.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

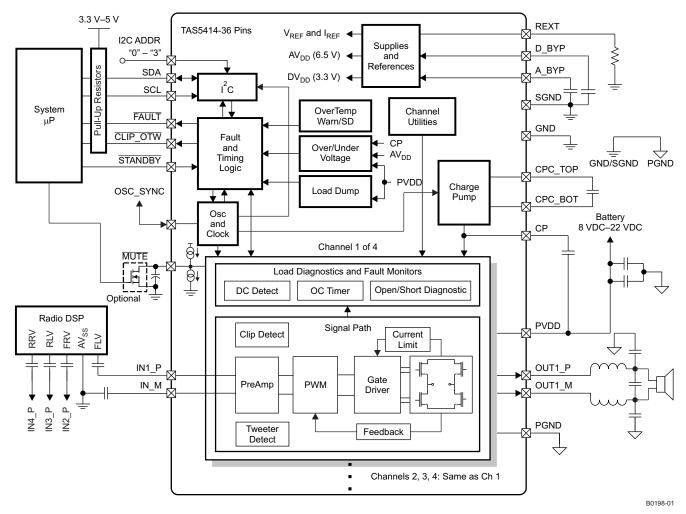

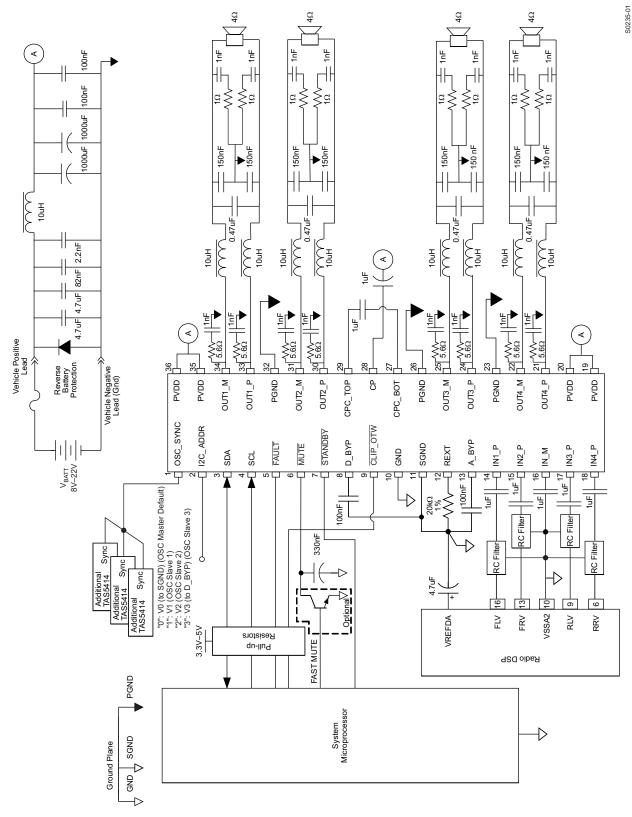

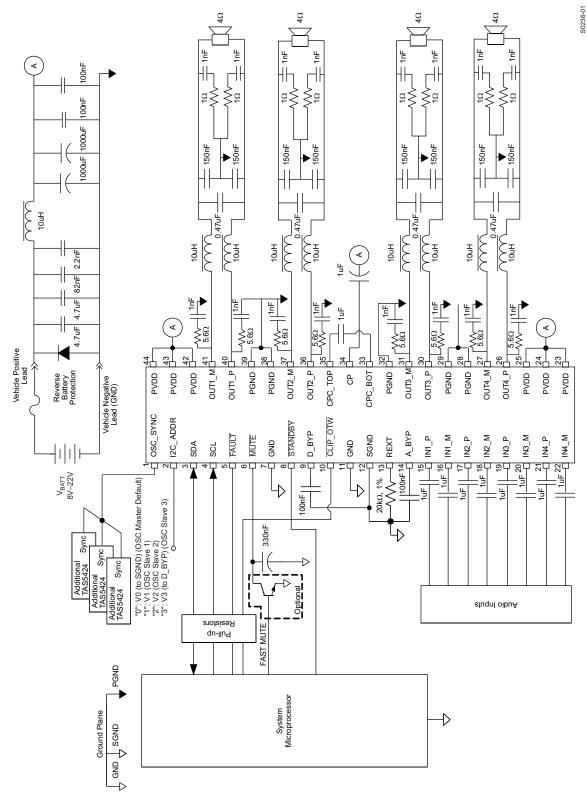

**TAS5414 FUNCTIONAL BLOCK DIAGRAM**

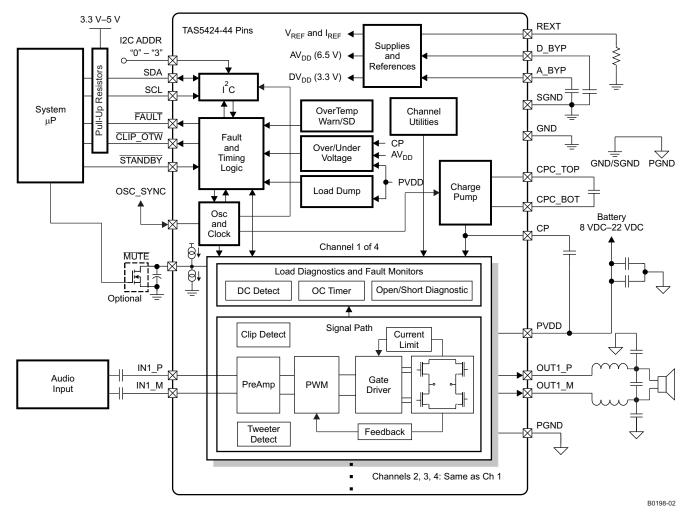

**TAS5424 FUNCTIONAL BLOCK DIAGRAM**

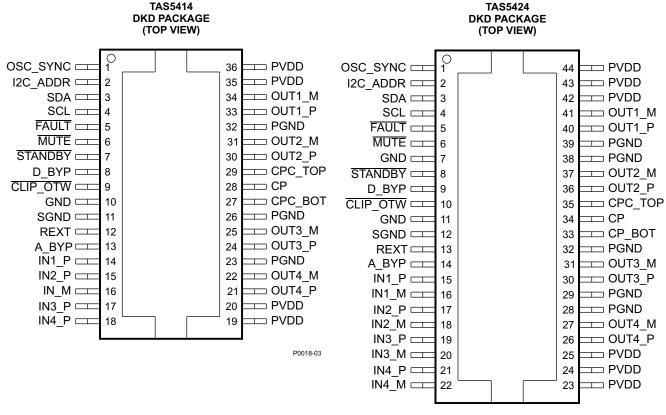

## **PIN ASSIGNMENTS AND FUNCTIONS**

The pin assignments for the TAS5414 and TAS5424 are shown as follows.

P0055-01

#### Table 1. TERMINAL FUNCTIONS

| TERMINAL |                   |                              |                     |                                                                                                                         |

|----------|-------------------|------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

|          | DKD P             | ackage                       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                             |

| NAME     | TAS5414<br>NO.    | TAS5424<br>NO.               |                     |                                                                                                                         |

| A_BYP    | 13                | 14                           | PBY                 | Bypass capacitor for the AVDD analog regulator                                                                          |

| CLIP_OTW | 9                 | 10                           | DO                  | Open-drain CLIP, OTW, or logical OR of the CLIP and OTW outputs. It also reports tweeter detection during tweeter mode. |

| CP       | 28                | 34                           | CP                  | Top of main storage capacitor for charge pump (bottom goes to PVDD)                                                     |

| CPC_BOT  | 27                | 33                           | CP                  | Bottom of flying capacitor for charge pump                                                                              |

| CPC_TOP  | 29                | 35                           | CP                  | Top of flying capacitor for charge pump                                                                                 |

| D_BYP    | 8                 | 9                            | PBY                 | Bypass pin for DVDD regulator output                                                                                    |

| FAULT    | 5                 | 5                            | DO                  | Global fault output (open drain): UV, OV, OTSD, OCSD, DC                                                                |

| GND      | 10                | 7, 11                        | DG                  | Ground                                                                                                                  |

| I2C_ADDR | 2                 | 2                            | AI                  | I <sup>2</sup> C address bit                                                                                            |

| IN1_M    | N/A               | 16                           | AI                  | Inverting analog input for channel 1 (TAS5424 only)                                                                     |

| IN1_P    | 14                | 15                           | AI                  | Non-inverting analog input for channel 1                                                                                |

| IN2_M    | N/A               | 18                           | AI                  | Inverting analog input for channel 2 (TAS5424 only)                                                                     |

| IN2_P    | 15                | 17                           | AI                  | Non-inverting analog input for channel 2                                                                                |

| IN3_M    | N/A               | 20                           | AI                  | Inverting analog input for channel 3 (TAS5424 only)                                                                     |

| IN3_P    | 17                | 19                           | AI                  | Non-inverting analog input for channel 3                                                                                |

| IN4_M    | N/A               | 22                           | AI                  | Inverting analog input for channel 4 (TAS5424 only)                                                                     |

| IN4_P    | 18                | 21                           | AI                  | Non-inverting analog input for channel 4                                                                                |

| IN_M     | 16                | N/A                          | ARTN                | Signal return for the 4 analog channel inputs (TAS5414 only)                                                            |

| MUTE     | 6                 | 6                            | AI                  | Gain ramp control: mute (low), play (high)                                                                              |

| OSC_SYNC | 1                 | 1                            | DI/DO               | Oscillator sync input from master or output to slave amplifiers (20 MHz divided by 5, 6, or 7)                          |

| OUT1_M   | 34                | 41                           | PO                  | - polarity output for bridge 1                                                                                          |

| OUT1_P   | 33                | 40                           | PO                  | + polarity output for bridge 1                                                                                          |

| OUT2_M   | 31                | 37                           | PO                  | - polarity output for bridge 2                                                                                          |

| OUT2_P   | 30                | 36                           | PO                  | + polarity output for bridge 2                                                                                          |

| OUT3_M   | 25                | 31                           | PO                  | - polarity output for bridge 3                                                                                          |

| OUT3_P   | 24                | 30                           | PO                  | + polarity output for bridge 3                                                                                          |

| OUT4_M   | 22                | 27                           | PO                  | - polarity output for bridge 4                                                                                          |

| OUT4_P   | 21                | 26                           | PO                  | + polarity output for bridge 4                                                                                          |

| PGND     | 23, 26,<br>32     | 28, 29,<br>32, 38,<br>39     | PGND                | Power GND                                                                                                               |

| PVDD     | 19, 20,<br>35, 36 | 23, 24,<br>25, 42,<br>43, 44 | PWR                 | PVDD supply                                                                                                             |

| REXT     | 12                | 13                           | AI                  | Precision resistor pin to set clock frequency                                                                           |

| SCL      | 4                 | 4                            | DI                  | I <sup>2</sup> C clock input from system I <sup>2</sup> C master                                                        |

| SDA      | 3                 | 3                            | DI/DO               | I <sup>2</sup> C data I/O for communication with system I <sup>2</sup> C master                                         |

| SGND     | 11                | 12                           | AG/DG               | Signal ground (analog and digital signal ground)                                                                        |

| STANDBY  | 7                 | 8                            | DI                  | Active-low STANDBY pin. Standby (low), power up (high)                                                                  |

(1) DI = digital input, DO = digital output, AI = analog input, ARTN = analog signal return, PWR = power supply, PGND = power ground, PBY = power bypass, PO = power output, AG = analog ground, DG = digital ground, CP = charge pump.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                                   |                                                                                              |                                              | VALUE                   | UNIT |

|-----------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------|------|

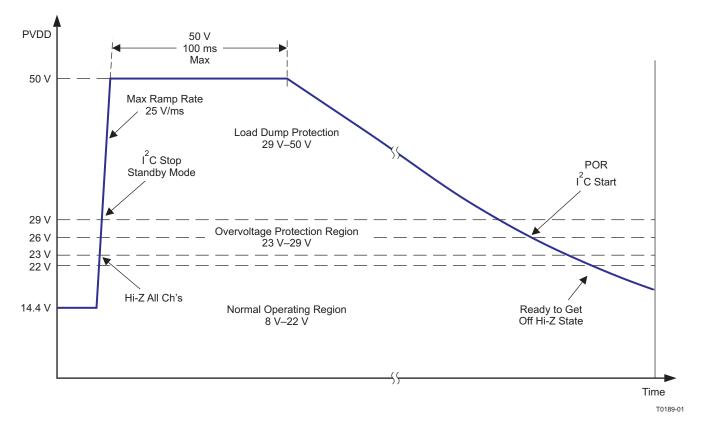

| PVDD                              | DC supply voltage range                                                                      | Relative to PGND                             | -0.3 to 30              | V    |

| PVDD <sub>MAX</sub>               | Pulsed supply voltage range                                                                  | t ≤ 100 ms exposure                          | -1 to 50                | V    |

| PVDD <sub>RAMP</sub>              | Supply voltage ramp rate                                                                     | Voltage rising up to PVDD <sub>MAX</sub>     | 25                      | V/ms |

| I <sub>PVDD</sub>                 | Externally imposed dc supply current per PVDD or PGND pin                                    |                                              | ±12                     | А    |

| PVDD_MAX                          | Pulsed supply current per PVDD pin (one shot)                                                | t < 100 ms                                   | 17                      | Α    |

| Io                                | Maximum allowed dc current per output pin                                                    |                                              | ±13.5                   | А    |

| I <sub>O_MAX</sub> <sup>(1)</sup> | Pulsed output current per output pin (single pulse)                                          | t < 100 ms                                   | ±17                     | А    |

| I <sub>IN_MAX</sub>               | Maximum current, all digital and analog input pins <sup>(2)</sup>                            | DC or pulsed                                 | ±1                      | mA   |

| I <sub>MUTE_MAX</sub>             | Maximum current on MUTE pin                                                                  | DC or pulsed                                 | ±20                     | mA   |

| I <sub>IN_ODMAX</sub>             | Maximum sinking current for open-drain pins                                                  |                                              | 7                       | mA   |

| V <sub>LOGIC</sub>                | Input voltage range for logic pin relative to SGND (SCL and SDA pins)                        | Supply voltage range:<br>6.5 V < PVDD < 24 V | -0.3 to 7               | V    |

| V <sub>I2C_ADDR</sub>             | Input voltage range for I2C_ADDR pin relative to SGND                                        | -0.3 to 7                                    | V                       |      |

| V <sub>STANDBY</sub>              | Input voltage range for STANDBY pin                                                          | Supply voltage range:<br>6.5 V < PVDD < 24V  | -0.3 to 5.8             | V    |

| V <sub>OSC_SYNC</sub>             | Input voltage range for OSC_SYNC pin relative to SGND                                        | Supply voltage range:<br>6.5 V < PVDD < 24 V | -0.3 to 3.6             | V    |

| V <sub>AIN_MAX</sub>              | Maximum instantaneous input voltage (per pin), analog input pins                             | Supply voltage range:<br>6.5 V < PVDD < 24 V | 6.5                     | V    |

| Vain_ac_max_5414                  | Maximum ac coupled input voltage for TAS5414 <sup>(2)</sup> , analog input pins              | Supply voltage range:<br>6.5 V < PVDD < 24 V | 1.9                     | Vrms |

| V <sub>AIN_AC_MAX_5424</sub>      | Maximum ac coupled differential input voltage for TAS5424 <sup>(2)</sup> , analog input pins | Supply voltage range:<br>6.5 V < PVDD < 24 V | 3.8<br>(1.9 per<br>pin) | Vrms |

| V <sub>AIN_DC</sub>               | Input voltage range for analog pin relative to AGND (INx pins)                               | Supply voltage range:<br>6.5 V < PVDD < 24 V | -0.3 to 6.5             | V    |

| TJ                                | Maximum operating junction temperature range                                                 |                                              | -55 to 150              | °C   |

| T <sub>stg</sub>                  | Storage temperature range                                                                    |                                              | -55 to 150              | °C   |

| T <sub>SOLDER</sub>               | Lead temperature during soldering 1,6 mm (1/16 inch) from case for 10 seconds                |                                              | 260                     | °C   |

| Power dissipation                 | Continuous power dissipation                                                                 | T <sub>case</sub> = 70°C                     | 80                      | W    |

(1) Pulsed current ratings are maximum survivable currents externally applied to the TAS5414 and TAS5424. High currents may be encountered during reverse battery, fortuitous open ground, and fortuitous open supply fault conditions.

(2) See *Application Information* section for information on analog input voltage and ac coupling.

#### **THERMAL CHARACTERISTICS**

|                       | PARAMETER                                       | VALUE                                                                                                                                               | UNIT |

|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $R_{	extsf{	heta}JC}$ | Junction-to-case (heat slug) thermal resistance | 1                                                                                                                                                   | °C/W |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance          | This device is not intended to be used without a heatsink. Therefore, $R_{\theta JA}$ is not specified. See the <i>Thermal Information</i> section. | °C/W |

## **RECOMMENDED OPERATING CONDITIONS**<sup>(1)</sup>

|                                      |                                                                                                                                  |                                                                               | MIN  | TYP      | MAX                   | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|----------|-----------------------|------|

| PVDD <sub>OP</sub>                   | DC supply voltage range relative to PGND                                                                                         |                                                                               | 8    | 14.4     | 22                    | V    |

| PVDD <sub>I2C</sub>                  | DC supply voltage range for I <sup>2</sup> C reporting                                                                           |                                                                               | 6    | 14.4     | 26.5                  | V    |

| V <sub>AIN_5414</sub> <sup>(2)</sup> | Analog audio input signal level (TAS5414)                                                                                        | AC-coupled input voltage                                                      | 0    |          | 0.25–1 <sup>(3)</sup> | Vrms |

| V <sub>AIN_5424</sub> <sup>(2)</sup> | Analog audio input signal level (TAS5424)                                                                                        | AC-coupled input voltage                                                      | 0    |          | 0.5–2 <sup>(3)</sup>  | Vrms |

| f <sub>AUDIO_TW</sub>                | Audio frequency for tweeter detect                                                                                               |                                                                               | 10   | 20       | 25                    | kHz  |

| T <sub>A</sub>                       | Ambient temperature                                                                                                              |                                                                               | -40  |          | 105                   | °C   |

| TJ                                   | Junction temperature                                                                                                             | An adequate heat sink is required to keep $T_J$ within specified range        | -40  |          | 115                   | °C   |

| RL                                   | Nominal speaker load impedance                                                                                                   |                                                                               | 2    | 4        |                       | Ω    |

| V <sub>PU</sub>                      | Pullup voltage supply (for open-drain logic outputs)                                                                             |                                                                               | 3    | 3.3 or 5 | 5.5                   | V    |

| R <sub>PU_EXT</sub>                  | External pullup resistor on open-drain logic outputs                                                                             | Resistor connected between open-drain logic output and $V_{\text{PU}}$ supply | 10   | 50       | 100                   | kΩ   |

| R <sub>PU_I2C</sub>                  | I <sup>2</sup> C pullup resistance on SDA and SCL pins                                                                           |                                                                               | 1    | 5        | 10                    | kΩ   |

| R <sub>I2C_ADD</sub>                 | Total resistance of voltage divider for I <sup>2</sup> C address<br>slave 1 or slave 2, connected between D_BYP and<br>SGND pins |                                                                               | 10   |          | 100                   | kΩ   |

| R <sub>REXT</sub>                    | External resistance on REXT pin                                                                                                  | 1% tolerance required                                                         | 19.8 | 20       | 20.2                  | kΩ   |

| C <sub>D_BYP</sub>                   | External capacitance on D_BYP pin                                                                                                |                                                                               | 10   |          | 120                   | nF   |

| C <sub>A_BYP</sub>                   | External capacitance on A_BYP pin                                                                                                |                                                                               | 10   |          | 120                   | nF   |

| C <sub>IN</sub>                      | External capacitance to analog input pin in series<br>with input signal                                                          |                                                                               |      | 1        |                       | μF   |

| C <sub>FLY</sub>                     | Flying capacitor on charge pump                                                                                                  |                                                                               | 0.47 | 1        | 1.5                   | μF   |

| C <sub>P</sub>                       | Charge pump capacitor                                                                                                            |                                                                               | 0.47 | 1        | 1.5                   | μF   |

| C <sub>MUTE</sub>                    | Capacitance on MUTE pin                                                                                                          |                                                                               | 3.3  | 330      |                       | nF   |

| C <sub>OSCSYNC_MAX</sub>             | Allowed loading capacitance on OSC_SYNC pin                                                                                      |                                                                               |      | 5        |                       | рF   |

The Recommended Operating Conditions table specifies only that the device is functional in the given range. See the Electrical Characteristics table for specified performance limits.

Signal input for full unclipped output with gains of 32 dB, 26 dB, 20 dB, and 12 dB

(3) Maximum recommended input voltage is determined by the gain setting.

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise noted):  $T_{Case} = 25^{\circ}C$ , PVDD = 14.4 V,  $R_L = 4 \Omega$ ,  $f_S = 417 \text{ kHz}$ , Rext = 20 k $\Omega$ , master mode operation (see application diagram)

|                          | PARAMETER                                       | TEST CONDITIONS                                                                      | MIN  | TYP   | MAX  | UNIT |

|--------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|------|-------|------|------|

| OPERATING C              | CURRENT                                         |                                                                                      |      |       |      |      |

| I <sub>PVDD_IDLE</sub>   |                                                 | All four channels running in MUTE mode                                               |      | 240   | 300  |      |

| I <sub>PVDD_Hi-Z</sub>   | PVDD idle current                               | All four channels in Hi-Z mode                                                       |      | 80    |      | mA   |

| I <sub>PVDD_STBY</sub>   | PVDD standby current                            | STANDBY mode, $T_J \le 85^{\circ}C$                                                  |      | 2     | 20   | μA   |

| OUTPUT POW               | /ER                                             |                                                                                      |      |       |      |      |

|                          |                                                 | 4 $\Omega$ , PVDD = 14.4V, THD+N $\leq$ 1%, 1 kHz, T <sub>c</sub> = 75°C             |      | 23    |      |      |

|                          |                                                 | 4 Ω, PVDD = 14.4V, THD+N = 10%, 1 kHz, $T_c = 75^{\circ}C$                           | 25   | 28    |      |      |

|                          |                                                 | 4 $\Omega$ , PVDD = 14.4V, square wave, 1 kHz, T <sub>c</sub> = 75°C                 |      | 43    |      |      |

|                          |                                                 | 4 Ω, PVDD = 21 V, THD+N = 1%, 1 kHz, $T_c = 75^{\circ}C$                             |      | 47    |      |      |

|                          |                                                 | 4 Ω, PVDD = 21 V, THD+N = 10%, 1 kHz, $T_c = 75^{\circ}C$                            | 50   | 58    |      |      |

| P <sub>OUT</sub>         | Output power per channel                        | 2 Ω, PVDD = 14.4V, THD+N = 1%, 1 kHz, $T_c = 75^{\circ}C$                            |      | 38    |      | W    |

| 001                      |                                                 | 2 Ω, PVDD = 14.4V, THD+N = 10%, 1 kHz, T <sub>c</sub> = 75°C                         | 40   | 45    |      |      |

|                          |                                                 | 2 $\Omega$ , PVDD = 14.4 V, square wave 1 kHz, T <sub>c</sub> = 75°C                 |      | 70    |      |      |

|                          |                                                 | PBTL 2-Ω operation, PVDD = 21 V, THD+N = 10%, 1 kHz, $T_c = 75^{\circ}C$             |      | 116   |      |      |

|                          |                                                 | PBTL 1- $\Omega$ operation, PVDD = 14.4 V, THD+N = 10%, 1 kHz, T <sub>c</sub> = 75°C |      | 90    |      |      |

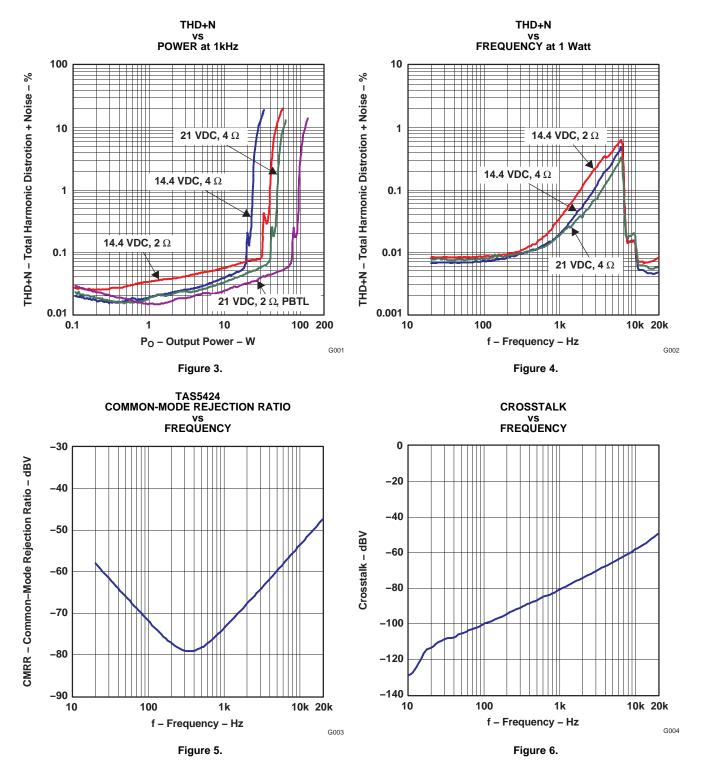

| EFF <sub>P</sub>         | Power efficiency                                | 4 channels operating, 23W output power/ch, L = 10 $\mu H,$ $T_J \leq 85^\circ C$     |      | 90%   |      |      |

| AUDIO PERFO              | DRMANCE                                         |                                                                                      |      |       |      |      |

| V <sub>NOISE</sub>       | Noise voltage at output                         | G = 26 dB, zero input, AES17 filter, and A-weighting                                 |      | 60    | 100  | μV   |

| Crosstalk                | Channel crosstalk                               | 1W, G = 26 dB, 1 kHz                                                                 | 60   | 75    |      | dB   |

| CMRR <sub>5424</sub>     | Common-mode rejection ratio (TAS5424)           | 1 kHz, 1 Vrms referenced to SGND, G = 26 dB                                          | 60   | 75    |      | dB   |

| PSRR                     | Power supply rejection ratio                    | G = 26 dB, PVDD = 14.4 Vdc + 1 Vrms, f = 1 kHz                                       | 60   | 75    |      | dB   |

| THD+N                    | Total harmonic distortion + noise               | $P=1\ W,\ G=26\ dB,\ f=1\ kHz,\ 0^\circC\leqT_J\leq75^\circC$                        |      | 0.02% | 0.1% |      |

|                          |                                                 |                                                                                      |      | 357   | 378  |      |

| f <sub>S</sub>           | Switching frequency                             | Switching frequency selectable for AM interference avoidance                         | 392  | 417   | 442  | kHz  |

|                          |                                                 |                                                                                      | 470  | 500   | 530  |      |

| R <sub>AIN</sub>         | Analog input resistance                         | Internal shunt resistance on each input pin                                          | 60   | 80    | 100  | kΩ   |

| V <sub>IN_CM</sub>       | Common-mode input voltage (non-clipping)        | AC-coupled common-mode input voltage (zero differential input)                       |      |       | 1.3  | Vrms |

| V <sub>CM_INT</sub>      | Internal common-mode input bias voltage         | Internal bias applied to IN_M pin                                                    |      | 3.25  |      | V    |

|                          |                                                 |                                                                                      | 11   | 12    | 13   |      |

| 0                        |                                                 | Source impedance = 0 $\Omega$                                                        |      | 20    | 21   | 10   |

| G                        | Voltage gain (V <sub>O</sub> /V <sub>IN</sub> ) |                                                                                      |      | 26    | 27   | dB   |

|                          |                                                 |                                                                                      |      | 32    | 33   |      |

| G <sub>CH</sub>          | Channel-to-channel variation                    | Any gain commanded                                                                   | -1   | 0     | 1    | dB   |

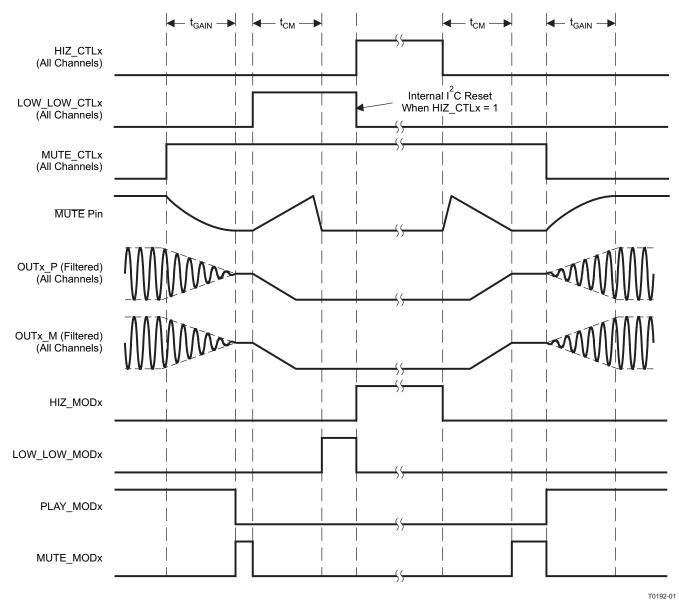

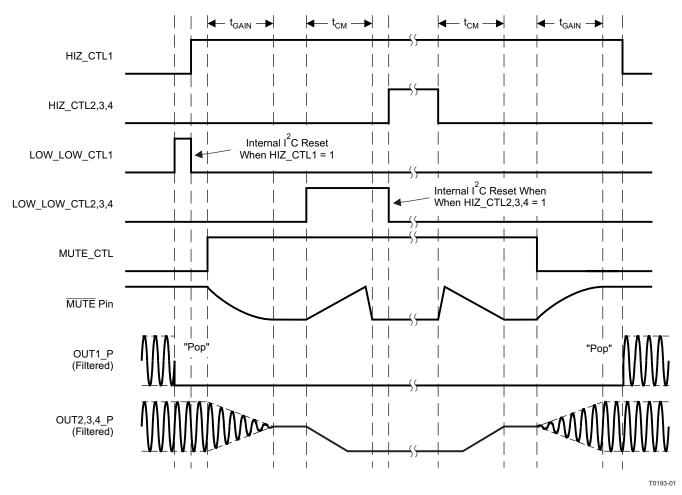

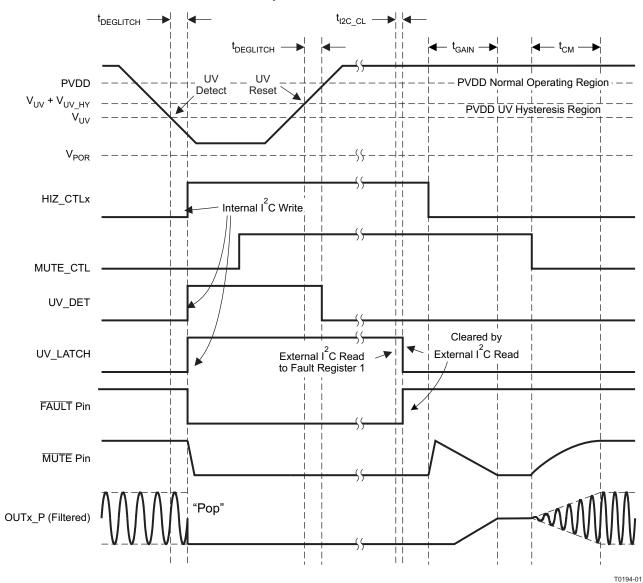

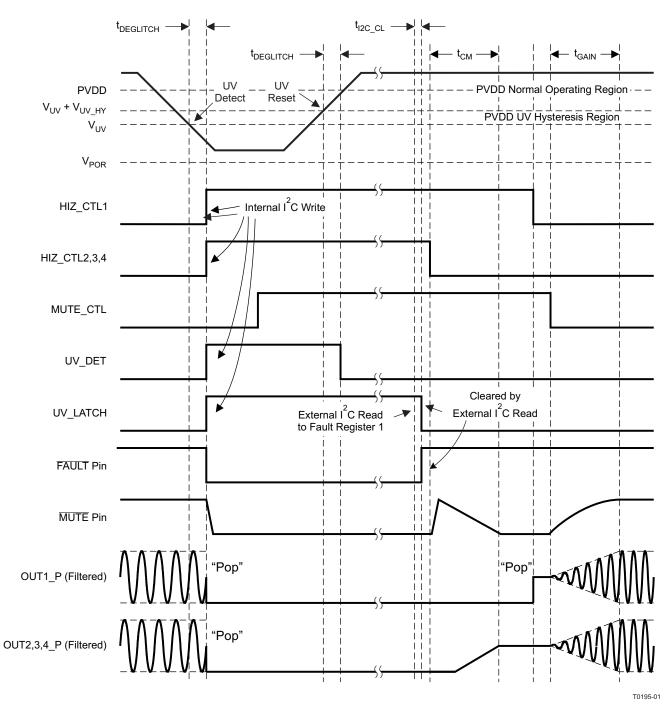

| t <sub>CM</sub>          | Output-voltage common-mode ramping time         |                                                                                      |      | 35    |      | ms   |

| t <sub>GAIN</sub>        | Gain ramping time                               | External C <sub>MUTE</sub> = 330 nF                                                  |      | 30    |      | ms   |

| PWM OUTPUT               | STAGE                                           |                                                                                      |      |       |      |      |

| R <sub>DSon</sub>        | FET Drain-to-source resistance                  | Not including bond wire resistance, $T_J = 25^{\circ}C$                              |      | 75    | 95   | mΩ   |

| V <sub>O_OFFSET</sub>    | Output offset voltage                           | Zero input signal and G = 26 dB                                                      |      | ±10   | ±25  | mV   |

|                          | OLTAGE (OV) PROTECTION                          | 1                                                                                    |      |       |      |      |

| V <sub>OV</sub>          | PVDD over voltage shutdown                      |                                                                                      | 22.1 | 23.7  | 26.3 | V    |

|                          | LD) PROTECTION                                  | 1                                                                                    | 1    |       |      |      |

| V <sub>LD_SD_SET</sub>   | Load-dump shutdown voltage                      |                                                                                      | 26.6 | 29    | 32   | V    |

| V <sub>LD SD CLEAR</sub> | Recovery voltage for load-dump shutdown         |                                                                                      | 23.5 | 26.4  | 28.4 | V    |

|                          | VOLTAGE (UV) PROTECTION                         | 1                                                                                    | 1    |       |      |      |

| V <sub>UV_SET</sub>      | PVDD under voltage shutdown                     |                                                                                      | 6.5  | 7     | 7.5  | V    |

| V <sub>UV_CLEAR</sub>    | Recovery voltage for PVDD UV                    |                                                                                      | 7    | 7.5   | 8    | V    |

## ELECTRICAL CHARACTERISTICS (continued)

Test conditions (unless otherwise noted):  $T_{Case} = 25^{\circ}C$ , PVDD = 14.4 V,  $R_L = 4 \Omega$ ,  $f_S = 417 \text{ kHz}$ , Rext = 20 k $\Omega$ , master mode operation (see application diagram)

|                                                    | PARAMETER                                                                      | TEST CONDITIONS                                                                    | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|------|

| AVDD                                               |                                                                                |                                                                                    | 1    |      |      |      |

| V <sub>A_BYP</sub>                                 | A_BYP pin voltage                                                              |                                                                                    |      | 6.5  |      | V    |

| V <sub>A_BYP_UV_SET</sub>                          | A_BYP UV voltage                                                               |                                                                                    |      | 4.8  |      | V    |

| V <sub>A_BYP_UV_CLEAR</sub>                        | Recovery voltage A_BYP UV                                                      |                                                                                    |      | 5.3  |      | V    |

| DVDD                                               |                                                                                |                                                                                    |      |      |      |      |

| V <sub>D_BYP</sub>                                 | D_BYP pin voltage                                                              |                                                                                    |      | 3.3  |      | V    |

| POWER-ON RES                                       |                                                                                |                                                                                    |      |      |      |      |

| V <sub>POR</sub>                                   | Maximum PVDD voltage for POR; I <sup>2</sup> C active above this voltage       |                                                                                    |      |      | 6    | V    |

| V <sub>POR_HY</sub>                                | PVDD recovery hysteresis voltage for POR                                       |                                                                                    |      | 0.1  |      | V    |

| REXT                                               |                                                                                |                                                                                    |      |      |      |      |

| V <sub>REXT</sub>                                  | Rext pin voltage                                                               |                                                                                    |      | 1.24 |      | V    |

| CHARGE PUMP                                        | (CP)                                                                           |                                                                                    |      |      |      |      |

| V <sub>CPUV_SET</sub>                              | CP undervoltage                                                                |                                                                                    |      | 4.8  |      | V    |

| V <sub>CPUV_CLEAR</sub>                            | Recovery voltage for CP UV                                                     |                                                                                    |      | 5.2  |      | V    |

|                                                    | TURE (OV) PROTECTION                                                           | 1                                                                                  | 1    |      |      |      |

| T <sub>OTW1 CLEAR</sub>                            |                                                                                |                                                                                    | 102  | 115  | 128  |      |

| T <sub>OTW1_SET</sub> /<br>T <sub>OTW2_CLEAR</sub> |                                                                                |                                                                                    | 112  | 125  | 138  |      |

| T <sub>OTW2_SET</sub> /<br>T <sub>OTW3 CLEAR</sub> | <ul> <li>Junction temperature for overtemperature<br/>warning</li> </ul>       |                                                                                    | 122  | 135  | 148  | °C   |

| T <sub>OTW3_SET</sub> /<br>T <sub>OTWD_CLEAR</sub> |                                                                                |                                                                                    | 132  | 145  | 158  |      |

| T <sub>OTSD</sub>                                  | Junction temperature for overtemperature shutdown                              |                                                                                    | 142  | 155  | 168  |      |

| CURRENT LIMIT                                      | ING PROTECTION                                                                 |                                                                                    |      |      |      |      |

| I <sub>LIM1</sub>                                  | Current limit 1 (load current)                                                 | Load < 4 $\Omega$                                                                  | 5.5  | 7.3  | 9    | А    |

| I <sub>LIM2</sub>                                  | Current limit 2 (load current), I <sup>2</sup> C setting current limit level 2 | Load < 2 $\Omega$                                                                  | 8.5  | 11   | 13.5 | А    |

| OVERCURRENT                                        | (OC) SHUTDOWN PROTECTION                                                       |                                                                                    |      |      |      |      |

| I <sub>MAX1</sub>                                  | Maximum current 1 (peak output current)                                        |                                                                                    | 9.5  | 11.3 | 13   | А    |

| I <sub>MAX2</sub>                                  | Maximum current 2 (peak output current)                                        | Any short to supply, ground, or other channels                                     | 11.5 | 14.3 | 17   | А    |

| TWEETER DETE                                       | СТ                                                                             | 1                                                                                  |      |      |      |      |

| I <sub>TH TW</sub>                                 | Load current threshold for tweeter detect                                      |                                                                                    | 325  | 540  | 750  | mA   |

|                                                    | Load current limit for tweeter detect                                          |                                                                                    |      | 2    |      | А    |

| STANDBY MODE                                       |                                                                                |                                                                                    |      |      |      |      |

| V <sub>IH_STBY</sub>                               | STANDBY input voltage for logic-level high                                     |                                                                                    | 2    |      | 5.5  | V    |

| V <sub>IL_STBY</sub>                               | STANDBY input voltage for logic-level low                                      |                                                                                    | 0    |      | 0.7  | V    |

|                                                    | STANDBY pin current                                                            |                                                                                    |      | 0.1  | 0.2  | μA   |

| MUTE MODE                                          | •                                                                              | 1                                                                                  | 1    |      |      |      |

| G <sub>MUTE</sub>                                  | Output attenuation                                                             | $\overline{\text{MUTE}}$ pin $\leq$ 0.9Vdc, V <sub>IN</sub> = 1 Vrms on all inputs |      | 85   |      | dB   |

| DC DETECT                                          | ·                                                                              | · · · · · · · · · · · · · · · · ·                                                  | 1    |      |      |      |

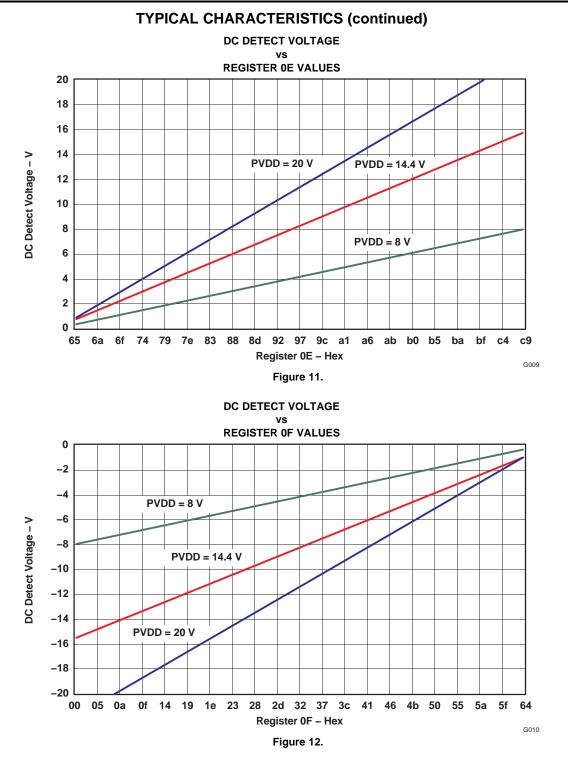

| V <sub>TH_DCD_POS</sub>                            | DC detect positive threshold default value                                     | PVDD = 14.4 Vdc, register 0x0E = 8EH                                               |      | 6.5  |      | V    |

| V <sub>TH_DCD_NEG</sub>                            | DC detect negative threshold default value                                     | PVDD = 14.4 Vdc, register 0x0F = 3DH                                               |      | -6.5 |      | V    |

| t <sub>DCD</sub>                                   | DC detect step response time for four channels                                 |                                                                                    |      |      | 4.3  | s    |

| CLIP_OTW REPO                                      |                                                                                | 1                                                                                  |      |      |      |      |

| V <sub>OH_CLIPOTW</sub>                            | CLIP_OTW pin output voltage for logic level high (open-drain logic output)     |                                                                                    | 2.4  |      |      | V    |

| V <sub>OL_CLIPOTW</sub>                            | CLIP_OTW pin output voltage for logic level<br>low (open-drain logic output)   | - External 47-kΩ pullup resistor to 3 V–5.5 V                                      |      |      | 0.5  | V    |

**ELECTRICAL CHARACTERISTICS (continued)**

Test conditions (unless otherwise noted):  $T_{Case} = 25^{\circ}C$ , PVDD = 14.4 V,  $R_L = 4 \Omega$ ,  $f_S = 417 \text{ kHz}$ , Rext = 20 k $\Omega$ , master mode operation (see application diagram)

|                                     | PARAMETER                                                                  | TEST CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNIT               |

|-------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|--------------------|

| t <sub>DELAY_CLIPDET</sub>          | CLIP_OTW signal delay when output<br>clipping detected                     |                                                                                              |      |      | 20   | μs                 |

| FAULT REPORT                        | r                                                                          |                                                                                              |      |      |      |                    |

| V <sub>OH_FAULT</sub>               | FAULT pin output voltage for logic-level<br>high (open-drain logic output) | External 47-k $\Omega$ pullup resistor to 3 V–5.5 V                                          |      |      |      | V                  |

| V <sub>OL_FAULT</sub>               | FAULT pin output voltage for logic-level low<br>(open-drain logic output)  |                                                                                              |      |      | 0.5  | v                  |

| OPEN/SHORT D                        | DIAGNOSTICS                                                                |                                                                                              |      |      |      |                    |

| R <sub>S2P</sub> , R <sub>S2G</sub> | Maximum resistance to detect a short from OUT pin(s) to PVDD or ground     |                                                                                              |      |      | 200  | Ω                  |

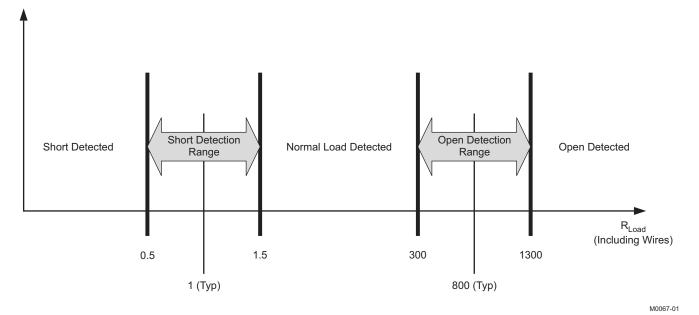

| R <sub>OPEN_LOAD</sub>              | Minimum load resistance to detect open circuit                             | Including speaker wires                                                                      | 300  | 800  | 1300 | Ω                  |

| R <sub>SHORTED_LOAD</sub>           | Maximum load resistance to detect short<br>circuit                         | Including speaker wires                                                                      | 0.5  | 1    | 1.5  | Ω                  |

| I <sup>2</sup> C ADDRESS D          | ECODER                                                                     |                                                                                              |      |      |      |                    |

| t <sub>LATCH_I2CADDR</sub>          | Time delay to latch I <sup>2</sup> C address after POR                     |                                                                                              |      | 300  |      | μs                 |

|                                     | Voltage on I2C_ADDR pin for address 0                                      | Connect to SGND                                                                              | 0%   | 0%   | 15%  |                    |

|                                     | Voltage on I2C_ADDR pin for address 1                                      | External resistors in series between D_BYP and SGND                                          | 25%  | 35%  | 45%  |                    |

| V <sub>I2C_ADDR</sub>               | Voltage on I2C_ADDR pin for address 2                                      | as a voltage divider                                                                         | 55%  | 65%  | 75%  | V <sub>D_BYP</sub> |

|                                     | Voltage on I2C_ADDR pin for address 3 Connect to D_BYP                     |                                                                                              | 85%  | 100% | 100% |                    |

| l <sup>2</sup> C                    |                                                                            |                                                                                              |      |      |      |                    |

| t <sub>HOLD_I2C</sub>               | Power-on hold time before I <sup>2</sup> C communication                   | STANDBY high                                                                                 |      | 1    |      | ms                 |

| f <sub>SCL</sub>                    | SCL clock frequency                                                        |                                                                                              |      |      | 100  | kHz                |

| V <sub>IH_SCL</sub>                 | SCL pin input voltage for logic-level high                                 |                                                                                              | 2.1  |      | 5.5  | V                  |

| V <sub>IL_SCL</sub>                 | SCL pin input voltage for logic-level low                                  | $R_{PU_{12C}} = 5 \cdot k\Omega$ pullup, supply voltage = 3.3 V or 5 V                       | -0.5 |      | 1.1  | V                  |

| V <sub>OH_SDA</sub>                 | SDA pin output voltage for logic-level high                                | $I^{2}C$ read, $R_{I2C} = 5 \cdot k\Omega$ pullup,<br>supply voltage = 3.3 V or 5 V          |      |      |      | V                  |

| V <sub>OL_SDA</sub>                 | SDA pin output voltage for logic-level low                                 | I <sup>2</sup> C read, 3-mA sink current                                                     | 0    |      | 0.4  | V                  |

| V <sub>IH_SDA</sub>                 | SDA pin input voltage for logic-level high                                 | $I^2C$ write, $R_{I2C} = 5 - k\Omega$ pullup,<br>supply voltage = 3.3 V or 5 V               | 2.1  |      | 5.5  | V                  |

| V <sub>IL_SDA</sub>                 | SDA pin input voltage for logic-level low                                  | $I^2C$ write, $R_{I2C} = 5-k\Omega$ pullup,<br>supply voltage = 3.3 V or 5 V                 | -0.5 |      | 1.1  | V                  |

| Ci                                  | Capacitance for SCL and SDA pins                                           |                                                                                              |      |      | 10   | pF                 |

| OSCILLATOR                          |                                                                            |                                                                                              |      |      |      |                    |

| V <sub>OH_OSCSYNC</sub>             | OSC_SYNC pin output voltage for<br>logic-level high                        |                                                                                              | 2.4  |      | 3.6  | V                  |

| V <sub>OL_OSCSYNC</sub>             | OSC_SYNC pin output voltage for<br>logic-level low                         | I2C_ADDR pin set to MASTER mode                                                              |      |      | 0.5  | V                  |

| VIH_OSCSYNC                         | OSC_SYNC pin input voltage for logic-level<br>high                         | 12C ADDR pip pot to SLAV/E mode                                                              | 2    |      | 3.6  | V                  |

| VIL_OSCSYNC                         | OSC_SYNC pin input voltage for logic-level low                             | I2C_ADDR pin set to SLAVE mode                                                               |      |      | 0.8  | V                  |

|                                     |                                                                            | I2C_ADDR pin set to MASTER mode, $f_S = 500 \text{ kHz}$ , maximum capacitive loading = 5 pF | 3.76 | 4.0  | 4.24 |                    |

| f <sub>OSC_SYNC</sub>               | OSC_SYNC pin clock frequency                                               | I2C_ADDR pin set to MASTER mode, $f_S$ = 417 kHz, maximum capacitive loading = 5 pF          | 3.13 | 3.33 | 3.63 | MHz                |

|                                     |                                                                            | I2C_ADDR pin set to MASTER mode, $f_S = 357$ kHz, maximum capacitive loading = 5 pF          | 2.68 | 2.85 | 3.0  |                    |

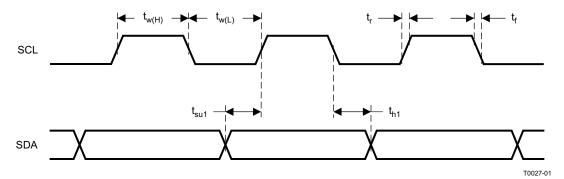

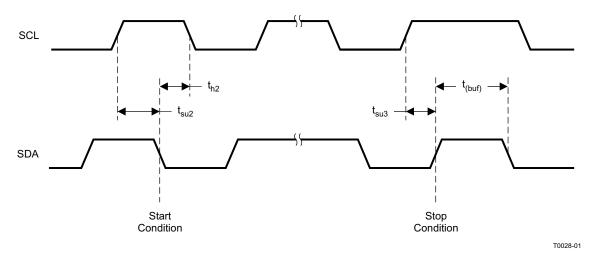

## TIMING REQUIREMENTS FOR I<sup>2</sup>C INTERFACE SIGNALS

over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                                            | MIN              | TYP | MAX  | UNIT |

|--------------------|----------------------------------------------------------------------|------------------|-----|------|------|

| t <sub>r</sub>     | Rise time for both SDA and SCL signals                               |                  |     | 1000 | ns   |

| t <sub>f</sub>     | Fall time for both SDA and SCL signals                               |                  |     | 300  | ns   |

| t <sub>w(H)</sub>  | SCL pulse duration, high                                             | 4                |     |      | μs   |

| t <sub>w(L)</sub>  | SCL pulse duration, low                                              | 4.7              |     |      | μs   |

| t <sub>su2</sub>   | Setup time for START condition                                       | 4.7              |     |      | μs   |

| t <sub>h2</sub>    | START condition hold time after which first clock pulse is generated | 4                |     |      | μs   |

| t <sub>su1</sub>   | Data setup time                                                      | 250              |     |      | ns   |

| t <sub>h1</sub>    | Data hold time                                                       | 0 <sup>(1)</sup> |     |      | ns   |

| t <sub>su3</sub>   | Setup time for STOP condition                                        | 4                |     |      | μs   |

| t <sub>(buf)</sub> | Time between a STOP and START condition                              | 4.7              |     |      | μs   |

| CB                 | Load capacitance for each bus line                                   |                  |     | 400  | pF   |

(1) A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

Figure 1. SCL and SDA Timing

## **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS (continued)**

## DESCRIPTION OF OPERATION

#### OVERVIEW

The TAS5414 and TAS5424 are single-chip, four-channel, analog-input audio amplifiers for use in the automotive environment. The design uses an ultra-efficient class-D technology developed by Texas Instruments, but with changes needed by the automotive industry. This technology allows for reduced power consumption, reduced heat, and reduced peak currents in the electrical system. The TAS5414 and TAS5424 realize an audio sound system design with smaller size and lower weight than traditional class-AB solutions.

The TAS5414 and TAS5424 are composed of eight elements:

- Preamplifier

- PWM

- Gate drive

- Power FETs

- Diagnostics

- Protection

- Power supply

- I<sup>2</sup>C serial communication bus

#### Preamplifier

The preamplifier of the TAS5414 and TAS5424 is a high-input-impedance, low-noise, low-offset-voltage input stage with adjustable gain. The high input impedance of the TAS5414 and TAS5424 allows the use of low-cost 1- $\mu$ F input capacitors while still achieving extended low-frequency response. The preamplifier is powered by a dedicated, internally regulated supply, which gives it excellent noise immunity and channel separation. Also included in the preamp are:

- 1. **Mute Pop-and-Click Control**—An audio input signal is reshaped and amplified as a step when a mute is applied at the crest or trough of the signal. Such a step is perceived as a loud click. This is avoided in the TAS5414 and TAS5424 by ramping the gain gradually when a mute or play command is received. Another form of click and pop can be caused by the start or stopping of switching in a class-D amplifier. The TAS5414 and TAS5424 incorporate a patented method to reduce the pop energy during the switching startup and shutdown sequence. Fault conditions require rapid protection response by the TAS5414 and the TAS5424, which do not have time to ramp the gain down in a pop-free manner. The device transitions into Hi-Z mode when an OV, UV, OC, OT, or DC fault is encountered. Also, activation of the STANDBY pin may not be pop-free.

- 2. **Gain Control**—The four gain settings are set in the preamplifier via I<sup>2</sup>C control registers. The gain is set outside of the global feedback resistors of the TAS5414 and the TAS5424, thus allowing for stability in the system under all load conditions and gain settings.

- DC Offset Reduction Circuitry—Circuitry has been incorporated to reduce the dc offset. DC offset in high-gain amplifiers can produce audible clicks and pops when the amplifier is started or stopped. The offset reduction circuitry can be disabled or enabled via l<sup>2</sup>C.

#### Pulse-Width Modulator (PWM)

The PWM converts the analog signal from the preamplifier into a switched signal of varying duty cycle. This is the critical stage that defines the class-D architecture. In the TAS5414 and TAS5424, the modulator is an advanced design with high bandwidth, low noise, low distortion, excellent stability, and full 0–100% modulation capability. The patented PWM uses clipping recovery circuitry to eliminate the deep saturation characteristic of PWMs when the input signal exceeds the modulator waveform.

#### Gate Drive

The gate driver accepts the low-voltage PWM signal and level shifts it to drive a high-current, full-bridge, power FET stage. The TAS5414 and TAS5424 use patent-pending techniques to avoid shoot-through and are optimized for EMI and audio performance.

#### **Power FETs**

The BTL output for each channel comprises four rugged N-channel 30-V FETs, each of which has an  $R_{DSon}$  of 75 m $\Omega$  for high efficiency and maximum power transfer to the load. These FETs are designed to handle large voltage transients during load dump.

#### Load Diagnostics

The TAS5414 and TAS5424 incorporate load diagnostic circuitry designed to help pinpoint the nature of output misconnections during installation. The TAS5414 and the TAS5424 include functions for detecting and determining the status of output connections. The following diagnostics are supported:

- Short to GND

- Short to PVDD

- Short across load (R < 1 Ω, typical)

- Open load (R > 800 Ω, typical)

- Tweeter detection

The presence of any of the short or open conditions is reported to the system via I<sup>2</sup>C register read. The tweeter detect status can be read from the CLIP\_OTW pin when properly configured.

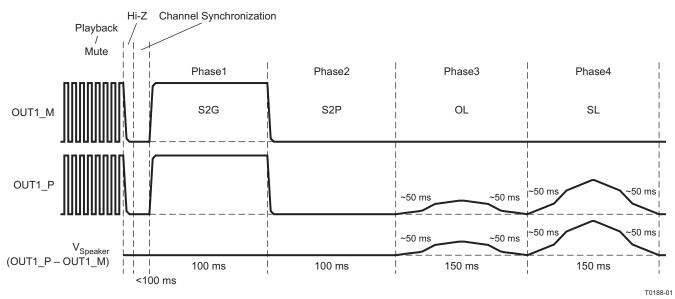

1. **Output Short and Open Diagnostics**—The TAS5414 and TAS5424 contain circuitry designed to detect shorts and open conditions on the outputs. The load diagnostic function can only be invoked when the output is in the Hi-Z mode. There are four phases of test during load diagnostics and two levels of test. In the full level, all channels must be in the Hi-Z state. All four phases are tested on each channel, all four channels at the same time. When fewer than four channels are in Hi-Z, the reduced level of test is the only available option. In the reduced level, only short to PVDD and short to GND can be tested. Load diagnostics can occur at power up before the amplifier is moved out of Hi-Z mode. If the amplifier is already in play mode, it must *Mute* and then *Hi-Z* before the load diagnostic can be performed. By performing the mute function, the normal pop- and click-free transitions occur before the diagnostics begin. The diagnostics are performed as shown in Figure 13. Figure 14 shows the impedance ranges for the open-load and shorted-load diagnostics. The results of the diagnostic are read from the diagnostic register for each channel via I<sup>2</sup>C. **Note:** Do not send a command via I<sup>2</sup>C to register 0x0C during the load diagnostic test.

Figure 13. Load Diagnostics Sequence of Events

Figure 14. Open and Shorted Load Detection

2. Tweeter Detection—The tweeter detection function is an ac diagnostic used to determine proper connection of the tweeter when a passive crossover is used. The proper implementation of this diagnostic function is dependent on the amplitude of a user-supplied test signal and on the impedance vs frequency curve of the acoustic package. The tweeter function is invoked via I<sup>2</sup>C, and all four channels should be tested individually. The tweeter detection uses the average cycle-by-cycle current limit circuit (see CBC section) to measure the current to the load. The current level for the tweeter detection threshold is typically 550 mA. The system (external to the TAS5414 and TAS5424) must generate a tone burst in the 10-kHz to 25-kHz range. If the tone burst employs a frequency higher than 20 kHz, and if a sufficiently smooth amplitude ramp is used, the tweeter detection results are monitored on the <u>CLIP\_OTW</u> pin during the application of the test tone. If the current threshold is attained during measurement, the tweeter is present; then the <u>CLIP\_OTW</u> pin is asserted. When the tweeter detector is activated, pulses on the <u>CLIP\_OTW</u> pin begin to toggle at 250 kHz to 500 kHz. As the detection signal gets stronger due to higher load current, the density (or duty cycle) of the pulses increases.

#### **Protection and Monitoring**

- Cycle-By-Cycle Current Limit (CBC)—The CBC current-limiting circuit terminates each PWM pulse to limit the output current flow when the average current limit (I<sub>LIM</sub>) threshold is exceeded. The overall effect on the audio in the case of a current overload is quite similar to a voltage-clipping event, where power is temporarily limited at the peaks of the musical signal and normal operation continues without disruption when the overload is removed. The TAS5414 and TAS5424 do not prematurely shut down in this condition. All four channels continue in play mode and pass signal.

- 2. Overcurrent Shutdown (OCSD)—Under severe short-circuit events, such as a short to PVDD or ground, a peak-current detector is used, and the affected channel shuts down in 200 µs to 390 µs if the conditions are severe enough. The shutdown speed depends on a number of factors, such as the impedance of the short circuit, supply voltage, and switching frequency. Only the shorted channels are shut down in such a scenario. The user may restart the affected channel via I<sup>2</sup>C. An OCSD event activates the fault pin, and the affected channel(s) are recorded in the I<sup>2</sup>C fault register. If the supply or ground short is strong enough to exceed the peak current threshold but not severe enough to trigger the OCSD, the peak current limiter prevents excess current from damaging the output FETs, and operation returns to normal after the short is removed.

- 3. DC Detect—This circuit detects a dc offset continously during normal operation at the output of the

amplifier. If the dc offset reaches the level defined in the  $I^2C$  registers for the specified time period, the circuit triggers. By default a dc detection event does not shut the output down. The shutdown function can be enabled or disabled via  $I^2C$ . If enabled, the triggered channel shuts down, but the others remain playing and the FAULT pin is asserted. The positive dc level and negative dc level are defined in  $I^2C$  registers and can have separate thresholds.

- 4. **Clip Detect**—The clip detect circuit alerts the user to the presence of a 100% duty-cycle PWM due to a clipped waveform. When this occurs, a signal is passed to the CLIP\_OTW pin and it is asserted until the 100% duty-cycle PWM signal is no longer present. All four channels are connected to the same CLIP\_OTW pin. Through I<sup>2</sup>C, the CLIP\_OTW signal can be changed to clip-only, OTW-only, or both. A fourth mode, used only during diagnostics, is the option to report tweeter detection events on this pin (see the *Tweeter Detection* section). The microcontroller in the system can monitor the signal at the CLIP\_OTW pin and may be configured to reduce the volume to all four channels in an active clipping-prevention circuit.

- 5. Overtemperature Warning (OTW) and Overtemperature Shutdown (OTSD)—By default, the CLIP\_OTW pin is set to indicate an OTW. This can be changed via I<sup>2</sup>C commands. If selected to indicate a temperature warning, the CLIP\_OTW pin is asserted when the die temperature reaches 125°C. The OTW has three temperature thresholds with a 10°C hysteresis. Each threshold is indicated in I<sup>2</sup>C register 0x04 bits 5, 6, and 7. The TAS5414 and TAS5424 still function until the temperature reaches the OTSD threshold. 155°C, at which time the outputs are placed into Hi-Z mode and the FAULT pin is asserted. I<sup>2</sup>C is still active in the event of an OTSD and the registers can be read for faults, but all audio ceases abruptly. The OTSD resets at 145°C, to allow the TAS5414/5424 to be turned back on through I<sup>2</sup>C. The OTW is still indicated until the temperature drops below 115°C. All temperatures are nominal values.

- 6. Undervoltage (UV) and Power-on-Reset (POR)—The undervoltage (UV) protection detects low voltages on PVDD, AVDD, and CP. In the event of an undervoltage, the FAULT pin is asserted and the I<sup>2</sup>C register is updated, depending on which voltage caused the event. Power-on-reset (POR) occurs when PVDD drops low enough. A POR event causes the I<sup>2</sup>C to go into a high-impedance state. After the device recovers from the POR event, the device must be re-initialized via I<sup>2</sup>C.

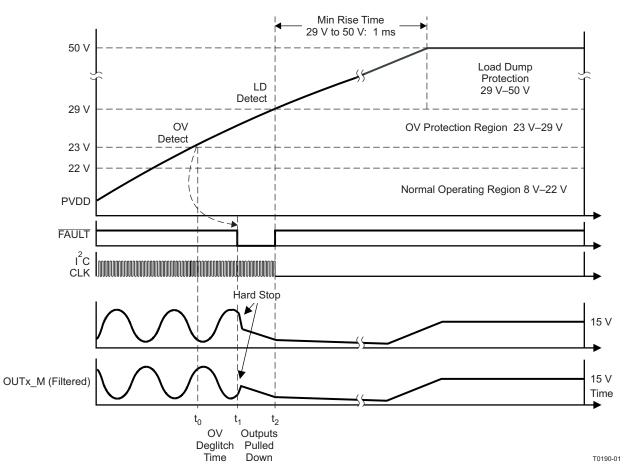

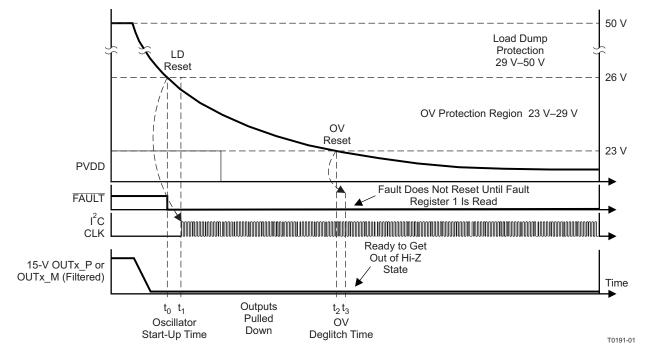

- 7. Overvoltage (OV) and Load Dump—The OV protection detects high voltages on PVDD. If PVDD reaches the overvoltage threshold, the FAULT pin is asserted and the I<sup>2</sup>C register is updated. If the voltage increases beyond the load dump threshold of 29 Vdc, the device shuts down and must be restarted once the voltage returns to a safe value. After the device recovers from the ≈ load dump event, the device must be re-initialized via I<sup>2</sup>C. The TAS5414 and TAS5424 can withstand 50-V load-dump voltage spikes (see Figure 15). Also depicted in this graph are the voltage thresholds for normal operation region, overvoltage operation region, and load-dump protection region. Figure 13 shows the regions of operating voltage and the profile of the load dump event. Battery charger voltages from 25 V to 35 V can be withstood for up to 1 hour.

Figure 15. Voltage Operating Regions With Load Dump Transition Defined

#### Power Supply

The power for the device is most commonly provided by a car battery that can have a large voltage swing, 8 Vdc to 18 Vdc. PVDD is a filtered battery voltage, and it is the supply for the output FETS and the low-side FET gate driver. The high-side FET gate driver is supplied by a charge pump (CP) supply. The charge pump supplies the gate drive voltage for all four channels. The analog circuitry is powered by AVDD, which is a provided by an internal linear regulator. A  $0.1\mu$ F/10V external bypass capacitor is needed at the A\_BYP pin for this supply. It is recommended that no external components except the bypass capacitor be attached to this pin. The digital circuitry is powered by DVDD, which is provided by an internal linear regulator. A  $0.1\mu$ F/10V external bypass capacitor be attached to this pin. The digital circuitry is powered by DVDD, which is provided by an internal linear regulator. A  $0.1\mu$ F/10V external bypass capacitor be attached to this pin. The digital circuitry is powered by DVDD, which is provided by an internal linear regulator. A  $0.1\mu$ F/10V external bypass capacitor be attached to this pin. The digital circuitry is needed at the D\_BYP pin. It is recommended that no external components except the bypass capacitor be attached to this pin.

The TAS5414 and TAS5424 can withstand fortuitous open ground and power conditions. Fortuitous open ground usually occurs when a speaker wire is shorted to ground, allowing for a second ground path through the body diode in the output FETs. The uniqueness of the diagnostic capabilities allows the speakers and speaker wires to be debugged, eliminating the need to remove the amplifier to diagnose the problem.

## I<sup>2</sup>C Serial Communication Bus

The TAS5414 and TAS5424 communicate with the system processor via the  $I^2C$  serial communication bus. The TAS5414 and TAS5424 are  $I^2C$  slave-only devices. The processor can poll the TAS5414 and the TAS5424 via  $I^2C$  to determine the operating status of the device. All fault conditions and detections are reported via  $I^2C$ . There are also numerous features and operating conditions that can be set via  $I^2C$ .

The I<sup>2</sup>C bus allows control of the following configurations:

• Independent gain control of each channel. The gain can be set to 12 dB, 20 dB, 26 dB, and 32 dB.

TAS5414 TAS5424 SLOS514A-FEBRUARY 2007-REVISED JULY 2007

## DESCRIPTION OF OPERATION (continued)

- Select current limit (for 2-Ω and for 4-Ω loads). This allows optimal design of the filter inductor, and the use of smaller gauge speaker wires for 4-Ω applications.

- Select AM non-interference switching frequency

- Select the function of OTW\_CLIP pin

- Enable or disable dc detect function with selectable threshold

- Place channel in Hi-Z (switching stopped) mode (mute)

- Select tweeter detect, set detect threshold and initiate function

- Initiate open/short load diagnostic

- Reset faults and return to normal switching operation from Hi-Z mode (unmute)

In addition to the standard SDA and SCL pins for the I<sup>2</sup>C bus, the TAS5414 and the TAS5424 include a single pin that allows up to four devices to work together in a system with no additional hardware required for communication or synchronization. The I2C\_ADDR pin sets the device in master or slave mode and selects the I<sup>2</sup>C address for that device. Tie I2C\_ADDR to DGND for master, to 1.2 Vdc for slave 1, to 2.4 Vdc for slave 2, and to D\_BYP for slave 3. The OSC\_SYNC pin is used to synchronize the internal clock oscillators and thereby avoid beat frequencies. An external oscillator can also be applied to this pin for external control of the switching frequency.

| DESCRIPTION                 | I2C_ADDR PIN CONNECTION                                                               | I <sup>2</sup> C ADDRESS |

|-----------------------------|---------------------------------------------------------------------------------------|--------------------------|

| TAS5414/5424 0 (OSC MASTER) | To SGND pin                                                                           | 0xD8/D9                  |

| TAS5414/5424 1 (OSC SLAVE1) | 35% DVDD (resistive voltage divider between D_BYP pin and SGND pin) <sup>(1)</sup>    | 0xDA/DB                  |

| TAS5414/5424 2 (OSC SLAVE2) | $65\%$ DVDD (resistive voltage divider between D_BYP pin and SGND pin) <sup>(1)</sup> | 0xDC/DD                  |

| TAS5414/5424 3 (OSC SLAVE3) | To D_BYP pin                                                                          | 0xDE/DF                  |

Table 2. Table 7. I2C\_ADDR Pin Connection

(1)  $R_{12C ADDR}$  with 5% or better tolerance is recommended.

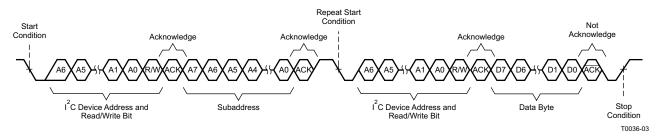

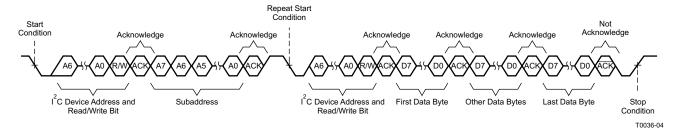

## I<sup>2</sup>C Bus Protocol

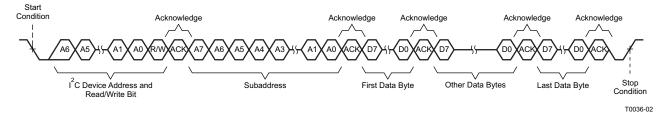

The TAS5414 and TAS5424 have a bidirectional serial control interface that is compatible with the Inter IC ( $I^2C$ ) bus protocol and supports 100-kbps data transfer rates for random and sequential write and read operations. This is a slave-only device that does not support a multimaster bus environment or wait state insertion. The control interface is used to program the registers of the device and to read device status.

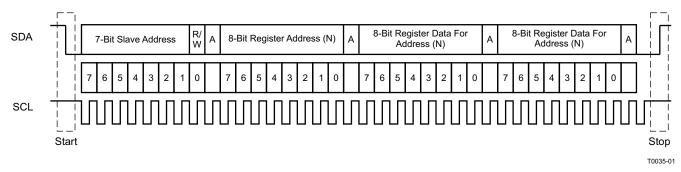

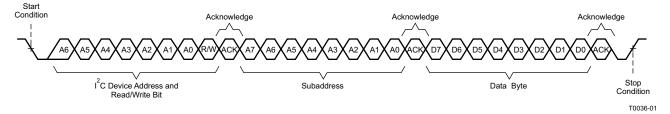

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially, one bit at a time. The address and data are transferred in byte (8-bit) format with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is HIGH to indicate a start and stop conditions. A HIGH-to-LOW transition on SDA indicates a start, and a LOW-to-HIGH transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 16. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then wait for an acknowledge condition. The TAS5414 and TAS5424 hold SDA LOW during the acknowledge-clock period to indicate an acknowledgement. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pullup resistor must be used for the SDA and SCL signals to set the HIGH level for the bus. There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus.

#### TEXAS INSTRUMENTS www.ti.com

#### Figure 16. Typical I<sup>2</sup>C Sequence

Use the I2C\_ADDR pin (pin 2) to program the device for one of four addresses. These four addresses are licensed I<sup>2</sup>C addresses and do not conflict with other licensed I<sup>2</sup>C audio devices. To communicate with the TAS5414 and the TAS5424, the I<sup>2</sup>C master uses addresses shown in Figure 16. Read and write data can be transmitted using single-byte or multiple-byte data transfers.

### Random Write