www.ti.com

# DIRECT RAMBUS™ CLOCK GENERATOR

#### **FEATURES**

- 533-MHz Differential Clock Source for Direct Rambus™ Memory Systems for an 1066-MHz Data Transfer Rate

- Fail-Safe Power Up Initialization

- Synchronizes the Clock Domains of the Rambus Channel With an External System or Processor Clock

- Three Power Operating Modes to Minimize Power for Mobile and Other Power-Sensitive Applications

- Operates From a Single 3.3-V Supply and 120 mW at 300 MHz (Typ)

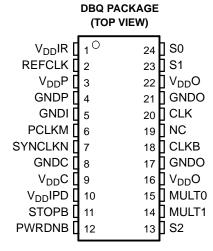

- Packaged in a Shrink Small-Outline Package (DBQ)

- Supports Frequency Multipliers: 4, 6, 8, 16/3

- No External Components Required for PLL

- Supports Independent Channel Clocking

- Spread Spectrum Clocking Tracking Capability to Reduce EMI

- Designed for Use With TI's 133-MHz Clock Synthesizers CDC924 and CDC921

- Cycle-Cycle Jitter Is Less Than 40 ps at 533 MHz

- Certified by Gigatest Labs to Exceed the Rambus DRCG Validation Requirement

- Supports Industrial Temperature Range of –40°C to 85°C

NC - No internal connection

#### **DESCRIPTION**

The Direct Rambus clock generator (DRCG) provides the necessary clock signals to support a Direct Rambus memory subsystem. It includes signals to synchronize the Direct Rambus channel clock to an external system or processor clock. It is designed to support Direct Rambus memory on a desktop, workstation, server, and mobile PC motherboards. DRCG also provides an off-the-shelf solution for a broad range of Direct Rambus memory applications.

The DRCG provides clock multiplication and phase alignment for a Direct Rambus memory subsystem to enable synchronous communication between the Rambus channel and ASIC clock domains. In a Direct Rambus memory subsystem, a system clock source provides the REFCLK and PCLK clock references to the DRCG and memory controller, respectively. The DRCG multiplies REFCLK and drives a high-speed BUSCLK to RDRAMs and the memory controller. Gear ratio logic in the memory controller divides the PCLK and BUSCLK frequencies by ratios M and N such that PCLKM = SYNCLKN, where SYNCLK = BUSCLK/4. The DRCG detects the phase difference between PCLKM and SYNCLKN and adjusts the phase of BUSCLK such that the skew between PCLKM and SYNCLKN is minimized. This allows data to be transferred across the SYNCLK/PCLK boundary without incurring additional latency.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DIRECT RAMBUS, Rambus are trademarks of Rambus Inc.

User control is provided by multiply and mode selection terminals. The multiply terminals provide selection of one of four clock frequency multiply ratios, generating BUSCLK frequencies ranging from 267 MHz to 533 MHz with clock references ranging from 33 MHz to 100 MHz. The mode select terminals can be used to select a bypass mode where the frequency multiplied reference clock is directly output to the Rambus channel for systems where synchronization between the Rambus clock and a system clock is not required. Test modes are provided to bypass the PLL and output REFCLK on the Rambus channel and to place the outputs in a high-impedance state for board testing.

The CDCFR83A has a fail-safe power up initialization state-machine which supports proper operation under all power up conditions.

The CDCFR83A is characterized for operation over free-air temperatures of -40°C to 85°C.

# **FUNCTIONAL BLOCK DIAGRAM PWRDWNB** S0 S2 **STOPB Test MUX Bypass MUX ByPCLK PLLCLK** CLK PLL Phase **CLKB REFCLK** В Aligner **PACLK** $\varphi_{\boldsymbol{D}}$ 2 PCLKM | SYNCLKN **MULTO**

#### FUNCTION TABLE(1)

| MODE             | S0 | <b>S</b> 1 | S2 | CLK                 | CLKB                  |

|------------------|----|------------|----|---------------------|-----------------------|

| Normal           | 0  | 0          | 0  | Phase aligned clock | Phase aligned clock B |

| Bypass           | 1  | 0          | 0  | PLLCLK              | PLLCLKB               |

| Test             | 1  | 1          | 0  | REFCLK              | REFCLKB               |

| Output test (OE) | 0  | 1          | Х  | Hi-Z                | Hi-Z                  |

| Reserved         | 0  | 0          | 1  | _                   | _                     |

| Reserved         | 1  | 0          | 1  | _                   | _                     |

| Reserved         | 1  | 1          | 1  | Hi-Z                | Hi-Z                  |

(1) X = don't care, Hi-Z = high impedance

MULT1

## **TERMINAL FUNCTIONS**

| TERMINAL            |        |     | DESCRIPTION                                           |  |  |  |

|---------------------|--------|-----|-------------------------------------------------------|--|--|--|

| NAME                | NO.    | I/O | DESCRIPTION                                           |  |  |  |

| CLK                 | 20     | 0   | Output clock                                          |  |  |  |

| CLKB                | 18     | 0   | Output clock (complement)                             |  |  |  |

| GNDC                | 8      |     | GND for phase aligner                                 |  |  |  |

| GNDI                | 5      |     | GND for control inputs                                |  |  |  |

| GNDO                | 17, 21 |     | GND for clock outputs                                 |  |  |  |

| GNDP                | 4      |     | GND for PLL                                           |  |  |  |

| MULT0               | 15     | ı   | PLL multiplier select                                 |  |  |  |

| MULT1               | 14     | I   | PLL multiplier select                                 |  |  |  |

| NC                  | 19     |     | Not used                                              |  |  |  |

| PCLKM               | 6      | I   | Phase detector input                                  |  |  |  |

| PWRDNB              | 12     | ı   | Active low power down                                 |  |  |  |

| REFCLK              | 2      | ı   | Reference clock                                       |  |  |  |

| S0                  | 24     | I   | Mode control                                          |  |  |  |

| S1                  | 23     | ı   | Mode control                                          |  |  |  |

| S2                  | 13     | I   | Mode control                                          |  |  |  |

| STOPB               | 11     | ı   | Active low output disable                             |  |  |  |

| SYNCLKN             | 7      | ı   | Phase detector input                                  |  |  |  |

| V <sub>DD</sub> C   | 9      |     | V <sub>DD</sub> for phase aligner                     |  |  |  |

| V <sub>DD</sub> IPD | 10     |     | Reference voltage for phase detector inputs and STOPB |  |  |  |

| $V_{DD}IR$          | 1      |     | Reference voltage for REFCLK                          |  |  |  |

| V <sub>DD</sub> O   | 16, 22 |     | V <sub>DD</sub> for clock outputs                     |  |  |  |

| $V_{DD}P$           | 3      |     | V <sub>DD</sub> for PLL                               |  |  |  |

### PLL DIVIDER SELECTION

Table 1 lists the supported REFCLK and BUSCLK frequencies. Other REFCLK frequencies are permitted, provided that (267 MHz < BUSCLK < 533 MHz) and (33 MHz < REFCLK < 100 MHz).

Table 1. REFCLK and BUSCLK Frequencies

| MULT0 | MULT1 | REFCLK<br>(MHz) | MULTIPLY<br>RATIO | BUSCLK <sup>(1)</sup><br>(MHz) |

|-------|-------|-----------------|-------------------|--------------------------------|

| 0     | 0     | 67              | 4                 | 267                            |

| 0     | 1     | 50              | 6                 | 300                            |

| 0     | 1     | 67              | 6                 | 400                            |

| 1     | 1     | 33              | 8                 | 267                            |

| 1     | 1     | 50              | 8                 | 400                            |

| 1     | 1     | 67              | 8                 | 533                            |

| 1     | 0     | 67              | 16/3              | 356                            |

<sup>(1)</sup> BUSCLK will be undefined until a valid reference clock is available at REFCLK. After applying REFCLK, the PLL requires stabilization time to achieve phase lock.

**Table 2. Clock Output Driver States**

| STATE     | PWRDNB | STOPB | CLK                                | CLKB                   |

|-----------|--------|-------|------------------------------------|------------------------|

| Powerdown | 0      | X     | GND                                | GND                    |

| CLK stop  | 1      | 0     | V <sub>X, STOP</sub>               | V <sub>X, STOP</sub>   |

| Normal    | 1      | 1     | PACLK/PLLCLK/REFCLK <sup>(1)</sup> | PACLKB/PLLCLKB/REFCLKB |

<sup>(1)</sup> Depending on the state of S0, S1, and S2

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                              | UNIT                                       |

|------------------|--------------------------------------------------------------|--------------------------------------------|

| $V_{DD}$         | Supply voltage range <sup>(2)</sup>                          | –0.5 V to 4 V                              |

| $V_{O}$          | Output voltage range at any output terminal                  | $-0.5 \text{ V to V}_{DD} + 0.5 \text{ V}$ |

| $V_{I}$          | Input voltage rangeat any input terminal                     | –0.5 V to V <sub>DD</sub> + 0.5 V          |

|                  | Continuous total power dissipation                           | See Dissipation Rating Table               |

| $T_A$            | Operating free-air temperature range                         | -40°C to 85°C                              |

| T <sub>stg</sub> | Storage temperature range                                    | –65°C to 150°C                             |

|                  | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                                      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **DISSIPATION RATINGS**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR                 | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |  |

|---------|-----------------------|---------------------------------|-----------------------|-----------------------|--|

|         | POWER RATING          | ABOVE $T_A = 25^{\circ}C^{(1)}$ | POWER RATING          | POWER RATING          |  |

| DBQ     | 1400 mW               | 11 mW/°C                        | 905 mW                | 740 mW                |  |

<sup>(1)</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

<sup>(2)</sup> All voltage values are with respect to the GND terminals.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                 |                                                                                 | MIN                     | NOM | MAX                    | UNIT |

|-----------------|---------------------------------------------------------------------------------|-------------------------|-----|------------------------|------|

| $V_{DD}$        | Supply voltage                                                                  | 3.135                   | 3.3 | 3.465                  | V    |

| $V_{IH}$        | High-level input voltage (CMOS)                                                 | $0.7 \times V_{DD}$     |     |                        | V    |

| $V_{IL}$        | Low-level input voltage (CMOS)                                                  |                         |     | $0.3 \times V_{DD}$    | V    |

|                 | Initial phase error at phase detector inputs (required range for phase aligner) | $-0.5 \times t_{c(PD)}$ |     | $0.5 \times t_{c(PD)}$ | V    |

| $V_{IL}$        | REFCLK low-level input voltage                                                  |                         |     | $0.3 \times V_{DD}IR$  | V    |

| $V_{IH}$        | REFCLK high-level input voltage                                                 | $0.7 \times V_{DD}IR$   |     |                        | V    |

| $V_{IL}$        | Input signal low voltage (STOPB)                                                |                         |     | $0.3 \times V_{DD}IPD$ | V    |

| $V_{IH}$        | Input signal high voltage (STOPB)                                               | $0.7 \times V_{DD}IPD$  |     |                        | V    |

|                 | Input reference voltage for (REFCLK) (V <sub>DD</sub> IR)                       | 1.235                   |     | 3.465                  | V    |

|                 | Input reference voltage for (PCLKM and SYSCLKN) (V <sub>DD</sub> IPD)           | 1.235                   |     | 3.465                  | V    |

| I <sub>OH</sub> | High-level output current                                                       |                         |     | -16                    | mA   |

| I <sub>OL</sub> | Low-level output current                                                        |                         |     | 16                     | mA   |

| $T_A$           | Operating free-air temperature                                                  | -40                     |     | 85                     | °C   |

# **TIMING REQUIREMENTS**

|                    |                                                     | MIN | MAX  | UNIT |

|--------------------|-----------------------------------------------------|-----|------|------|

| t <sub>c(in)</sub> | Input cycle time                                    | 10  | 40   | ns   |

|                    | Input cycle-to-cycle jitter                         |     | 250  | ps   |

|                    | Input duty cycle over 10,000 cycles                 | 40% | 60%  |      |

| f <sub>mod</sub>   | Input frequency modulation                          | 30  | 33   | kHz  |

|                    | Modulation index, nonlinear maximum 0.5%            |     | 0.6% |      |

|                    | Phase detector input cycle time (PCLKM and SYNCLKN) | 30  | 100  | ns   |

| SR                 | Input slew rate                                     | 1   | 4    | V/ns |

|                    | Input duty cycle (PCLKM and SYNCLKN)                | 25% | 75%  |      |

## **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

|                          | PARAMETE                                                | R                                   | TEST CON                                           | DITIONS <sup>(1)</sup>    | MIN                   | TYP <sup>(2)</sup> | MAX  | UNIT |

|--------------------------|---------------------------------------------------------|-------------------------------------|----------------------------------------------------|---------------------------|-----------------------|--------------------|------|------|

| V <sub>O(STOP)</sub>     | Output voltage during                                   | CLK Stop (STOPB = 0)                | See Figure 1                                       |                           | 1.1                   |                    | 2    |      |

| V <sub>O(X)</sub>        | Output crossing-point                                   | voltage                             | See Figure 1 and F                                 | See Figure 1 and Figure 6 |                       |                    | 1.8  | V    |

| Vo                       | Output voltage swing                                    |                                     | See Figure 1                                       |                           | 0.4                   |                    | 0.6  | V    |

| $V_{IK}$                 | Input clamp voltage                                     |                                     | $V_{DD} = 3.135 \text{ V},$                        | $I_1 = -18 \text{ mA}$    |                       |                    | -1.2 | V    |

|                          |                                                         |                                     | See Figure 1                                       |                           |                       |                    | 2    |      |

| V <sub>OH</sub>          | High-level output volta                                 | age                                 | $V_{DD} = min to max,$                             | $I_{OH} = -1 \text{ mA}$  | V <sub>DD</sub> - 0.1 |                    |      | V    |

|                          |                                                         |                                     | $V_{DD} = 3.135 \text{ V},$                        | $I_{OH} = -16 \text{ mA}$ | 2.4                   |                    |      |      |

|                          |                                                         |                                     | See Figure 1                                       |                           | 1                     |                    |      |      |

| V <sub>OL</sub>          | Low-level output volta                                  | age                                 | $V_{DD} = min to max,$                             | I <sub>OH</sub> = 1 mA    |                       |                    | 0.1  | V    |

|                          |                                                         |                                     | $V_{DD} = 3.135 \text{ V},$                        | I <sub>OH</sub> = 16 mA   |                       |                    | 0.5  |      |

|                          |                                                         |                                     | $V_{DD} = 3.135 \text{ V},$                        | V <sub>O</sub> = 1 V      | -32                   | -52                |      |      |

| I <sub>OH</sub>          | High-level output curr                                  | ent                                 | $V_{DD} = 3.3 \text{ V},$                          | V <sub>O</sub> = 1.65 V   |                       | <b>–</b> 51        |      | mA   |

|                          |                                                         |                                     | $V_{DD} = 3.465 \text{ V},$                        | V <sub>O</sub> = 3.135 V  |                       | -14.5              | -21  |      |

|                          |                                                         |                                     | $V_{DD} = 3.135 \text{ V},$                        | V <sub>O</sub> = 1.95 V   | 43                    | 61.5               |      |      |

| $I_{OL}$                 | Low-level output curre                                  | ent                                 | $V_{DD} = 3.3 V,$                                  | V <sub>O</sub> = 1.65 V   |                       | 65                 |      | mA   |

|                          |                                                         |                                     | $V_{DD} = 3.465 V,$                                | V <sub>O</sub> = 0.4 V    |                       | 25.5               | 36   |      |

| I <sub>OZ</sub>          | High-impedance-state output current                     |                                     | S0 = 0, S1 = 1                                     |                           |                       |                    | ±10  | μΑ   |

| I <sub>OZ(STOP)</sub>    | High-impedance-state during CLK stop                    | e output current                    | Stop = 0, $V_O = GNI$                              | O or V <sub>DD</sub>      |                       |                    | ±100 | μΑ   |

| I <sub>OZ(PD)</sub>      | High-impedance-state output current in power-down state |                                     | PWRDNB = 0, $V_0$ = GND or $V_{DD}$                |                           | -10                   |                    | 100  | μΑ   |

|                          | High-level input                                        | REFCLK, PCLKM,<br>SYNCLKN, STOPB    | V 0.405.V                                          |                           |                       |                    | 10   |      |

| I <sub>IH</sub>          | current                                                 | PWRDNB, S0, S1,<br>S2, MULT0, MULT1 | $V_{DD} = 3.465 \text{ V},$                        | $V_I = V_{DD}$            |                       |                    | 10   | μΑ   |

|                          | Low-level input                                         | REFCLK, PCLKM,<br>SYNCLKN, STOPB    | V 0.405.V                                          |                           |                       |                    | -10  | ^    |

| I <sub>IL</sub>          | current                                                 | PWRDNB, S0, S1,<br>S2, MULT0, MULT1 | $V_{DD} = 3.465 \text{ V},$                        | V <sub>I</sub> = 0        |                       |                    | -10  | μΑ   |

| 7                        | Output insurantenas                                     | High state                          | R <sub>I</sub> at I <sub>O</sub> - 14.5 mA to      | o –16.5 mA                | 15                    | 35                 | 50   | 0    |

| Z <sub>O</sub>           | Output impedance                                        | Low state                           | R <sub>I</sub> at I <sub>O</sub> 14.5 mA to        | 16.5 mA                   | 11                    | 17                 | 35   | Ω    |

|                          | Defense                                                 | V 10 V 100                          | V 0.405.V                                          | PWRDNB = 0                |                       |                    | 50   | μΑ   |

|                          | Reference current                                       | $V_{DD}IR$ , $V_{DD}IPD$            | $V_{DD} = 3.465 \text{ V}$                         | PWRDNB = 1                |                       |                    | 0.5  | mA   |

| C <sub>I</sub>           | Input capacitance                                       |                                     | $V_I = V_{DD}$ or GND                              |                           |                       | 2                  |      | pF   |

| Co                       | Output capacitance                                      |                                     | $V_O = V_{DD}$ or GND                              |                           |                       | 3                  |      | pF   |

| I <sub>DD(PD)</sub>      | Supply current in pwo                                   | per-down state                      | REFCLK = 0 MHz to 100 MHz,<br>PWDNB = 0, STOPB = 1 |                           |                       |                    | 100  | μΑ   |

| I <sub>DD(CLKSTOP)</sub> | Supply current in CLF                                   | Stop state                          | BUSCLK configure                                   | d for 533 MHz             |                       |                    | 45   | mA   |

| I <sub>DD(NORMAL)</sub>  | Supply current in norr                                  | mal state                           | BUSCLK = 533 MH                                    | lz                        |                       |                    | 100  | mA   |

$V_{DD}$  refers to any of the following;  $V_{DD},\,V_{DD}IPD,\,V_{DD}IR,\,V_{DD}O,\,V_{DD}C,$  and  $V_{DD}P$  All typical values are at  $V_{DD}$  = 3.3 V,  $T_A$  = 25°C.

## **SWITCHING CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                       |                                                                                                     |                            |                        | TEST CONDITIONS                    | MIN  | TYP <sup>(1)</sup> MAX | UNIT |

|---------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------|------------------------|------------------------------------|------|------------------------|------|

| t <sub>c(out)</sub>             | Clock output cycle time                                                                             |                            | 1.87                   | 3.75                               | ns   |                        |      |

|                                 |                                                                                                     |                            | 267 MHz                |                                    |      | 80                     |      |

|                                 |                                                                                                     | Infinite and               | 300 MHz                | Coo Figure 2                       |      | 70                     |      |

| t <sub>(jitter)</sub>           | Total cycle jitter over 1, 2, 3, 4, 5, or 6 clock cycles                                            | stopped phase              | 356 MHz                | See Figure 3                       |      | 60                     | ps   |

|                                 | o, 4, o, or o didok dydios                                                                          | alignment                  | 400 MHz                |                                    |      | 50                     |      |

|                                 |                                                                                                     |                            | 533 MHz <sup>(2)</sup> |                                    |      | 40                     |      |

| t <sub>(phase)</sub>            | Phase detector phase error for distributed loop                                                     |                            |                        | Static phase error <sup>(3)</sup>  | -100 | 100                    | ps   |

| t <sub>(phase, SSC)</sub>       | C) PLL output phase error when tracking SSC                                                         |                            |                        | Dynamic phase error <sup>(3)</sup> | -100 | 100                    | ps   |

| I <sub>(DC)</sub>               | Output duty cycle over 10,0                                                                         | 000 cycles                 |                        | See Figure 4                       | 45%  | 55%                    |      |

|                                 |                                                                                                     | Infinite and stopped phase | 267 MHz                |                                    |      | 80                     |      |

|                                 |                                                                                                     |                            | 300 MHz                | See Figure 5                       |      | 70                     |      |

| t <sub>(DC, err)</sub>          | Output cycle-to-cycle duty cycle error                                                              |                            | 356 MHz                |                                    |      | 60                     | ps   |

|                                 | cycle circi                                                                                         | alignment                  | 400 MHz                |                                    |      | 50                     |      |

|                                 |                                                                                                     |                            | 533 MHz                |                                    |      | 50                     |      |

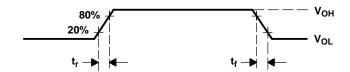

| t <sub>r</sub> , t <sub>f</sub> | Output rise and fall times (measured at 20%–80% of output voltage)                                  |                            |                        | See Figure 7                       | 160  | 400                    | ps   |

| Δt                              | Difference between rise and fall times on a single device (20%–80%)  t <sub>r</sub> -t <sub>r</sub> |                            |                        | See Figure 7                       |      | 100                    | ps   |

## STATE TRANSITION LATENCY SPECIFICATIONS

|                           | PARAMETER                                                                                                                     |                 | то        | TEST<br>CONDITIONS | MIN TYP(1) | MAX | UNIT         |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|--------------------|------------|-----|--------------|

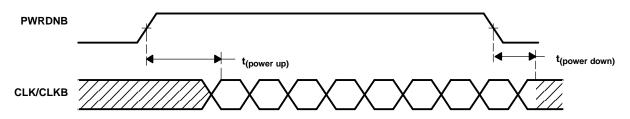

| t <sub>(powerup)</sub>    | Delay time, PWRDNB↑ to CLK/CLKB output settled (excluding t <sub>(DISTLOCK)</sub> )                                           | Powerdown       | Normal    | See Figure 8       |            | 3   | <b>770.0</b> |

|                           | Delay time, PWRDNB↑ to internal PLL and clock are on and settled                                                              | Powerdown       | inomai    |                    |            | 3   | ms           |

| t <sub>(VDDpowerup)</sub> | Delay time, power up to CLK/CLKB output settled                                                                               | V               | Normal    | See Figure 8       |            | 3   | ms           |

|                           | Delay time, power up to internal PLL and clock are on and settled                                                             | V <sub>DD</sub> | Nomiai    |                    |            | 3   | 1115         |

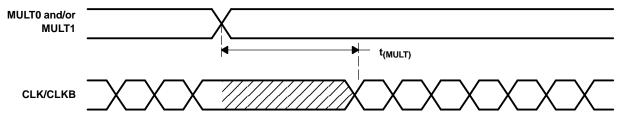

| t <sub>(MULT)</sub>       | MULT0 and MULT1 change to CLK/CLKB output resettled (excluding t <sub>(DISTLOCK)</sub> )                                      | Normal          | Normal    | See Figure 9       |            | 1   | ms           |

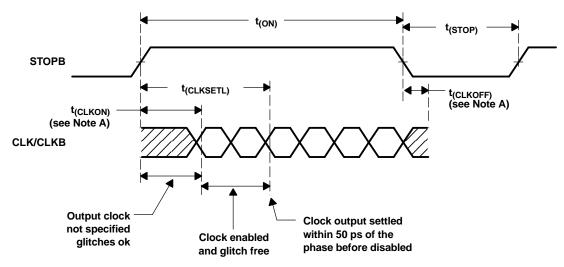

| t <sub>(CLKON)</sub>      | STOPB <sup>↑</sup> to CLK/CLKB glitch-free clock edges                                                                        | CLK Stop        | Normal    | See Figure 10      |            | 10  | ns           |

| t(CLKSETL)                | STOPB <sup>↑</sup> to CLK/CLKB output settled to within 50 ps of the phase before STOPB was disabled                          | CLK Stop        | Normal    | See Figure 10      |            | 20  | cycles       |

| t <sub>(CLKOFF)</sub>     | STOPB↓ to CLK/CLKB output disabled                                                                                            | Normal          | CLK Stop  | See Figure 10      |            | 5   | ns           |

| t <sub>(powerdown)</sub>  | Delay time, PWRDNB↓ to the device in the power-down mode                                                                      | Normal          | Powerdown | See Figure 8       |            | 1   | ms           |

| t <sub>(STOP)</sub>       | Maximum time in CLKSTOP (STOPB = 0) before reentering normal mode (STOPB = 1)                                                 | STOPB           | Normal    | See Figure 10      |            | 100 | μs           |

| t <sub>(ON)</sub>         | Minimum time in normal mode (STOPB = 1) before reentering CLKSTOP (STOPB = 0)                                                 | Normal          | CLK Stop  | See Figure 10      | 100        |     | ms           |

| t(DISTLOCK)               | Time from when CLK/CLKB output is settled to when the phase error between SYNCLKN and PCLKM falls within t <sub>(phase)</sub> | Unlocked        | Locked    |                    |            | 5   | ms           |

<sup>(1)</sup> All typical values are at  $V_{DD}$  = 3.3 V,  $T_A$  = 25°C.

All typical values are at  $V_{DD}=3.3~\rm{V}$  ,  $T_{A}=25^{\circ}C$  . Jitter measurement according to Rambus validation specification Assured by design

### PARAMETER MEASUREMENT INFORMATION

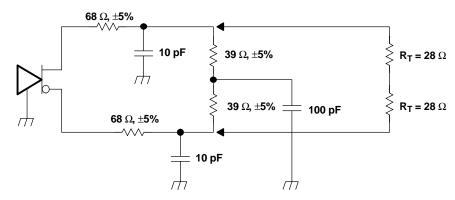

Figure 1. Test Load and Voltage Definitions ( $V_{O(STOP)}$ ,  $V_{O(X)}$ ,  $V_{O}$ ,  $V_{OH}$ ,  $V_{OL}$ )

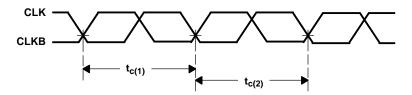

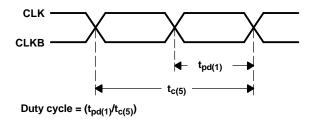

Cycle-to-cycle jitter =  $|t_{c(1)} - t_{c(2)}|$  over 10000 consecutive cycles

Figure 2. Cycle-to-Cycle Jitter

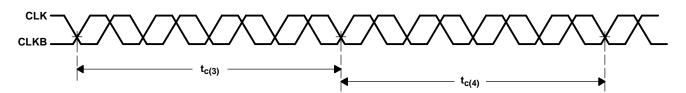

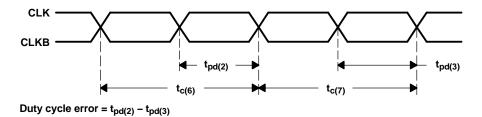

Cycle-to-cycle jitter =  $|t_{c(3)} - t_{c(4)}|$  over 10000 consecutive cycles

Figure 3. Short Term Cycle-to-Cycle Jitter Over Four Cycles

Figure 4. Output Duty Cycle

# PARAMETER MEASUREMENT INFORMATION (continued)

Figure 5. Duty Cycle Error (Cycle-to-Cycle)

Figure 6. Crossing-Point Voltage

Figure 7. Voltage Waveforms

Figure 8. PWRDNB Transition Timings

**Figure 9. MULT Transition Timings**

# PARAMETER MEASUREMENT INFORMATION (continued)

A.  $V_{ref} = V_O \pm 200 \text{ mV}$

**Figure 10. STOPB Transition Timings**

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

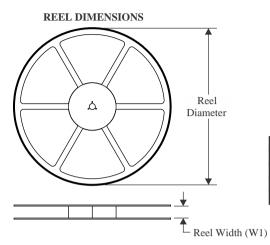

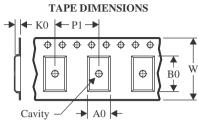

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

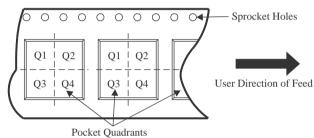

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CDCFR83ADBQR | SSOP            | DBQ                | 24 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

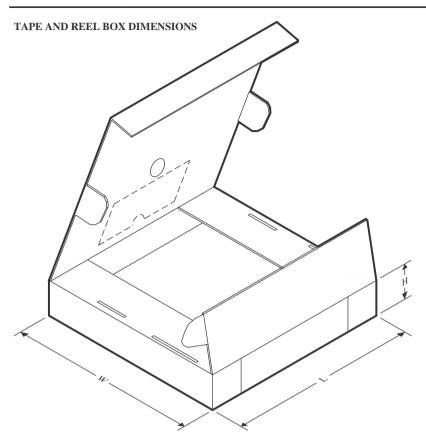

## \*All dimensions are nominal

|   | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ı | CDCFR83ADBQR | SSOP         | DBQ             | 24   | 2500 | 356.0       | 356.0      | 35.0        |  |

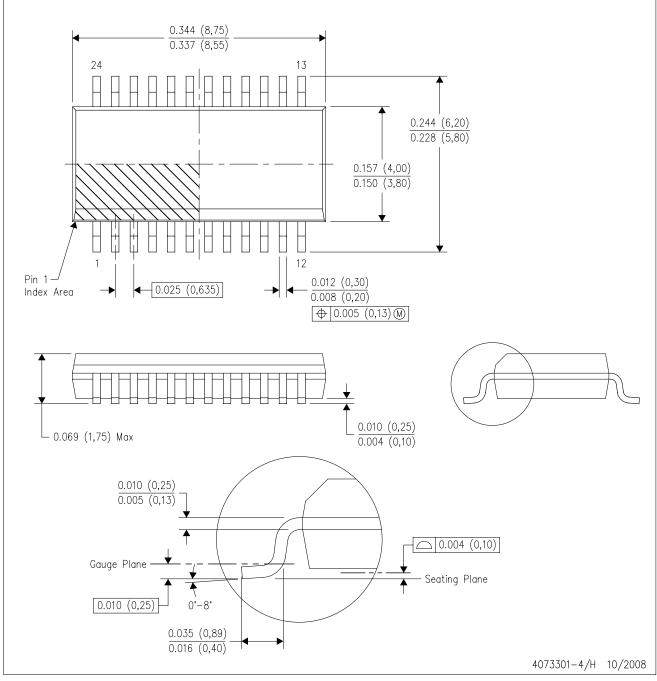

DBQ (R-PDSO-G24)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15) per side.

- D. Falls within JEDEC MO-137 variation AE.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated