## **General Description**

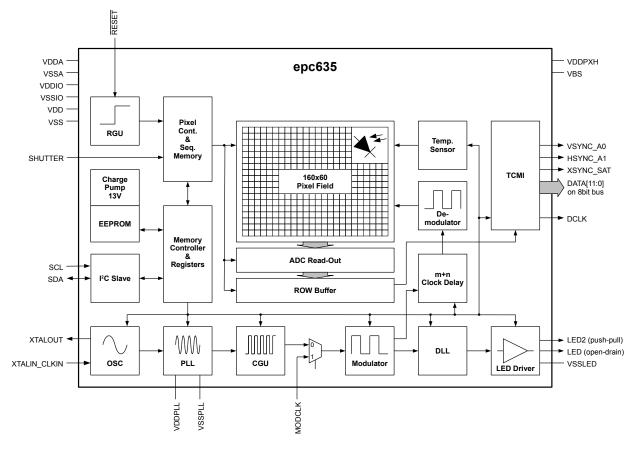

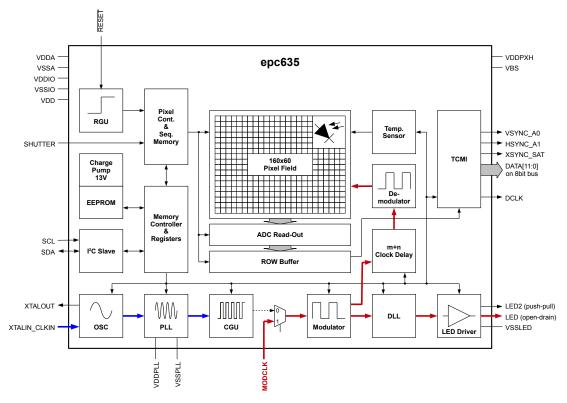

The epc635 is a fully integrated 3D-TOF imager with a resolution of 160 x 60 pixels (Half-QQVGA). As a system on chip, the epc635 contains next to the CCD pixel-field the complete control logic to operate the device. The output of the chip is 12 bit DCS distance data per pixel, which are accessible through a high-speed digital 8-bit parallel video interface.

Only few additional components are needed to generate a complete 3D camera. Depending on illumination power and optical design, a resolution in the millimeter range for distances up to dozens of meters is feasible. Up to 512 full frame TOF images are delivered in rolling mode. The extremely high sensitivity of the chip allows for a reduced illumination power and reduced overall power consumption compared to other TOF imagers.

epc635 is based on the same technology and instruction set as the epc660 QVGA TOF imager from ESPROS.

An evaluation kit for the epc635 is available with hard- and software examples and a comprehensive manual to speed up system integration.

## **Applications**

- People detection and counting

- Postal parcel size measurement

- Machine safety

- Helicopter near terrain flight assistance

- ADAS systems

- Pedestrian detection and breaking systems

- Man-Machine interface

- Gesture control

- Body size measurement

- General volumetric mapping

- Mobile robotics

- Simultaneous localization and mapping (SLAM)

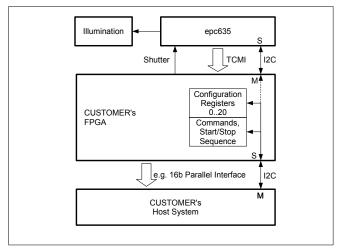

## **Block Diagram**

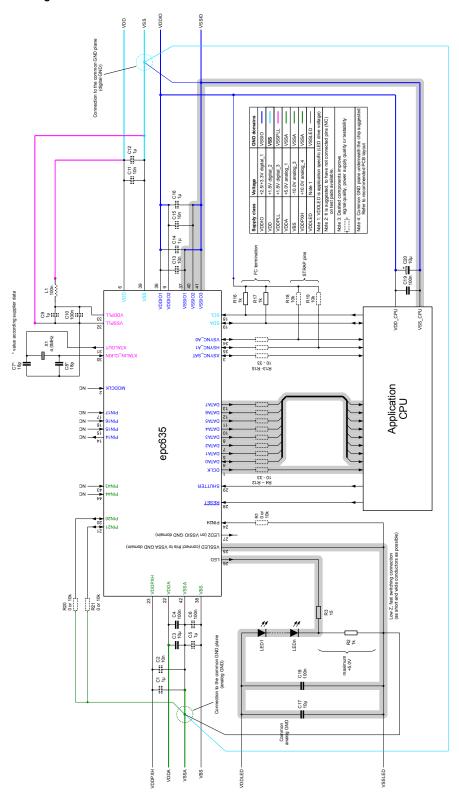

Figure 1: Functional block diagram

## **Main Features**

#### ■ General

- □ 3D TOF imager in full monolithic design

- □ 160 x 60 pixel-field, backside illuminated

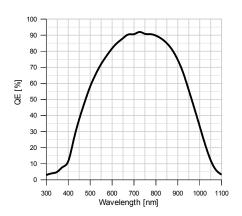

- □ QE >80% @ 850nm

- □ Full well capacity 8'000 ke- (ambient and signal)

- □ 128 fps full 3D TOF frame rate, in rolling mode up to 512fps

- □ Integrated temperature sensor

#### ■ Measurement performance

Absolute accuracy in the centimeter range with appropriate setup and calibration

#### ■ Integrated LED (or laser diode) driver

- □ Laser diode (LD) illumination possible

- □ Open-drain LED output pad, up to 200mA drive

- □ Push-pull LED2 output pad, up to 50mA drive

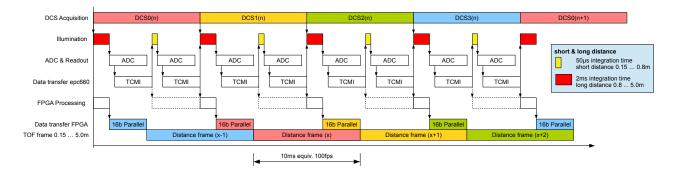

### ■ Parallel digital data interface TCMI

- □ 80MS/s max. data rate, 2.5/3.3V compatible

- □ 12/8-bit DATA output + XSYNC/SAT flag on 8 bit parallel TCMI interface.

- □ VSYNC, HSYNC and DCLK outputs

## ■ I<sup>2</sup>C control interface (slave)

□ 400kHz (FM) / 1MHz (FM+)

#### ■ Integrated EEPROM 128 x 8-bit

- □ Calibration data and user programmable parameters

- □ Unique chip ID

#### ■ System / Modulation clock

- □ System clock 4MHz, internal by using crystal/resonator or using external input

- □ External LED/LD modulation input MODCLK (optional) up to 80MHz

#### ■ Power supplyø

- □ Supply voltages +10V, +5V, +2.5/3.3V, +1.8V, -10V

- □ Power consumption approx. 300mW (average)

#### ■ Packaging

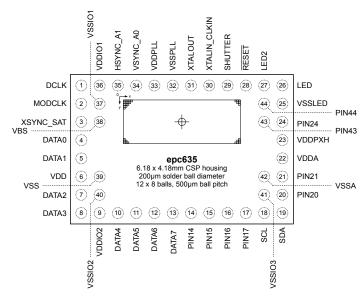

- □ 6.3x4.2mm cost optimized 44pin CSP (chip scale package),

- □ Backside illuminated flip-chip SMD mounting

## ■ Other data

□ ROHS compatible

## **Measurement Modes**

#### ■ Illumination modulation modes

- □ Sinusoidal modulation

- □ Selectable modulation frequencies 0.625 ... 20MHz resulting in unambiguity distance of 7.5m ... 240m

#### ■ Distance measurement modes

- □ 128 fps 3D TOF with 4x DCS frames, full pixel-field

- □ 256 fps 3D TOF with 2x DCS frames, full pixel-field

- 512 fps 3D TOF with rolling read-out 4x DCS frames, full pixel-field

- □ SHUTTER release input for precise start/stop and single / continuous measurement control

#### ■ Non distance measurement modes

- □ Ambient-light measurement (Grayscale imaging without illumination)

- □ Grayscale image with active illumination

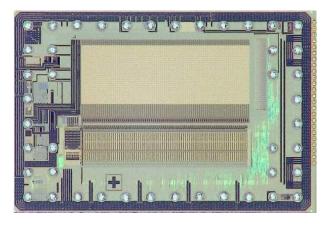

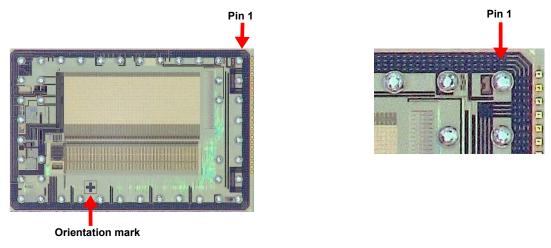

Figure 2: Picture of the epc635 die

## **Table of contents**

| 1. | . Electrical, optical and timing characteristics                 | 6  |

|----|------------------------------------------------------------------|----|

|    | 1.1. Operating conditions and electrical characteristics         | 6  |

|    | 1.2. Absolute maximum ratings                                    | 7  |

|    | 1.3. Timing parameters                                           | 7  |

|    | 1.4. Optical characteristics                                     | 7  |

|    | 1.5. Sensitivity                                                 | 8  |

|    | 1.6. Ambient-light suppression (ABS)                             |    |

|    | 1.7. Other optical parameters                                    |    |

|    | 1.8. Distance measurement temperature drift                      |    |

|    | 1.9. Temperature sensor characteristics                          | 9  |

| 2. | . Pin-out                                                        | 10 |

|    | 2.1. Pin mapping                                                 | 10 |

|    | 2.2. Pin list                                                    | 10 |

|    | 2.3. Power domains and ESD protection                            | 12 |

| 3. | . Packaging and layout information                               | 12 |

|    | 3.1. Mechanical dimensions                                       |    |

|    | 3.2. Parasitic light sensitivity (PLS)                           |    |

|    | 3.3. Pin1 marking                                                |    |

|    | 3.4. Location of the photosensitive area                         |    |

|    | 3.5. PCB design and SMD manufacturing process considerations     | 14 |

|    | 3.6. Tape & reel information                                     | 15 |

| 4. | Ordering information                                             | 15 |

|    | 4.1. Notes to various chip releases                              |    |

| _  | . Hardware implementation                                        |    |

| Э. | ·                                                                |    |

|    | 5.1. Typical application diagram                                 |    |

|    | 5.3. Hardware implementation notes                               |    |

|    | 5.4. Clock source                                                |    |

|    | 5.5. External modulation MODCLK                                  |    |

|    | 5.6. Supply, reset and start-up options                          |    |

|    | 5.6.1. Supply voltages and external reset                        |    |

|    | 5.6.2. Start-up (Clock, PLL turn-on and EEPROM copy)             |    |

|    | 5.6.3. Strap pins                                                |    |

|    | 5.7. LED driver                                                  | 20 |

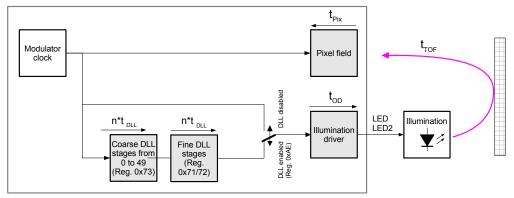

|    | 5.8. DLL (Delay Line)                                            | 20 |

|    | 5.9. Application system overview                                 | 22 |

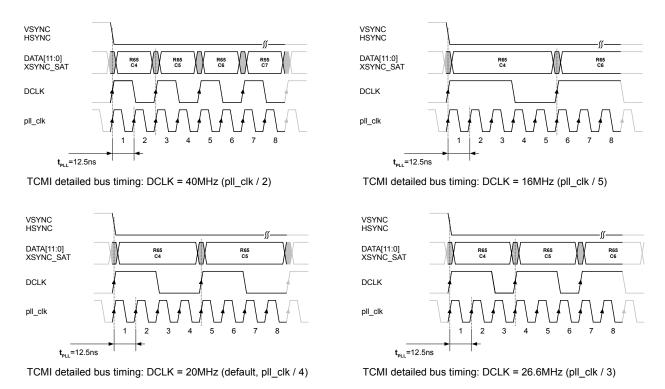

| 6. | . TOF camera interface (TCMI)                                    | 22 |

| •  | 6.1. TCMI clock                                                  |    |

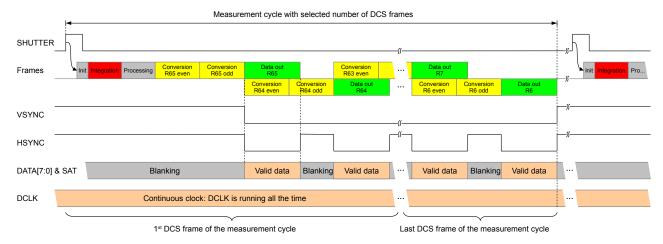

|    | 6.1.1. Continuous clock mode                                     |    |

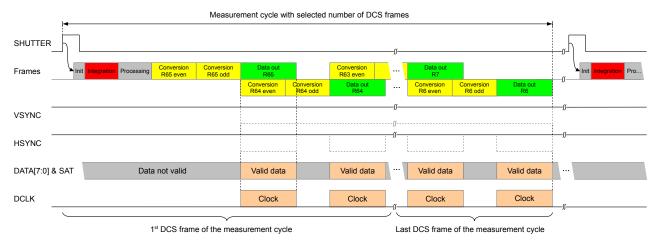

|    | 6.1.2. Gated clock mode                                          |    |

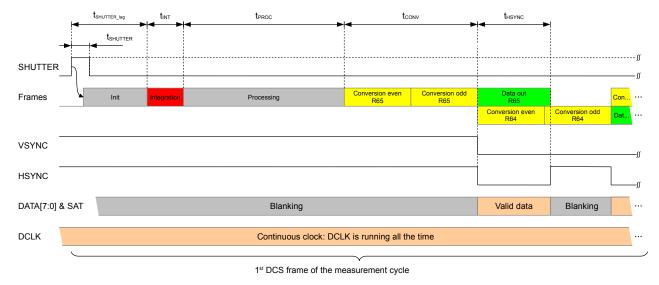

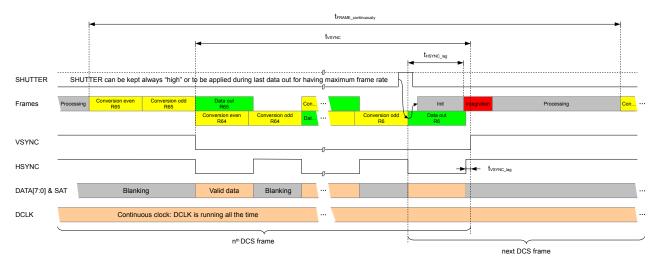

|    | 6.2. Single or continuous measurement control                    | 23 |

|    | 6.2.1. Single measurement control                                | 23 |

|    | 6.2.2. Continuous measurement control (auto-run)                 | 23 |

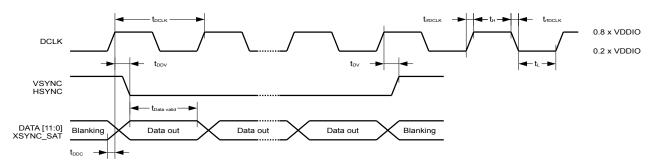

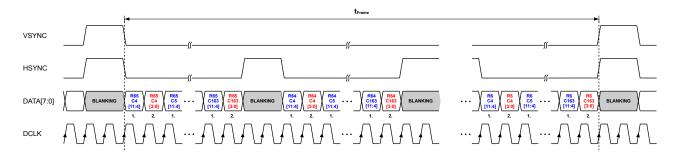

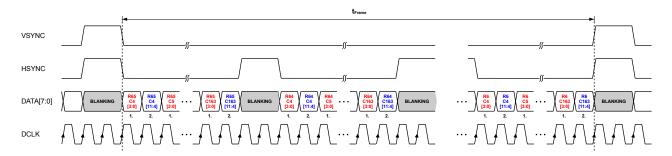

|    | 6.3. TCMI timing                                                 | 24 |

|    | 6.4. TCMI data format                                            | 25 |

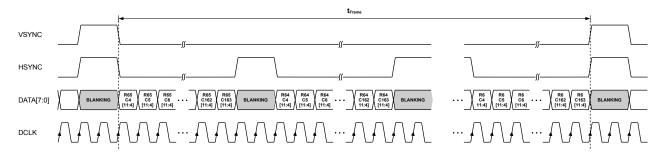

|    | 6.5. TCMI embedded synchronization mode                          |    |

|    | 6.6. Frame rate and data-out performance                         |    |

|    | 6.7. Memory space estimation                                     | 28 |

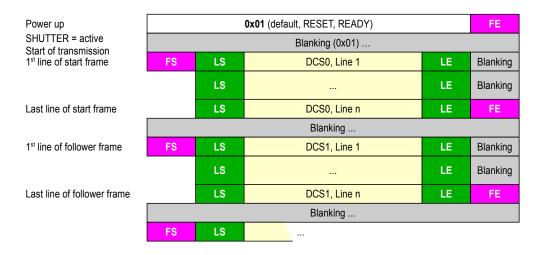

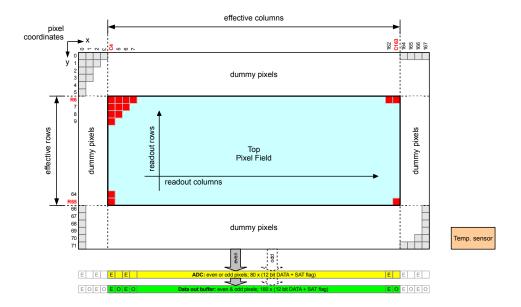

| 7. | Pixel architecture                                               | 29 |

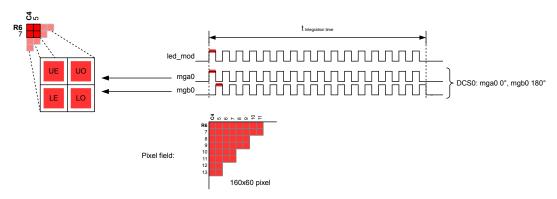

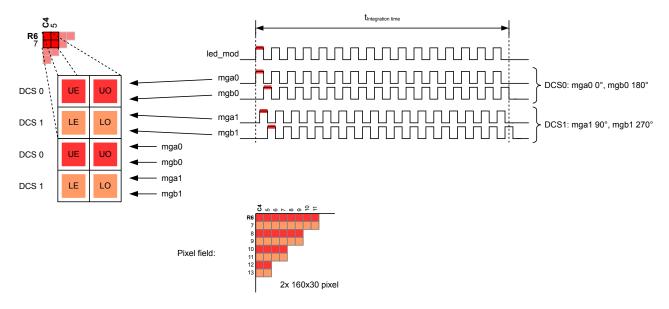

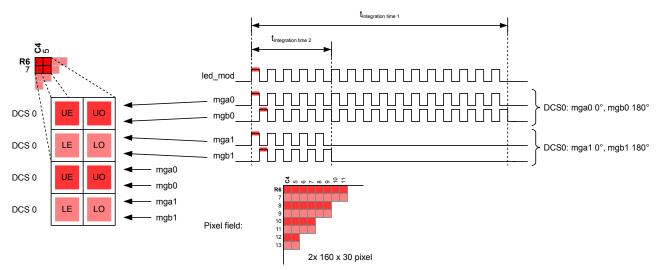

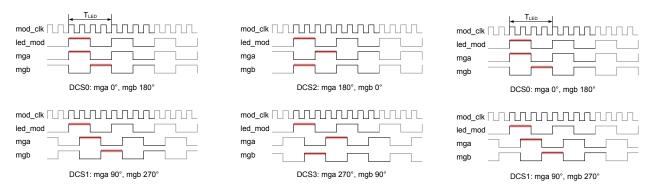

| 8. | Pixel-field and operation modes                                  | 30 |

| ٠. | 8.1. Pixel coordinates                                           |    |

|    | 8.2. Operation modes                                             |    |

|    | 8.2.1. Full resolution mode (default)                            |    |

|    | 8.2.2. Dual phase mode (motion blur reduction)                   |    |

|    | 8.2.3. Dual integration time mode (high dynamic range, HDR mode) |    |

|    | 8.3. Pixel saturation detection                                  |    |

|       | 8.3.1. Hardware saturation flag                                                                                                         | 32       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | 8.3.2. Software saturation flag                                                                                                         |          |

|       | 8.4. ADC conversion speed-up                                                                                                            | 32       |

| 9.    | Imaging                                                                                                                                 | 33       |

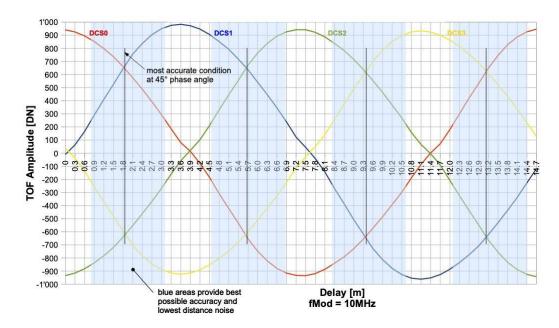

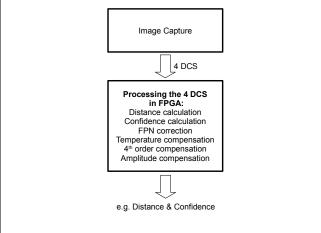

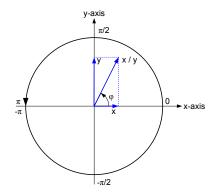

|       | 9.1. Distance measurement (3D TOF)                                                                                                      | 33       |

|       | 9.2. Distance calculation algorithm                                                                                                     | 34       |

|       | 9.2.1. Unambiguity range versus time base setting                                                                                       | 34       |

|       | 9.2.2. Quality of the measurement                                                                                                       | 35       |

|       | 9.3. Grayscale imaging                                                                                                                  | 36       |

|       | 9.4. Calibration and compensation of TOF cameras                                                                                        |          |

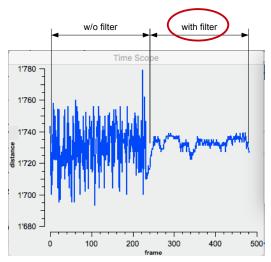

|       | 9.5. Noise reduction and signal filtering                                                                                               | 36       |

| 10.   | Temperature sensor                                                                                                                      | 38       |

|       | 10.1. Initialization                                                                                                                    |          |

|       | 10.2. Read-out during runtime                                                                                                           | 38       |

|       | 10.3. Calculate temperature in °C                                                                                                       | 39       |

| 11    | Application information                                                                                                                 | 40       |

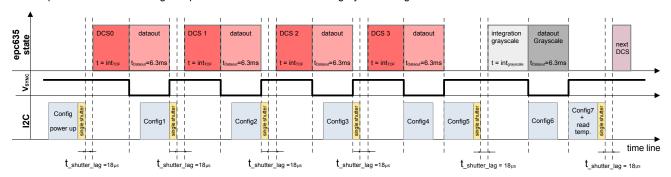

| • • • | 11.1. Start-up and initialization sequence                                                                                              |          |

|       | 11.1.1 Default                                                                                                                          |          |

|       | 11.1.2. Customer specific                                                                                                               |          |

|       | 11.2. Image acquisition                                                                                                                 |          |

|       | 11.3. 3D TOF distance measurement flow                                                                                                  |          |

|       | 11.4. Integration time setting                                                                                                          |          |

|       | 11.5. Special mode setting                                                                                                              |          |

|       | 11.5.1. Dual phase mode (motion blur reduction)                                                                                         |          |

|       | 11.5.2. TOF and grayscale single DCS acquisition with 2 different integration times (High dynamic range)                                |          |

|       | 11.6. Power consumption                                                                                                                 | 43       |

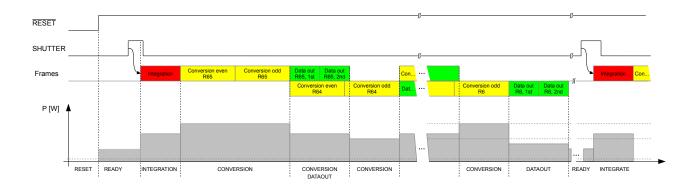

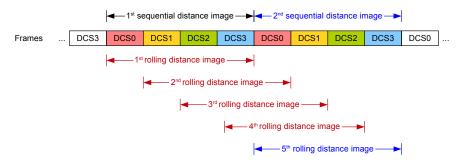

|       | 11.7. Rolling DCS frames                                                                                                                | 44       |

|       | 11.8. Enhanced rolling DCS frame mode                                                                                                   | 44       |

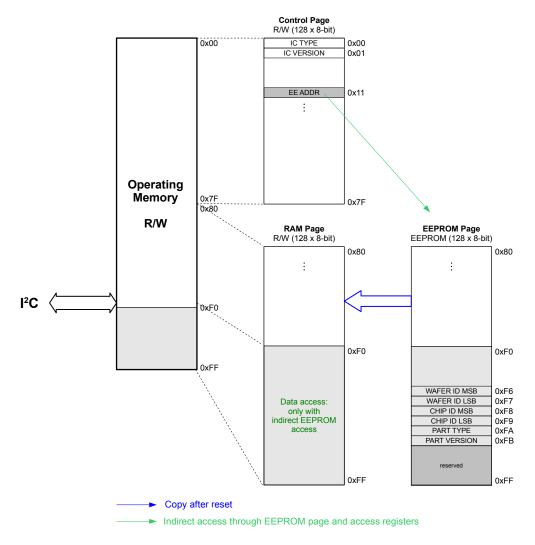

| 12.   | Parameter and configuration memory                                                                                                      | 46       |

|       | 12.1. Sequencer program                                                                                                                 |          |

|       | 12.2. Data memory map                                                                                                                   |          |

|       | 12.2.1. Control page                                                                                                                    |          |

|       | 12.2.2. RAM page                                                                                                                        | 46       |

|       | 12.2.3. EEPROM page                                                                                                                     | 46       |

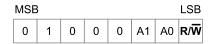

| 13    | I <sup>2</sup> C interface                                                                                                              | 47       |

|       | 13.1. Device addressing                                                                                                                 |          |

|       | ·                                                                                                                                       | 47<br>47 |

|       | 13.3. I <sup>2</sup> C bus timing                                                                                                       |          |

|       | 13.4. I <sup>2</sup> C commands                                                                                                         |          |

|       | 13.4.1. Software reset                                                                                                                  |          |

|       | 13.4.2. Device address reload                                                                                                           |          |

|       | 13.4.3. Write single-byte                                                                                                               |          |

|       | 13.4.4. Write multi-byte                                                                                                                |          |

|       | 13.4.5. Read single-byte                                                                                                                |          |

|       | 13.4.6. Read multi-byte                                                                                                                 | 49       |

|       | 13.4.7. Command timing                                                                                                                  | 49       |

| 14.   | Register map                                                                                                                            | 50       |

|       | 14.1. Control page 0x00 ~ 0x7F                                                                                                          |          |

|       | 14.2. RAM page (0x80 ~ 0xEF)                                                                                                            |          |

|       | 14.3. EEPROM page, indirect data access section (0xF0 ~ 0xFF)                                                                           |          |

| 4 6   |                                                                                                                                         |          |

| 13.   | Control command examples                                                                                                                |          |

|       | 15.1. Software reset                                                                                                                    |          |

|       | 15.2. 4 DCS: Acquire DCS0 3 frames with t <sub>int</sub> = 20µs @ 10MHz modulation frequency                                            |          |

|       | 15.3. 4 DCS: Acquire DCS0 3 frames with $t_{int}$ = 20 $\mu$ s, followed by DCS 0 3 with $t_{int}$ 400 $\mu$ s @ 10MHz mod. frequency . |          |

|       | 15.4. 2 DCS: Acquire DCS0 and 1 frames with t <sub>int</sub> = 20µs @ 10MHz modulation frequency                                        |          |

|       | 15.5. Indirect single write to EEPROM: Store 1 byte at user register 0xF0                                                               | 57       |

|       | 15.6. Indirect single read from EEPROM: Read 1 byte from user register 0xF0                                                             | 57       |

|       | 15.7. Reading part version (register 0xFB)                                                                                              |          |

|       | 15.8. Reading IC version (register 0x01)                                                                                                | 57       |

| 17. | IMPORTANT NOTICE                            | 62 |

|-----|---------------------------------------------|----|

|     | 16.2. Related documents                     | 61 |

|     | 16.1. Terms, definitions and abbreviations  | 61 |

| 16. | Addendum                                    | 61 |

|     | 15.12. Pixel sequencer code readback        |    |

|     | 15.11. Pixel sequencer code                 |    |

|     | 15.10. Pixel sequencer code write procedure |    |

|     | 15.9. Reading WAFER ID and CHIP ID          | 57 |

## 1. Electrical, optical and timing characteristics

All characteristics are at typical operational ratings, T<sub>A</sub> = +25°C, modulation frequency 10MHz, unless otherwise stated

#### 1.1. Operating conditions and electrical characteristics

| Parameter              | Description                                     | Conditions/Comments                                                  | Min.                    | Тур.              | Max.                    | Units  |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-------------------------|-------------------|-------------------------|--------|

| $V_{DD}, V_{DDPLL}$    | Digital supply voltage                          | Ripple <sup>1</sup> < ± 20 mV                                        | 1.71                    | 1.80              | 1.98                    | V      |

| $V_{\text{DDIO}}$      | IO supply voltage <sup>3</sup>                  | Ripple <sup>1</sup> < ± 50 mV                                        | 2.25                    | 2.5/3.3           | 3.63                    | V      |

| $V_{DDA}$              | Analog 1 supply voltage <sup>2</sup>            | Ripple <sup>1</sup> < ± 20 mV                                        | 4.9                     | 5.0               | 5.1                     | V      |

| $V_{\text{DDPXH}}$     | Analog 2 supply voltage <sup>2</sup>            | Ripple <sup>1</sup> < ± 20 mV                                        | 9.5                     | 10                | 10.5                    | V      |

| V <sub>BS</sub>        | Bias supply voltage                             | Ripple <sup>1</sup> < ±50 mV                                         | -10.5                   | -10.0             | -9.75                   | V      |

| I <sub>VDD</sub>       | Digital supply current                          | @nominal voltage                                                     |                         | 10                | 11                      | mA     |

| I <sub>VDDPLL</sub>    | PLL supply current                              | @nominal voltage                                                     |                         | 4                 |                         | mA     |

| I <sub>VDDIO</sub>     | IO supply current <sup>4</sup>                  |                                                                      |                         | 15                | 25                      | mA     |

| $I_{VDDA}$             | Analog supply current                           | @nominal voltage                                                     |                         | 22                | 33                      | mA     |

| I <sub>VDDPXH</sub>    | Analog 2 supply current                         | @nominal voltage                                                     |                         | 2                 | 2                       | mA     |

| I <sub>VBS</sub>       | Bias supply current <sup>8</sup>                |                                                                      |                         | -2.0 <sup>8</sup> |                         | mA     |

| V <sub>LED_ON</sub>    | LED on-voltage forward voltage                  | @ I <sub>LEDOD-ON</sub> = 100 mA<br>@ I <sub>LEDOD-ON</sub> = 200 mA |                         | 0.1<br>0.2        |                         | V<br>V |

| I <sub>LED_LEAK</sub>  | LED leakage current                             | @ LEDOD off-voltage                                                  |                         |                   | 10                      | μΑ     |

| I <sub>LED2_SINK</sub> | LED2 output sink/source current                 |                                                                      |                         |                   | 50                      | mA     |

| V <sub>IH_VDDIO</sub>  | Digital high level input voltage 5              | excluding XTALIN                                                     | 0.7 x V <sub>DDIO</sub> |                   |                         | V      |

| $V_{\text{IL\_VDDIO}}$ | Digital low level input voltage 5               | excluding XTALIN                                                     |                         |                   | 0.3 x V <sub>DDIO</sub> | V      |

| V <sub>IH_XTALIN</sub> | Digital high level input voltage                | XTALIN                                                               | 1.35                    |                   |                         | V      |

| V <sub>IL_XTALIN</sub> | Digital low level input voltage                 | XTALIN                                                               |                         |                   | 0.2                     | V      |

| V <sub>OH</sub>        | Digital high level output voltage 5,6           |                                                                      | 0.8 x V <sub>DDIO</sub> |                   |                         | V      |

| V <sub>OL</sub>        | Digital low level output voltage 5,6            |                                                                      |                         |                   | 0.2 x V <sub>DDIO</sub> | V      |

| R <sub>PD</sub>        | Pull-down resistor in RESET, VSYNC_A0, HSYNC_A1 |                                                                      |                         | 600               |                         | kΩ     |

| I <sub>IH</sub>        | Digital high level input current <sup>7</sup>   | V <sub>IH</sub> max.                                                 |                         |                   | 10 <sup>7</sup>         | μA     |

| I <sub>IL</sub>        | Digital low level input current 7               | V <sub>IL</sub> min.                                                 | -10 <sup>7</sup>        |                   |                         | μΑ     |

| I <sub>OH</sub>        | Digital output source current 7                 | V <sub>OH</sub> max.                                                 |                         |                   | 50                      | mA     |

| I <sub>OL</sub>        | Digital output sink current <sup>3</sup>        | V <sub>OL</sub> min.                                                 | -50                     |                   |                         | mA     |

| C <sub>IO</sub>        | IO load capacitance <sup>5</sup>                |                                                                      |                         |                   | 30                      | pF     |

| f <sub>IO</sub>        | IO switching frequency 5                        |                                                                      |                         | 20                | 80                      | MHz    |

| $P_{Pk}$               | Power dissipation (average)                     | See Error: Reference source not found                                |                         | 300               |                         | mW     |

| R <sub>Th</sub>        | Thermal resistance                              | on PCB with underfill                                                |                         |                   | 40                      | °K/W   |

| T <sub>OP</sub>        | Operating temperature                           |                                                                      | -40                     |                   | 105                     | °C     |

Table 1: Operating conditions and electrical characteristics

#### Notes:

<sup>&</sup>lt;sup>1</sup> Min. and Max. voltage values include noise and ripple voltages.

<sup>&</sup>lt;sup>2</sup> Analog voltage supplies have direct influence on measurement performance. They must be properly decoupled for low noise and ripple.

<sup>3</sup> IO voltage supply must be equal to external processor's IO supply voltage levels used in the application. It can be set to any value within min and max. operating voltage.

When device is operated at max f<sub>DCS</sub> frame rate, DCLK at 40MHz, driving loads 15pF each.

<sup>&</sup>lt;sup>5</sup> I<sup>2</sup>C pins SCL and SDA are open-drain outputs and need termination (Pull-up resistor) according to I<sup>2</sup>C standards.

$<sup>^6</sup>$   $\,\,$   $V_{\text{OH/OL}}$  and  $I_{\text{OH/OL}}$  values are measured at max  $C_{\text{IO}}$  and max  $f_{\text{IO}}.$

<sup>&</sup>lt;sup>7</sup> Value is without termination resistors

<sup>8</sup> A bright illuminated white target right in front of the chip with lens leads to an I<sub>VBS</sub> of approx. -2.0 mA, without any illumination approx. -2.0 mA and with strong illumination (approx. 55 mW/cm², no lens) typ. -9.0 mA.

## 1.2. Absolute maximum ratings

| Parameter                                                                         | Conditions                                                                                          |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Supply voltage V <sub>DD</sub> , V <sub>DDPLL</sub>                               | -0.5V +2.0V                                                                                         |

| Supply voltage V <sub>DDIO</sub> , V <sub>DDA</sub> , V <sub>DDPXM</sub>          | -0.5V +5.5V                                                                                         |

| Supply voltage V <sub>DDPXH</sub>                                                 | -0.5V +13.5V                                                                                        |

| Supply voltage V <sub>BS</sub>                                                    | -12.0 +0.5V                                                                                         |

| Voltage to any pin in the same V <sub>SC</sub> supply class.                      | V <sub>SC min</sub> - 0.3V V <sub>SC max</sub> + 0.3V                                               |

| LED sink current I <sub>ON_LED</sub> (modulated peak current, refer to Figure 17) | 200 mA @T <sub>J</sub> 85°C<br>25 mA @T <sub>J</sub> 125°C<br>linear reduction between 85 and 125°C |

| LED off-voltage V <sub>OFF_LED</sub> (open-drain output)                          | 7.5 V                                                                                               |

| ESD rating                                                                        | JEDEC HBM class 1C (1kV to < 2kV)                                                                   |

| Junction temperature (T <sub>J</sub> )                                            | -40°C to +125°C                                                                                     |

| Relative humidity                                                                 | 0 95%, non-condensing                                                                               |

Table 2: Absolute maximum ratings

## 1.3. Timing parameters

| Parameter                                   | Description                         | Conditions                                                                                                                | Min.  | Тур. | Max.  | Units  |

|---------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|------|-------|--------|

| t <sub>STARTUP</sub>                        | Start-up time                       | after applying external supplies                                                                                          |       | 340  | 1'000 | μs     |

| t <sub>RESET</sub>                          | RESET                               |                                                                                                                           | 100   |      |       | ns     |

| t <sub>PLL</sub>                            | PLL lock time                       |                                                                                                                           |       |      | 30    | μs     |

| t <sub>DLL</sub>                            | DLL delay for 1 step                | approx. 30cm distance shift per step. Refer for details to register 0x73 and Figure 21, for exact value to register 0xE9. |       | 2.1  |       | ns     |

| t <sub>DRV</sub>                            | Illumination driver delay           | delay of LED/LED2 versus demodulation, refer to Figure 21                                                                 |       | 8.4  |       | ns     |

| t <sub>EEPROM_to_CFG</sub>                  | Load CFG registers                  | copy EEPROM to CFG registers                                                                                              |       | 340  |       | μs     |

| t <sub>EEPROM_Write</sub>                   | Write EEPROM                        | waiting time per byte                                                                                                     |       |      | 25    | ms     |

| f <sub>XTAL</sub>                           | Clock frequency                     | determines the distance measurement accuracy                                                                              | 3.8   | 4    | 4.2   | MHz    |

| df <sub>XTAL</sub>                          | Clock frequency deviation           | any deviation is added as a linear distance error                                                                         |       |      | ±100  | ppm    |

| f <sub>JITTER</sub>                         | Clock frequency phase jitter        | peak-to-peak, cycle to cycle                                                                                              |       |      | 50    | ps     |

| f <sub>LED</sub>                            | LED modulation frequency,           | Internal modulation                                                                                                       | 0.625 |      | 10    | MHz    |

| teeprom_write  fxtal  dfxtal  fjitter  fled | refer to chapter 11.1.2, section 13 | External modulation                                                                                                       | 0.625 |      | 20    | MHz    |

| f <sub>MODCLK</sub>                         | Ext. modulation clock               | refer to chapter 5.5                                                                                                      |       |      | 80    | MHz    |

| t <sub>LED_rise/fall</sub>                  | Rise/fall time LED/LD               | slower rise/fall time lead to illumination losses                                                                         |       |      | 12    | ns     |

| f <sub>DCLK</sub>                           | TCMI DCLK                           | 8 bit TCMI data + saturation flag                                                                                         |       | 20   | 80    | MHz    |

| f <sub>TCMI_data</sub>                      | TCMI data rate                      |                                                                                                                           |       | 130  | 520   | Mbit/s |

| f <sub>SCL</sub>                            | I <sup>2</sup> C data rate          |                                                                                                                           |       |      | 1     | Mbit/s |

Table 3: Timing parameters

## 1.4. Optical characteristics

| Parameter           | Description               | Conditions/Comments | Min. | Тур.      | Max. | Units |

|---------------------|---------------------------|---------------------|------|-----------|------|-------|

| A <sub>PIXEL</sub>  | Pixel photosensitive area | 100% fill factor    |      | 20 x 20   |      | μm    |

| A <sub>SENSOR</sub> | Pixel field area          | 160 x 60 pixel      |      | 3.2 x 1.2 |      | mm    |

Table 4: Optical characteristics

#### Note

Values depend on camera integration. Typical examples only. Refer for details to Figure 21 and application note AN10 Calibration and Compensation, chapter temperature compensation.

#### 1.5. Sensitivity

@ integration time 100 µs

| Parameter                        | Description                                |       | Min. | Тур. | Max. | Units          |

|----------------------------------|--------------------------------------------|-------|------|------|------|----------------|

|                                  | Modulation frequency 12MHz                 | 640nm | 0.75 | 0.9  | 1.05 | 2              |

| TOF sensitivity S <sub>TOF</sub> | Amplitude 1,400 LSB                        | 850nm | 0.50 | 0.6  | 0.70 | nW/mm²<br>LSB  |

|                                  |                                            | 940nm | 0.65 | 0.8  | 0.95 |                |

| TOF <sub>SENS</sub> FPN          | Sensitivity fix pattern noise, @ 1,400 LSB |       |      | 40   | 100  | LSB            |

| TOF <sub>DIST</sub> FPN          | Distance fix pattern noise, @ 1,400 LSB    |       |      | 18   | 50   | mm             |

| Dark                             | Dark current (drift during readout)        |       |      | 10   | 20   | LSB/ms         |

|                                  | Normal operation                           |       | 0.19 | 0.25 | 0.31 | nW/mm²         |

| Grayscale sensitivity            | Temperature sensing mode                   |       | 0.48 | 0.62 | 0.76 | LSB            |

| Η <sub>ν</sub>                   | Optical sensitivity                        |       |      | 150k |      | LSB<br>Lux/sec |

| GS <sub>STD</sub>                | Grayscale standard deviation               |       |      | 25   | 100  | LSB            |

Table 5: Sensitivity

## 1.6. Ambient-light suppression (ABS)

An important function of the 3D TOF pixel is the ambient-light suppression. It removes DC or low frequency modulated light caused by sunlight, room illumination, etc. from the modulated light generated by the camera illumination. The amount of collected ambient light is proportional to the integration time. The longer the integration time, the more unwanted light will be collected. It's a good practice to keep the integration time for TOF imaging below 1ms. In addition, optical bandpass filters to block the unwanted light spectrum is mandatory.

| Parameter      | Ambient light suppression | Integration time | Wavelengt<br>h | Min. | Тур. | Max. | Units  |

|----------------|---------------------------|------------------|----------------|------|------|------|--------|

| E <sub>e</sub> | Irradiance, DC light      | 100 µs           | 640nm          | 0.30 |      |      | mW/mm² |

|                |                           |                  | 850nm          | 0.20 |      |      |        |

|                |                           |                  | 940nm          | 0.25 |      |      |        |

| Parameter      | Ambient light suppression      | Integration time | Center wavelength | Bandwidth | Min. | Тур. | Max. | Units |

|----------------|--------------------------------|------------------|-------------------|-----------|------|------|------|-------|

| E <sub>v</sub> | Luminance equivalent, sunlight | 500µs            | 640nm             | ±27.5nm   | 85   |      |      | kLux  |

|                |                                |                  | 850nm             | ±32.5nm   | 70   |      |      |       |

|                |                                |                  | 940nm             | ±30nm     | 190  |      |      |       |

Table 6: Ambient light suppression

#### Note:

The default and suggested chip configuration is set to achieve highest possible frame rate and using additional ambient-light correction according the Application note AN10 Calibration and compensation: Register 0x90, bit 3 = 0 and 0xAB = 0x00. A 20% more efficient ambient-light suppression is possible, if the the following registers are modified:

0x90, bit 3 = 10xAB = 0x01

It turns the LED modulation before each integration for additional 33 $\mu$ s @ 24MHz modulation frequency on. This modulation is independent of the effective integration time. The on-time depends on the modulation frequency by  $t_{\text{ON}}$  = 40 $\mu$ s \* 20MHz / modulation frequency.

## 1.7. Other optical parameters

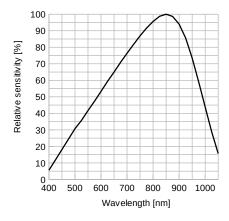

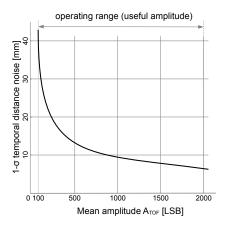

Figure 3: Relative spectral sensitivity  $(S_{\lambda})$  vs. wavelength

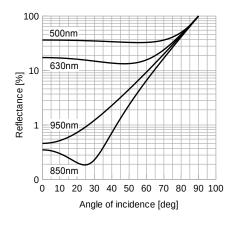

Figure 4: Reflectance vs. illumination angle (AOI)

Figure 5: Typ. distance noise, single shot, 4 DCS, no ambient-light, see chapter 9.2.2

Figure 6: Typical quantum efficiency

## 1.8. Distance measurement temperature drift

@12MHz modulation frequency

| Parameter          | Description          | Min. | Тур. | Max. | Units |

|--------------------|----------------------|------|------|------|-------|

| TC <sub>PIX</sub>  | Pixel                |      | 12.9 |      | mm/K  |

| TC <sub>OD</sub>   | LED/LD driver        |      | 2.7  |      | mm/K  |

| TC <sub>DLLn</sub> | DLL stage, per stage |      | 0.65 |      | mm/K  |

Table 7: Optical characteristics

Note: Values vary from imager to imager. Refer for details to Figure 21 and application note AN10 Calibration and Compensation, chapter temperature compensation.

### 1.9. Temperature sensor characteristics

| Parameter         | Description             | Conditions             | Min. | Тур.  | Max. | Units |

|-------------------|-------------------------|------------------------|------|-------|------|-------|

| T <sub>TEMP</sub> | Measurement range       |                        | -40  |       | +105 | °C    |

| P <sub>TEMP</sub> | Sensor resolution       |                        |      | 14    |      | bit   |

| k                 | Temperature sensor gain |                        |      | 0.067 |      | K/LSB |

| Lin               | Linearity               | Over temperature range |      | 5     |      | %     |

| T <sub>CAL</sub>  | Calibration temperature |                        | 26.5 | 27.0  | 27.5 | °C    |

Table 8: Temperature sensor characteristics

Note: Refer also to chapter 10

## 2. Pin-out

## 2.1. Pin mapping

Figure 7: Pin mapping (top-view, solder balls are at the bottom, pixel-field is at the top)

#### 2.2. Pin list

| Pin<br>No. | Pin name     | Supply class V <sub>sc</sub> | Pin<br>type | RESET function | RESET<br>level   | Description                                                           |  |  |  |  |  |

|------------|--------------|------------------------------|-------------|----------------|------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| IO pi      | ns           |                              |             |                |                  |                                                                       |  |  |  |  |  |

| 4          | DATA0        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 0 (LSB), no pull-up resistor allowed       |  |  |  |  |  |

| 5          | DATA1        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 1                                          |  |  |  |  |  |

| 7          | DATA2        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 2                                          |  |  |  |  |  |

| 8          | DATA3        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 3                                          |  |  |  |  |  |

| 10         | DATA4        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 4                                          |  |  |  |  |  |

| 11         | DATA5        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 5                                          |  |  |  |  |  |

| 12         | DATA6        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 6                                          |  |  |  |  |  |

| 13         | DATA7        | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI high-speed output bit 7                                          |  |  |  |  |  |

| 1          | DCLK         | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI data clock output                                                |  |  |  |  |  |

| 34         | VSYNC_A0     | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OH</sub>  | TCMI VSYNC output / strap input 0, refer to 5.6.3                     |  |  |  |  |  |

| 35         | HSYNC_A1     | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OH</sub>  | TCMI HSYNC output / strap input 1, refer to 5.6.3                     |  |  |  |  |  |

| 3          | XSYNC_SAT    | $V_{DDIO}$                   | DIO         | IPD            | V <sub>OL</sub>  | TCMI XSYNC / TCMI Saturation flag output, no pull-up resistor allowed |  |  |  |  |  |

| 18         | SCL          | $V_{DDIO}$                   | DIOD        | I              | V <sub>IH</sub>  | I <sup>2</sup> C clock input <sup>4</sup>                             |  |  |  |  |  |

| 19         | SDA          | $V_{DDIO}$                   | DIOD        | I              | V <sub>IH</sub>  | I <sup>2</sup> C data input/output <sup>4</sup>                       |  |  |  |  |  |

| 29         | SHUTTER      | $V_{DDIO}$                   | DI          | PD             | V <sub>IL</sub>  | Shutter input <sup>5</sup>                                            |  |  |  |  |  |

| 28         | RESET        | $V_{DDIO}$                   | DI          | PD             | V <sub>IL</sub>  | Reset input (active low), $600k\Omega$ int. pull-down $^3$            |  |  |  |  |  |

| 2          | MODCLK       | $V_{DDIO}$                   | DI          | PD             |                  | Modulator/demodulator external clock input.                           |  |  |  |  |  |

| 27         | LED2         | $V_{DDIO}$                   | DO          |                | V <sub>IL</sub>  | LED driver push-pull output <sup>2</sup>                              |  |  |  |  |  |

| 14         | PIN14        | $V_{DDIO}$                   | DO          |                | V <sub>OL</sub>  |                                                                       |  |  |  |  |  |

| 15         | PIN15        | $V_{DDIO}$                   | DI          | PU             | V <sub>IH</sub>  | Do not any electrical connection except to a test pad (suggested).    |  |  |  |  |  |

| 16         | PIN16        | $V_{DDIO}$                   | DI          | PD             | V <sub>IL</sub>  | Do not any electrical connection except to a test pad (suggested).    |  |  |  |  |  |

| 17         | PIN17        | $V_{DDIO}$                   | DI          | PU             | V <sub>IH</sub>  |                                                                       |  |  |  |  |  |

| Digit      | al pins      |                              |             |                |                  |                                                                       |  |  |  |  |  |

| 30         | XTALIN_CLKIN | $V_{DDPLL}$                  | AI          |                |                  | XTAL or Resonator in / CLKIN from external clock source               |  |  |  |  |  |

| 31         | XTALOUT      | $V_{DDPLL}$                  | AO          |                |                  | XTAL or Resonator out                                                 |  |  |  |  |  |

| Anal       | og pins      |                              |             |                |                  |                                                                       |  |  |  |  |  |

| 26         | LED          | V <sub>DDLED</sub>           | AOD         |                | V <sub>LED</sub> | LED/LD driver open-drain output <sup>2</sup>                          |  |  |  |  |  |

| 24         | PIN24        | V <sub>DDLED</sub>           | Al          |                |                  |                                                                       |  |  |  |  |  |

| 20         | PIN20        | $V_{DDA}$                    |             |                |                  | Connect to VSSA with 10 kOhm                                          |  |  |  |  |  |

| 21         | PIN21        | $V_{DDA}$                    |             |                |                  |                                                                       |  |  |  |  |  |

| 43         | PIN43        | $V_{DDPXH}$                  | Al          |                |                  | Do not any electrical connection except to a test pad (suggested).    |  |  |  |  |  |

| 44         | PIN44        | $V_{DDPXH}$                  | Al          |                |                  | Do not any electrical confrection except to a test pad (suggested).   |  |  |  |  |  |

| Pin<br>No. | Pin name          | Supply class V <sub>sc</sub> | Pin<br>type | RESET function | RESET<br>level                          | Description            |  |  |  |  |  |

|------------|-------------------|------------------------------|-------------|----------------|-----------------------------------------|------------------------|--|--|--|--|--|

| Supp       | oly pins, digital |                              |             |                |                                         |                        |  |  |  |  |  |

| 36         | VDDIO1            | $V_{DDIO}$                   | PWR         |                |                                         | IO gupply VDDIO        |  |  |  |  |  |

| 9          | VDDIO2            | V <sub>DDIO</sub>            | PWR         |                |                                         | O supply VDDIO         |  |  |  |  |  |

| 6          | VDD               | $V_{DD}$                     | PWR         |                |                                         | Digital supply VDD     |  |  |  |  |  |

| 33         | VDDPLL            | V <sub>DDPLL</sub>           | PWR         |                |                                         | PLL supply             |  |  |  |  |  |

| 37         | VSSIO1            | V <sub>DDIO</sub>            | GND         |                |                                         |                        |  |  |  |  |  |

| 40         | VSSIO2            | V <sub>DDIO</sub>            | GND         |                |                                         | IO ground VSSIO        |  |  |  |  |  |

| 41         | VSSIO3            | V <sub>DDIO</sub>            | GND         |                |                                         |                        |  |  |  |  |  |

| 39         | VSS               | $V_{DD}$                     | GND         |                |                                         | Digital ground VSS     |  |  |  |  |  |

| 32         | VSSPLL            | $V_{DDPLL}$                  | GND         |                |                                         | PLL ground             |  |  |  |  |  |

| Supp       | oly pins, analog  |                              |             |                |                                         |                        |  |  |  |  |  |

| 22         | VDDA              | $V_{DDA}$                    | PWR         |                |                                         | Analog supply VDDA     |  |  |  |  |  |

| 38         | VBS               | V <sub>BS</sub>              | PWR         |                |                                         | Bias supply            |  |  |  |  |  |

| 23         | VDDPXH            | $V_{DDPXH}$                  | PWR         |                |                                         | Analog 2 supply VDDPXH |  |  |  |  |  |

| 42         | VSSA              | $V_{DDA}$                    | GND         |                |                                         | Analog ground VSSA     |  |  |  |  |  |

| 25         | VSSLED            | V <sub>DDLED</sub>           | GND         |                | LED/LD driver ground (return current) 1 |                        |  |  |  |  |  |

Table 9: Pin list

#### Notes:

- 1 VSSLED is the dedicated, isolated GND pin for the LED/LD return-current from external circuitry. It must be connected to PCB GND plane together with the other VSSA GND pins.

- <sup>2</sup> LED output can be used to drive an external amplifier with an addition of a pull-up resistor. The voltages at LED output must not exceed values in Table 1: Operating conditions and electrical characteristics.

LED2 output is a push-pull driver for delivering symmetric rise/fall times to the external LED driver circuit. LED2 is internally connected to VDDIO/VSSIO supplies. During integration time, all TCMI pins are silent except for DCLK. As a result, LED2 pin will not pick up switching noise from all other TCMI pins. This can be avoided by using gated DCLK mode.

LED and LED2 must not be used simultaneously for driving LED circuits on the PCB. They exhibit different insertion delays and may cause unpredicted distance offset/measurement results.

- <sup>3</sup> RESET pin has a 600kΩ (typical) internal pull-down resistor. Therefore, this pin can be safely connected to a standard GPIO of a CPU which is initially high-Z or open-drain during power-up sequence. Once the SW takes control, it can program this GPIO as output and drive 1 to release the RESET. The internal pull-down can be override by and external 10kΩ pull-up and a series capacitor to build a simple delayed power-on reset for evaluation/qualification purposes.

- <sup>4</sup> I<sup>2</sup>C pins SCL, SDA are according to I<sup>2</sup>C standards. They are I<sup>2</sup>C slave pins which need external pull-up resistors on the PCB. Values of R1 and R2 in the schematics are given only for indicative purposes and must be re-calculated according to the total capacitive load of all I<sup>2</sup>C slave/master devices and operating mode (FM or FM+) of the I<sup>2</sup>C (chapter 13) in the application.

- <sup>5</sup> If HW shutter is not used, connect this pin to GND

'Pin type' in Table 9 defines the following:

■ DI: Digital Input

■ DO: Digital Output

■ DIO: Digital Input/Output (bidirectional)

■ DIOD: Digital Input/Output (bidirectional), open-Drain

■ Al: Analog Input

■ AO: Analog Output

■ AOD: Analog Output, open-Drain

■ PWR: Supply

■ GND: Ground

'RESET function' in Table 9 defines the function of IO pins during reset:

■ I: Input

■ PU: internal Pull-Up

■ PD: internal Pull-Down

■ IPD: Input with internal Pull-Down

'RESET level' in Table 9 defines the level of the IO pins during/after reset (chapter 5.6)

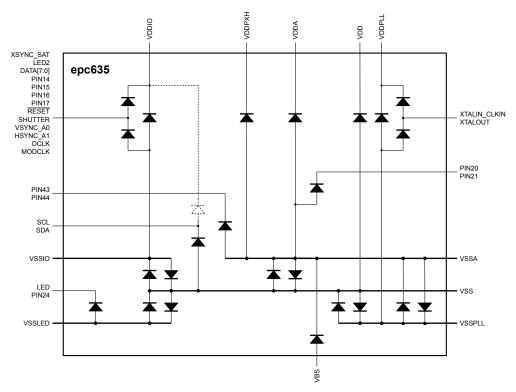

#### 2.3. Power domains and ESD protection

The epc635 chip has internally 7 different power domains and 5 ground references which are interconnected with ESD protection diodes. All pins are also equipped with ESD protection diodes. The diodes have a breakthrough voltage of 0.3V. The designer has to take care that none of these diodes become conductive either at power-up, power-down or normal operation.

Figure 8: I/O pins and ESD protection diagram

## 3. Packaging and layout information

#### 3.1. Mechanical dimensions

#### Top side view 3.200 (0.350)C163 Pin 1 2 34 29 36 35 33 32 (31) (30) 27 26 3.500 (8 bumps with 0.5mm pitch) 37 44 25 R6 1.600 epc635 pixel-field 160 x 60 pixel Pixel size: 20μm x 20μm 0.500 1.200 (3) (38) 43 24 (∅ 0.200) 4.18 +0.00/-0.08 R65 4 23 Top side 5 22 6 (39) 42 21 41 7 (40) 20 (11) (12) (13) (14) (15) (16) (17) 18 (19)-(0.430)0.19 ±0.02 (0.050)0.500 2.700 5.500 (12 bumps with 0.5mm pitch) 6.26 +0.00/-0.08

Figure 9: Mechanical dimensions

#### Notes:

- all measures in mm

- not specified tolerances: ±0.001mm

- Top side is illumination side

#### 3.2. Parasitic light sensitivity (PLS)

CMOS circuits are sensitive to light. That is why they can be used for photo-sensing, imaging, etc. However, if strong light is radiating the chip beside the pixel field, analog and digital circuits can be affected in its function by such parasitic light. It is called parasitic light sensitivity (PLS). A known effect is a shift of the measured distance under strong ambient light.

Imager lenses have always a larger field of view than the pixel-field area. In order to prevent the chip being illuminated by strong ambient light, an opaque aperture should be placed onto the photosensitive side of the imager as shown in Figure 10. The cover shall have a opening of  $3.490 \times 1.490$  mm. With regard to the  $3.200 \times 1.200$  mm pixel-field size, this shield can be assembled with a tolerance of  $\pm 120 \mu m$  in x and y axis. Such a cover can be made by a thin sheet metal stencil like an SMD solder paste printing stencil or by silk screen printing of black color.

#### Top side view Opening: 3.490 ±0.050 Minimize gap to reduce 3.200 Pin 1 stray-light underneath (0.350)the cover 63 2 $^{\circ}$ 36 35 26 34 (33) (32) (31) 30 (29) 28 27 44 25 R6 2 37 200 Photosensitive area 3 38 43 (24) 4.18 +0.00/-0.08 on top side R65 23 дo 5 (22) Opening: 1.490 ±0.050 6 39 42 (21) 40 41 (20) (11) (12) (13) (14) (15) (16) (17) 19 (0.430)2.700 Light absorbing cover Chip size: 6.26 +0.00/-0.08 with opening at pixel-field, nor reflective nor transparent, blocking ambient-light surrounding the pixel-field

Figure 10: Opaque cover for protection against unwanted ambient-light

#### 3.3. Pin1 marking

The following pictures shows the epc635 chip from the bottom side with view to the solder balls. Please note the location of pin 1. It's highly recommended to check the pin 1 location with a vision system during the SMT assembly process.

epc635 chip from the solder ball side

Top right corner from the solder ball side

Figure 11: Pin 1 marking

#### 3.4. Location of the photosensitive area

The photosensitive area is not marked (neither on the front nor on the backside of the IC). As a visible reference, a metal ring of the IC can be used. From the solder ball side it is visible. Also from the front side (photosensitive area) it can be seen with a camera which is sensitive in the near infrared wavelength domain (950 .. 1'150nm).

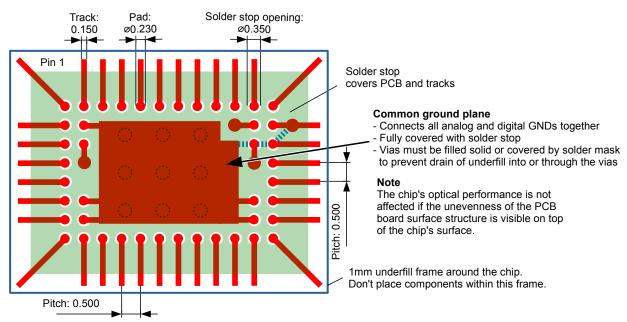

#### 3.5. PCB design and SMD manufacturing process considerations

As the epc635 chip comes in a 44 pin chip scale package with only 50µm thickness, the PCB layout should be made with special care. In addition, careful handling during the assembly process shall be assured in order to avoid mechanical damage during the assembly process. Because the silicon chip is small and light weight compared the solder balls, it is highly recommended that all tracks to the chip should come straight from the side. A symmetrical design is highly recommended to achieve high production yield. The pads and the tracks should also have exactly the same width at least for 1mm from the pad. They shall be covered by a solder resist mask in order to avoid drain of the solder tin alloy to the track.

Figure 12: Recommended PCB layout (all measures in mm)

As shown in Figure 12, a ground plane shall be placed on the top PCB layer underneath the chip. This ground plane acts as a shield to suppress high frequency emission of fast interface signal lines. It is important that this plane is completely flat. Thus, the plane must not be scattered nor divided into sections. It should be rather full-faced and no via should be placed in this plane. Otherwise chip bending might occur. In addition, the ground plane helps to dissipate the heat generated by the chip operation. A good heat dissipation is achieved if there is a temperature increase of the chip under normal operation of max. 20K. The temperature can be read direct from the chip.

Underfill of the components reduces stress to the solder pads caused by e.g. temperature cycling or mechanical bending. Furthermore the

thermal and mechanical fatigue will be reduced and the longterm reliability will be increased. Underfill material and underfill selection is application specific. It shall follow JEDEC-STD JEP150: Stress-Test-Driven Qualification of and Failure Mechanisms Associated with Assembled Solid State Surface- Mount Components. Please also, refer to the application note AN08 Process-Rules CSP Assembly which can be downloaded from the ESPROS Website at www.espros.com, section Downloads. Obeying these recommendations a high manufacturing yield can be achieved.

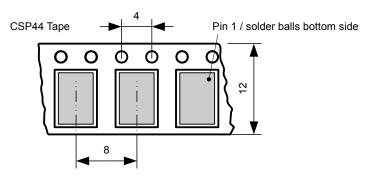

#### 3.6. Tape & reel information

The devices are mounted on embossed tape for automatic placement systems. The tape is wound on 178 mm (7 inch) or 330 mm (13 inch) reels and individually packaged for shipment. General tape-and-reel specification data are available in a separate data sheet and indicate the tape sizes for various package types. Further tape-and-reel specifications can be found in the Electronic Industries Association (EIA) standard 481-1, 481-2, 481-3.

Figure 13: Tape dimensions (all measures in mm)

ESPROS does not guarantee that there are no empty cavities. Thus, the pick-and-place machine should check the presence of a chip during picking.

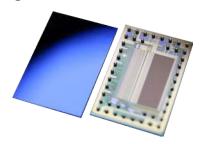

## 4. Ordering information

Figure 14: epc635-CSP44, top and bottom side

Figure 15: epc635 Card Edge Connector Carrier, refer to separate datasheet

| Part Number | Part Name                          | Package              | RoHS compliance |

|-------------|------------------------------------|----------------------|-----------------|

| P100 181    | epc635-CSP44                       | CSP44                | Yes             |

| P100 404    | epc635 Card Edge Connector Carrier | PCB 37.25 x 36.00 mm | Yes             |

Table 10: Ordering Information

#### 4.1. Notes to various chip releases

The supplied chip version can be identified by

- reading the extension -XXX of the part name on the packaging labels or delivery papers: epc635-CSP44-XXX.

- reading the part version register 0xFB: Refer to chapter 15.10

- The latest download code for each chip version is included in the download package for the epc660 Evaluation Kit (see chapter 15.10).

## 5. Hardware implementation

#### 5.1. Typical application diagram

Figure 16: Typical application diagram

Notes: R4 -R15: R1, R20, R21: R18, R19: SHUTTER and XSYNC\_SAT

VSS

Resistor value depends on fast bus decoupling.

Pins need to be connected to corresponding GND. In case of need to testability: use 10k resistors.

Resistor value depends of needed strap function.

Must be at low level until RESET release. Otherwise malfunction occurs.

Connect all VSS as direct as possible using vias to the GND plane underneath the imager

#### 5.2. Application diagram part list

| Part        | Description              | Pin No.                  |                  | Value              |        | Toleranc | Supply                | Comments           |

|-------------|--------------------------|--------------------------|------------------|--------------------|--------|----------|-----------------------|--------------------|

| designator  |                          |                          | Min.             | Тур.               | Max.   | е        | class V <sub>sc</sub> |                    |

| Minimum par | t count:                 |                          |                  |                    |        |          |                       |                    |

| C3          | VDDA                     | 22 - 42                  | 4.7 µF           | 10 µF              |        | ±20%     | V <sub>DDA</sub>      | Ceramic X7R        |

| C4          | VDDA                     | 22 - 42                  |                  | 100 nF             |        | ±20%     | V <sub>DDA</sub>      | Ceramic X7R        |

| C7, C8      | XTAL                     | 30 – 32, 31 - 32         |                  | 18 pF <sup>2</sup> |        | ±20%     | V <sub>DDPLL</sub>    | Ceramic NPO        |

| X1          | XTAL                     | 30 - 31                  |                  | 4 MHz              |        | ±100ppm  | V <sub>DDPLL</sub>    | Quartz / Resonator |

| R4 - R15    | Bus<br>termination       |                          | 0 Ohm            | 10 Ohm             | 33 Ohm | ±20%     | V <sub>DDIO</sub>     | Resistors          |

| R16, R17    | I <sup>2</sup> C pull-up |                          |                  | 1 kOhm             |        | ±20%     | V <sub>DDIO</sub>     | Resistors          |

| R18, R19    | I <sup>2</sup> C address |                          |                  | 10 kOhm            |        | ±20%     | V <sub>DDIO</sub>     | Resistors          |

| Dashed comp | onents improve           | signal quality, power su | upply quality or | testability        |        |          |                       |                    |

| C1          | VDDPXH                   | 23 - 42                  | 1 µF             |                    |        | ±20%     | V <sub>DDPXH</sub>    | Ceramic X7R        |

| C5          | VBS                      | 38 - 42                  | 1 µF             |                    |        | ±20%     | V <sub>BS</sub>       | Ceramic X7R        |

| C9          | VDDPLL                   | 33 - 32                  | 1 µF             |                    |        | ±20%     | V <sub>DDPLL</sub>    | Ceramic X7R        |

| C12         | VDD                      | 6 - 39                   | 1 µF             |                    |        | ±20%     | V <sub>DD</sub>       | Ceramic X7R        |

| C14, C16    | VDDIO                    | 36 – 37, 9 - 40          | 1 µF             |                    |        | ±20%     | V <sub>DDIO</sub>     | Ceramic X7R        |

| C6          | VBS                      | 38 - 42                  |                  | 100 nF             |        | ±20%     | V <sub>BS</sub>       | Ceramic X7R        |

| C22         | VDDPLL                   | 61 - 62                  |                  | 100 nF             |        | ±20%     | V <sub>DDPLL</sub>    | Ceramic X7R        |

| C2          | VDDPXH                   | 22 - 42                  |                  | 10 nF              |        | ±20%     | V <sub>DDPXH</sub>    | Ceramic X7R        |

| C11         | VDD                      | 6 - 39                   |                  | 10 nF              |        | ±20%     | V <sub>DD</sub>       | Ceramic X7R        |

| C13, C15    | VDDIO                    | 36 – 37, 9 - 40          |                  | 10 nF              |        | ±20%     | V <sub>DDIO</sub>     | Ceramic X7R        |

| L1          | VDDPLL                   |                          |                  | 100 nH             |        | ±20%     | V <sub>DDPLL</sub>    | Inductor           |

Table 11: Values of component related to epc635 chip, see Figure 16

#### Notes:

- <sup>1</sup> All other components are application specific.

- <sup>2</sup> The capacitor value has to be selected according the crystal or resonator supplier's recommendation

#### 5.3. Hardware implementation notes

- 1. Decoupling capacitors must be placed as close as possible to their supply pin pair in order to minimise ripple on the supply rails due to fast switching high-speed signals (Table 11).

- 2. +1.8V is used for supplying the digital logic (VDD), the on-chip oscillator OSC and the phase-look-loop PLL (VDDPLL). The digital logic creates some internal switching noise on VDD. When the same supply is shared together with OSC and PLL, their supply wiring must be separated from the digital wires and physically isolated from each other. These supplies are marked in the application diagram as VDD and VDDPLL respectively (Figure 16). A good practice is inserting on the PCB a series inductance of 100nH between them close to the supply source, then creating separate supply islands for both on the board. The XTAL/OSC and PLL are critical parts of the chip which directly impacts the optical system performance (i.e. distance calculation).

- 3. +2.5/3.3V is used for supplying the high-speed IO pins (MODCLK, TCMI and LED2) and the slow I<sup>2</sup>C pins (VDDIO). High speed IO pins toggle at 10/20/40/80MHz during data transfer, hence generating continuously switching noise (much more dominant than the digital noise). Therefore VDDIO supply wires and layers must be carefully designed and isolated in a separate supply island on the PCB. It is not recommend to change this voltage on the fly when the TCMI, LED2 or I<sup>2</sup>C interfaces are running. When the application needs power saving during system idle periods, it can be scaled from +3.3V down to +2.5V only after frame acquisition is stopped and both interfaces are completely inactivated. It can be increased back to +3.3V before re-activating the chip for frame acquisition, accessing I<sup>2</sup>C, LED2 or TCMI interface. Note that, voltage scaling must be done in a controlled way having both application CPU's and epc635's IO voltages at the same time at the same level.

- 4. +5V is used for supplying analog blocks of the chip e.g. pixel-field drivers and ADC readout circuitry. Refer to Figure 16.

- 5. +10V is used for supplying pixel-field circuitry (VDDPXH).

- -10V (VBS) is used for biasing the the pixel-field like reverse-biasing a photodiode. The use of a stable supply source with a low ripple

is recommended. There is no switching or active internal circuit dependent current consumption, except ambient-light dependent leakage current (refer to Table 1, note 8).

- A 4MHz quartz crystal or a ceramic resonator is connected to XTALIN\_CLKIN and XTALOUT pins in order to use internal oscillator OSC as time base for the epc635. The frequency accuracy and stability are directly related to the distance readings. Alternatively an external clock source can be used (chapter 5.4).

- 8. MODCLK input can be used for user controlled/modulated clock. It is used for both the LED driver and the pixel-field demodulator.

- 9. SCL, SDA are I<sup>2</sup>C slave pins which need external pull-up resistors on the PCB (see also VDDIO supply). Values of R16 and R17 are given only for indicative purpose and must be re-calculated according to the total capacitive load of all I<sup>2</sup>C slave/master devices and the operating mode FM or FM+ of the I<sup>2</sup>C (chapter 13) in the application.

- 10. VSYNC\_A0, HSYNC\_A1, XSYNC\_SAT, DATA[11:0], DCLK, high-speed TCMI signals (chapter 6), SHUTTER and RESET control signals toggle in the VDDIO range. To minimize the skew, the high-speed \*SYNC, DATA[11:0], DCLK signals wires must be routed equal in impedance and length less than 10cm long with less than 10mm difference on the PCB. As they are toggling all the time, they can be separated with ground wires on the side adjacent to other signals/supply lines, routed with enough distance from other sensitive signal wires on the board. Series termination resistors R4 ... R15 (10 ... 33Ω) are needed at high-speed outputs to control the slew.

- 11. Optional pull-up resistors R18 and R19 ( $10k\Omega$ ) set initial values of some configuration registers during start up of the chip. Such outputs pins are called strap pins. They are scanned one time immediately after  $\overline{RESET}$  is released (chapter 5.6.3).

- 12. The LED pin is an open-drain LED/LD driver output. When the driver is active (on), the LED/LD on-current flows through the power resistor R3 into the LED pin, through the driver and comes out of the chip on the VSSLED ground pin. The LED pin toggles up to 20MHz or according to the MODCLK clock with a current maximum of 200mA limited by the resistor R3. The number of IR LEDs depends on the level of the LED supply voltage and the turned-on forward voltage drop of the IR LEDs. This signal creates a lot of ground noise. Therefore, VSSLED pin is decoupled from the other analog grounds internally. It must be shorted with the other analog ground pins with a low-ohmic connection as short as possible on the PCB. In this way, there will be minimal voltage differences in the ground planes of the board. The LED supply line must be isolated properly from any analog supply on the PCB to minimize noise coupling from the LED drivers.

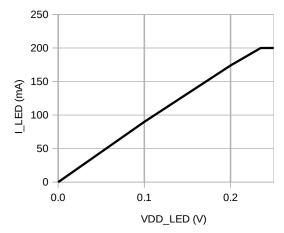

Figure 17: Output characteristic  $I_{\text{LED}}$  versus  $V_{\text{DDLED}}.$  Refer for maximum values of  $V_{\text{DDLED}}$  and  $I_{\text{LED}}$  to Table 1 and Table 2

- 13. The LED2 pin is the alternative push-pull driver providing symmetric rise/fall times to drive external LED driver. It works from the +2.5/+3.3 VDDIO supply (VSSIO GND domain) and swings in the same voltage range like the TCMI pins. LED2 = LOW (approx. 0V) corresponds to LED = OFF (max. output voltage). LED and LED2 pins must not be used at the same time for driving the external illumination. They exhibit different phase delays and this can result wrong distance measurements. None of the TCMI pads toggle during integration time, LED2 pin is the only toggling during integration time and it is not affected from switching noise of others.

- 14. It is recommended having "not connected pins" (PINxx) on test pads available. It helps e.g. to check after assembly for correct orientation of the chip or for short-cuts.

- 15. Pins not listed here have to be connected according Figure 16.

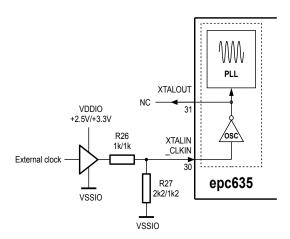

#### 5.4. Clock source

Instead of a crystal, an external 4MHz clock source can be connected to the XTALIN\_CLKIN pin. XTALOUT output pin left unconnected. Input clock signal levels must match V<sub>DDPLL</sub>/V<sub>SSPLL</sub> supply levels (Table 1). If the external clock source comes from the +2.5/3.3V voltage domain, a resistor divider circuit can be deployed to adjust the voltage level according to Figure 18.

Figure 18: Resistor divider to adjust external clock voltage levels to XTALIN CLKIN

**IMPORTANT:** The optical performance of the chip directly depends on the input clock precision/stability. XTALOUT must not be used to drive external loads.

#### 5.5. External modulation MODCLK

The epc635 has for enhanced user applications the possibility to bring an external modulation clock to the chip. The optional MODCLK input can be used to inject a user controlled/modulated clock for both the LED driver and the pixel demodulator, see Figure 19.

Figure 19: The MODCLK signal flow (red marked)

The external MODCLK can be used e.g. in concepts for reliable multi camera applications. It allows to use e.g. frequency-division multiple access (FDMA). In corresponding literature, the details of these concepts are explained in detail.

The user is free to apply any digital waveform up to 80MHz during frame acquisition as external MODCLK signal. Even more, he is also free to use modulations like pseudo-random edge jitter, dithering, etc.

The signal from the MODCLK pin is used instead of the clock generated by the CGU if bit 6 in register 0x80 is set to 1. The effective modulation signal is the MODCLK divided by 4. The unambiguity range and the integration time are in this case based on the MODCLK:

$$[1] d_{UNAMB} = 2*\frac{c}{MODCLK}$$

$$[2] \qquad t_{\text{INT}} \, = \, \frac{\text{reg}(0\text{x85}) + \, 1}{\text{MODCLK}} \cdot [\text{reg}(0\text{xA2:0xA3}) + \, 1] \cdot \text{reg}(0\text{xA0:0xA1})$$

Whereas "c" is the speed of light (300\*106m/s). For more details refer to chapter 9.2.1 and 11.4.

#### 5.6. Supply, reset and start-up options

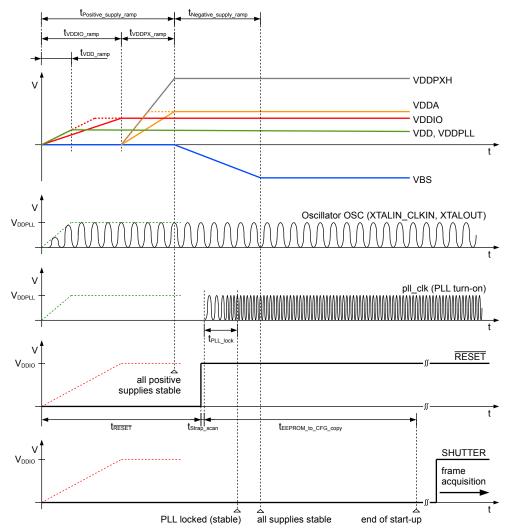

## 5.6.1. Supply voltages and external reset

During power-up, VDD and VDDPLL supplies (Figure 20) must be applied at the same time to the epc635. VDDIO can be applied either at the same time or after VDD and VDDPLL supplies become stable. In a system where VDDIO voltage is connected in parallel to application CPU IO supply pins (see Figure 16), VDD and VDDPLL can be generated by a linear regulator directly from VDDIO supply. In this case, all these three supplies ramp together.

VDDA and VDDPXH supplies must be applied as a second group, after all VDD, VDDPLL and VDDIO supplies become stable.

The negative supply VBS must be applied after all positive supplies reached their rated levels.

Image acquisition shall not start before all supply voltage are at their stable level.

RESET must be kept low while all positive voltages are ramping-up in order to guarantee proper reset of all internal circuits. As soon as rated positive levels are reached, RESET can be set to high. In case of an external clock is applied at XTALIN\_CLKIN instead of a crystal/resonator is used with on-chip OSC, clock must be present before RESET is released.

## IMPORTANT:

- It is possible to shutdown entire supplies for a very low standby current. In that case, first RESET must be driven low, then supplies must be turned off in the reverse order. Refer for details to chapter 11.6

- VDDA and VDDPXH supplies must never kept on while turning off VDD, VDDPLL and VDDIO. Damage to the chip can be the result.

Figure 20: Power-up and reset sequence

### 5.6.2. Start-up (Clock, PLL turn-on and EEPROM copy)

The epc635 starts using either the internal 4MHz oscillator OSC with a crystal/resonator (Figure 16) or an external 4MHz clock, followed by an EEPROM copy sequence in parallel to the PLL turn-on phase. This is the factory default configuration. Several configuration registers are modified by copying the EEPROM content (Figure 49, i.e. overwrite reset values). The EEPROM copy step takes 340µs after the RESET is released.

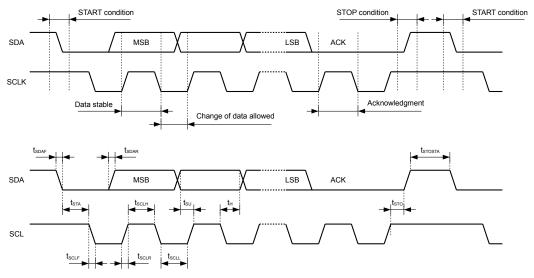

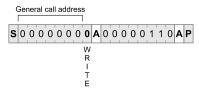

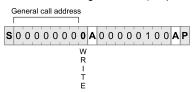

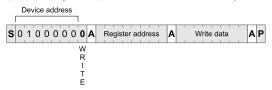

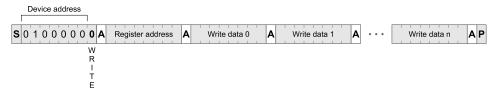

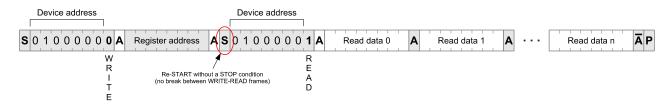

## 5.6.3. Strap pins