# RENESAS

### TW3801

Security Link Over Coax (SLOC) Transmitter

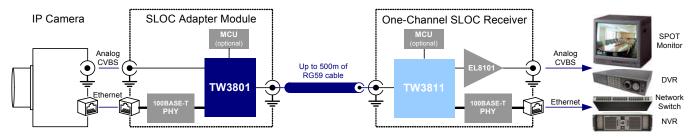

SLOC<sup>™</sup> (Security Link Over Coax) is a transmission protocol for simultaneously transmitting analog CVBS video and digital IP video over a single coaxial cable.

The TW3801 is the transmitting ("camera") end of a SLOC link, combining Ethernet digital video data and analog CVBS video into a single SLOC signal that can be transmitted over 500m of coaxial cable. It can be embedded into a camera or configured as a stand-alone IP+CVBS-to-SLOC converter.

The TW3801 includes an AFE, digital modem, and two Ethernet MII/RMII interfaces. The device accepts an analog CVBS signal and an Ethernet (R)MII signal and encodes it into a SLOC signal.

## **Applications**

- Single-channel SLOC transmitter modem

- Embedded SLOC camera modem

# DATASHEET

FN8283 Rev.1.00 November 29, 2012

### **Features**

- Simultaneous transmission of IP video data and analog CVBS video over up to 500m of RG59 coaxial cable

- Analog CVBS video preview support

- Proprietary adaptive analog equalizer for extending the reach of CVBS video

- Proprietary SLOC-based IP DVR detection

- Creates a full-duplex 100BASE-T digital link

- 36Mbps downlink speed from TW3801 to TW3811

- 4Mbps uplink for SLOC compliance

- Ethernet MAC MII/RMII interface for interfacing to Camera ISPs

- Ethernet PHY MII/RMII interface for interfacing to Ethernet PHY chip

- I<sup>2</sup>C 2-wire control interface

- Integrated PLL with 25MHz crystal interface

- 1.8V, 3.3V supplies

- 100-TQFP (12mmx12mm) Package

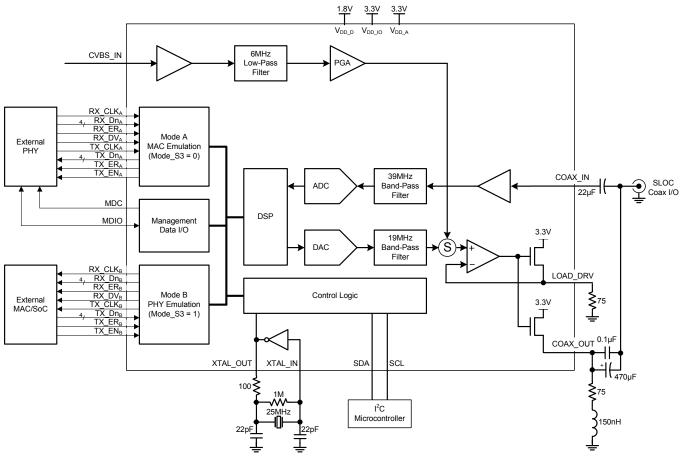

### **Application Block Diagram**

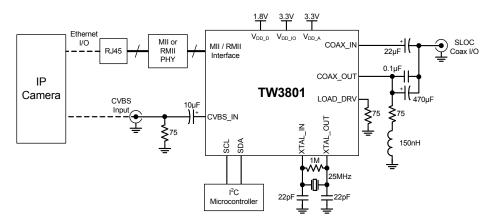

## **Simplified Application Schematic**

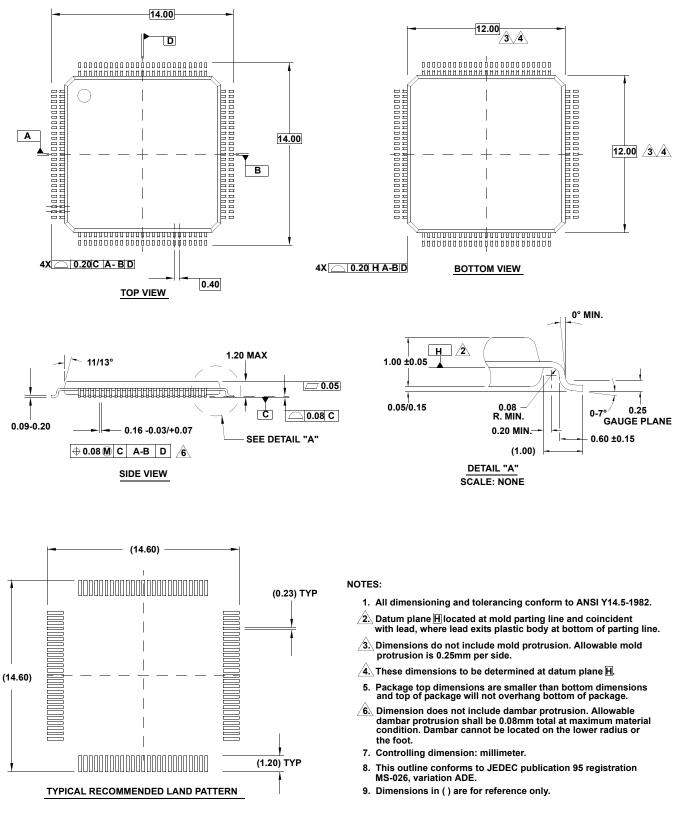

### **Ordering Information**

| PART<br>NUMBER                | PART<br>MARKING  | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|-------------------------------|------------------|--------------------|----------------------|----------------|

| TW3801-TC1-CR (Notes 1, 2, 3) | TW3801 TC1-CR    | -40 to +85         | 100 Ld TQFP          | Q100.12X12A    |

| TW3801-TC1-CR-EVAL            | Evaluation Board |                    |                      |                |

NOTES:

1. Add "T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For more information on MSL please see tech brief  $\underline{\text{TB363}}.$

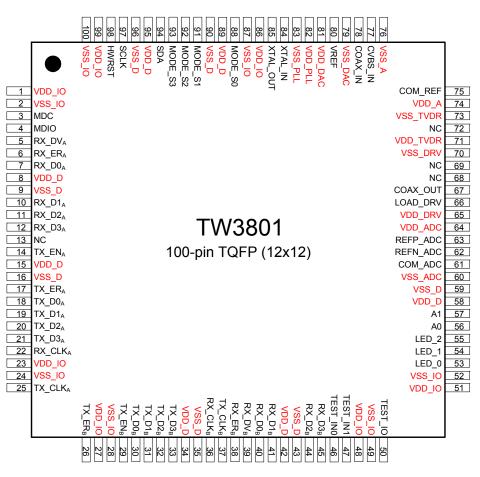

# **Pin Configuration**

TW3801 (100 LD TQFP) TOP VIEW

# **Pin Descriptions**

| SYMBOL    | NUMBER                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SU  | PPLY AND GP                      | ROUND                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDD_IO    | 1, 23, 27,<br>48,<br>51, 86, 99  | 3.3V Power supply for all digital I/Os. Connect to the 3.3V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass each supply pin to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                              |

| VSS_IO    | 2, 24, 28,<br>49,<br>52, 87, 100 | Digital I/O Ground. Connect each pin to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                 |

| VDD_D     | 8, 15, 34,<br>42<br>58, 89, 95   | 1.8V Power supply for core digital logic. Connect to the 1.8V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass each supply pin to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                            |

| VSS_D     | 9, 16, 35,<br>43<br>59, 90, 96   | Digital Core Ground. Connect each pin to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                |

| VDD_ADC   | 64                               | 3.3V Power supply for internal ADC. Connect to the 3.3V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass to ground plane with a $0.1\mu$ F capacitor.                                                                                                                                                                                                                                             |

| VSS_ADC   | 60                               | ADC Analog Ground. Connect to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                           |

| VDD_DRV   | 65                               | 3.3V Power supply for analog output stages. Connect to the 3.3V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                          |

| VSS_DRV   | 70                               | Analog Output Driver Ground. Connect to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                 |

| VDD_A     | 71, 74                           | 3.3V Power supply for internal analog. Connect to the 3.3V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass each pin to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                      |

| VSS_A     | 73, 76                           | Analog Ground. Connect each pin to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                      |

| VDD_DAC   | 81                               | 3.3V Power supply for DAC. Connect to the 3.3V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass to ground plane with a $0.1\mu$ F capacitor.                                                                                                                                                                                                                                                      |

| VSS_DAC   | 79                               | DAC Analog Ground. Connect to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                           |

| VDD_PLL   | 82                               | 3.3V Power supply for PLL. Connect to the 3.3V supply through a MI0805K601R-10 (or equivalent) ferrite bead and bypass to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                                           |

| VSS_PLL   | 83                               | PLL Analog Ground. Connect to ground plane using the shortest/lowest inductance path possible.                                                                                                                                                                                                                                                                                                                           |

| ANALOG    |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADC_COM   | 61                               | Analog Output. Internally Generated ADC Reference Voltage. Common mode reference voltage for ADC. Bypass to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                                                         |

| ADC_REFN  | 62                               | Analog Output. Internally Generated ADC Reference Voltage. Negative differential reference voltage for ADC. Bypass to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                                               |

| ADC_ REFP | 63                               | Analog Output. Internally Generated ADC Reference Voltage. Positive differential reference voltage for ADC. Bypass to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                                               |

| LOAD_DRV  | 66                               | Analog Output. Driver Reference Load. The signal on this pin generates the output current that is mirrored onto the COAX_OUT pin. Connect to a 75 $\Omega$ , 1% resistor to ground. To maximize stability, ensure that this signal is isolated from the COAX_OUT signal. This can be achieved by placing the resistor on the bottom side of PCB and routing the trace in the opposite direction from the COAX_OUT trace. |

| COAX_OUT  | 67                               | Analog Output. Coaxial TX Output. This pin is a high impedance current source output. Terminate to VSS_A with a 75 $\Omega$ 1% resistor in series with a 150nH inductor. AC-couple per Figure 1 to SLOC I/O connector.                                                                                                                                                                                                   |

| COM_REF   | 75                               | Analog Output. Internally Generated Reference Voltage. Bypass to ground plane with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                    |

| CVBS_IN   | 77                               | Analog Input. Standard 1V <sub>PP</sub> CVBS video signal from camera or other source.                                                                                                                                                                                                                                                                                                                                   |

| COAX_IN   | 78                               | Analog Input. Coaxial RX Input.                                                                                                                                                                                                                                                                                                                                                                                          |

| VREF      | 80                               | Analog Input. Externally Generated Reference Voltage. Voltage reference input for internal DAC. Connect to a 1.2VDC source. This voltage can be generated from AVD_DAC with a 6.34k/3.65k resistor divider and 0.1µF bypass capacitor. Refer to reference schematic for more details.                                                                                                                                    |

# Pin Descriptions (Continued)

| SYMBOL              | NUMBER        | DESCRIPTION                                                                                                                                                                                                                                                                       |  |  |  |

|---------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| XTAL_IN             | 84            | Analog Input. Crystal Input. Connect to one end of a 25MHz crystal with 22pF capacitor and 1MΩ feedback resistor. Refer to reference schematic for more details.                                                                                                                  |  |  |  |

| XTAL_OUT            | 85            | Analog Output. Crystal Output. Connect to other end of a 25MHz crystal with 22pF capacitor and 1MΩ feedback resistor. Refer to reference schematic for more details.                                                                                                              |  |  |  |

| MII/RMII DI         | GITAL INTER   | FACE                                                                                                                                                                                                                                                                              |  |  |  |

| MDC                 | 3             | Digital Output. MDC is the management data clock reference for the serial management interface. The maximum frequency supported is 3.125MHz.                                                                                                                                      |  |  |  |

| MDIO                | 4             | Digital I/O. MDIO is the management data. MDIO transfers data synchronously with MDC.                                                                                                                                                                                             |  |  |  |

| The followin        | ng pins are u | sed to connect TW3801 to an external Ethernet PHY using the A Interface pins, when MODE_S3 = 0.                                                                                                                                                                                   |  |  |  |

| RX_DV <sub>A</sub>  | 5             | Digital Input with internal 57k pull-down resistor to VSS_IO. Receive Data Valid.<br>O: The incoming data on the RX_Dn <sub>A</sub> is not ready to be latched.<br>1: The incoming data on the RX_Dn <sub>A</sub> pins is valid and should be latched using RX_CLK <sub>A</sub> . |  |  |  |

| RX_ER <sub>A</sub>  | 6             | Digital Input with internal 57k pull-down resistor to VSS_IO. Receive Error.<br>0: The incoming data on the RX_Dn <sub>A</sub> pins is valid.<br>1: The incoming data on the RX_Dn <sub>A</sub> pins has an error.                                                                |  |  |  |

| RX_D0 <sub>A</sub>  | 7             | Digital Input with internal 57k pull-down resistor to VSS_IO. Receive Data bit 0.                                                                                                                                                                                                 |  |  |  |

| RX_D1 <sub>A</sub>  | 10            | Digital Input with internal 57k pull-down resistor to VSS_IO. Receive Data bit 1.                                                                                                                                                                                                 |  |  |  |

| RX_D2 <sub>A</sub>  | 11            | Digital Input with internal 57k pull-down resistor to VSS_IO. Receive Data bit 2. (MII mode only)                                                                                                                                                                                 |  |  |  |

| RX_D3 <sub>A</sub>  | 12            | Digital Input with internal 57k pull-down resistor to VSS_IO. Receive Data bit 3. (MII mode only)                                                                                                                                                                                 |  |  |  |

| TX_EN <sub>A</sub>  | 14            | Digital Output. Transmit Enable.<br>O: Data on the TX_Dn <sub>A</sub> pins is not ready.<br>1: Data on the TX_Dn <sub>A</sub> pins is valid and should be latched using TX_CLK <sub>A</sub> .                                                                                     |  |  |  |

| TX_ER <sub>A</sub>  | 17            | Digital Output. Transmit Error<br>This pin is normally low. When in "Passthrough Mode", this pin duplicates the state of TX_ER <sub>B</sub> .                                                                                                                                     |  |  |  |

| TX_D0 <sub>A</sub>  | 18            | Digital Output. Transmit Data bit 0.                                                                                                                                                                                                                                              |  |  |  |

| TX_D1 <sub>A</sub>  | 19            | Digital Output. Transmit Data bit 1.                                                                                                                                                                                                                                              |  |  |  |

| TX_D2 <sub>A</sub>  | 20            | Digital Output. Transmit Data bit 2. (MII mode only)                                                                                                                                                                                                                              |  |  |  |

| TX_D3 <sub>A</sub>  | 21            | Digital Output. Transmit Data bit 3. (MII mode only)                                                                                                                                                                                                                              |  |  |  |

| RX_CLK <sub>A</sub> | 22            | Digital Input with internal $57k\Omega$ pull-down resistor to VSS_IO. Receive Data Clock signal.                                                                                                                                                                                  |  |  |  |

| TX_CLK <sub>A</sub> | 25            | Digital Input with internal 57kΩ pull-down resistor to VSS_IO. Transmit Data Clock signal. MII: 25MHz. RMII: 50MHz.                                                                                                                                                               |  |  |  |

| The followin        | ng pins are u | sed to connect TW3801 to an external MAC/SoC using the B Interface pins, when MODE_S3 = 1.                                                                                                                                                                                        |  |  |  |

| TX_ER <sub>B</sub>  | 26            | Digital Input with internal 57kΩ pull-down resistor to VSS_IO. Receive Error. This bit is synchronous to TX_CLK <sub>B</sub> .<br>O: The incoming data on the TX_Dn <sub>B</sub> pins is valid.<br>1: The incoming data on the TX_Dn <sub>B</sub> pins has an error.              |  |  |  |

| TX_EN <sub>B</sub>  | 29            | Digital Input with internal 57kΩ pull-down resistor to VSS_IO. Transmit Enable.<br>0: Data on the TX_Dn <sub>B</sub> pins is not ready.<br>1: Data on the TX_Dn <sub>B</sub> pins is valid and should be latched using TX_CLK <sub>B</sub> .                                      |  |  |  |

| TX_D0 <sub>B</sub>  | 30            | Digital Input with internal $57k\Omega$ pull-down resistor to VSS_IO. Transmit Data bit 0.                                                                                                                                                                                        |  |  |  |

| TX_D1 <sub>B</sub>  | 31            | Digital Input with internal $57K\Omega$ pull-down resistor to VSS_10. Transmit Data bit 0.                                                                                                                                                                                        |  |  |  |

| TX_D2B              | 32            | Digital Input with internal $57k\Omega$ pull-down resistor to VSS_I0. Transmit Data bit 2. (MII mode only)                                                                                                                                                                        |  |  |  |

| TX_D3 <sub>B</sub>  | 33            | Digital Input with internal 57k $\Omega$ pull-down resistor to VSS_I0. Transmit Data bit 3. (MII mode only)                                                                                                                                                                       |  |  |  |

| RX_CLK <sub>B</sub> | 36            | Digital Output. Receive Data Clock signal.                                                                                                                                                                                                                                        |  |  |  |

| TX_CLKB             | 37            | Digital Output. Transmit Data Clock signal.                                                                                                                                                                                                                                       |  |  |  |

| RX_ER <sub>B</sub>  | 38            | Digital Output. Receiver Error.<br>This pin is normally low. When in "Passthrough Mode", this pin duplicates the state of RX_ER <sub>A</sub> .                                                                                                                                    |  |  |  |

# Pin Descriptions (Continued)

| SYMBOL                         | NUMBER                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RX_DV <sub>B</sub>             | 39                    | Digital Output. Receive Data Valid.<br>0: The data on the RX_Dn <sub>B</sub> is not ready to be latched.<br>1: The data on the RX_Dn <sub>B</sub> pins is valid and should be latched using RX_CLK <sub>B</sub> .                                                                                                                                                                                                                                                                         |  |  |  |  |

| RX_D0 <sub>B</sub>             | 40                    | Digital Output. Receive Data bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| RX_D1 <sub>B</sub>             | 41                    | Digital Output. Receive Data bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| RX_D2 <sub>B</sub>             | 44                    | Digital Output. Receive Data bit 2. (MII mode only)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| RX_D3 <sub>B</sub>             | 45                    | Digital Output. Receive Data bit 3. (MII mode only)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| MISCELLAN                      | EOUS                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| MODE_S0                        | 88                    | Digital Inputs. TW3801 Transmission Speed Selection. Status latched at power-on/reset. Only valid if register 0x01[0] = 0. If                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| MODE_S1                        | 91                    | register 0x01[0] = 1, Transmission Speed is set by register 0x0A.<br><b>MODE_S1 = 0, MODE_S0 = 0: 36Mbps</b><br>MODE_S1 = 0, MODE_S0 = 1: 28Mbps<br>MODE_S1 = 1, MODE_S0 = 0: 25Mbps<br>MODE_S1 = 1, MODE_S0 = 1: 21Mbps<br>Note: <b>This bitrate should always be set to 36Mbps for maximum compatibility with all cameras.</b> A lower bitrate will increase<br>the chances of a buffer overflow without significantly increasing cable connection distance                             |  |  |  |  |

| MODE_S2                        | 92                    | Digital Input. Tie to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| MODE_S3                        | 93                    | Digital Input. MII Interface Selection. Status latched on reset/power-on. Only valid if register 0x01[0] = 0. If register 0x01[0] = 1, Interface Mode is set by register 0x01.<br>0: Ethernet PHY connect with SLOC by MII <sub>A</sub> data bus.<br>1: SOC connect with SLOC by MII <sub>B</sub> data bus.                                                                                                                                                                               |  |  |  |  |

| LED_0 /<br>MII_Mode_<br>Select | 53                    | Digital I/O with internal 57kΩ pull-up resistor to VDD_IO (active low). As an output during normal operation, a low output on LED_0 indicates the SLOC data link is connected.<br>If register 0x01[0] = 0, the state of this pin is latched at power-on/reset to set MII or RMII operation. If register 0x01[0] = 1, MII or RMII operation is determined by register 0x01[5].<br>>2.0V: MII mode (default if pin is floating)<br><0.8V: RMII mode (10kΩ pull-down resistor or equivalent) |  |  |  |  |

| LED_1                          | 54                    | Digital I/O with internal 57kΩ pull-up resistor to VDD_IO (active low). A low output on LED_1 indicates MII Transmit Data is v<br>For correct TW3801 operation, this pin must be left floating or be held to a voltage >2.0V during power on/reset.                                                                                                                                                                                                                                       |  |  |  |  |

| LED_2                          | 55                    | Digital I/O with internal 57kΩ pull-up resistor to VDD_IO (active low). A low output on LED_2, indicates MII Receive Data is valid. For correct TW3801 operation, this pin must be left floating or be held to a voltage >2.0V during power on/reset.                                                                                                                                                                                                                                     |  |  |  |  |

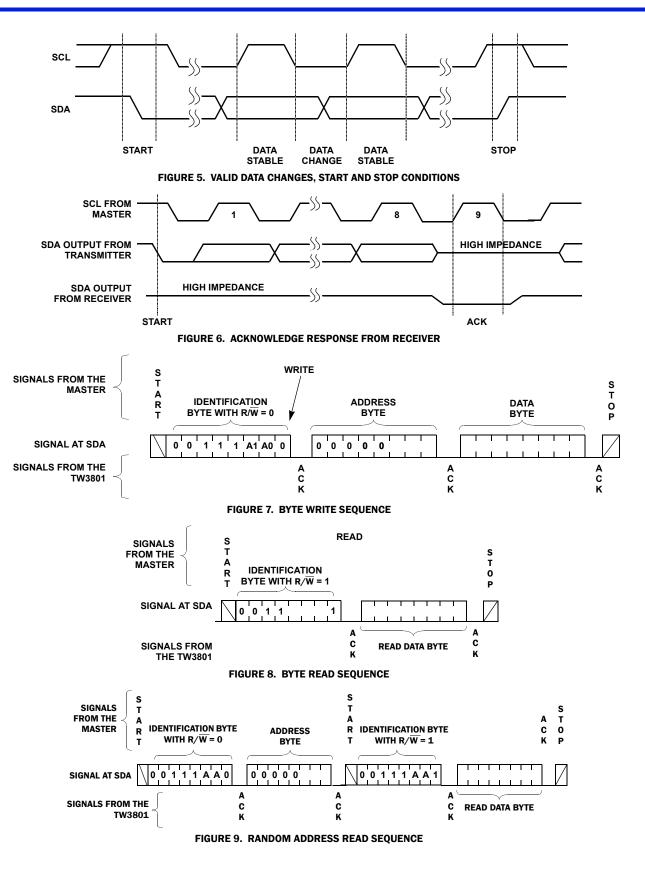

| SDA                            | 94                    | Digital I/O with open-drain. I <sup>2</sup> C Serial Data.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SCLK                           | 97                    | Digital Input. I <sup>2</sup> C Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| AO                             | 56                    | Digital Input with internal 57k $\Omega$ pull-down resistor to VSS_IO. TW3801 I <sup>2</sup> C Address Bit 0.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| A1                             | 57                    | Digital Input with internal 57k $\Omega$ pull-down resistor to VSS_IO. TW3801 I <sup>2</sup> C Address Bit 1.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| HWRST                          | 98                    | Digital I/O with internal 57k $\Omega$ pull-up resistor to VDD_IO (active low). Active LOW system reset. To reset the TW3801, hold low (<0.8V) for at least 12 cycles of the 25MHz crystal clock after the oscillator has stabilized (crystal oscillator may take up to 1ms to start up and stabilize after power is applied).                                                                                                                                                            |  |  |  |  |

| TEST_INO,<br>TEST_IN1          | 46, 47                | Digital Input with internal $57k\Omega$ pull-down resistor to VSS_IO. Do not connect anything to this pin.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TEST_IO                        | 50                    | Digital I/O with internal 57k $\Omega$ pull-down resistor to VDD_IO. Do not connect anything to this pin.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| NC                             | 13, 68, 69,<br>72, 77 | Do Not Connect. Do not connect anything to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

#### **Absolute Maximum Ratings**

| VDD_D Digital Core Supply Voltage Range                |

|--------------------------------------------------------|

| VDD_IO Digital I/O Supply Voltage Range0.5V to 4.3V    |

| VDD_A=VDD_ADC=VDD_DRV=VDD_TVDR=VDD_DAC=VDD_PLL         |

| Analog Supply Voltage Range                            |

| Voltage on Digital I/O Pins0.5V to 5.5V                |

| Voltage on Analog I/O Pins0.5V to 4.3V                 |

| ESD Rating                                             |

| Human Body Model (Tested per JESD22-A114E) 2kV         |

| Machine Model (Tested per JESD22-A115-A) 200V          |

| CDM Model (Tested per JESD22-C101)                     |

| Latch Up (Tested per JESD-78B; Class 2, Level A)±100mA |

#### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------------------|----------------------|------------------------|

| 100 Ld TQFP Package (Notes 4, 5)          | 41                   | 7                      |

| Maximum Junction Temperature (Plastic Pac | kage)                | +125°C                 |

| Storage Temperature Range                 | 65                   | 5°C to +150°C          |

| Pb-Free Reflow Profile                    |                      | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp            |                        |

| Pb-Free Reflow Profile (*)                |                      | see <u>TB487</u>       |

| *Peak temperature during solder reflow +  | 235°C max            |                        |

#### **Recommended Operating Conditions**

| Temperature40                          | °C to +85°C  |

|----------------------------------------|--------------|

| VDD_D Digital Supply Voltage           | 1.6V to 2.0V |

| VDD_IO Digital Supply Voltage          | 3.0V to 3.6V |

| VDD_ADC=VDD_DRV=VDD_TVDR=VDD_A=VDD_DAC |              |

| =VDD_PLL Analog Supply Voltage         | 3.0V to 3.6V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 5. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

| Electrical Specifications vdd_d = 1.8V, vdd_l/0 = 3.3V, vdd_adc = vdd_drv = vdd_tvdr = vdd_a = vdd_dac = vdd_pll = 3.3V | , |

|-------------------------------------------------------------------------------------------------------------------------|---|

| T <sub>A</sub> = +25°C. Boldface limits apply over the operating temperature range, -40°C to +85°C. (Note 6)            |   |

| SYMBOL                     | PARAMETER                                                   | TEST CONDITIONS                                                                                    | MIN | TYP  | MAX | UNITS            |

|----------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|-----|------------------|

| POWER SU                   | PPLY                                                        |                                                                                                    |     |      |     |                  |

| VDD_D                      | Digital Core Supply Voltage Range                           |                                                                                                    | 1.6 | 1.8  | 2.0 | v                |

| IDD_D                      | VDD_D Supply Current                                        |                                                                                                    |     | 160  |     | mA               |

| VDD_I0                     | Digital I/O Supply Voltage Range                            |                                                                                                    | 3.0 | 3.3  | 3.6 | v                |

| IDD_IO                     | VDD_IO Supply Current                                       |                                                                                                    |     | 7    |     | mA               |

| VDD_A                      | Analog Supply Voltage Range                                 |                                                                                                    | 3.0 | 3.3  | 3.6 | v                |

| IDD_A                      | VDD_A Supply Current                                        |                                                                                                    |     | 135  |     | mA               |

| PD                         | Total Power Dissipation                                     |                                                                                                    |     | 760  |     | mW               |

| COAX I/O                   | 1                                                           |                                                                                                    | 1   | 1 1  |     |                  |

|                            | COAX_IN Input Capacitance                                   |                                                                                                    |     | 9    |     | pF               |

| VCXO COAX_OUT Output Level |                                                             | RL = 37.5Ω, 15 - 24MHz,<br>transmitting IP Data and CVBS                                           |     | 0.5  |     | V <sub>P-P</sub> |

|                            | Return Loss                                                 | RL = 75Ω, 6 - 42MHz                                                                                |     | -10  |     | dB               |

| CVBS OUTP                  | UT                                                          |                                                                                                    |     | 1    |     |                  |

| Vin                        | Video Input Range                                           | 100IRE White Pattern; AC-coupled to CVBS_IN                                                        |     | 1    | 1.2 | Vpp              |

|                            | Luminance Non-Linearity                                     | 1M COAX, IP data on, VIN = TW3801<br>CVBS_IN, 5 step pattern,<br>VOUT = TW3811 CVBS_OUT            |     | 5    |     | %                |

|                            | Chroma Non-Linear Gain Distortion<br>(reference for 40IRE)  | 1M COAX, IP data on, VIN = TW3801<br>CVBS_IN, Modulated pedestal signal,<br>VOUT = TW3811 CVBS_OUT |     | -1.8 |     | %                |

|                            | Chroma Non-Linear Phase Distortion<br>(Reference for 40IRE) | 1M COAX, IP data on, VIN = TW3801<br>CVBS_IN, Modulated pedestal signal,<br>VOUT = TW3811 CVBS_OUT |     | -2   |     | ۰                |

| SYMBOL            | PARAMETER                                                             | TEST CONDITIONS                                                                                          | MIN  | TYP  | MAX | UNITS |

|-------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| DG                | Differential Gain                                                     | 1M COAX, IP data on, VIN = TW3801<br>CVBS_IN, Modulated ramp,<br>VOUT = TW3811 CVBS_OUT                  |      | 4    |     | %     |

| DP                | Differential Phase                                                    | 1M COAX, IP data on, VIN = TW3801<br>CVBS_IN, Modulated ramp,<br>VOUT = TW3811 CVBS_OUT                  |      | -0.6 |     | 0     |

| BW                | Video Bandwidth (-3dB)                                                | 1M COAX, IP data on, VIN = TW3801<br>CVBS_IN, VOUT = TW3811 CVBS_OUT                                     |      | 5.4  |     | MHz   |

| SNR               | Video Signal-To-Noise Ratio                                           | 1M COAX, IP data on, Unweighted filter,<br>VIN = TW3801, 100IRE White pattern,<br>VOUT = TW3811 CVBS_OUT |      | 52.5 |     | dB    |

| DIGITAL I/O       | )                                                                     | · · · ·                                                                                                  |      | -H   |     |       |

| DIGITAL INF       | PUTS                                                                  |                                                                                                          |      |      |     |       |

| VIH               | Input High Voltage (TTL)                                              |                                                                                                          | 2.0  |      | 5.5 | v     |

| VIL               | Input Low Voltage (TTL)                                               |                                                                                                          | -0.3 |      | 0.8 | v     |

| IL                | Input Leakage Current (Inputs Without Pull-up Or Pull-down Resistors) | VIN = 3.3V and OV                                                                                        |      |      | ±10 | μA    |

| CIN               | Input Capacitance                                                     |                                                                                                          |      | 6    |     | pF    |

| DIGITAL OU        | TPUTS                                                                 | · · · ·                                                                                                  |      |      |     |       |

| VOH               | Output High Voltage                                                   |                                                                                                          | 2.4  |      |     | v     |

| VOL               | Output Low Voltage                                                    |                                                                                                          |      |      | 0.4 | v     |

| EXTERNAL          | CRYSTAL/REFERENCE CLOCK REQUIRE                                       | MENTS (per MII/RMII standard)                                                                            |      |      |     |       |

| f <sub>XTAL</sub> | External Crystal/Clock Frequency                                      | 25                                                                                                       |      |      | MHz |       |

| XTALTOL           | External Crystal/Clock Tolerance                                      |                                                                                                          |      |      | ±50 | ppm   |

**Electrical Specifications**  $VDD_D = 1.8V$ ,  $VDD_1/0 = 3.3V$ ,  $VDD_ADC = VDD_DRV = VDD_TVDR = VDD_A = VDD_DAC = VDD_PLL = 3.3V$ ,  $T_A = +25^{\circ}C$ . Boldface limits apply over the operating temperature range, -40°C to +85°C. (Note 6) (Continued)

NOTES:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

# **Register Listing**

| ADDRESS | REGISTER (DEFAULT VALUE)          | BIT(S) | FUNCTION NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------------------------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00    | Reset and Device ID (0x80)        | 0      | Soft Reset          | Soft chip reset. Write a 1 to reset. Will set itself to 0 when rese<br>is complete. Does not reset register settings.                                                                                                                                                                                                                                    |

|         |                                   | 4:1    | Reserved            | Set to 0 when writing this register.                                                                                                                                                                                                                                                                                                                     |

|         |                                   | 7:5    | Revision ID         | 100: C1 Revision                                                                                                                                                                                                                                                                                                                                         |

| 0x01    | SLOC Configuration (0x60)         | 0      | Config Source       | 0: Configuration determined by external pins (default).<br>1: Configuration determined by registers 0x01 and 0x0A.                                                                                                                                                                                                                                       |

|         |                                   | 1      | Operational Mode    | 0: Transmitter (TW3801) (default)<br>1: Receiver (TW3811)                                                                                                                                                                                                                                                                                                |

|         |                                   | 2      | Reserved            | Set to 0 when writing this register.                                                                                                                                                                                                                                                                                                                     |

|         |                                   | 4:3    | I/O Configuration   | <ul> <li>00: MII<sub>A</sub> bus enabled. TW3801 acts like a MAC and is connected to a PHY (default).</li> <li>01: MII<sub>B</sub> bus enabled. TW3801 acts like a PHY and is connected to a MAC.</li> <li>02: Both MII<sub>A</sub> and MII<sub>B</sub> buses are connected together (passthrough mode) (experimental).</li> <li>03: Reserved</li> </ul> |

|         |                                   | 5      | Interface Selection | 0: RMII<br>1: MII (default)                                                                                                                                                                                                                                                                                                                              |

|         |                                   | 6      | RMII Clock Source   | 0: An internally-generated 50MHz RMII reference clock is<br>available on the TEST_IO pin.<br>1: An externally-supplied 50MHz RMII reference clock must b<br>supplied to TX_CLK <sub>A</sub> pin for RMII operation (default).                                                                                                                            |

|         |                                   | 7      | Reserved            | Set to 0 when writing this register.                                                                                                                                                                                                                                                                                                                     |

| 0x0A    | Transmit Link Datarate (0x00)     | 4:0    | Tx Link Datarate    | When 0x01[0] = 0, the transmit datarate is determined by the MODE_S0 and MODE_S1 pins.                                                                                                                                                                                                                                                                   |

|         |                                   |        |                     | When 0x01[0]=1, this register sets the bitrate of data<br>transmitted from the TW3801 to the TW3811. This bitrate<br>should always be set to 36Mbps for maximum compatibility<br>with all cameras. A lower bitrate will increase the chances of<br>a buffer overflow without significantly increasing cable<br>connection distance.                      |

|         |                                   |        |                     | The speed selection choices below are shown for historical<br>continuity. Use 0x13 for all new designs.<br>0x0C: 25Mbps<br>0x0A: 21Mbps<br>0x11: 28Mbps<br><b>0x13: 36Mbps</b><br>0x00 - 0x0B, 0x10, 0x12, 0x14-0x1F: Reserved                                                                                                                           |

|         |                                   | 7:5    | Reserved            | Set to 0 when writing this register.                                                                                                                                                                                                                                                                                                                     |

| 0x14    | Receive Link Datarate (Read Only) | 4:0    | Rx Link Datarate    | When a SLOC link is established, this register indicates the birate of the data from the TW3811 to the TW3801.<br>0x02: 3Mbps<br>0x04: 4Mbps<br>0x11: 9Mbps<br>0x13: 11Mbps                                                                                                                                                                              |

|         |                                   | 7:5    | Reserved            |                                                                                                                                                                                                                                                                                                                                                          |

| 0x19    | CVBS Channel Gain (0x00)          | 6:0    | CVBS Gain           | 0x00: Minimum CVBS Gain (default)                                                                                                                                                                                                                                                                                                                        |

# Register Listing (Continued)

| ADDRESS | REGISTER (DEFAULT VALUE)                                         | BIT(S) | FUNCTION NAME                | DESCRIPTION                                                                                                                                                                                                                                                   |

|---------|------------------------------------------------------------------|--------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1E    | MDIO 1 (0x00)                                                    | 0      | MDIO Register Read           | MDIO register read command. Specify MDIO register address<br>in 0x1F, apply read command (set this bit), clear read<br>command (clear this bit), then read MDIO register value in<br>registers 0x22 and 0x23.                                                 |

|         |                                                                  | 1      | MDIO Register Write          | MDIO register write command. Specify MDIO register address<br>in 0x1F, write MDIO register data into registers 0x20 and<br>0x21, apply write command (set this bit), then clear write<br>command (clear this bit).                                            |

|         |                                                                  | 3:2    | Reserved                     | Set to 0 when writing this register.                                                                                                                                                                                                                          |

|         |                                                                  | 6:4    | MDIO PHY Address             | These are the 3 MSB bits of MDIO PHY address that SLOC<br>needs to match with Ethernet-PHY chip's PHY address. The 2<br>lower LSB = $\{A1,A0\}$ , where A1 and A0 are set by the logic<br>levels of the external A1 and A0 pins.                              |

|         |                                                                  | 7      | Reserved                     | Set to 0 when writing this register.                                                                                                                                                                                                                          |

| 0x1F    | MDIO 2 (0x00)                                                    | 4:0    | MDIO Register R/W<br>Address |                                                                                                                                                                                                                                                               |

|         |                                                                  | 7:5    | Reserved                     | Set to 0 when writing this register.                                                                                                                                                                                                                          |

| 0x20    | MDIO OUT DATA LSB (0x00)                                         | 7:0    | MDIO OUT (LSB)               | Lower 8 bits of 16 bit word to be transmitted.                                                                                                                                                                                                                |

| 0x21    | MDIO OUT DATA MSB (0x00)                                         | 7:0    | MDIO OUT (MSB)               | Upper 8 bits of 16 bit word to be transmitted.                                                                                                                                                                                                                |

| 0x22    | MDIO IN DATA LSB (Read Only)                                     | 7:0    | MDIO IN (LSB)                | Lower 8 bits of 16 bit word received.                                                                                                                                                                                                                         |

| 0x23    | MDIO IN DATA MSB (Read Only)                                     | 7:0    | MDIO IN (MSB)                | Upper 8 bits of 16 bit word received.                                                                                                                                                                                                                         |

| 0x26    | SLOC Control (0x00)                                              | 0      | Control Overwrite            | 0: Automatic System Control. SLOC Tx and Rx automatically<br>enabled if "Ethernet PHY Connected" bit is set (44[3] = 1).<br>1: Manual System Control. SLOC Tx and Rx enabled based on<br>bits 3 and 4 of this register.                                       |

|         |                                                                  | 2:1    | Reserved                     | Set to 11b when writing this register.                                                                                                                                                                                                                        |

|         |                                                                  | 3      | SLOC Transmitter<br>Enable   | 0: Disabled.<br>1: Enabled.                                                                                                                                                                                                                                   |

|         |                                                                  | 4      | SLOC Receiver<br>Enable      | 0: Disabled.<br>1: Enabled.                                                                                                                                                                                                                                   |

|         |                                                                  | 7:5    | Reserved                     | Set to 0 when writing this register.                                                                                                                                                                                                                          |

| 0x27    | Reed-Solomon Segment Monitor Count<br>(0x00)                     | 7:0    | Reed-Solomon<br>Segments     | The number of segments to monitor error count at Reed-Solomon Decoder. Actual segment number is $65536 \times [$ the value in this register]. After setting this register, check status bit Error Count Updated (0x43, bit[0]) for completion of error count. |

|         |                                                                  |        |                              | A value of 0 in this register will disable the Reed-Solomon<br>Error Counter and reset Error Count Updated (0x43 bit[0]) to 0.                                                                                                                                |

| 0x40    | Reed-Solomon Error Count 7:0<br>(Read Only, default is 0xFF)     | 7:0    | Error Count 7:0              | Bits 7:0 of the 24-bit Reed-Solomon Error Count.<br>Registers 0x40 - 0x42 = 0xFFFFFF whenever 0x43[0] = 0.                                                                                                                                                    |

| 0x41    | Reed-Solomon Error Count 15:8<br>(Read Only, default is 0xFF)    | 7:0    | Error Count 15:8             | Bits 15:8 of the 24-bit Reed-Solomon Error Count.<br>Registers 0x40 - 0x42 = 0xFFFFFF whenever 0x43[0] = 0.                                                                                                                                                   |

| 0x42    | Reed-Solomon Error Count 23:16<br>(Read Only, default is 0xFF)   | 7:0    | Error Count 23:16            | Bits 23:16 of the 24-bit Reed-Solomon Error Count.<br>Registers 0x40 - 0x42 = 0xFFFFFF whenever 0x43[0] = 0.                                                                                                                                                  |

| 0x43    | Reed-Solomon Error Count Updated<br>(Read Only, default is 0x00) | 0      | Error Count Updated          | 0: Reed-Solomon Error Count is not valid.<br>1: Reed-Solomon Error Count value has been updated.<br>To clear this bit, write a 0 to register 0x27.                                                                                                            |

|         |                                                                  | 7:1    | Reserved                     |                                                                                                                                                                                                                                                               |

## **Register Listing**(Continued)

| ADDRESS | REGISTER (DEFAULT VALUE) | BIT(S) | FUNCTION NAME             | DESCRIPTION                                                                       |

|---------|--------------------------|--------|---------------------------|-----------------------------------------------------------------------------------|

| 0x44    | Status Bits (Read Only)  | 2:0    | Reserved                  |                                                                                   |

|         |                          | 3      | Ethernet PHY<br>Connected | 0: Ethernet PHY reporting no link.<br>1: Ethernet PHY reporting link established. |

|         |                          | 4      | SLOC Rx Locked            | 0: SLOC carrier not detected.<br>1: SLOC carrier detected and locked.             |

|         |                          | 5      | SLOC Data Active          | 0: SLOC data link not established.<br>1: SLOC data link established.              |

|         |                          | 7:6    | Reserved                  |                                                                                   |

# **Functional Description**

### **Functional Overview**

The TW3801 block diagram is shown in Figure 1.

FIGURE 1. TW3801 INTERNAL BLOCK DIAGRAM

## **Applications Information**

### **External Interfacing**

The TW3801 uses the standard Ethernet MII or RMII interface to communicate with Ethernet PHYs (in Mode A, where the TW3801 emulates a MAC) or Ethernet MACs (in Mode B, where the TW3801 emulates a PHY).

The TW3801 supports the 100BASE-T communication mode. 10BASE-T communication is not supported, so both ends of a SLOC system must be connected to 100BASE-T devices.

### **Management Interface**

The management interface is a serial bus used in Mode A to communicate between the TW3801 and the external PHY it is connected to.

SLOC as a MDIO master will check Ethernet PHY linkup status periodically by sending out MDC and MDIO signals. It requires SLOC to have MDIO PHY address to sync with the Ethernet-PHY chip's PHY address [4:0]. The SLOC MDIO PHY address can be programmed at {Reg0x1E[6:4], A1,A0}, where A1 and A0 are set by the logic levels of the external A1 and A0 pins.

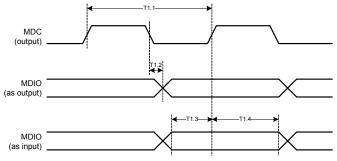

#### Management Data I/O Timing

| PARAMETER         | DESCRIPTION                | MIN | TYP                 | MAX | UNIT |

|-------------------|----------------------------|-----|---------------------|-----|------|

| T1.1              | MDC Clock Cycle Time       |     | 8/f <sub>XTAL</sub> |     | ns   |

| DC <sub>MDC</sub> | MDC Clock Duty Cycle       | 45  |                     | 55  | %    |

| T1.2              | MDIO Data Output Delay     |     |                     | 5   | ns   |

| T1.3              | MDIO Data Input Setup Time | 10  |                     |     | ns   |

| T1.4              | MDIO Data Input Hold Time  | 10  |                     |     | ns   |

### **Setting the MDIO PHY Address**

The TW3801's MDIO PHY address is abcde (in binary), where:

- a = register 0x1E bit 6

- b = register 0x1E bit 5

- c = register 0x1E bit 4

- d = state of A1 (pin 57)

- e = state of A0 (pin 56)

The TW3801's MDIO PHY address should be set to match the PHY address of the device it is connected to.

### **MII Interface**

Ethernet data is transferred via the MII or RMII interface. The TW3801 is designed to work with any PHY with an MII interface, and has been tested with the following PHYs in MII mode:

- 88E1111 (Marvell)

- IP101A (IC+)

- LAN8710 (SMSC)

- RTL8201EL (Realtek)

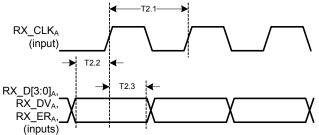

#### **MII Mode A (MAC Emulation) Input Timing**

| PARAMETER             | DESCRIPTION                    | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------|-----|-----|-----|------|

| T2.1                  | RX_CLK <sub>A</sub> Period     |     | 40  |     | ns   |

| DC <sub>RX_CLKA</sub> | RX_CLK <sub>A</sub> Duty Cycle | 20  |     | 80  | %    |

| T2.2                  | Data Setup Time                | 10  |     |     | ns   |

| T2.3                  | Data Hold Time                 | 10  |     |     | ns   |

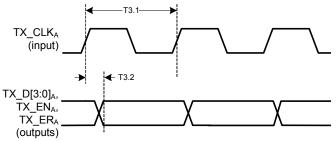

#### **MII Mode A (MAC Emulation) Output Timing**

#### TABLE 3. MII MODE A (MAC EMULATION) OUTPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------|-----|-----|-----|------|

| T3.1                  | TX_CLK <sub>A</sub> Period     |     | 40  |     | ns   |

| DC <sub>TX_CLKA</sub> | TX_CLK <sub>A</sub> Duty Cycle | 20  |     | 80  | %    |

| T3.2                  | Output Data Valid Delay        |     |     | 14  | ns   |

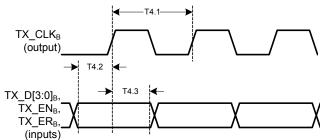

### **MII Mode B (PHY Emulation) Input Timing**

#### TABLE 4. MII MODE B (PHY EMULATION) INPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP                 | MAX | UNIT |

|-----------------------|--------------------------------|-----|---------------------|-----|------|

| T4.1                  | TX_CLK <sub>B</sub> Period     |     | 1/f <sub>XTAL</sub> |     | ns   |

| DC <sub>TX_CLKB</sub> | TX_CLK <sub>B</sub> Duty Cycle | 45  |                     | 55  | %    |

| T4.2                  | Data Setup Time                | 10  |                     |     | ns   |

| T4.3                  | Data Hold Time                 | 10  |                     |     | ns   |

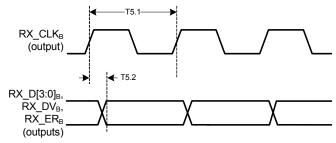

### **MII Mode B (PHY Emulation) Output Timing**

#### TABLE 5. MII MODE B (PHY EMULATION) OUTPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP                 | MAX | UNIT |

|-----------------------|--------------------------------|-----|---------------------|-----|------|

| T5.1                  | RX_CLK <sub>B</sub> Period     |     | 1/f <sub>XTAL</sub> |     | ns   |

| DC <sub>RX_CLKB</sub> | RX_CLK <sub>B</sub> Duty Cycle | 45  |                     | 55  | %    |

| T5.2                  | Output Data Valid Delay        |     |                     | 5   | ns   |

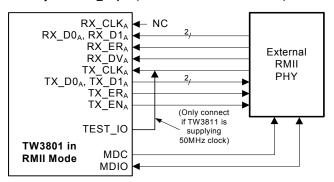

#### **RMII Interface**

Ethernet data is transferred via the MII or RMII interface. The TW3801 is designed to work with any PHY with an RMII interface, and has been tested with the IP101A (IC+) PHY in RMII mode. The 50MHz RMII clock may be supplied by the external PHY or by the TEST\_IO pin (when RMII Clock Source = 1).

FIGURE 2. OPTIONAL USE OF TEST\_IO AS RMII CLOCK SOURCE

#### **RMII Mode A (MAC Emulation) Input Timing**

#### TABLE 6. RMII MODE A (MAC EMULATION) INPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------|-----|-----|-----|------|

| T6.1                  | TX_CLK <sub>A</sub> Period     |     | 20  |     | ns   |

| DC <sub>TX_CLKA</sub> | TX_CLK <sub>A</sub> Duty Cycle | 20  |     | 80  | %    |

| T6.2                  | Data Setup Time                | 4   |     |     | ns   |

| T6.3                  | Data Hold Time                 | 2   |     |     | ns   |

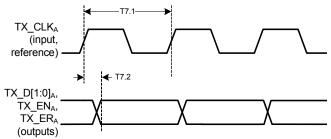

#### **RMII Mode A (MAC Emulation) Output Timing**

#### TABLE 7. RMII MODE A (MAC EMULATION) OUTPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------|-----|-----|-----|------|

| T7.1                  | TX_CLK <sub>A</sub> Period     |     | 20  |     | ns   |

| DC <sub>TX_CLKA</sub> | TX_CLK <sub>A</sub> Duty Cycle | 20  |     | 80  | %    |

| T7.2                  | Output Data Valid Delay        |     |     | 14  | ns   |

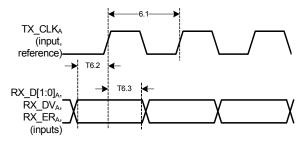

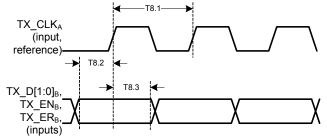

#### **RMII Mode B (PHY Emulation) Input Timing**

#### TABLE 8. RMII MODE B (PHY EMULATION) INPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------|-----|-----|-----|------|

| T8.1                  | TX_CLK <sub>A</sub> Period     |     | 20  |     | ns   |

| DC <sub>TX_CLKA</sub> | TX_CLK <sub>A</sub> Duty Cycle | 20  |     | 80  | %    |

| T8.2                  | Data Setup Time                | 4   |     |     | ns   |

| T8.3                  | Data Hold Time                 | 2   |     |     | ns   |

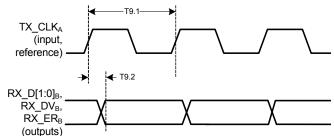

#### **RMII Mode B (PHY Emulation) Output Timing**

#### TABLE 9. RMII MODE B (PHY EMULATION) OUTPUT TIMING

| PARAMETER             | DESCRIPTION                    | MIN | TYP                 | MAX | UNIT |

|-----------------------|--------------------------------|-----|---------------------|-----|------|

| T9.1                  | TX_CLK <sub>A</sub> Period     |     | 1/f <sub>XTAL</sub> |     | ns   |

| DC <sub>TX_CLKA</sub> | TX_CLK <sub>A</sub> Duty Cycle | 45  |                     | 55  | %    |

| T9.2                  | Output Data Valid Delay        |     |                     | 14  | ns   |

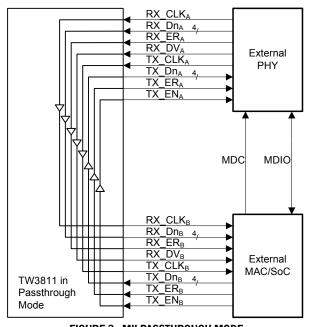

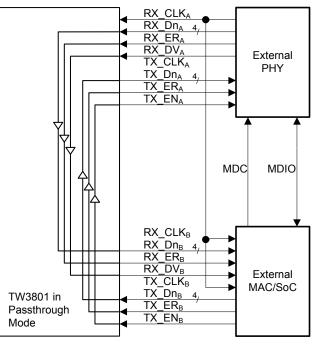

#### **MII Passthrough Mode**

Passthrough mode connects all the MII Inputs to all the MII outputs through the TW3801's internal drivers (Figure 3). Passthrough mode is enabled by setting Register 0x01[4:3] to 10b. Passthrough mode introduces a small delay between the input and output signals.

FIGURE 3. MII PASSTHROUGH MODE

#### TABLE 10. MII PASSTHROUGH MODE TIMING

| PARAMETER    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MIN | TYP | MAX | UNIT |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|