# 6 GHz Selectable Fanout Buffer with Internal Termination

# **Features**

- → Input Clock Frequency up to 6 GHz Typical

- → 5 pairs of differential LVPECL/ CML outputs

- $\rightarrow$  Low additive jitter, < 0.05ps (max)

- → Input CLK accepts: LVPECL, LVDS, CML, SSTL input level

- → Output to Output skew: <20ps

- → Operating Temperature:  $-40^{\circ}$ C to  $85^{\circ}$ C

- → Power supply:  $3.3V \pm 10\%$  or  $2.5V \pm 5\%$

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- → For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

- → Packaging (Pb-free & Green)

- 24-pin TQFN available

# Description

The PI6C59S6005 is a high-performance low-skew 1-to-5 LVPECL fanout buffer. The CLK inputs accept LVPECL, LVDS, CML and SSTL signals. PI6C59S6005 is ideal for clock distribution applications such as providing fanout for low noise Diodes oscillators.

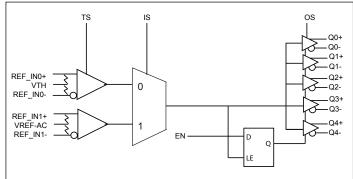

# **Block Diagram**

Notes:

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

<sup>2.</sup> See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

<sup>3.</sup> Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

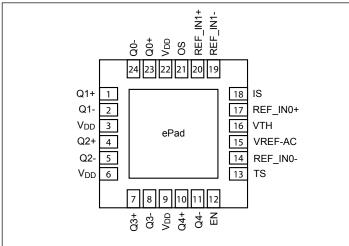

# **Pin Configuration**

# **Pin Description**

|        | N               | T      | Description                                                                                                                                                                                              |

|--------|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #  | Name            | Туре   | Description                                                                                                                                                                                              |

| 1, 2   | Q1+, Q1-        | Output | Differential output pair, LVPECL/ CML interface level.                                                                                                                                                   |

| 3      | V <sub>DD</sub> | Power  | Power Supply                                                                                                                                                                                             |

| 4, 5   | Q2+, Q2-        | Output | Differential output pair, LVPECL/ CML interface level.                                                                                                                                                   |

| 6      | V <sub>DD</sub> | Power  | Power Supply                                                                                                                                                                                             |

| 7, 8   | Q3+, Q3-        | Output | Differential output pair, LVPECL/ CML interface level.                                                                                                                                                   |

| 9      | V <sub>DD</sub> | Power  | Power Supply                                                                                                                                                                                             |

| 10, 11 | Q4+, Q4-        | Output | Differential output pair, LVPECL/ CML interface level.                                                                                                                                                   |

| 12     | EN              | Input  | Synchronous Output Enable, with internal $25k\Omega$ pull-up resistor. Logic high selects enable, and logic low selects disable.                                                                         |

| 13     | TS              | Input  | Type Select. Input type select between high and low bias voltage at $V_{TH}$ , with internal 25k $\Omega$ pull-up resistor. Logic high selects high bias voltage, and logic low selects low bias voltage |

| 14     | REF_IN0-        | Input  | Differential IN negative input, AC and DC coupled                                                                                                                                                        |

| 15     | VREF-AC         | Output | Reference Voltage: Biased to $V_{DD}$ -1.4V. Used when AC coupling inputs                                                                                                                                |

| 16     | V <sub>TH</sub> | Output | Differential pair IN0 center-tap node                                                                                                                                                                    |

| 17     | REF_IN0+        | Input  | Differential IN positive input, AC and DC coupled                                                                                                                                                        |

| 18     | IS              | Input  | Input Select. Select between IN0 and IN1, with internal $25k\Omega$ pull-up resistor. Logic high selects IN1, and logic low selects IN0.                                                                 |

| 19     | REF_IN1-        | Input  | Differential IN1 negative input, AC coupled only                                                                                                                                                         |

| 20     | REF_IN1+        | Input  | Differential IN1 positive input, AC coupled only                                                                                                                                                         |

| 21     | OS              | Input  | Output Select. Output type select between LVPECL/ CML, with internal $25k\Omega$ pull-up resistor. Logic high selects LVPECL, and logic low selects CML.                                                 |

| 22     | V <sub>DD</sub> | Power  | Power Supply                                                                                                                                                                                             |

| 23, 24 | Q0+, Q0-        | Output | Differential output pair, LVPECL/ CML interface level.                                                                                                                                                   |

| _      | ePad            | Power  | Connect to GND                                                                                                                                                                                           |

# **Functional Description**

| REF_IN+ | REF_IN- | EN | Q+ | Q- |

|---------|---------|----|----|----|

| 0       | 1       | 1  | 0  | 1  |

| 1       | 0       | 1  | 1  | 0  |

| X       | X       | 0  | 0  | 1  |

# **Select Pin Descriptions**

| OS | Q+     | Q-     |

|----|--------|--------|

| 0  | CML    | CML    |

| 1  | LVPECL | LVPECl |

| NC | LVPECL | LVPECL |

# Maximum Ratings (Over operating free-air temperature range)

|                                      | Note:                   |

|--------------------------------------|-------------------------|

| Storage Temperature65°C to+155°C     | Stresses g              |

| Junction TemperatureMax. 125°C       | may cause<br>only and   |

| 3.3V Core Supply Voltage0.5 to +4.6V | condition               |

| ESD Protection (HBM)                 | specificat<br>condition |

greater than those listed under MAXIMUM RATINGS se permanent damage to the device. This is a stress rating l functional operation of the device at these or any other ns above those indicated in the operational sections of this ation is not implied. Exposure to absolute maximum rating ons for extended periods may affect reliability.

# **DC Characteristics**

| Symbol               | Parameter                                             | Conditions                   | Min                   | Тур                   | Max                   | Units |

|----------------------|-------------------------------------------------------|------------------------------|-----------------------|-----------------------|-----------------------|-------|

| V                    | Come Derven Summity Volte ge                          |                              | 3.0                   |                       | 3.6                   | V     |

| V <sub>DD</sub>      | Core Power Supply Voltage                             |                              | 2.375                 |                       | 2.625                 | V     |

| T <sub>A</sub>       | Ambient Temperature                                   |                              | -40                   |                       | 85                    | °С    |

| I <sub>DD</sub>      | Power Supply Current                                  | No load, max V <sub>DD</sub> |                       |                       | 170                   | mA    |

| R <sub>DIFF_IN</sub> | Differential Input Resistance<br>(REF_IN+ to REF_IN-) |                              | 90                    | 100                   | 110                   | Ω     |

| V <sub>IH</sub>      | Input High Voltage                                    |                              | 1.2                   |                       | V <sub>DD</sub> - 0.9 | V     |

| V <sub>IL</sub>      | Input Low Voltage                                     |                              | 0.4                   |                       | V <sub>IH</sub> - 0.1 | V     |

| V <sub>IN</sub>      | Input Voltage Swing                                   |                              | 0.1                   |                       | 1.7                   | V     |

| V <sub>DIFF_IN</sub> | Differential Input Swing                              |                              | 0.2                   |                       |                       | V     |

| V <sub>REF-AC</sub>  | Output Reference Voltage                              |                              | V <sub>DD</sub> -1.50 | V <sub>DD</sub> -1.30 | V <sub>DD</sub> -1.15 | V     |

# **LVCMOS/LVTTL DC Characteristics** (TA = -40°C to +85°C, $V_{DD}$ = 2.5V ±5% to 3.3V ±10%)

| Symbol          | Parameter          | Conditions | Min  | Тур | Max             | Units |

|-----------------|--------------------|------------|------|-----|-----------------|-------|

| V <sub>IH</sub> | Input High Voltage |            | 2.0  |     | V <sub>DD</sub> | V     |

| V <sub>IL</sub> | Input Low Voltage  |            | 0    |     | 0.8             | v     |

| I <sub>IH</sub> | Input High Current |            | -125 |     | 20              | μA    |

| I <sub>IL</sub> | Input Low Current  |            | -300 |     |                 | μA    |

| Symbol                | Parameter                          | Conditions                      | Min                   | Тур                        | Max                   | Units |

|-----------------------|------------------------------------|---------------------------------|-----------------------|----------------------------|-----------------------|-------|

| V <sub>OH</sub>       | Output High Voltage                | $V_{DD} = 3.3V \pm 10\%$        | V <sub>DD</sub> -1.4  | V <sub>DD</sub><br>-1.145  | V <sub>DD</sub> -0.76 | V     |

|                       |                                    | $V_{DD} = 2.5V \pm 5\%$         | V <sub>DD</sub> - 1.1 | V <sub>DD</sub> -0.95      | V <sub>DD</sub> -0.8  | V     |

| V <sub>OL</sub>       | Output Low Voltage                 | $V_{DD} = 3.3V \pm 10\%$        | V <sub>DD</sub> -2.1  | V <sub>DD</sub> -<br>1.945 | V <sub>DD</sub> -1.6  | V     |

|                       |                                    | $V_{DD} = 2.5 V \pm 5\%$        | V <sub>DD</sub> -1.75 | V <sub>DD</sub> -1.6       | V <sub>DD</sub> -1.4  | V     |

| V                     | Output Voltage Suring              | Single Ended, $V_{DD} = 3.3V$   | ==0                   | 000                        |                       | m V   |

| V <sub>OUT</sub>      | Output Voltage Swing               | Single Ended, $V_{DD} = 2.5V$   | 550                   | 800                        |                       | mV    |

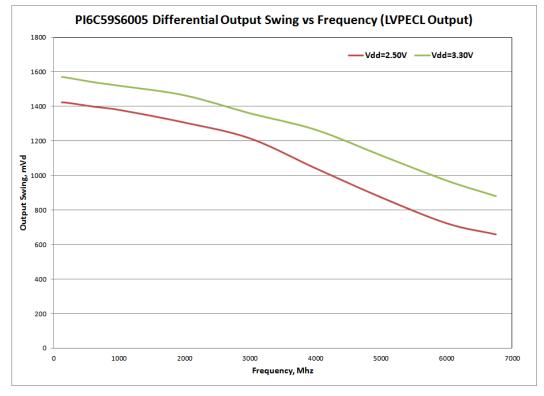

| V <sub>DIFF_OUT</sub> | Differential Output Valtera Suring | $V_{DD}$ = 3.3V, f $\leq$ 5 GHz | 1100                  | 1600                       |                       | m V   |

|                       | Differential Output Voltage Swing  | $V_{DD}$ = 2.5V, f $\leq$ 3 GHz | 1100                  | 1000                       |                       | mV    |

# **LVPECL DC Characteristics** ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , $V_{DD} = 3.3V \pm 10\%$ , 2.5V $\pm 5\%$ )

# CML DC Characteristics (T<sub>A</sub> = -40°C to +85°C, V<sub>DD</sub> = $3.3V \pm 10\%$ , 2.5V $\pm 5\%$ )

| Symbol                     | Parameter                         | Conditions    | Min | Тур | Max | Units |

|----------------------------|-----------------------------------|---------------|-----|-----|-----|-------|

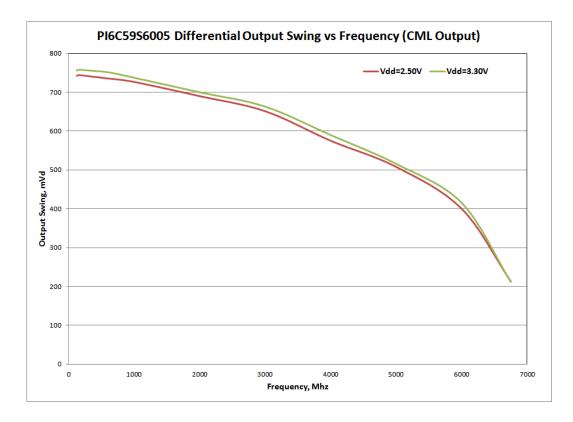

| V <sub>OUT</sub>           | Output Voltage Swing              | Single Ended  | 325 | 400 |     | mV    |

| V <sub>DIFF</sub> _<br>out | Output Differential Voltage Swing | $f \leq 3GHz$ | 650 | 800 |     | mV    |

# AC Characteristics (T<sub>A</sub> = -40°C to +85°C, $V_{DD}$ = 3.3V ±10%, 2.5V ±5%)

| Symbol                         | Parameter                            | Conditions                                                     | Min | Тур | Max | Units |

|--------------------------------|--------------------------------------|----------------------------------------------------------------|-----|-----|-----|-------|

| f <sub>max</sub>               | Output Frequency                     |                                                                |     | 6   |     | GHz   |

| t <sub>pd</sub>                | Propagation Delay <sup>(1)</sup>     |                                                                |     |     | 400 | ps    |

| т.                             | Output-to-output Skew <sup>(2)</sup> |                                                                |     |     | 20  | ps    |

| T <sub>sk</sub>                | Device to Device skew                |                                                                |     |     | 200 | ps    |

| Ts                             | Setup time                           |                                                                |     | 240 |     | ps    |

| T <sub>h</sub>                 | Hold time                            |                                                                |     | 240 |     | ps    |

| t <sub>r</sub> /t <sub>f</sub> | Output Rise/Fall time                | 20% - 80%                                                      | 40  |     | 90  | ps    |

| t .                            | Output duty avala                    | $f \le 1 \text{ GHz}$                                          | 48  |     | 52  | %     |

| t <sub>odc</sub>               | Output duty cycle                    | $1 \text{ GHz} \le f < 6 \text{ GHz}$                          | 40  |     | 60  | %     |

| tj                             | Puffor additive iitter DMS           | 156.25MHz with 12KHz to<br>20MHz integration range<br>(LVPECL) |     | 10  |     | fs    |

|                                | Buffer additive jitter RMS           | 156.25MHz with 12KHz to<br>20MHz integration range<br>(CML)    |     | 40  |     | fs    |

#### Notes:

1. Measured from the differential input to the differential output crossing point

2. Defined as skew between outputs at the same supply voltage and with equal loads. Measured at the output differential crossing point

# **Output Swing vs Frequency**

May 2021

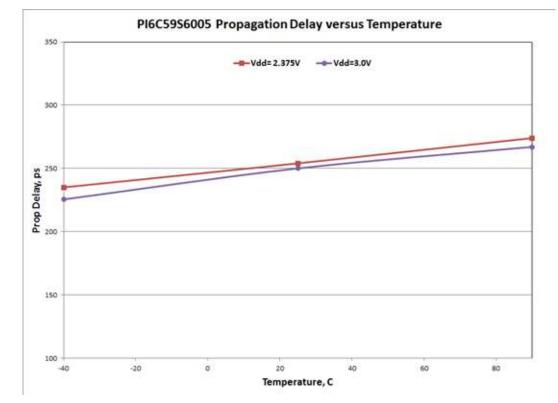

# **Average Propagation Delay vs Temperature**

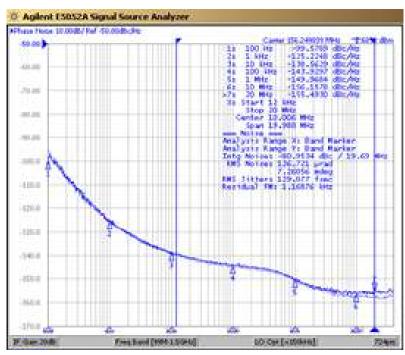

# **Phase Noise Plots**

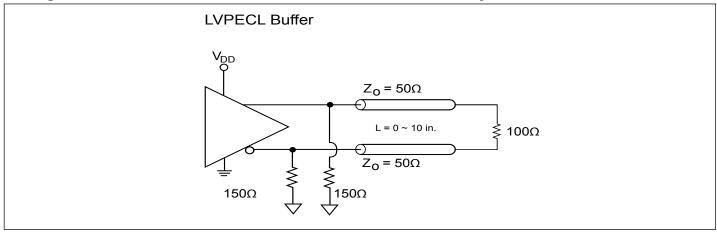

# **Configuration Test Load Board Termination for LVPECL Outputs**

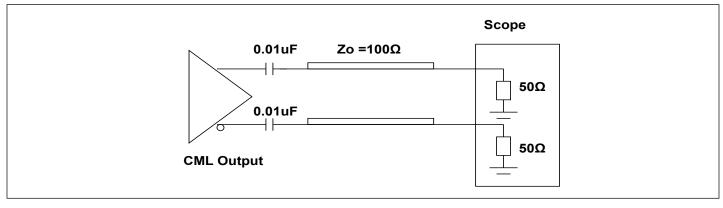

# **Configuration Test Load Board Termination for CML Outputs**

# **Thermal Information**

| Symbol | Description                            | Condition |           |

|--------|----------------------------------------|-----------|-----------|

| ΘJA    | Junction-to-ambient thermal resistance | Still air | 54.4 °C/W |

| ΘJC    | Junction-to-case thermal resistance    |           | 40.8 °C/W |

Note: Thermal data accounts for ePad being connected to GND.

# Application Information Suggest for Unused Inputs and Outputs

# **LVCMOS Input Control Pins**

It is suggested to add pull-up=4.7k and pull-down=1k for LVCMOS pins even though they have internal pull-up/down but with much higher value (>=50k) for higher design reliability.

#### **REF\_IN=/ REF\_IN- Input Pins**

They can be left floating if unused. For added reliability, connect  $1k\Omega$  to GND.

# Outputs

All unused outputs are suggested to be left open and not connected to any trace. This can lower the IC power supply power.

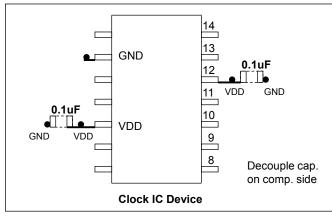

# Power Decoupling & Routing

# VDD Pin Decoupling

As general design rule, each VDD pin must have a 0.1uF decoupling capacitor. For better decoupling, 1uF can be used. Locating the decoupling capacitor on the component side has better decoupling filter result as shown in Fig. 1.

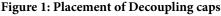

# **Differential Clock Trace Routing**

Always route differential signals symmetrically, make sure there is enough keep-out space to the adjacent trace (>20mil.). In 156.25MHz XO drives IC example, it is better routing differential trace on component side as the following Fig. 2.

Figure 2: IC Routing for XO Drive

Clock timing is the most important component in PCB design, so its trace routing must be planned and routed as a first priority in manual routing. Some good practices are to use minimum vias (total trace vias count <4), use independent layers with good reference plane and keep other signal traces away from clock traces (>20mil.) etc.

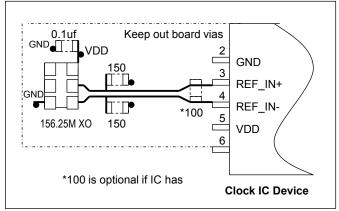

# **LVPECL and LVDS Input Interface**

# LVPECL and LVDS DC Input

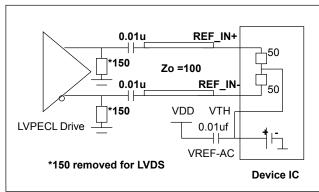

LVPECL and LVDS clock input to this IC is connected as shown in the Fig. 3.

#### Figure 3: LVPECL/ LVDS Input

#### LVPECL and LVDS AC Input

LVPECL and LVDS AC drive to this clock IC requires the use of the VREF-AC output to recover the DC bias for the IC input as shown in Fig. 4

Figure 4: LVPECL/ LVDS AC Coupled Input

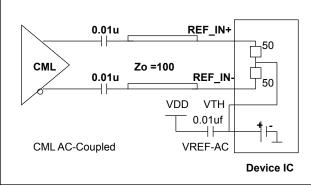

#### CML AC-Coupled Input

CML AC-coupled drive requires a connection to VREF-AC as shown in Fig. 5. The CML DC drive is not recommended as different vendors have different CML DC voltage level. CML is mostly used in AC coupled drive configuration for data and clock signals.

Figure 5: CML AC-Coupled Input Interface

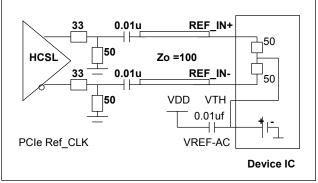

# **HCSL AC-Coupled Input**

It is suggested to use AC coupling to buffer PCIe HCSL 100MHz clock since its V\_cm is relatively low at about 0.4V, as shown in Fig. 6.

Figure 6: HCSL AC-Coupled Input Interface

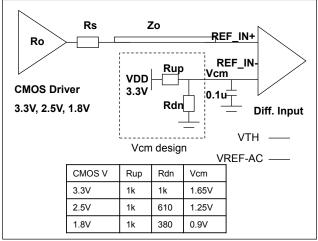

#### **CMOS Clock DC Drive Input**

LVCMOS clock has voltage Voh levels such as 3.3V, 2.5V, 1.8V. CMOS drive requires a Vcm design at the input: Vcm= ½ (CMOS V) as shown in Fig. 7. Rs = $22 \sim 33\Omega$  typically.

Figure 7: CMOS DC Input Vcm Design

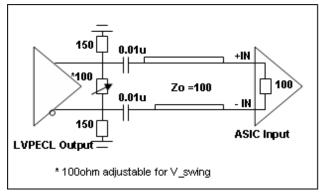

#### **Device LVPECL Output Terminations**

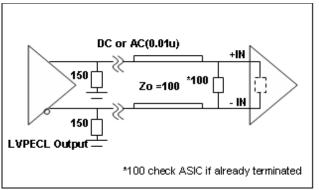

#### **LVPECL Output Popular Termination**

The most popular LVPECL termination is 150Ω pull-down bias and 100Ω across at RX side. Please consult ASIC datasheet if it already has  $100\Omega$  or equivalent internal termination. If so, do not connect external  $100\Omega$  across as shown in Fig. 8. This popular termination's advantage is that it does not allow any bias through from V<sub>DD</sub>. This prevents V<sub>DD</sub> system noise coupling onto clock trace.

# A Product Line of Diodes Incorporated

PI6C59S6005

# Figure. 8 LVPECL Output Popular Termination

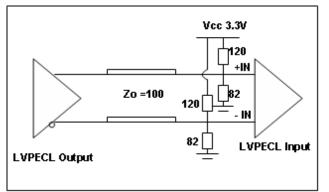

# LVPECL Output Thevenin Termination

Fig. 9 shows LVPECL output Thevenin termination which is used for shorter trace drive (<5in.), but it takes  $V_{DD}$  bias current and  $V_{DD}$  noise can get onto clock trace. It also requires more component count. So it is seldom used today.

Figure. 9 LVPECL Thevenin Output Termination

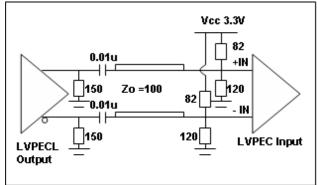

# LVPECL Output AC Thevenin Termination

LVPECL AC Thevenin terminations require a  $150\Omega$  pull-down before the AC coupling capacitor at the source as shown in Fig. 10. Note that pull-up/down resistor value is swapped compared to Fig. 9. This circuit is good for short trace (<5in.) application only.

12

Figure. 10 LVPECL Output AC Thenvenin Termination

A Product Line of Diodes Incorporated

# PI6C59S6005

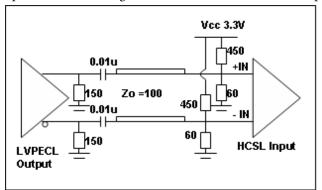

#### LVPECL Output Drive HCSL Input

Using the LVPECL output to drive a HCSL input can be done using a typical LVPECL AC Thenvenin termination scheme. Use pullup/down  $450/60\Omega$  to generate Vcm=0.4V for the HCSL input clock. This termination is equivalent to  $50\Omega$  load as shown in Fig. 11.

Figure. 11 LVPECL Output Drive HCSL Termination

#### LVPECL Output V\_swing Adjustment

It is suggested to add another cross 100 $\Omega$  at TX side to tune the LVPECL output V\_swing without changing the optimal 150 $\Omega$  pull-down bias in Fig. 12. This form of double termination can reduce the V\_swing in ½ of the original at the RX side. By fine tuning the 100 $\Omega$  resistor at the TX side with larger values like 150 to 200 $\Omega$ , one can increase the V\_swing by > 1/2 ratio.

Figure. 12 LVPECL Output V\_swing Adjustment

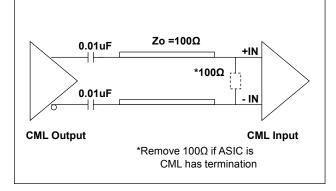

#### **CML AC Output Drive**

CML is implemented mostly via AC coupling. With AC coupling, CML can drive LVPECL and LVDS inputs as well with an external  $100\Omega$  equivalent differential termination.

#### **Clock Jitter Definitions**

#### Total jitter= RJ + DJ

Random Jitter (RJ) is unpredictable and unbounded timing noise that can fit in a Gaussian math distribution in RMS. RJ test values are directly related with how long or how many test samples are available. Deterministic Jitter (DJ) is timing jitter that is predictable and periodic in fixed interference frequency. Total Jitter (TJ) is the combination of random jitter and deterministic jitter: , where is a factor based on total test sample count. JEDEC std. specifies digital clock TJ in 10k random samples.

#### Phase litter

Phase noise is short-term random noise attached on the clock carrier and it is a function of the clock offset from the carrier, for example dBc/Hz@10kHz which is phase noise power in 1-Hz normalized bandwidth vs. the carrier power @10kHz offset. Integration of phase noise in plot over a given frequency band yields RMS phase jitter, for example, to specify phase jitter <=1ps at 12k to 20MHz offset band as SONET standard specification.

#### PCIe Ref CLK Jitter

PCIe reference clock jitter specification requires testing via the PCI-SIG jitter tool, which is regulated by US PCI-SIG organization. The jitter tool has PCIe Serdes embedded filter to calculate the equivalent jitter that relates to data link eye closure. Direct peak-peak jitter or phase jitter test data, normally is higher than jitter measure using PCI-SIG jitter tool. It has high-frequency jitter and low-frequency jitter spec. limit. For more information, please refer to the PCI-SIG website: http://www.pcisig.com/specifications/pciexpress/

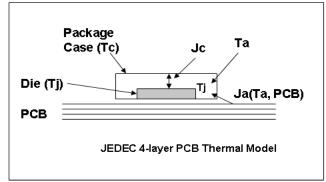

#### **Device Thermal Calculation**

Fig. 13 shows the JEDEC thermal model in a 4-layer PCB.

#### Figure. 13 JEDEC IC Thermal Model

Important factors to influence device operating temperature are:

1) The power dissipation from the chip (P chip) is after subtracting power dissipation from external loads. Generally it can be the no-load device Idd

2) Package type and PCB stack-up structure, for example, loz 4 layer board. PCB with more layers and are thicker has better heat dissipation

3) Chassis air flow and cooling mechanism. More air flow M/s and adding heat sink on device can reduce device final die junction temperature Tj

The individual device thermal calculation formula:

# Tj =Ta + Pchip x Ja

# Tc = Tj - Pchip x Jc

Ja \_\_\_\_ Package thermal resistance from die to the ambient air in C/W unit; This data is provided in JEDEC model simulation. An air flow of 1m/s will reduce Ja (still air) by 20~30%

Jc \_\_\_\_ Package thermal resistance from die to the package case in C/W unit

Tj \_\_\_\_ Die junction temperature in C (industry limit <125C max.)

Ta Ambiant air température in C

Tc \_\_\_\_ Package case temperature in C

Pchip\_\_\_ IC actually consumes power through Iee/GND current

# Thermal calculation example

To calculate Tj and Tc of PI6CV304 in an SOIC-8 package: Step 1: Go to Diodes web to find Ja=157 C/W, Jc=42 C/W https://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

Step 2: Go to device datasheet to find Idd=40mA max.

| 5  |                | C <sub>L</sub> = 33pF/33MHz | 20 |    |

|----|----------------|-----------------------------|----|----|

|    |                | C <sub>L</sub> = 33pF/66MHz | 40 |    |

| Ţ  |                | C <sub>L</sub> = 22pF/80MHz | 35 |    |

| ID | Supply Current | CL = 15pF/100MHz            | 32 | mA |

|    |                | C <sub>L</sub> =10pF/125MHz | 28 |    |

|    |                | CL = 10pF/155MHz            | 41 |    |

Step 3: P\_total= 3.3Vx40mA=0.132W Step 4: If Ta=85C

Tj= 85 + Ja xP\_total= 85+25.9 = 105.7C

$Tc = Tj + Jc xP_total = 105.7 - 5.54 = 100.1C$

#### Note:

The above calculation is directly using Idd current without subtracting the load power, so it is a conservative estimation. For more precise thermal calculation, use P\_unload or P\_chip from device Iee or GND current to calculate Tj, especially for LVPECL buffer ICs that have a 150 $\Omega$  pull-down and equivalent 100 $\Omega$  differential RX load.

# **Part Marking**

YY: Year WW: Workweek 1st X: Assembly Code 2nd X: Fab Code

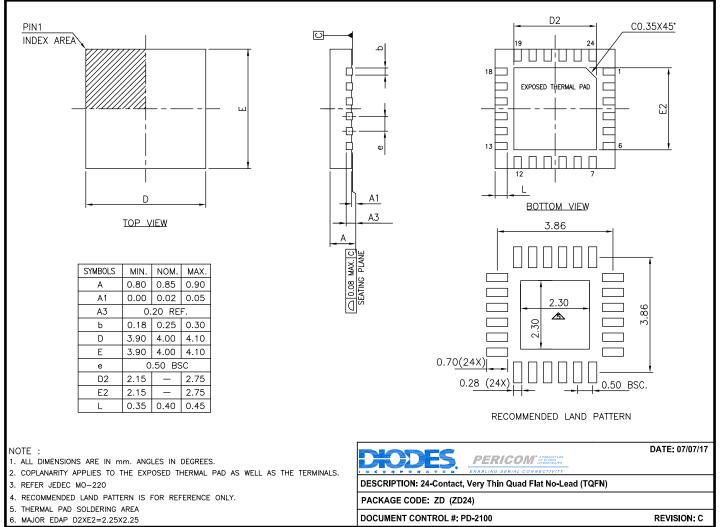

# Packaging Mechanical: 24-TQFN (ZD)

17-0533

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Ordering Code    | Package Code | Package Description                        |

|------------------|--------------|--------------------------------------------|

| PI6C59S6005ZDIEX | ZD           | 24-pin, Very Thin Quad Flat No-Lead (TQFN) |

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. I = Industrial

5. E = Pb-free and Green

6. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS 1. TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FIT-NESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3 Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product 4. names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5 Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7 While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes 8. assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2021 Diodes Incorporated

www.diodes.com