### **General Description**

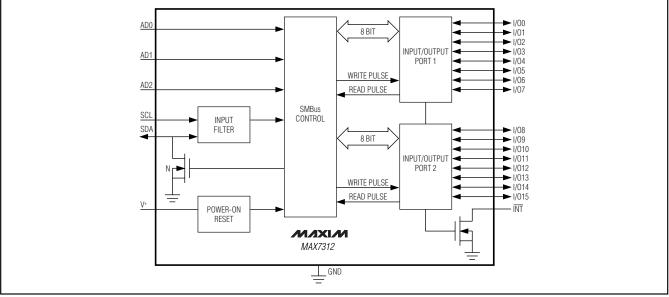

The MAX7312 2-wire-interfaced expander provides 16-bit parallel input/output (I/O) port expansion in SMBus<sup>™</sup> and I<sup>2</sup>C applications. The MAX7312 consists of input port registers, output port registers, polarity inversion registers, configuration registers, a bus timeout register, and an I<sup>2</sup>C-compatible serial interface logic, compatible with SMBus. The system master can invert the MAX7312 input data by writing to the active-high polarity inversion register. The system master can enable or disable bus timeout by writing to the bus timeout register.

EVALUATION KIT

AVAILABLE

Any of the 16 I/O ports can be configured as an input or an output. A power-on reset (POR) initializes the 16 I/Os as inputs. Three address select pins configure the part to one of 64 slave ID addresses.

The MAX7312 supports hot insertion. All port pins, the INT output, SDA, SCL, and the slave address inputs AD0-2 remain high impedance in power-down ( $V_t = 0V$ ) up to 6V.

The MAX7312 is available in 24-pin SO, SSOP, TSSOP, and thin QFN packages and is specified over the -40°C to  $+125^{\circ}$ C automotive temperature range.

For applications requiring I/Os with integrated  $100k\Omega$  pullup resistors, refer to the MAX7311 data sheet.

### Applications

Servers/Blades RAID Systems Medical Equipment Instrumentation and Test Measurement Networking

### \_Features

- ♦ 400kbps I<sup>2</sup>C-Compatible Serial Interface

- 2V to 5.5V Operation

- ♦ 5V Overvoltage Tolerant I/Os

- Supports Hot Insertion

- ♦ 16 I/O Pins that Default to Inputs on Power-Up

- ◆ Open-Drain Interrupt Output (INT)

- Bus Timeout for Lock-Up-Free Operation

- Noise Filter on SCL/SDA Inputs

- ♦ 64 User-Selectable Slave ID Addresses

- Low Standby Current (2.9µA typ)

- Polarity Inversion

- ♦ 4mm × 4mm, 0.8mm Thin QFN Package

- ♦ -40°C to +125°C Operation

### \_Ordering Information

| PART       | TEMP RANGE      | PIN-PACKAGE                | PKG<br>CODE |

|------------|-----------------|----------------------------|-------------|

| MAX7312AWG | -40°C to +125°C | 24 Wide SO                 | _           |

| MAX7312AAG | -40°C to +125°C | 24 SSOP                    | _           |

| MAX7312ATG | -40°C to +125°C | 24 Thin QFN<br>(4mm x 4mm) | T2444-4     |

| MAX7312AUG | -40°C to +125°C | 24 TSSOP                   | _           |

SMBus is a trademark of Intel Corp.

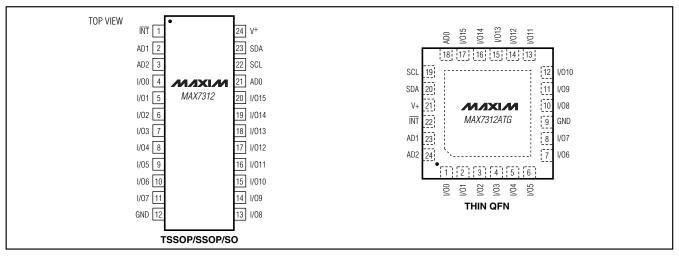

### Pin Configurations

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND                       | 0.3V to +6V         |

|---------------------------------|---------------------|

| I/O0–I/O15 as Inputs            | (GND - 0.3V) to +6V |

| SCL, SDA, AD0, AD1, AD2, INT    | (GND - 0.3V) to +6V |

| Maximum V+ Current              | +250mA              |

| Maximum GND Current             | 250mA               |

| DC Input Current on I/O0–I/O15  | ±20mA               |

| DC Output Current on I/O0-I/O15 | ±80mA               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V^+ = 2V \text{ to } 5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V^+ = 3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                | SYMBOL           | CONDIT                                        | IONS           | MIN                  | ТҮР | MAX                | UNITS |

|--------------------------|------------------|-----------------------------------------------|----------------|----------------------|-----|--------------------|-------|

| Supply Voltage           | V <sup>+</sup>   |                                               |                | 2                    |     | 5.5                | V     |

|                          |                  |                                               | $V^{+} = 2V$   |                      | 23  | 35                 |       |

| Supply Current           | ۱+               | All I/Os unloaded,<br>fsci = 400kHz           | $V^{+} = 3.3V$ |                      | 43  | 60                 | μA    |

|                          |                  | ISCL = 400KHZ                                 | $V^{+} = 5.5V$ |                      | 80  | 120                |       |

|                          |                  |                                               | $V^{+} = 2V$   |                      | 2.3 | 11                 |       |

| Standby Current          | ISTBY            | All I/Os unloaded,                            | $V^{+} = 3.3V$ |                      | 2.9 | 12                 | μA    |

|                          |                  | $f_{SCL} = 0$                                 | $V^{+} = 5.5V$ |                      | 3.8 | 15.5               |       |

| Power-On Reset Voltage   | V <sub>POR</sub> |                                               |                |                      | 1.4 | 1.7                | V     |

| SCL, SDA                 |                  |                                               |                |                      |     |                    |       |

| Input Voltage Low        | VIL              |                                               |                |                      |     | $0.3 \times V^{+}$ | V     |

| Input Voltage High       | VIH              |                                               |                | 0.7 x V <sup>+</sup> |     |                    | V     |

| Low-Level Output Voltage | Vol              | I <sub>SINK</sub> = 6mA                       |                |                      |     | 0.4                | V     |

| Leakage Current          | ١L               |                                               |                | -1                   |     | +1                 | μΑ    |

| Input Capacitance        |                  |                                               |                |                      | 10  |                    | рF    |

| I/O_                     |                  | ·                                             |                |                      |     |                    |       |

| Input Voltage Low        | VIL              |                                               |                |                      |     | 0.8                | V     |

| Input Voltage High       | VIH              |                                               |                | 1.8                  |     |                    | V     |

| Input Leakage Current    |                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                | -1                   |     | +1                 | μA    |

|                          |                  | $V^+ = 2V, V_{OL} = 0.5V$                     |                | 8.5                  | 17  |                    |       |

| Low-Level Output Current | ISINK            | $V^+ = 3.3V, V_{OL} = 0.5V$                   |                | 17                   | 32  |                    | mA    |

|                          |                  | $V^+ = 5V, V_{OL} = 0.5V$                     |                |                      | 43  |                    |       |

|                          | 1                | V <sup>+</sup> = 3.3V, V <sub>OH</sub> = 2.4V |                | 29                   | 41  |                    |       |

| High Output Current      | ISOURCE          | $V^+ = 5V, V_{OH} = 4.5V$                     |                | 31                   |     | mA                 |       |

| AD0, AD1, AD2            |                  |                                               |                |                      |     |                    |       |

| Input Voltage Low        | VIL              |                                               |                |                      |     | $0.3 \times V^+$   | V     |

| Input Voltage High       | VIH              |                                               |                | 0.7 x V <sup>+</sup> |     |                    | V     |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V^+ = 2V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } + 125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V^+ = 3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                | SYMBOL          | CONDITIONS      | MIN | ТҮР | MAX | UNITS |  |  |

|--------------------------|-----------------|-----------------|-----|-----|-----|-------|--|--|

| Leakage Current          |                 |                 | -1  |     | +1  | μA    |  |  |

| Input Capacitance        |                 |                 |     | 4   |     | pF    |  |  |

|                          |                 |                 |     |     |     |       |  |  |

| Low-Level Output Current | I <sub>OL</sub> | $V_{OL} = 0.4V$ | 6   |     |     | mA    |  |  |

### **AC ELECTRICAL CHARACTERISTICS**

(V<sup>+</sup> = 2V to 5.5V,  $T_A = -40^{\circ}C$  to +125°C, unless otherwise noted.) (Note 1)

| PARAMETER                                          | SYMBOL              | CONDIT                | IONS                   | MIN | ТҮР | MAX        | UNITS |

|----------------------------------------------------|---------------------|-----------------------|------------------------|-----|-----|------------|-------|

| SCL Clock Frequency                                | fscl                | (Note 2)              |                        |     |     | 400        | kHz   |

| Bus Timeout                                        | <b>TIMEOUT</b>      |                       |                        | 29  |     | 61         | ms    |

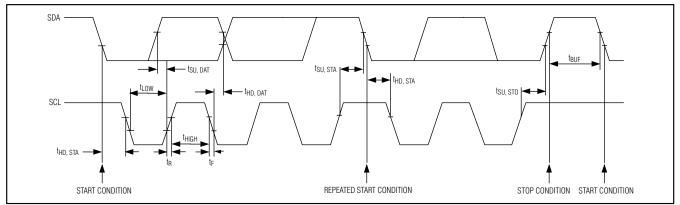

| Bus Free Time Between STOP<br>and START Conditions | <sup>t</sup> BUF    | Figure 2              |                        | 1.3 |     |            | μs    |

| Hold Time (Repeated) START<br>Condition            | <sup>t</sup> HD,STA | Figure 2              | 0.6                    |     |     | μs         |       |

| Repeated START Condition<br>Setup Time             | tsu,sta             | Figure 2              | 0.6                    |     |     | μs         |       |

| STOP Condition Setup Time                          | tsu,sto             | Figure 2              | 0.6                    |     |     | μs         |       |

| Data Hold Time                                     | thd,dat             | Figure 2 (Note 3)     |                        |     | 0.9 | μs         |       |

| Data Setup Time                                    | tsu,dat             | Figure 2              | 100                    |     |     | ns         |       |

| SCL Low Period                                     | tLOW                | Figure 2              | 1.3                    |     |     | μs         |       |

| SCL High Period                                    | thigh               | Figure 2              |                        | 0.7 |     |            | μs    |

| SDA Fall Time                                      | t⊨                  | Figure 2 (Notes 4, 5) | V+ < 3.3V<br>V+ ≥ 3.3V |     |     | 500<br>250 | ns    |

| Pulse Width of Spike Suppressed                    | tsp                 | (Note 6)              |                        |     | 50  |            | ns    |

| PORT TIMING                                        |                     |                       |                        |     |     |            | •     |

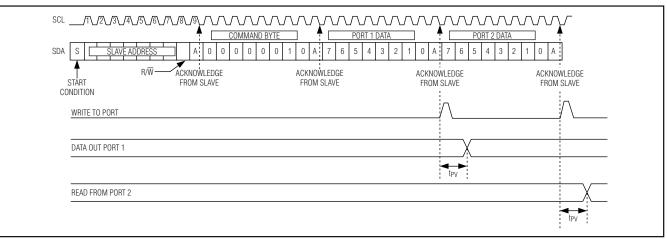

| Output Data Valid                                  | tPV                 | Figure 7              |                        |     |     | 3          | μs    |

| Input Data Setup Time                              |                     |                       |                        | 27  |     |            | μs    |

| Input Data Hold Time                               |                     |                       |                        | 0   |     |            | μs    |

| INTERRUPT TIMING                                   |                     |                       |                        |     |     |            |       |

| Interrupt Valid                                    | tıv                 | Figure 9              |                        |     |     | 30.5       | μs    |

| Interrupt Reset                                    | tıR                 | Figure 9              |                        |     |     | 2          | μs    |

Note 1: All parameters are 100% production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

Note 2: Minimum SCL clock frequency is limited by the MAX7312 bus timeout feature, which resets the serial bus interface if either SDA or SCL is held low for a minimum of 25ms. Disable bus timeout feature for DC operation.

**Note 3:** A master device must internally provide a hold time of at least 300ns for the SDA signal (referred to the  $V_{IL}$  of the SCL signal) in order to bridge the undefined region SCL's falling edge.

**Note 4:**  $C_B$  = total capacitance of one bus line in pF.

**Note 5:** The maximum t<sub>F</sub> for the SDA and SCL bus lines is specified at 300ns. The maximum fall time for the SDA output stage t<sub>F</sub> is specified at 250ns. This allows series protection resistors to be connected between the SDA and SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>F</sub>.

Note 6: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

MAX7312

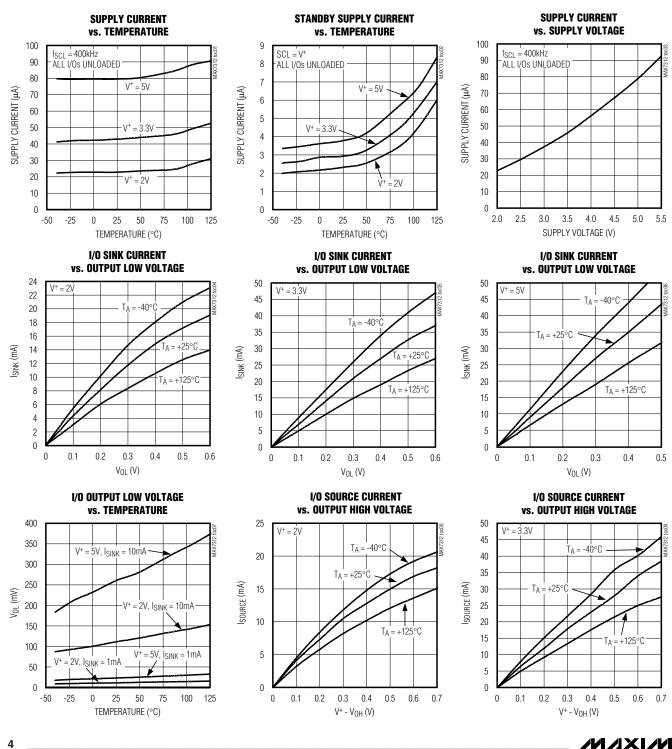

### Typical Operating Characteristics

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

4

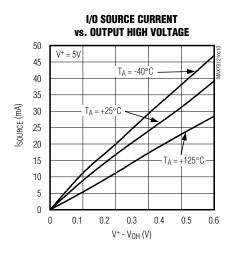

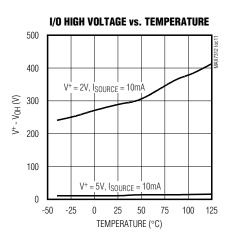

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# **MAX7312**

### **Pin Description**

| PI                | IN          |                |                                                         |

|-------------------|-------------|----------------|---------------------------------------------------------|

| TSSOP/<br>SSOP/SO | THIN<br>QFN | NAME           | FUNCTION                                                |

| 1                 | 22          | ĪNT            | Interrupt Output (Open Drain)                           |

| 2                 | 23          | AD1            | Address Input 1                                         |

| 3                 | 24          | AD2            | Address Input 2                                         |

| 4–11              | 1–8         | I/00–I/07      | Input/Output Port 1                                     |

| 12                | 9           | GND            | Supply Ground                                           |

| 13–20             | 10–17       | I/08–I/015     | Input/Output Port 2                                     |

| 21                | 18          | AD0            | Address Input 0                                         |

| 22                | 19          | SCL            | Serial Clock Line                                       |

| 23                | 20          | SDA            | Serial Data Line                                        |

| 24                | 21          | V <sup>+</sup> | Supply Voltage. Bypass with a 0.047µF capacitor to GND. |

| _                 | PAD         | Exposed<br>pad | Exposed Pad on Package Underside. Connect to GND.       |

Figure 1. MAX7312 Block Diagram

Figure 2. 2-Wire Serial Interface Timing Diagram

### **Detailed Description**

The MAX7312 general-purpose input/output (GPIO) peripheral provides up to 16 I/O ports, controlled through an I<sup>2</sup>C-compatible serial interface. The MAX7312 consists of input port registers, output port registers, polarity inversion registers, configuration registers, and a bus-timeout register. Upon power-on, all I/O lines are set as inputs. Three slave ID address select pins, AD0, AD1, and AD2, choose one of 64 slave ID addresses, including the eight addresses supported by the Phillips PCA9555. Table 1 is the register address table. Tables 2–6 show detailed register information.

### Serial Interface

### Serial Addressing

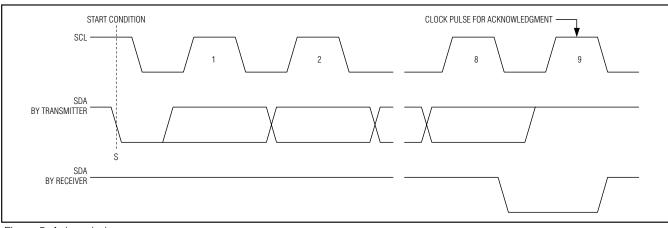

The MAX7312 operates as a slave that sends and receives data through a 2-wire interface. The interface uses a serial data line (SDA) and a serial clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master, typically a microcontroller, initiates all data transfers to and from the MAX7312, and generates the SCL clock that synchronizes the data transfer (Figure 2).

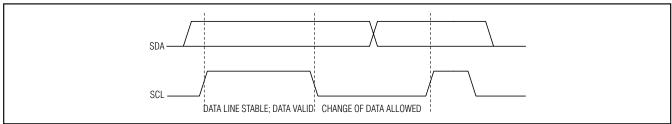

Figure 4. Bit Transfer

Figure 5. Acknowledge

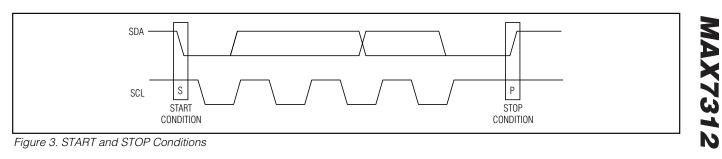

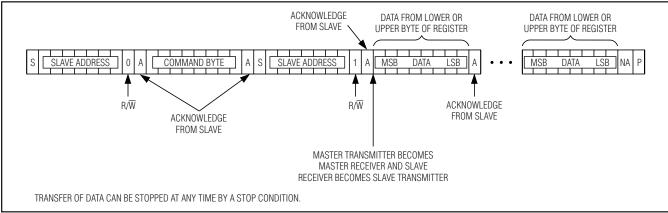

Each transmission consists of a START condition sent by a master, followed by the MAX7312 7-bit slave address plus R/W bit, a register address byte, 1 or more data bytes, and finally a STOP condition (Figure 3).

### **START and STOP Conditions**

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 3).

### **Bit Transfer**

One data bit is transferred during each clock pulse. The data on SDA must remain stable while SCL is high (Figure 4).

### Acknowledge

The acknowledge bit is a clocked 9th bit, which the recipient uses as a handshake receipt of each byte of data (Figure 5). Thus, each byte transferred effectively requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, such that the SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MAX7312, the

### M/X/M

MAX7312 generates the acknowledge bit since the MAX7312 is the recipient. When the MAX7312 is transmitting to the master, the master generates the acknowledge bit.

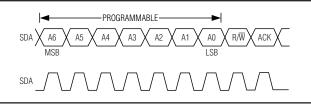

#### **Slave Address**

The MAX7312 has a 7-bit-long slave address (Figure 6). The 8th bit following the 7-bit slave address is the R/W bit. Set this bit low for a write command and high for a read command.

Figure 6. Slave Address

### Table 1. Command Byte Register

Slave address pins AD2, AD1, and AD0 choose 1 of 64 slave ID addresses (Table 7).

#### **Data Bus Transaction**

The command byte is the first byte to follow the 8-bit device slave address during a write transmission (Table 1, Figure 7). The command byte is used to determine which of the following registers are written or read.

#### Writing to Port Registers

Transmit data to the MAX7312 by sending the device slave address and setting the LSB to a logic zero. The command byte is sent after the address and determines which registers receive the data following the command byte (Figure 7).

| COMMAND BYTE<br>ADDRESS (HEX) | FUNCTION                                           | PROTOCOL        | POWER-UP<br>DEFAULT |

|-------------------------------|----------------------------------------------------|-----------------|---------------------|

| 0x00                          | Input port 1                                       | Read byte       | XXXX XXXX           |

| 0x01                          | Input port 2                                       | Read byte       | XXXX XXXX           |

| 0x02                          | Output port 1                                      | Read/write byte | 1111 1111           |

| 0x03                          | Output port 2                                      | Read/write byte | 1111 1111           |

| 0x04                          | Port 1 polarity inversion                          | Read/write byte | 0000 0000           |

| 0x05                          | Port 2 polarity inversion                          | Read/write byte | 0000 0000           |

| 0x06                          | Port 1 configuration                               | Read/write byte | 1111 1111           |

| 0x07                          | Port 2 configuration                               | Read/write byte | 1111 1111           |

| 0x08                          | Timeout register                                   | Read/write byte | 0000 0001           |

| 0xFF                          | Factory reserved. (Do not write to this register.) | _               | —                   |

Eight of the MAX7312's nine registers are configured to operate as four register pairs: input ports, output ports, polarity inversion ports, and configuration ports. After sending 1 byte of data to one register, the next byte is sent to the other register in the pair. For example, if the first byte of data is sent to output port 2, then the next byte of data is stored in output port 1. An unlimited number of data bytes can be sent in one write transmission. This allows each 8-bit register to be updated independently of the other registers.

#### **Reading Port Registers**

MAX7312

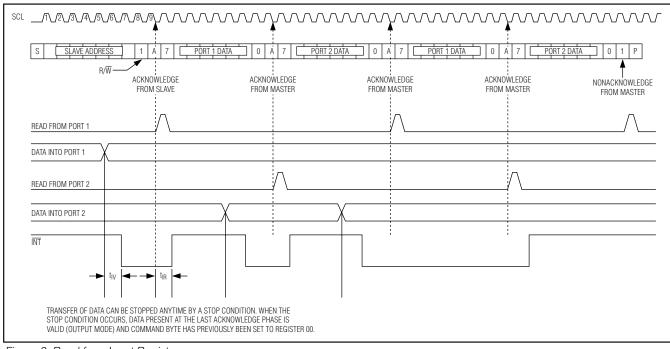

To read the device data, the bus master must first send the MAX7312 address with the R/W bit set to zero, followed by the command byte, which determines which register is accessed. After a restart, the bus master must then send the MAX7312 address with the R/W bit set to 1. Data from the register defined by the command byte is then sent from the MAX7312 to the master (Figures 8, 9).

Figure 8. Read from Register

Figure 9. Read from Input Registers

M/XI/M

**MAX7312**

Data is clocked into a register on the falling edge of the acknowledge clock pulse. After reading the first byte, additional bytes may be read and reflect the content in the other register in the pair. For example, if input port 1 is read, the next byte read is input port 2. An unlimited number of data bytes can be read in one read transmission, but the final byte received must not be acknowledged by the bus master.

### Interrupt (INT)

The open-drain interrupt output, INT, activates when one of the port pins changes states and only when the pin is configured as an input. The interrupt deactivates when the input returns to its previous state or the input register is read (Figure 9). A pin configured as an output does not cause an interrupt. Each 8-bit port register is read independently; therefore, an interrupt caused by port 1 is not cleared by a read of port 2's register.

Changing an I/O from an output to an input may cause a false interrupt to occur if the state of that I/O does not match the content of the input port register.

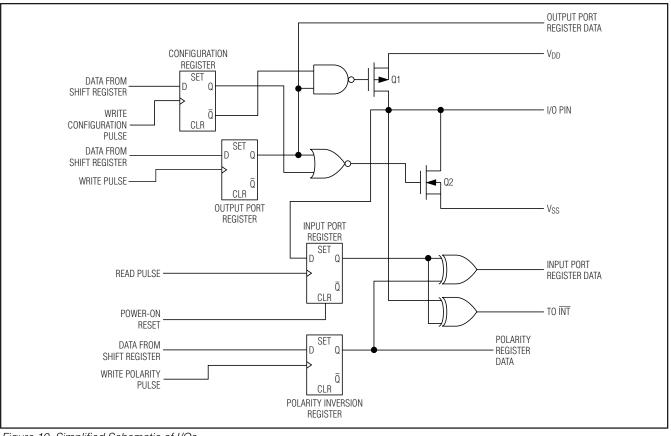

### Input/Output Port

When an I/O is configured as an input, FETs Q1 and Q2 are off (Figure 10), creating a high-impedance input. All inputs are overvoltage protected to 5.5V, independent of supply voltage. When a port is configured as an output, either Q1 or Q2 is on, depending on the state of the output port register. When V+ powers up, an internal power-on reset sets all registers to their respective defaults (Table 1).

#### Input Port Registers

The input port registers (Table 2) are read-only ports. They reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the respective configuration register. A read of the input port 1 register latches the current value of I/OO–I/O7. A read of the input port 2 register latches the current value of I/O8–I/O15. Writes to the input port registers are ignored.

Figure 10. Simplified Schematic of I/Os

### Table 2. Registers 0x00, 0x01—Input Port Registers

| BIT | 17  | 16  | 15  | 14  | 13 | 12  | l1 | 10 |

|-----|-----|-----|-----|-----|----|-----|----|----|

| БП  | 115 | 114 | 113 | l12 | 11 | I10 | 19 | 18 |

### Table 3. Registers 0x02, 0x03—Output Port Registers

| DIT              | 07  | O6  | O5  | 04  | 03  | 02  | 01 | 00 |

|------------------|-----|-----|-----|-----|-----|-----|----|----|

| BIT              | 015 | 014 | 013 | 012 | 011 | 010 | O9 | 08 |

| Power-up default | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  |

### Table 4. Registers 0x04, 0x05—Polarity Inversion Registers

| DIT              | I/07  | I/O6  | I/O5  | I/O4  | I/O3  | I/O2  | I/O1 | I/O0 |

|------------------|-------|-------|-------|-------|-------|-------|------|------|

| BIT              | I/O15 | I/O14 | I/O13 | I/O12 | I/011 | I/O10 | I/O9 | I/O8 |

| Power-up default | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0    |

### Table 5. Registers 0x06, 0x07—Configuration Registers

| BIT              | I/07  | I/O6  | I/O5  | I/O4  | I/O3  | I/O2  | I/O1 | I/O0 |

|------------------|-------|-------|-------|-------|-------|-------|------|------|

| DII              | I/O15 | I/O14 | I/O13 | I/O12 | I/011 | I/O10 | I/O9 | I/O8 |

| Power-up default | 1     | 1     | 1     | 1     | 1     | 1     | 1    | 1    |

### Table 6. Register 0x08—Timeout Register

| BIT              | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|---|---|---|---|---|---|---|---|

| Power-up default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

### **Output Port Registers**

The output port registers (Table 3) set the outgoing logic levels of the I/Os defined as outputs by the respective configuration register. Reads from the output port registers reflect the value that is in the flip-flop controlling the output selection, not the actual I/O value.

### **Polarity Inversion Registers**

The polarity inversion registers (Table 4) enable polarity inversion of pins defined as inputs by the respective port configuration registers. Set the bit in the polarity inversion register to invert the corresponding port pin's polarity. Clear the bit in the polarity inversion register to retain the corresponding port pin's original polarity.

### **Configuration Registers**

The configuration registers (Table 5) configure the directions of the I/O pins. Set the bit in the respective configuration register to enable the corresponding port as an input. Clear the bit in the configuration register to enable the corresponding port as an output.

### **Bus Timeout**

Set register 0x08 LSB (bit 0) to enable the bus timeout function (Table 6) or clear it to disable the bus timeout function. Enabling the timeout feature resets the MAX7312 serial bus interface when SCL stops either high or low during a read or write. If either SCL or SDA is low for more than 29ms after the start of a valid serial transfer, the interface resets itself and sets up SDA as an input. The MAX7312 then waits for another START condition.

### Standby

The MAX7312 goes into standby when the I<sup>2</sup>C bus is idle. Standby supply current is typically 2.9µA.

### **Applications Information**

### **Hot Insertion**

The I/O ports I/O0–I/O15 interrupt output  $\overline{INT}$ , and serial interfaces SDA, SCL, AD0-2 remain high impedance with up to 6V asserted on them when the MAX7312 is powered down (V+ = 0V). The MAX7312 can therefore be used in hot-swap applications.

### **Power-Supply Consideration**

The MAX7312 operates from a supply voltage of 2V to 5.5V. Bypass the power supply to GND with a  $0.047\mu$ F capacitor as close to the device as possible. For the QFN version, connect the underside exposed pad to GND.

///XI//

MAX7312

### Table 7. MAX7312 Address Map

| AD2            | AD1            | AD0 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ADDRESS (HEX) |

|----------------|----------------|-----|----|----|----|----|----|----|----|---------------|

| GND            | SCL            | GND | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0x20          |

| GND            | SCL            | V+  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0x22          |

| GND            | SDA            | GND | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0x24          |

| GND            | SDA            | V+  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0x26          |

| $V^+$          | SCL            | GND | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0x28          |

| $V^+$          | SCL            | V+  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0x2A          |

| $V^+$          | SDA            | GND | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 0x2C          |

| V <sup>+</sup> | SDA            | V+  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 0x2E          |

| GND            | SCL            | SCL | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0x30          |

| GND            | SCL            | SDA | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0x32          |

| GND            | SDA            | SCL | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0x34          |

| GND            | SDA            | SDA | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0x36          |

| $V^+$          | SCL            | SCL | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0x38          |

| $V^+$          | SCL            | SDA | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0x3A          |

| $V^+$          | SDA            | SCL | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0x3C          |

| $V^+$          | SDA            | SDA | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 0x3E          |

| GND            | GND            | GND | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0x40          |

| GND            | GND            | V+  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0x42          |

| GND            | V+             | GND | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0x44          |

| GND            | V+             | V+  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0x46          |

| $V^+$          | GND            | GND | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0x48          |

| $V^+$          | GND            | V+  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0x4A          |

| $V^+$          | V+             | GND | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 0x4C          |

| $V^+$          | V+             | V+  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0x4E          |

| GND            | GND            | SCL | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0x50          |

| GND            | GND            | SDA | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0x52          |

| GND            | V+             | SCL | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0x54          |

| GND            | V+             | SDA | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0x56          |

| $V^+$          | GND            | SCL | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0x58          |

| $V^{+}$        | GND            | SDA | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0x5A          |

| $V^+$          | V <sup>+</sup> | SCL | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 0x5C          |

| $V^+$          | V+             | SDA | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 0x5E          |

| Table 7. MAX7312 Address Map (continued) |

|------------------------------------------|

|------------------------------------------|

| AD2 | AD1 | AD0 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ADDRESS (HEX) |

|-----|-----|-----|----|----|----|----|----|----|----|---------------|

| SCL | SCL | GND | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0xA0          |

| SCL | SCL | V+  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 0xA2          |

| SCL | SDA | GND | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0xA4          |

| SCL | SDA | V+  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 0xA6          |

| SDA | SCL | GND | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0xA8          |

| SDA | SCL | V+  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0xAA          |

| SDA | SDA | GND | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0xAC          |

| SDA | SDA | V+  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0xAE          |

| SCL | SCL | SCL | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0xB0          |

| SCL | SCL | SDA | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 0xB2          |

| SCL | SDA | SCL | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0xB4          |

| SCL | SDA | SDA | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 0xB6          |

| SDA | SCL | SCL | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 0xB8          |

| SDA | SCL | SDA | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 0xBA          |

| SDA | SDA | SCL | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 0xBC          |

| SDA | SDA | SDA | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0xBE          |

| SCL | GND | GND | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0xC0          |

| SCL | GND | V+  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0xC2          |

| SCL | V+  | GND | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 0xC4          |

| SCL | V+  | V+  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 0xC6          |

| SDA | GND | GND | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0xC8          |

| SDA | GND | V+  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0xCA          |

| SDA | V+  | GND | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0xCC          |

| SDA | V+  | V+  | 1  | 1  | 0  | 0  | 1  | 1  | 1  | 0xCE          |

| SCL | GND | SCL | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0xD0          |

| SCL | GND | SDA | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0xD2          |

| SCL | V+  | SCL | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0xD4          |

| SCL | V+  | SDA | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 0xD6          |

| SDA | GND | SCL | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0xD8          |

| SDA | GND | SDA | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0xDA          |

| SDA | V+  | SCL | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0xDC          |

| SDA | V+  | SDA | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 0xDE          |

### Chip Information

TRANSISTOR COUNT: 12,994 PROCESS: BICMOS

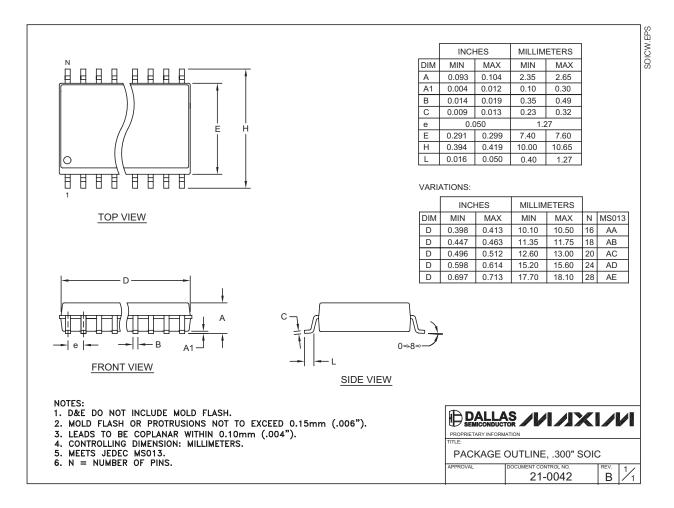

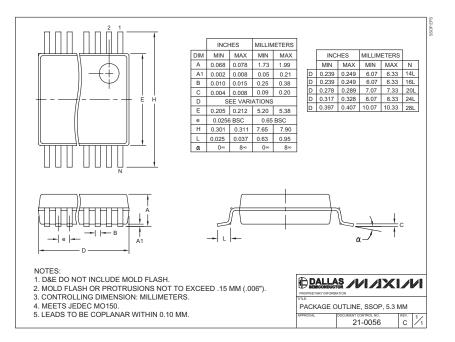

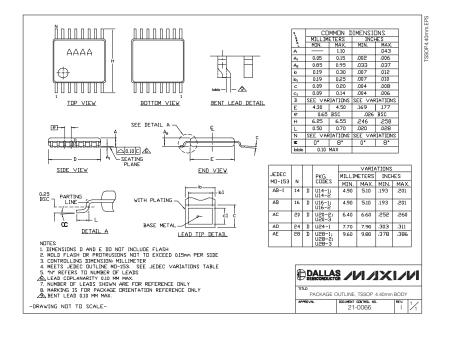

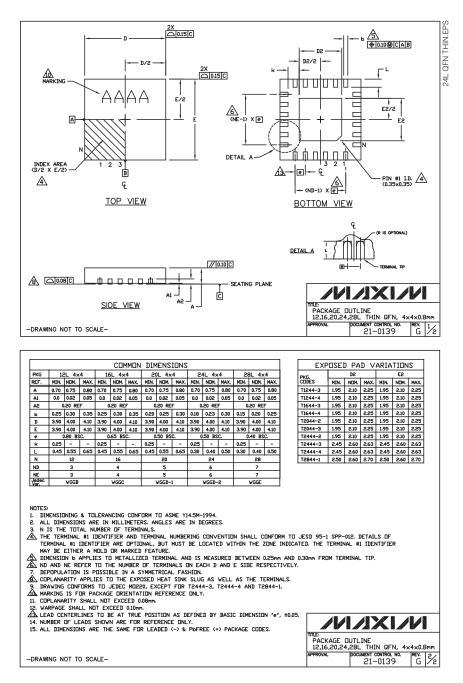

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

M/IXI/M

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

### \_Package Information (continued)

16

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2005 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products, Inc.