## FEATURES AND BENEFITS

- AEC-Q100 qualified

- Wide input voltage range of 4.5 to 36 V

- Operates down to 3.9 V (V $_{\rm IN}$  falling) for idle stop, and up to 40 V for load dump

- Integrated boost converter with DMOS switch and OVP protection up to 39 V

- 8 fully integrated LED current sinks, with individually programmable current up to 60 mA per channel

- I<sup>2</sup>C<sup>™</sup> interface for programming LED current, PWM dimming, and various protection thresholds per channel

- Ability to drive multiple loads from a single IC

- Extensive PWM dimming (up to 10,000:1 at 100 Hz), individually programmable for each channel

- Extensive diagnostics and fault reporting

- Thermal warning and derating of LED current at higher temperatures

Continued on the next page ....

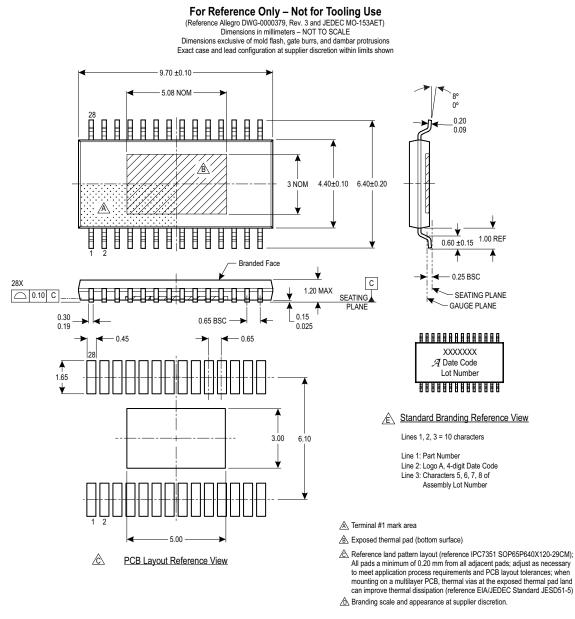

## PACKAGE:

28-pin TSSOP with exposed thermal pad (suffix LP)

Not to scale

# DESCRIPTION

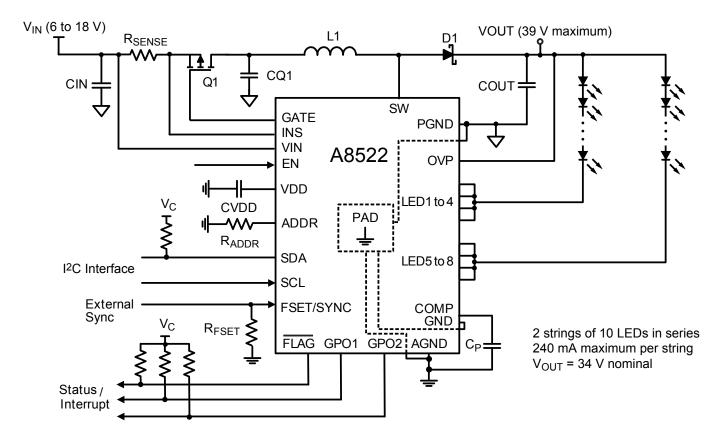

The A8522 is a programmable multi-output LED driver for LCD backlighting. It integrates a current-mode boost converter with internal power switch and 8 current sinks. The IC operates from 4.5 to 36 V, and is able to withstand up to 40 V load-dump conditions encountered in automotive systems.

The control loop is optimized to eliminate night flash in display backlight applications.

The I<sup>2</sup>C interface allows the user to set the LED currents individually, up to 60 mA per LED channel. Adjacent channels may be combined to drive higher-current LED strings. The PWM dimming duty cycle also is independently controlled for each LED channel. This flexibility makes the A8522 a single solution for a wide range of LED applications. Two-way communication allows fault status to be reported.

Continued on the next page ...

# **APPLICATIONS:**

Automotive:

- Infotainment

- Cluster

- Center-stack lighting

- Head-up display (HUD)

- Daytime running lights (DRL)

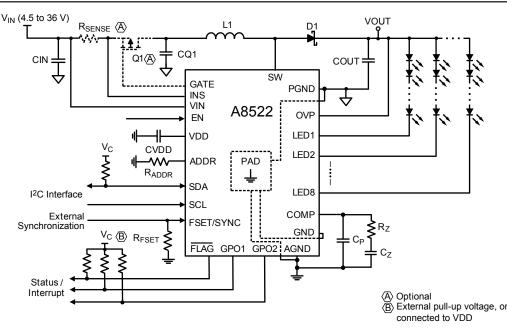

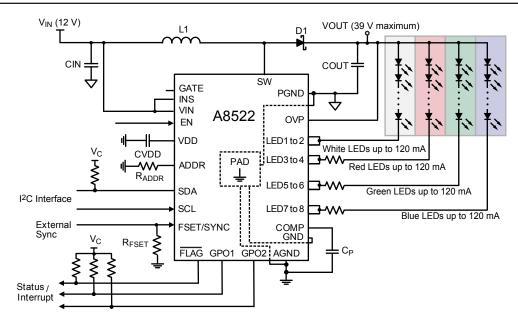

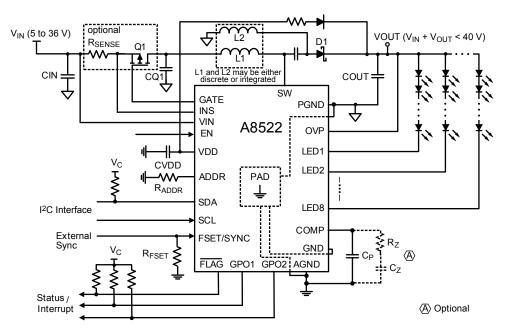

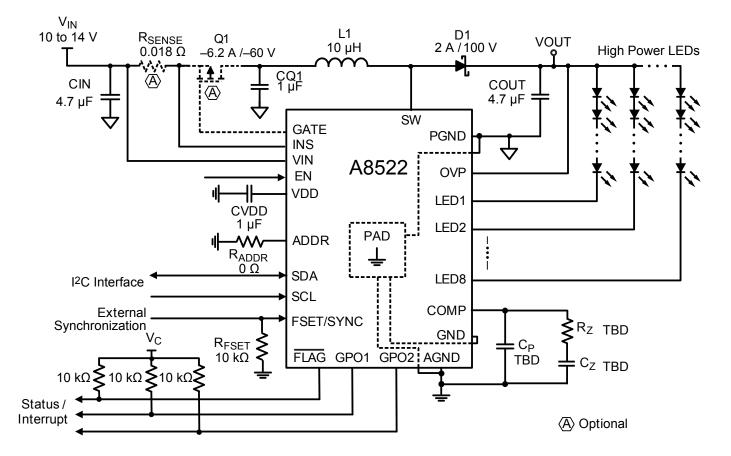

Typical Application Drawing

## FEATURES AND BENEFITS (continued)

- Buffered PWM dimming control for all channels to facilitate localized dimming applications

- Polyphase PWM dimming: LED currents staggered to reduce light flickering and input ripple current

- Synchronize boost switching frequency: 400 kHz to 2.3 MHz to allow operation below or above the AM band

- · Programmable frequency dithering to reduce EMI

- Typical LED current accuracy of 0.7%, and LED-to-LED matching accuracy of 0.8%

- Protection features

SELECTION GUIDE

- $\Box$  Open/shorted LED pin detection

- □ Programmable LED string short detection

- Open/shorted external components (including boost inductor, Schottky diode, FSET resistor and so forth)

- □ Input overcurrent protection against output to GND short

- $\hfill\square$  Cycle-by-cycle switch current limit

- □ Overtemperature, and output overvoltage and undervoltage protection

## **DESCRIPTION** (continued)

PWM dimming duty cycle also is independently controlled for each LED channel. This flexibility makes the A8522 a single solution for a wide range of LED applications, in some cases offering the ability to replace two or more LED driver ICs with a single device.

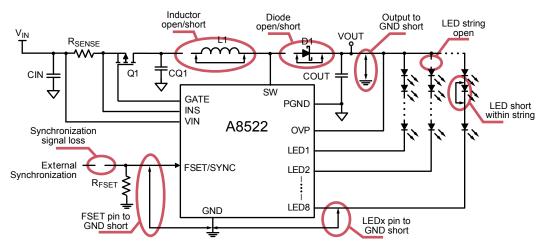

The A8522 detects and protects against a wide variety of fault conditions, and two-way communication allows fault status to be reported. It provides protection against output short and overvoltage, open or shorted diode, open or shorted LED pin, shorted boost switch or inductor, and IC overtemperature. A dual cycle-by-cycle current limit protects the internal switch against switch overcurrent. If required, the IC can drive an external PFET as an input-disconnect switch that is triggered by integrated current sense.

| Part Number  | Operating Ambient<br>Temperature Range<br>T <sub>A</sub> (°C) | Package                               | Packing <sup>[1]</sup>      | Leadframe<br>Plating | (Rh) |

|--------------|---------------------------------------------------------------|---------------------------------------|-----------------------------|----------------------|------|

| A8522KLPTR-T | -40 to 125                                                    | 28-pin TSSOP with exposed thermal pad | 4000 pieces per 13-in. reel | 100% matte tin       |      |

<sup>[1]</sup> Contact Allegro<sup>™</sup> for additional packing options.

## Table of Contents

| Features and Benefits                       | 1  | Polyphase Grouping                           | 22  |  |

|---------------------------------------------|----|----------------------------------------------|-----|--|

| Description                                 | 1  | Boost Output Voltage Regulation              | 23  |  |

| Applications                                | 1  | Output Hysteresis                            | 24  |  |

| Package                                     | 1  | Soft Start Timing                            | 24  |  |

| Typical Application Drawing                 | 1  | Input Disconnect Switch                      | 24  |  |

| Selection Guide                             | 2  | System Failure Detection and Protection      | 26  |  |

| Specifications                              | 3  | Fault Handling                               | 27  |  |

| Absolute Maximum Ratings                    | 3  | Application Information                      | 30  |  |

| Thermal Characteristics                     | 3  | Package Outline Design                       | 37  |  |

| Functional Block Diagram                    | 4  | Appendix A: Programming Information          | A-1 |  |

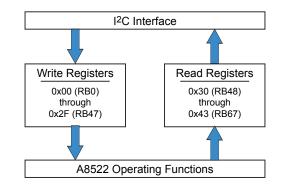

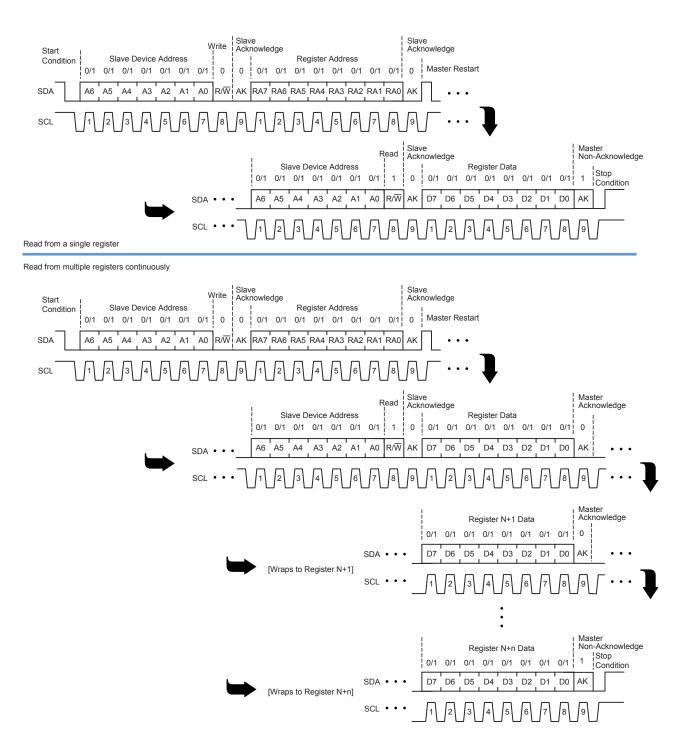

| Pinout Diagram and Terminal List Table      | 5  | I <sup>2</sup> C Interface Description       | A-2 |  |

| Electrical Characteristics                  | 6  | Timing Considerations                        | A-2 |  |

| Characteristic Performance                  | 9  | I <sup>2</sup> C Command Write to the A8522  | A-3 |  |

| Fault Handling                              | 14 | I <sup>2</sup> C Command Read from the A8522 | A-4 |  |

| Input Overcurrent Protection                | 14 | Order of Reading and Writing Registers       | A-4 |  |

| Switch Overcurrent Protection               | 15 | Dealing with Incomplete Transmission         | A-4 |  |

| LED String Open Fault Detection             | 15 | Register Map                                 | A-6 |  |

| Protection Against Open/Missing BOOST Diode | 16 | Register Field Reference                     | A-8 |  |

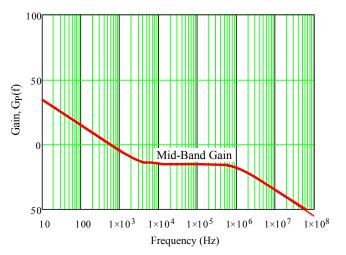

| Functional Description                      | 17 | Appendix B: Feedback Loop Calculations       | B-1 |  |

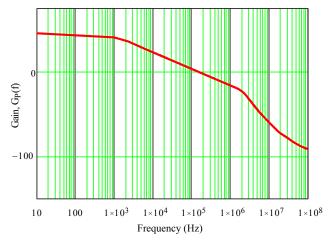

| Enabling the IC                             | 17 | Power Stage Transfer Function                | B-1 |  |

| PWM Dimming                                 | 18 | Output to Control Transfer Function          | B-2 |  |

| Output Current and Voltage                  | 18 | Stabilizing the Closed Loop System           | B-4 |  |

| Boost Frequency Dithering                   | 22 | Measuring Feedback Loop Gain, Phase Margin   | B-6 |  |

|                                             |    |                                              |     |  |

## **SPECIFICATIONS**

## ABSOLUTE MAXIMUM RATINGS [1]

| Characteristic                                         | Symbol               | Notes                                                               | Rating      | Unit |

|--------------------------------------------------------|----------------------|---------------------------------------------------------------------|-------------|------|

| LEDx Pins                                              | V <sub>LEDx</sub>    |                                                                     | -0.3 to 42  | V    |

| FLAG, GPO2, and OVP Pins                               |                      |                                                                     | -0.3 to 42  | V    |

| EN, VIN, INS, and GATE Pins                            |                      | INS and GATE pins should not exceed $\rm V_{IN}$ by more than 0.4 V | -0.3 to 40  | V    |

| SIM/ Dia                                               |                      | Continuous                                                          | -0.6 to 42  | V    |

| SW Pin                                                 | V <sub>SW</sub>      | t < 50 ns                                                           | -1.0 to 46  | V    |

| VDD, FSET/SYNC, COMP, GPO1,<br>SDA, SCL, and ADDR Pins |                      |                                                                     | -0.3 to 5.5 | V    |

| Operating Ambient Temperature                          | T <sub>A</sub>       | K temperature range                                                 | -40 to 125  | °C   |

| Maximum Junction Temperature                           | T <sub>J</sub> (max) |                                                                     | 150         | °C   |

| Storage Temperature                                    | T <sub>stg</sub>     |                                                                     | -65 to 150  | °C   |

<sup>[1]</sup> Operation at levels beyond the ratings listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to Absolute Maximumrated conditions for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol                | Test Conditions <sup>[2]</sup>         | Value | Unit |

|----------------------------|-----------------------|----------------------------------------|-------|------|

| Package Thermal Resistance | $R_{	extsf{	heta}JA}$ | On 4-layer PCB based on JEDEC standard | 28    | °C/W |

<sup>[2]</sup> Additional thermal information available on the Allegro website.

# A8522

# Wide Input Voltage, Fault Tolerant, Independently Controlled Multi-Channel LED Driver with I<sup>2</sup>C Interface

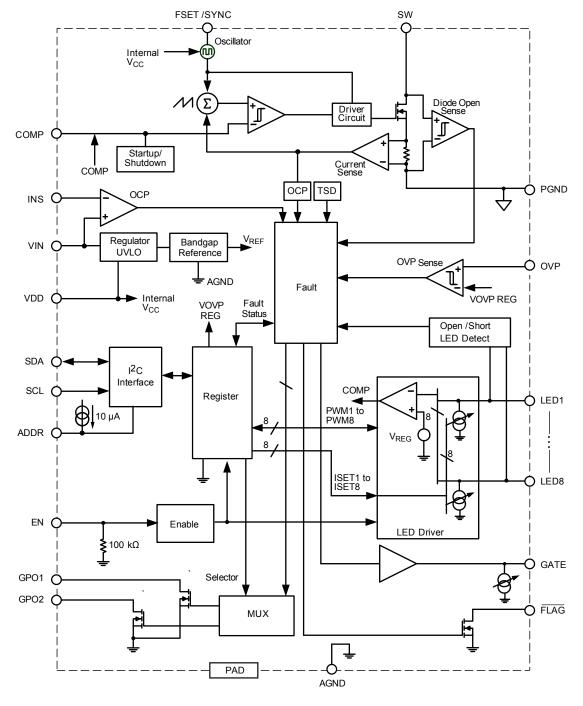

**Functional Block Diagram**

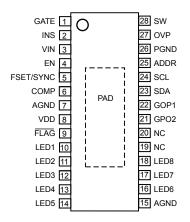

## Package LP, 28-Pin TSSOP Pinout Diagram

### **Terminal List Table**

| Name      | Number                               | Function                                                                                                                                                                                                                                           |

|-----------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR      | 25                                   | This pin has 4 levels that allow the user to set up to 4 physical IC addresses based on the voltage level. Connect a resistor to GND to set the voltage level.                                                                                     |

| AGND      | 7, 15                                | Analog ground; connect all noise-sensitive components (especially for COMP) to this quiet ground, and connect to thermal pad.                                                                                                                      |

| COMP      | 6                                    | Output of error amplifier and compensation node; connect a type-2 feedback network from this pin to AGND for control loop compensation.                                                                                                            |

| EN        | 4                                    | Enable for the A8522; IC stays in shutdown mode as long as EN = $V_{EN(L)}$ , enables the part when connected to $V_{EN(H)}$ or to VIN.                                                                                                            |

| FLAG      | 9                                    | This active-low, open-drain pin is used to indicate that system attention is required, such as during startup or a fault condition. Connect a resistor with a value from 10 to 100 k $\Omega$ between this pin and the target logic level voltage. |

| FSET/SYNC | 5                                    | Frequency/synchronization pin; a resistor, R <sub>FSET</sub> , from this pin to GND sets the switching frequency, and this pin can also be used to synchronize to an external switching frequency.                                                 |

| GATE      | 1                                    | Gate driver for optional external PMOS input disconnect switch, that in the event of a fault (such as output shorted to GND) is turned off by this pin being pulled high (turning off input supply); if not used, this pin should be left open.    |

| GPO1      | 22                                   | General purpose open-drain output 1, programmable by internal register.                                                                                                                                                                            |

| GPO2      | 21                                   | General purpose open-drain output 2, programmable by internal register.                                                                                                                                                                            |

| INS       | 2                                    | Input current sense, used together with VIN pin to detect input overcurrent fault; if not used, this pin should be tied to VIN.                                                                                                                    |

| LEDx      | 10, 11, 12,<br>13, 14, 16,<br>17, 18 | LED current sink channels 1 through 8. Up to 60 mA per channel. Any unused LEDx pin should be connected to GND through a 4.7 k $\Omega$ resistor.                                                                                                  |

| NC        | 19, 20                               | No connect. Terminate each pin to GND through a 4.7 k $\Omega$ resistor (do not short to GND directly). See page A-8 for important notes on initialization of register 0x00.                                                                       |

| OVP       | 27                                   | Connect this pin to output voltage V <sub>OUT</sub> to provide output Overvoltage Protection (OVP) and Undervoltage Protection (UVP).                                                                                                              |

| PAD       | _                                    | Exposed pad of the package providing enhanced thermal dissipation. This pad must be connected to the ground plane(s) of the PCB with at least 8 vias, directly in the pad, and AGND and PGND pins must be connected to this ground pad on the PCB. |

| PGND      | 26                                   | Power ground for internal NMOS switching device; connect this pin to ground terminal of output ceramic capacitor(s) and to thermal pad.                                                                                                            |

| SCL       | 24                                   | I <sup>2</sup> C clock signal.                                                                                                                                                                                                                     |

| SDA       | 23                                   | I <sup>2</sup> C data signal.                                                                                                                                                                                                                      |

| SW        | 28                                   | The drain of the internal NMOS switch of the boost converter.                                                                                                                                                                                      |

| VDD       | 8                                    | Output of internal LDO; connect a 0.47 µF decoupling capacitor between this pin and AGND.                                                                                                                                                          |

| VIN       | 3                                    | Input power to the A8522.                                                                                                                                                                                                                          |

ELECTRICAL CHARACTERISTICS <sup>[1]</sup>: Valid at  $V_{IN} = 16 V$ ,  $T_A = 25^{\circ}C$ , EN =  $V_{EN(H)}$ , • indicates specifications valid across the full operating temperature range with  $T_A = T_J = -40^{\circ}C$  to 125°C and with typical specifications at  $T_A = 25^{\circ}C$ ; unless otherwise specified

| Characteristic                            | Symbol                  | Test Conditions                                                                                     |       | Min. | Тур. | Max. | Unit     |

|-------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|-------|------|------|------|----------|

| INPUT VOLTAGE                             |                         |                                                                                                     |       |      |      |      |          |

| Input Voltage Range                       | V <sub>IN</sub>         | Measured at the VIN pin                                                                             | •     | 4.5  | -    | 36   | V        |

| VIN Pin UVLO Start                        | V <sub>INUV(ON)</sub>   | V <sub>IN</sub> rising                                                                              | •     | -    | -    | 4.35 | V        |

| VIN Pin UVLO Stop                         | V <sub>INUV(OFF)</sub>  | V <sub>IN</sub> falling                                                                             | •     | -    | _    | 3.90 | V        |

| VIN Pin UVLO Hysteresis                   | V <sub>INUV(HYS)</sub>  |                                                                                                     |       | -    | 400  | -    | mV       |

| INPUT CURRENT                             |                         |                                                                                                     |       |      |      |      |          |

| Input Quiescent Current                   | IQ                      | Measured at the VIN pin, EN = $V_{EN(H)}$ , $f_{SW}$ = 2 MHz no load                                | •     | -    | 15   | -    | mA       |

| Input Sleep Supply Current                | I <sub>QSLEEP</sub>     | Sum of VIN and INS pin currents, $V_{IN} = V_{INS} = 16 \text{ V}, V_{EN} = 0 \text{ V}$            | •     | -    | 3.5  | 10.0 | μA       |

| EN (ENABLE) PIN                           |                         |                                                                                                     |       |      |      |      |          |

| EN Input Logic Level - Low                | V <sub>EN(L)</sub>      | 4.5 V < V <sub>IN</sub> < 36 V                                                                      | •     | -    | -    | 0.4  | V        |

| EN Input Logic Level - High               | V <sub>EN(H)</sub>      | 4.5 V < V <sub>IN</sub> < 36 V                                                                      | •     | 1.5  | -    | -    | V        |

| EN Internal Pull-Down Resistance          | R <sub>ENPD</sub>       |                                                                                                     |       | -    | 100  | -    | kΩ       |

| Error Amplifier                           |                         |                                                                                                     |       |      |      |      | <u> </u> |

| Source Current                            | I <sub>EA(SRC)</sub>    | V <sub>COMP</sub> = 0.75 V, V <sub>LEDx</sub> = 0.3 V                                               | -     |      | -200 | -    | μA       |

| Sink Current                              | I <sub>EA(SINK)</sub>   | V <sub>COMP</sub> = 0.75 V, V <sub>LEDx</sub> = 1.5 V                                               | -     |      | +200 | -    | μA       |

| COMP Pin Internal Pull-Down<br>Resistance | R <sub>COMPPD</sub>     | During startup and shutdown                                                                         |       | -    | 2000 | -    | Ω        |

| OUTPUT OVERVOLTAGE AND UN                 | DERVOLTA                | GE PROTECTION                                                                                       |       |      |      |      |          |

| Over eltere Threehold                     | V <sub>OVPMIN</sub>     | OVP register = xxx0 0000                                                                            | •     | 7.5  | 8    | 8.5  | V        |

| Overvoltage Threshold                     | V <sub>OVPMAX</sub>     | OVP register = xxx1 1111                                                                            | •     | 38   | 39   | 40   | V        |

| Overvoltage Step Size                     | V <sub>OVPSTEP</sub>    |                                                                                                     |       | -    | 1.0  | -    | V        |

| Linder voltage Threehold                  | V <sub>UVPMIN</sub>     | OVP register = xxx0 0000                                                                            |       | -    | 0.49 | -    | V        |

| Undervoltage Threshold                    | VUVPMAX                 | OVP register = xxx1 1111                                                                            |       | -    | 2.5  | -    | V        |

| OVP Pin Input Impedance                   | R <sub>OVP</sub>        | $V_{OVP}$ = 20 V, EN = $V_{EN(H)}$                                                                  |       | -    | 800  | -    | kΩ       |

| OVP Leakage Current                       | I <sub>OVPLKG</sub>     | $V_{OVP}$ =16 V, EN = $V_{EN(L)}$                                                                   | •     | -    | 0.1  | 1    | μA       |

| Secondary Overvoltage Protection          | V <sub>OVP(sec)</sub>   | Measured at SW pin                                                                                  |       | -    | 44   | -    | V        |

| BOOST Switch                              |                         |                                                                                                     |       |      |      |      |          |

| Switch On-Resistance                      | R <sub>DS(ON)</sub>     | I <sub>SW</sub> = 0.750 A, V <sub>IN</sub> = 16 V                                                   |       | -    | 220  | 350  | mΩ       |

| Switch Leakage Current                    | I <sub>SWLKG</sub>      | $V_{SW}$ = 16 V, EN = $V_{EN(L)}$ , $T_A$ = $T_J$ = -40°C<br>to 85°C                                |       | -    | 0.1  | 10   | μA       |

| -                                         |                         | $V_{SW} = 16 \text{ V}, \text{ EN} = V_{EN(L)}, \text{ T}_{A} = \text{T}_{J} = 125^{\circ}\text{C}$ |       | -    | 3    | -    | μA       |

| Cycle-by-Cycle Switch Current Limit       | I <sub>SW(LIM)</sub>    |                                                                                                     | • 3.6 |      | 4.2  | 4.8  | A        |

| Secondary Switch Current Limit [2]        | I <sub>SWLIM(sec)</sub> | Higher than maximum I <sub>SW(LIM)</sub> at any condition (A8522 latches when detected)             | • 5.6 |      | 7.0  | -    | А        |

| Minimum Switch On-Time                    | t <sub>SWONTIME</sub>   | R <sub>FSET</sub> = 10 kΩ                                                                           | •     | -    | 85   | 130  | ns       |

| Minimum Switch Off-Time                   | t <sub>SWOFFTIME</sub>  | R <sub>FSET</sub> = 10 kΩ                                                                           | •     | _    | 55   | 85   | ns       |

Continued on the next page ...

**ELECTRICAL CHARACTERISTICS**<sup>[1]</sup> (continued): valid at  $V_{IN} = 16 V$ ,  $T_A = 25^{\circ}C$ ,  $EN = V_{EN(H)}$ , • indicates specifications valid across the full operating temperature range with  $T_A = T_J = -40^{\circ}C$  to 125°C and with typical specifications at  $T_A = 25^{\circ}C$ ; unless otherwise specified

| Characteristic                                  | Symbol                 | Test Conditions                                                         |           | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|------------------------|-------------------------------------------------------------------------|-----------|------|------|------|------|

| SWITCHING FREQUENCY                             |                        |                                                                         |           |      |      |      |      |

|                                                 |                        | R <sub>FSET</sub> = 10 kΩ                                               | •         | 1.8  | 2    | 2.2  | MHz  |

| Boost Stage Switching Frequency                 | f <sub>SW</sub>        | R <sub>FSET</sub> = 20.1 kΩ                                             |           | _    | 1    | -    | MHz  |

|                                                 |                        | R <sub>FSET</sub> = 40.6 kΩ                                             |           | _    | 500  | -    | kHz  |

| FSET/SYNC Pin Voltage                           | V <sub>FSETSYNC</sub>  | R <sub>FSET</sub> = 10 kΩ                                               |           | -    | 1.00 | -    | V    |

| SYNCHRONIZATION                                 |                        |                                                                         |           |      |      |      |      |

| Synchronized Boost Stage Switching<br>Frequency | f <sub>SW_SYNC</sub>   |                                                                         | •         | 400  | -    | 2300 | kHz  |

| Synchronization Input Minimum<br>Off-Time       | t <sub>SYNCPWOFF</sub> |                                                                         | •         | 150  | -    | -    | ns   |

| Synchronization Input Minimum<br>On-Time        | <sup>t</sup> SYNCPWON  |                                                                         | •         | 150  | -    | -    | ns   |

| Synchronization Input Logic – Low               | V <sub>SYNCON(L)</sub> |                                                                         | •         | -    | -    | 0.4  | V    |

| Synchronization Input Logic – High              | V <sub>SYNCON(H)</sub> |                                                                         | •         | 2    | -    | -    | V    |

| LED CURRENT SINKS                               |                        | L                                                                       |           |      |      |      |      |

| LEDx Accuracy (Average)                         | Err <sub>LEDx</sub>    | Measured at I <sub>LEDMAX</sub> (maximum LED current)                   | •         | -    | 0.7  | 3    | %    |

| LEDx Matching                                   | ΔI <sub>LEDx</sub>     | Compared to average I <sub>LEDx</sub> , measured at I <sub>LEDMAX</sub> | • -       |      | 0.8  | 3    | %    |

| LEDx Regulation Voltage                         | V <sub>REG</sub>       | ISET register= xx11 1111                                                | •         | -    | 0.85 | 1.0  | V    |

| I <sub>LEDx</sub> Step Size                     | ISETSTEP               | Total 64 steps                                                          | •         | 0.9  | 1    | 1.1  | mA   |

| Maximum LEDx Current (Average)                  | ILEDMAX                | ISET register = xx11 1111                                               | $\square$ | 60   | 64   | 66   | mA   |

| Minimum LEDx Current                            | ILEDMIN                | ISET register = xx00 0000                                               |           | -    | 1    | -    | mA   |

| LEDx Short-Detect Threshold                     |                        | Short-Detect register = 000                                             |           | _    | 12   | -    | V    |

| LEDX Short-Detect Threshold                     | V <sub>LED_SD</sub>    | Short-Detect register = 111                                             |           | -    | 5    | -    | V    |

| INTERRUPTS (FLAG, GPO1 AND G                    | PO2 PINS)              |                                                                         |           |      |      |      |      |

| Pin Pull-Down Voltage                           |                        | Fault/Interrupt condition asserted, pull-up<br>current = 0.5 mA         | •         | -    | -    | 0.4  | V    |

| Pin Leakage Current                             |                        | Fault/Interrupt condition cleared, pull-up to 3.6 V                     |           | -    | -    | 2    | μA   |

| INTERNAL MASTER CLOCK                           |                        |                                                                         |           |      |      |      |      |

| Master Clock Period                             | T <sub>CLK</sub>       |                                                                         | •         | 120  | 150  | 180  | ns   |

| Master Clock Temperature Deviation [2]          | ΔT <sub>CLK</sub>      | T <sub>CLK</sub> change over temperature range                          | •         | -2.5 | _    | 2.5  | %    |

Continued on the next page ...

**ELECTRICAL CHARACTERISTICS** <sup>[1]</sup> (continued): valid at  $V_{IN} = 16 V$ ,  $T_A = 25^{\circ}C$ ,  $EN = V_{EN(H)}$ , • indicates specifications valid across the full operating temperature range with  $T_A = T_J = -40^{\circ}C$  to 125°C and with typical specifications at  $T_A = 25^{\circ}C$ ; unless otherwise specified

| Characteristic                             | Symbol                 | Test Conditions                                                                     |   | Min. | Тур.            | Max.  | Unit |

|--------------------------------------------|------------------------|-------------------------------------------------------------------------------------|---|------|-----------------|-------|------|

| INPUT DISCONNECT                           |                        |                                                                                     |   | ~    | ·               |       |      |

| GATE Pin Sink Current                      | I <sub>GSINK</sub>     | V <sub>GATE</sub> = V <sub>IN</sub> , no input overcurrent fault<br>tripped         |   | _    | 115             | -     | μA   |

| GATE Pin Source Current                    | IGSOURCE               | $V_{GATE} = V_{IN} - 5 V$ , input overcurrent fault tripped                         |   | -    | -6              | -     | mA   |

| GATE Voltage at Off                        | V <sub>GSOFF</sub>     | EN = V <sub>EN(L)</sub> , or overcurrent fault occurred                             |   | -    | V <sub>IN</sub> | -     | V    |

| GATE Voltage at On                         | V <sub>GSON</sub>      | Gate-to-source voltage when gate is on, measured as $V_{\text{IN}}-V_{\text{GATE}}$ | • | 5    | -               | 8     | V    |

| GATE Pin Leakage Current                   | I <sub>GLKG</sub>      | $EN = V_{EN(L)}, V_{GATE} = V_{IN}$                                                 | • | -    | -               | 1     | μA   |

| INS Pin Sink Current                       | IINSSINK               |                                                                                     |   | -    | 20              | -     | μA   |

| INS Trip Point                             | VINSTRIP               | Measured between VIN and INS                                                        | • | 90   | 105             | 120   | mV   |

| INS Trip Detection Time [2]                | t <sub>INSTRIP</sub>   | Sensed voltage, V <sub>IN</sub> – V <sub>INS</sub> = 160 mV                         |   | -    | 2               | -     | μs   |

| Thermal Protection (TSD)                   |                        |                                                                                     |   |      |                 |       |      |

| Thermal Shutdown Threshold <sup>[2]</sup>  | T <sub>SD</sub>        | Temperature rising                                                                  |   | 155  | 170             | -     | °C   |

| Thermal Shutdown Hysteresis <sup>[2]</sup> | T <sub>SDHYS</sub>     |                                                                                     |   | -    | 20              | -     | °C   |

| Thermal Warning Threshold                  | T <sub>SDWARN</sub>    | Temperature rising, measured as difference from TSD                                 |   | -    | 20              | -     | °C   |

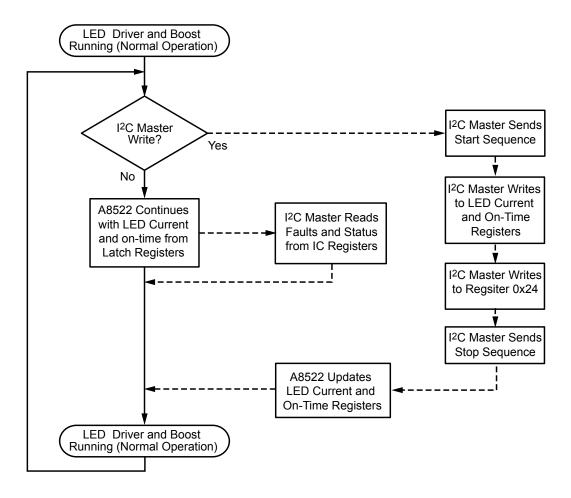

| I <sup>2</sup> C INTERFACE                 |                        |                                                                                     |   |      |                 |       |      |

| Logic Input (SDA, SCL) – Low               | V <sub>SCL(L)</sub>    |                                                                                     |   | -    | -               | 0.8   | V    |

| Logic Input (SDA, SCL) – High              | V <sub>SCL(H)</sub>    |                                                                                     |   | 2.3  | -               | -     | V    |

| Logic Input Hysteresis                     | V <sub>I2CIHYS</sub>   |                                                                                     |   | -    | 150             | -     | mV   |

| Logic Input Current                        | I <sub>I2CI</sub>      |                                                                                     |   | -1   | -               | 1     | μA   |

| Output Voltage SDA                         | V <sub>I2COut(L)</sub> | SDA = low, pull-up current = 2.5 mA                                                 |   | _    | -               | 0.4   | V    |

| Output Leakage SDA                         | I <sub>I2CLKG</sub>    | EN = low, pull-up to 5.5 V                                                          |   | _    | -               | 1     | μA   |

| SCL Clock Frequency                        | f <sub>CLK</sub>       |                                                                                     |   | -    | -               | 400   | kHz  |

| ADDR PIN                                   |                        |                                                                                     |   |      |                 |       |      |

| Voltage Level for Address 100,0000         | V <sub>ADDLEVEL1</sub> | ADDR connected to GND                                                               |   | 0    | -               | 0.5   | V    |

| Voltage Level for Address 101,0000         | V <sub>ADDLEVEL2</sub> | $R_{ADDR}$ = 110 k $\Omega$ from ADDR to GND                                        |   | 0.9  | -               | 1.3   | V    |

| Voltage Level for Address 110,0000         | V <sub>ADDLEVEL3</sub> | $R_{ADDR}$ = 210 k $\Omega$ from ADDR to GND                                        |   | 1.75 | -               | 2.45  | V    |

| Voltage Level for Address 111,0000         | V <sub>ADDLEVEL4</sub> | ADDR connected to VDD pin or open                                                   |   | 3.2  | -               | 3.6   | V    |

| ADDR Pull-Up Current                       | I <sub>ADDR</sub>      | V <sub>ADDR</sub> = 1 V                                                             |   | -8.5 | -10             | -11.5 | μA   |

| INTERNAL REGULATOR                         |                        |                                                                                     |   |      |                 |       |      |

| Bias Supply Voltage                        | V <sub>DD</sub>        |                                                                                     |   | -    | 3.6             | -     | V    |

|                                            |                        |                                                                                     |   |      |                 |       |      |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

A8522

# Wide Input Voltage, Fault Tolerant, Independently Controlled Multi-Channel LED Driver with I<sup>2</sup>C Interface

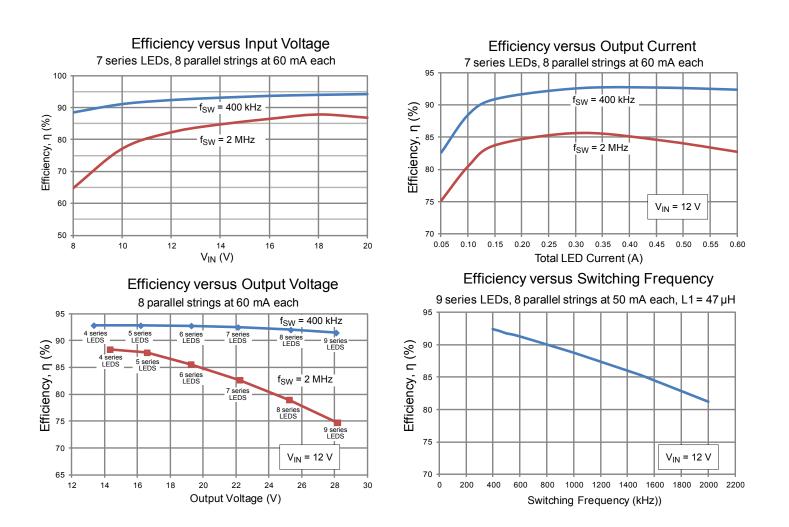

## CHARACTERISTIC PERFORMANCE

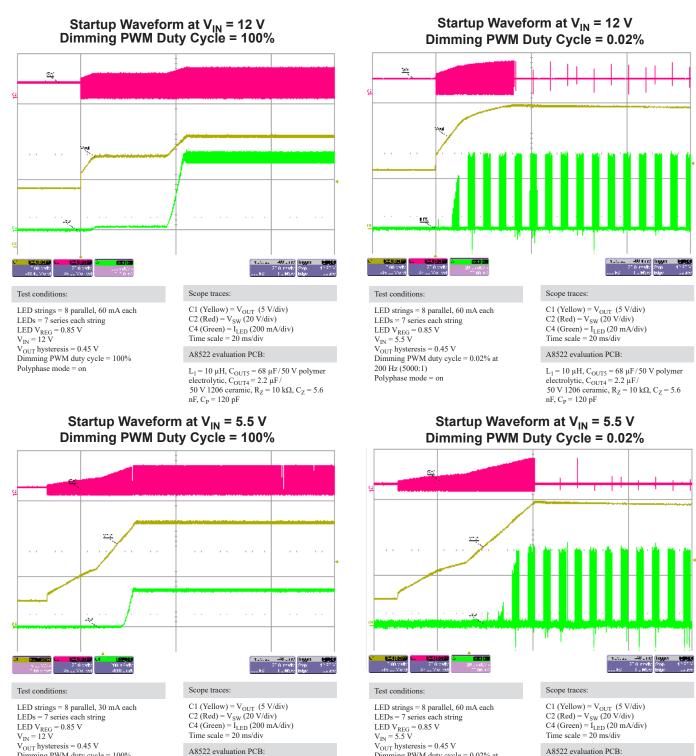

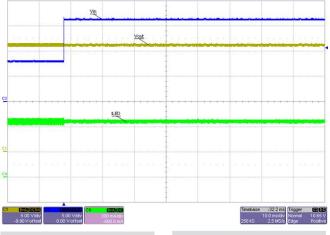

Dimming PWM duty cycle = 100% Polyphase mode = on

# Wide Input Voltage, Fault Tolerant, Independently Controlled Multi-Channel LED Driver with I<sup>2</sup>C Interface

A8522 evaluation PCB:

$L_1 = 10 \ \mu\text{H}, C_{OUT5} = 68 \ \mu\text{F} / 50 \ \text{V}$  polymer electrolytic,  $C_{OUT4} = 2.2 \ \mu F/$ 50 V 1206 ceramic,  $R_Z = 10$  kΩ,  $C_Z = 5.6$ nF,  $C_P = 120$  pF

$L_1 = 10 \ \mu H, C_{OUT5} = 68 \ \mu F / 50 \ V$  polymer

50 V 1206 ceramic,  $R_Z = 10 \text{ k}\Omega$ ,  $C_Z = 5.6 \text{ nF}$ ,  $C_P = 120 \text{ pF}$

electrolytic,  $C_{OUT4} = 2.2 \ \mu F/$

Dimming PWM duty cycle = 0.02% at 200 Hz (5000:1)

Polyphase mode = on

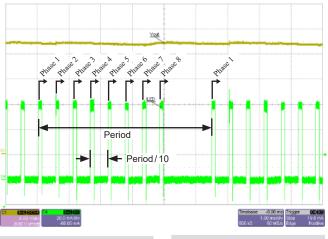

**PWM Operation with Polyphase**

#### Test conditions:

Scope traces: C1 (Yellow) = V<sub>OUT</sub> (5 V/div)

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string LED  $V_{REG} = 0.85$  V  $V_{IN} = 12$  V  $V_{OUT}$  hysteresis = 0.45 V Dimming PWM duty cycle = 2% at 200 Hz Polyphase mode = on (each on at assigned time slot)

C4 (Green) =  $I_{LED}$  (200 mA/div) Time scale = 1 ms/div A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_P=120 \ pF \end{array}$

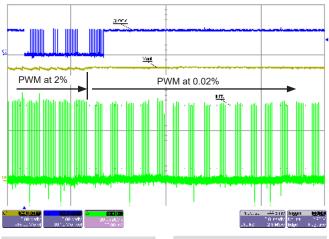

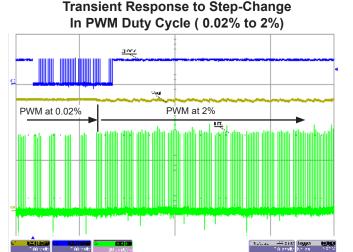

## Transient Response to Step-Change In PWM Duty Cycle (2% to 0.02%)

#### Test conditions:

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $V_{IN} = 12 V$ Dimming PWM duty cycle = change from 2% to 0.02% at 200 Hz (PWM on-time change from 100  $\mu$ s to 1  $\mu$ s) Polyphase mode = on

#### Scope traces:

$C1 (Yellow) = V_{OUT} (5 V/div) \\ C3 (Blue) = I^2C clock (5 V/div) \\ C4 (Green) = I_{LED} (20 mA/div) \\ Time scale = 10 ms/div$

### A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_P=120 \ pF \end{array}$

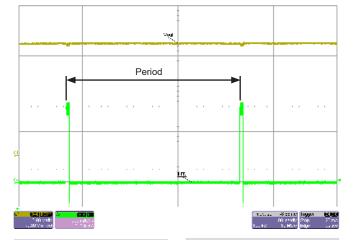

**PWM Operation without Polyphase**

#### Test conditions:

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $V_{IN}$  = 12 V Dimming PWM duty cycle = 2% at 200 Hz Polyphase mode = off (all simultaneously on)

#### Scope traces:

$\begin{array}{l} C1 \; (Yellow) = V_{OUT} \; (5 \; V/div) \\ C4 \; (Green) = I_{LED} \; (200 \; mA/div) \\ Time \; scale = 1 \; ms/div \end{array}$

#### A8522 evaluation PCB

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUT5}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6\\ nF, \ C_P=120 \ pF \end{array}$

#### Test conditions:

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $V_{IN} = 12 V$ Dimming PWM duty cycle = change from 0.02% to 2% at 200 Hz (PWM on-time change from 1 µs to 100 µs) Polyphase mode = on

#### Scope traces:

C1 (Yellow) =  $V_{OUT}$  (5 V/div) C3 (Blue) =  $I^2C$  clock (5 V/div) C4 (Green) =  $I_{LED}$  (20 mA/div) Time scale = 10 ms/div

#### A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_P=120 \ pF \end{array}$

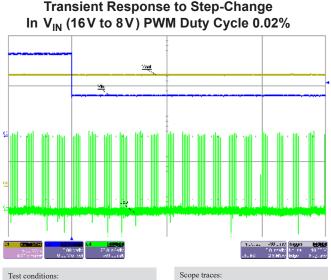

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $V_{IN}$  = change from 16 V to 8 V Dimming PWM duty cycle = 0.02% at 200 Hz  $\begin{array}{l} C1 \ (Yellow) = V_{OUT} \ (5 \ V/div) \\ C3 \ (Blue) = V_{IN} \ (5 \ V/div) \\ C4 \ (Green) = I_{LED} \ (20 \ mA/div) \\ Time \ scale = 10 \ ms/div \end{array}$

#### A8522 evaluation PCB:

$\begin{array}{l} L_1 = 10 \; \mu H, \ C_{OUTS} = 68 \; \mu F/50 \; V \; polymer \\ electrolytic, \ C_{OUT4} = 2.2 \; \mu F/ \\ 50 \; V \; 1206 \; ceramic, \ R_Z = 10 \; k\Omega, \ C_Z = 5.6 \\ nF, \ C_P = 120 \; pF \end{array}$

## Transient Response to Step-Change In V<sub>IN</sub> (16V to 8V) PWM Duty Cycle 100%

#### Test conditions:

$\begin{array}{l} LED \mbox{ strings} = 8 \mbox{ parallel}, 45 \mbox{ mA each} \\ LEDs = 7 \mbox{ series each string} \\ V_{\rm IN} = \mbox{ change from 16 V to 8 V} \\ Dimming \mbox{ PWM duty cycle} = 100\% \end{array}$

#### Scope traces:

$\begin{array}{l} C1 \; (Yellow) = V_{OUT} \; (5 \; V/div) \\ C3 \; (Blue) = V_{IN} \; (5 \; V/div) \\ C4 \; (Green) = I_{LED} \; (20 \; mA/div) \\ Time \; scale = 10 \; ms/div \end{array}$

#### A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_P=120 \ pF \end{array}$

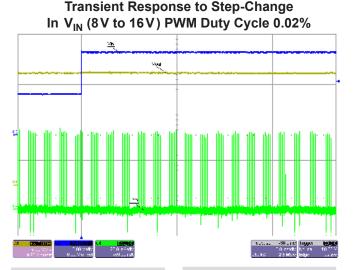

#### Test conditions:

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $V_{IN}$  = change from 8 V to 16 V Dimming PWM duty cycle = 0.02% at 200 Hz

Scope traces:

$\begin{array}{l} C1 \; (Yellow) = V_{OUT} \; (5 \; V/div) \\ C3 \; (Blue) = V_{IN} \; (5 \; V/div) \\ C4 \; (Green) = I_{LED} \; (20 \; mA/div) \\ Time \; scale = 10 \; ms/div \end{array}$

A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer \\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/ \\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_p=120 \ pF \end{array}$

## Transient Response to Step-Change In $V_{IN}$ (8 V to 16 V) PWM Duty Cycle 100%

#### Test conditions:

LED strings = 8 parallel, 45 mA each LEDs = 7 series each string  $V_{IN}$  = change from 8 V to 16 V Dimming PWM duty cycle = 100%

#### Scope traces:

$\begin{array}{l} C1 \ (Yellow) = V_{OUT} \ (5 \ V/div) \\ C3 \ (Blue) = V_{IN} \ (5 \ V/div) \\ C4 \ (Green) = I_{LED} \ (20 \ mA/div) \\ Time \ scale = 10 \ ms/div \end{array}$

### A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_P=120 \ pF \end{array}$

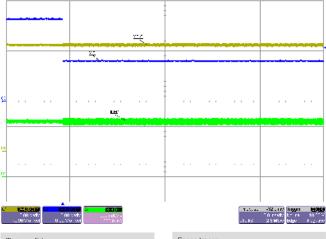

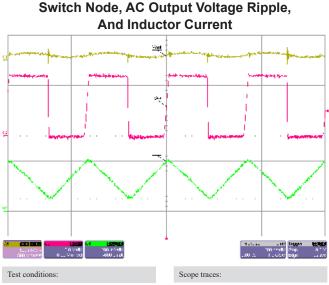

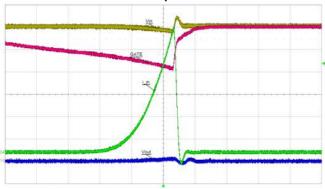

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string LED V<sub>REG</sub> = 0.85 V V<sub>IN</sub> = 12 V V<sub>OUT</sub> hysteresis = 0.45 V Dimming PWM duty cycle = 20% Polyphase mode = on

electrolytic,  $C_{OUT4} = 2.2 \ \mu\text{F}/$ 50 V 1206 ceramic,  $R_Z = 10 \ k\Omega$ ,  $C_Z = 5.6$

nF,  $C_P = 120 \text{ pF}$

C1 (Yellow) =  $V_{OUT}$  (500 mV, AC/div) C2 (Red) =  $V_{SW}$  (10 V/div) C4 (Green) =  $I_L$  (inductor current)(200 mA/ div) Time scale = 200 ns/div

A8522 evaluation PCB:

$\begin{array}{l} L_{1}=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_{Z}=10 \ k\Omega, \ C_{Z}=5.6 \\ nF, \ C_{p}=120 \ pF \end{array}$

6 7 8 9 10 11 12 13 14 15 16 17 18 V<sub>IN</sub>(V)

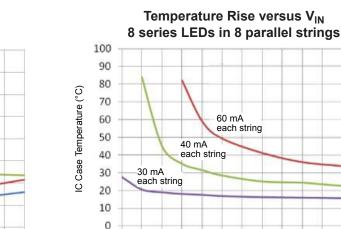

Test conditions:  $\label{eq:LED} \begin{array}{l} LED \mbox{ strings } = 8 \mbox{ parallel} \\ LEDs = 8 \mbox{ series each string} \\ f_{SW} = 2 \mbox{ MHz} \\ Dimming \mbox{ PWM duty cycle } = 100\% \\ Polyphase \mbox{ mode } = on \end{array}$

5

### A8522 evaluation PCB:

$\begin{array}{l} L_1=10 \ \mu H, \ C_{OUTS}=68 \ \mu F/50 \ V \ polymer\\ electrolytic, \ C_{OUT4}=2.2 \ \mu F/\\ 50 \ V \ 1206 \ ceramic, \ R_Z=10 \ k\Omega, \ C_Z=5.6 \\ nF, \ C_P=120 \ pF \end{array}$

####

Temperature Rise versus V<sub>IN</sub>

7 series LEDs in 8 parallel strings

LED strings = 8 parallel LEDs = 7 series each string  $f_{SW}$  = 2 MHz Dimming PWM duty cycle = 100% Polyphase mode = on

80

A8522

# Wide Input Voltage, Fault Tolerant, Independently Controlled Multi-Channel LED Driver with I<sup>2</sup>C Interface

## FAULT HANDLING

## **Input Overcurrent Protection**

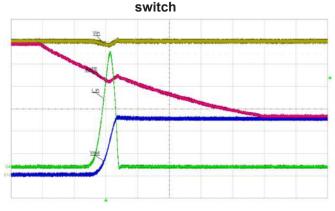

Case 1: Normal startup when using input disconnect

Case 2: Output-to-GND short fault occurred before startup

# Case 3: Output-to-GND short occurred during normal operation

#### Test conditions:

$\begin{array}{l} Q1 = AO4421 \\ C_{GS} = 10 \text{ nF} \\ V_{IN} = 12 \text{ V} \\ R_{SENSE} = 18 \text{ m}\Omega \end{array}$

GATE is being slowly pulled down (from  $V_{\text{IN}}$  to  $V_{\text{IN}}$  – 6.8 V) to control the inrush current.

#### Scope traces:

$\begin{array}{l} \text{C1 (Yellow)} = \textit{V}_{\text{IN}} \left( 2 \; \textit{V/div} \right) \\ \text{C2 (Red)} = \textit{V}_{\text{GATE}} \left( 2 \; \textit{V/div} \right) \\ \text{C3 (Blue)} = \textit{V}_{\text{OUT}} \left( 5 \; \textit{V/div} \right) \\ \text{C4 (Green)} = \textit{I}_{\text{IN}} \left( 1 \; \textit{A/div} \right) \\ \text{Time scale} = 200 \; \mu \text{s/div} \end{array}$

#### Test conditions:

$\begin{array}{l} Q1 = AO4421 \\ C_{GS} = 10 \text{ nF} \\ V_{IN} = 12 \text{ V} \\ R_{SENSE} = 18 \text{ m}\Omega \end{array}$

Startup into a VOUT-to-GND short. GATE is pulled high as soon as the input current > 5.8 A, in order to turn off the input disconnect switch.

#### Scope traces:

$\begin{array}{l} \text{C1 (Yellow)} = \text{V}_{\text{IN}} \left(2 \ \text{V/div}\right) \\ \text{C2 (Red)} = \text{V}_{\text{GATE}} \left(2 \ \text{V/div}\right) \\ \text{C3 (Blue)} = \text{V}_{\text{OUT}} \left(5 \ \text{V/div}\right) \\ \text{C4 (Green)} = \text{I}_{\text{IN}} \left(1 \ \text{A/div}\right) \\ \text{Time scale} = 50 \ \mu\text{s/div} \end{array}$

#### Test conditions:

$\begin{array}{l} Q1 = AO4421 \\ C_{GS} = 10 \text{ nF} \\ V_{IN} = 12 \text{ V} \\ R_{SENSE} = 18 \text{ m}\Omega \end{array}$

Output shorted to GND during normal operation, causing a huge inrush current. GATE is pulled high, in order to turn off the input disconnect switch and prevent damage to the power supply.

#### Scope traces:

$\begin{array}{l} \text{C1 (Yellow)} = \text{V}_{\text{IN}} \left(2 \text{ V/div}\right) \\ \text{C2 (Red)} = \text{V}_{\text{GATE}} \left(2 \text{ V/div}\right) \\ \text{C3 (Blue)} = \text{V}_{\text{OUT}} \left(5 \text{ V/div}\right) \\ \text{C4 (Green)} = \text{I}_{\text{IN}} \left(5 \text{ A/div}\right) \\ \text{Time scale} = 10 \ \mu\text{s/div} \end{array}$

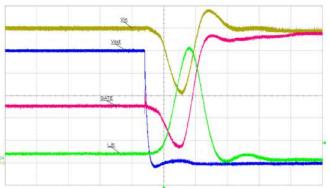

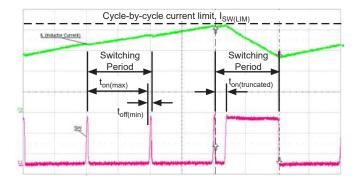

## **Switch Overcurrent Protection**

#### Test conditions:

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $f_{SW}$  = 1 MHz  $V_{IN}$  = 6.5 V

$V_{\rm IN}$  intentionally lowered to the point where SW cycle-by-cycle current limit is tripped. SW operating at maximum on-time initially. Inductor current ramps up and trips cycle-by-cycle current limit (= 4.2 A). Present on-time is truncated immediately. Next switching cycle starts normally.

#### Scope traces:

C2 (Red) =  $V_{SW}$  (10 V/div) C4 (Green) =  $I_L$  (1 A/div) Time scale = 500 ns/div

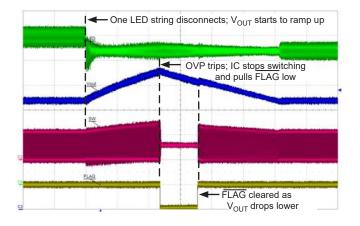

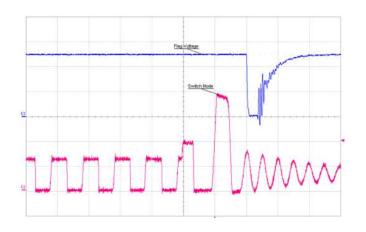

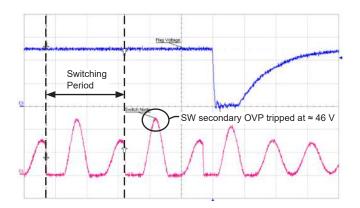

## **LED String Open Fault Detection**

#### Test conditions:

LED strings = 8 parallel, 60 mA each LEDs = 7 series each string  $f_{SW}$  = 2 MHz  $V_{IN}$  = 12 V

One LED string is disconnected during normal operation. After output trips OVP, the offending LED string is removed from regulation, while other strings continue to function correctly.

#### Scope traces:

$\begin{array}{l} \text{C1 (Yellow)} = \text{V}_{\text{FLAG}} \left( 5 \text{ V/div} \right) \\ \text{C2 (Red)} = \text{V}_{\text{SW}} \left( 10 \text{ V/div} \right) \\ \text{C3 (Blue)} = \text{V}_{\text{OUT}} \left( 5 \text{ V/div} \right) \\ \text{C4 (Green)} = \text{I}_{\text{LED}} \left( 100 \text{ mA/div} \right) \\ \text{Time scale} = 200 \ \mu\text{s/div} \end{array}$

## Protection Against Open/Missing BOOST Diode

Case 1: BOOST diode becomes open during normal operation

## Case 2: BOOST diode missing during startup

#### Test conditions:

BOOST diode becomes open during normal operation. Energy stored in inductor causes a high voltage across SW. SW DMOS conducts at V<sub>SW</sub> > 75 V to discharge the energy safely. IC shuts off after detecting an overvoltage condition at the SW pin.

#### Scope traces:

C2 (Red) =  $V_{SW}$  (20 V/div) C3 (Blue) =  $V_{FLAG}$  (2 V/div) Time scale = 500 ns/div

#### Test conditions:

BOOST diode is missing during startup. Energy stored in inductor gradually builds up, causing higher and higher voltage across the SW pin. Eventually the IC shuts off after detecting an overvoltage fault at the SW pin ( $V_{SW} > 50$  V).

#### Scope traces:

C2 (Red) =  $V_{SW}$  (20 V/div) C3 (Blue) =  $V_{FLAG}$  (2 V/div) Time scale = 200 ns/div

## FUNCTIONAL DESCRIPTION

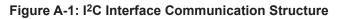

The A8522 is an I<sup>2</sup>C programmable, multi-channel LED driver for automotive lighting applications. It incorporates a currentmode boost controller with internal DMOS boost switch, and 8 integrated current sinks to regulate currents through up to 8 LED strings. Each LED string can be independently enabled or disabled, with its own LED current and PWM duty cycle programmed through I<sup>2</sup>C registers.

## **Enabling the IC**

The IC turns on when a logic high signal,  $V_{EN(H)}$ , is applied on the EN pin, and the input voltage present on the VIN pin is greater than the UVLO threshold,  $V_{INUV(ON)}$ . The EN pin is rated for 40 V, so it can be tied directly to  $V_{IN}$  for certain applications (see Application Information section). In addition, if the FSET/SYNC pin is pulled low, the IC does not power up.

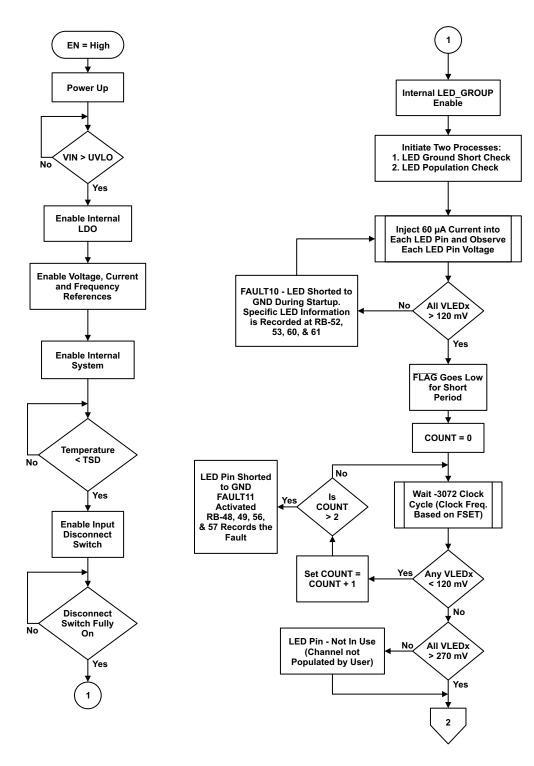

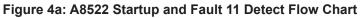

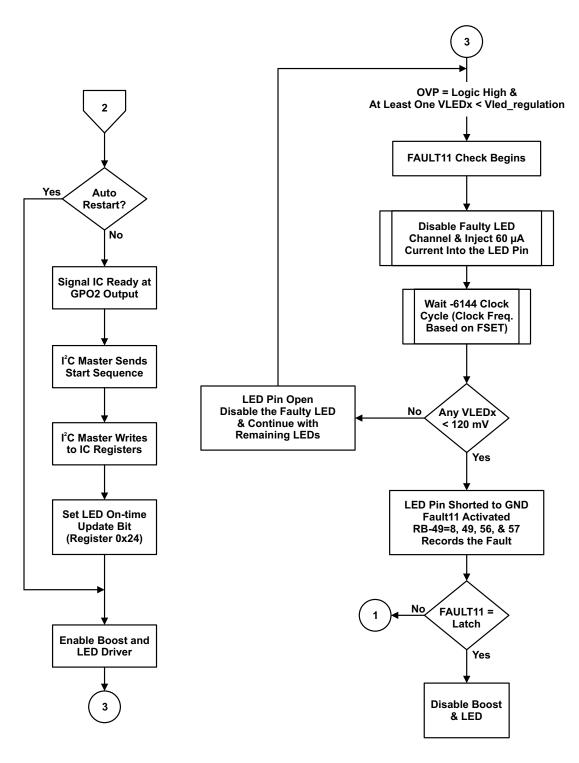

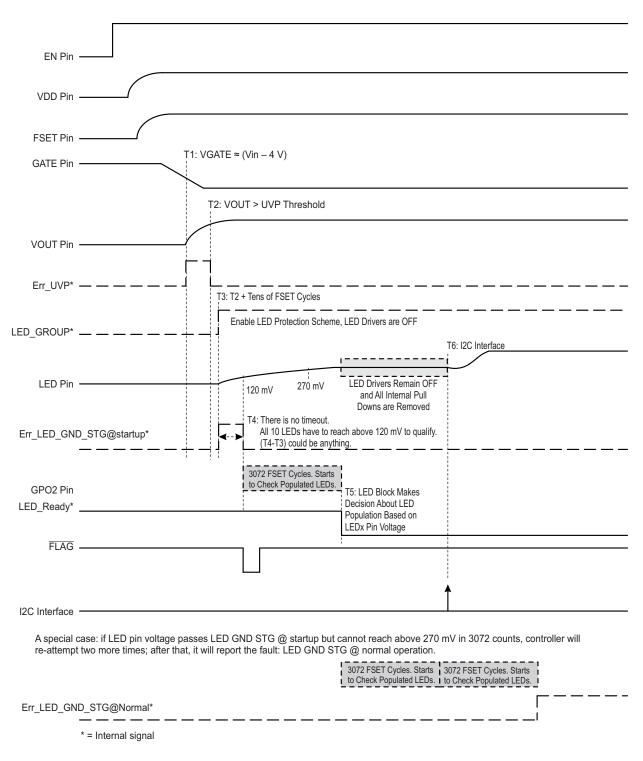

The A8522 performs a detailed startup sequence, flow chart and timing diagram are shown in figures 4a to 4c. Before the LEDs are enabled, the device goes through a system check to determine if there are any possible fault conditions that might prevent the system from functioning correctly. Once the LEDs pass the "LED short during start up" test the FLAG pin will be pulled low for a short period of time. If no subsequent faults are detected during this startup sequence, the IC pulls down the GPO2 pin to signal to the system controller that the A8522 is ready to receive I<sup>2</sup>C commands.

The system controller programs the A8522 internal registers through I<sup>2</sup>C Write commands, in order to configure individual LED strings before they can be turned on. On initial startup I<sup>2</sup>C should first send a clear command to bit 2 of register bank number 56, this ensures that an erroneous fault does not prevent the LEDs turning on. This command is only required on power up and/or enable (via EN pin) of the A8522. I<sup>2</sup>C can now communicate regularly with the A8522. Ensure I<sup>2</sup>C only enables populated LED's. If I<sup>2</sup>C tries to enable unpopulated LED strings an illegal action is declared and no LEDs will turn on.

In the event of a genuine fault during start up, the  $\overline{FLAG}$  pin is pulled low, and the system controller can issue I<sup>2</sup>C Read commands to investigate the status of fault registers. In this instance I<sup>2</sup>C should not clear bit 2 of register bank number 56.

The device enters into shutdown mode when the EN pin is pulled low,  $\mathrm{V}_{\mathrm{EN}(\mathrm{L})}.$

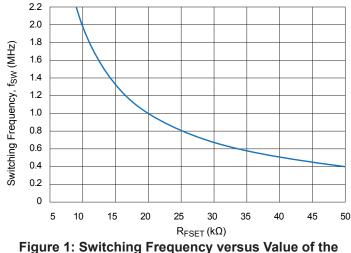

## **Frequency Selection and Synchronization**

The internally-generated switching frequency of the boost converter,  $f_{SW}$ , is set by the resistor  $R_{FSET}$ , connected from the FSET/SYNC pin to GND. The frequency can be set in the range from 400 kHz to 2.3 MHz. The switching frequency is determined according to the following equation:

$$f_{SW}(MHz) = 19.9 / R_{FSET}(k\Omega) + 0.01$$

(1)

Figure 1 illustrates how  $f_{SW}$  varies with  $R_{FSET}$ .

Alternatively, the switching frequency can also be synchronized using an external clock signal on the FSET/SYNC pin. The external clock should be a logic signal between 400 kHz and 2.3 MHz. When an external clock is applied, the  $R_{FSET}$  resistor is ignored. If the A8522 is started up with a valid external SYNC signal, but the SYNC signal is lost during normal operation, then one of the following happens:

- If the external SYNC signal becomes high impedance (open), the A8522 waits for approximately 6 μs from the last edge detected, before it resumes normal operation at the switching frequency set by RFSET. No fault flag is generated.

- 2. If the external SYNC signal gets stuck low (shorted to ground), the A8522 will still attempt to operate at switching frequency set by RFSET. However, since RFSET is shorted to GND by the external SYNC signal, it will trip the FSET to GND short fault and shut down the output. The Fault Flag is pulled low in this case.

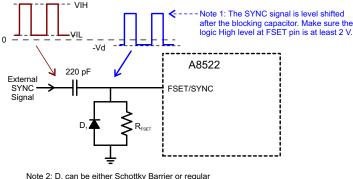

To avoid the outcome of the second scenario above, the circuit shown in Figure 2 can be used. In this case, after the external SYNC signal goes low, the A8522 will continue to operate normally at the switching frequency set by  $R_{FSET}$ .

silicon diode. Schottky has the advantage of lower Vd, but it suffers from higher leakage current at hot.

## Figure 2: Low FSET\_SYNC Signal Fault Counteraction Circuit

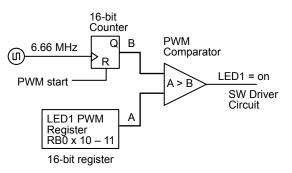

## **PWM Dimming**

The PWM dimming period (hence the PWM frequency) is defined by the 13-bit PWM\_Period register. It is programmable at any time through the I<sup>2</sup>C interface, in 1.5  $\mu$ s increments, as:

$$PWM\_Period = (N+1) \times 1.5 \ (\mu s) \tag{2}$$

where N is the value contained in the register.

The PWM on-time (hence the PWM duty cycle) for each LED string is defined by the corresponding 16-bit register. The PWM on-time can be adjusted in 0.15  $\mu$ s increments. This is illustrated in Figure 4. The smallest PWM on-time is 1  $\mu$ s. This corresponds to a 5000:1 ratio at a 200 Hz PWM frequency.

## **Output Current and Voltage**

The current through each LED string can be programmed through  $I^2C$  registers to between 1 and 64 mA, in 1 mA steps.

For optimal efficiency, the output of the boost stage is dynamically adjusted to the minimum voltage required for all active LED strings. This is expressed by the following equation:

$$V_{OUT} = MAX(V_{LED1}, V_{LED2}, \dots V_{LED8}) + V_{REG} + V_{HYST}$$

(3)

where

$V_{LEDx}$  is the voltage drop across an LED string (only the enabled LED strings are considered),

$V_{REG}$  is the regulation voltage of the LED current sink (0.85 V (typ)), and

$V_{\rm HYST}$  is the hysteresis control voltage at the output (typically 0.25 V).

The boost output voltage is protected by the OVP threshold, which can be programmed up to 39 V. This is sufficient for driving up to 10 white LEDs in series.

Figure 3: PWM On-time Comparator Circuit

# A8522

# Wide Input Voltage, Fault Tolerant, Independently Controlled Multi-Channel LED Driver with I<sup>2</sup>C Interface

Figure 4b: A8522 Startup and Fault 11 Detect Flow Chart (Cont.)

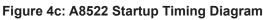

## **Boost Frequency Dithering**

The Boost Dithering function allows the user to randomize the main switching frequency within a certain frequency range. By shifting the main switching frequency of the regulator in a pseudo-random fashion around the main switching frequency, the overall system noise magnitude can be greatly reduced. Note that the frequency dithering function is not available when an external synchronization signal is used at the FSET/SYNC pin.

This spread spectrum functionality is achieved by a programmable register (0x05[BD1:BD0]. A non-zero number enables the boost dithering and sets the modulation index of 5%, 10%, or 15% of  $f_{SW}$ . For example, if 10% dithering is selected, then the switching frequency will jump between a low of 1.8 MHz and a high of 2.2 MHz, as governed by the pseudo-random pattern.

Every two switching cycles, the switching frequency may randomly jump between low and high levels. The random pattern repeats itself after 92 switching cycles. This is illustrated by the timing diagram in Figure 5.

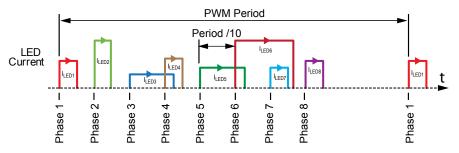

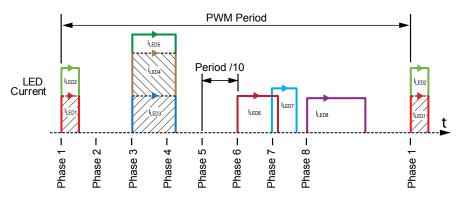

## Polyphase Grouping

During PWM operation, by default each of the ten LED channels starts at a separate time slot, or phase, (Figure 6, top panel) and with a specified on-time setting. If required, two or more adjacent LED channels can be grouped by programming to turn on and off simultaneously (Figure 6, bottom panel). By tying the corresponding pins together on the PCB, it is possible to combine several channels to drive higher-current LED strings (see Typical Application schematics).

Each LED channel has an LED channel enable bit (register 0x01) and an LED PWM on-time setting register (0x10 to 0x1F). In normal PWM operation, any enabled LED channel is turned on starting at its own time slot, and remains on for the duration controlled by its own PWM on-time register. By staggering the time slots for LED channels, the input ripple current is reduced during PWM operation.

If necessary, such as when more than 1 channel is required to drive an LED string at current higher than 60 mA, the user can group two or more adjacent LED channels together, so that they turn on/off simultaneously. Grouping is done by setting the corresponding bits in the Polyphase Grouping registers (0x08 and 0x09).

Figure 5: A8522 Dithering Scheme at 2 MHz ±10%

(frequency jumps between 1.8 MHz and 2.2 MHz, as governed by a 46-bit pseudorandom pattern)

A grouped LED channel starts in the same time slot as the lowernumbered channel, and inherits the PWM Dimming On-Time of that lower-numbered channel (the original time slot of the grouped channel is not used). If more than one adjacent channels are grouped, the entire group starts at the time slot of the lowestnumbered channel in the group, and inherits that on-time setting.

For example, in Figure 6, LED1 and LED2 are grouped together, so they start at PWM slot 1 and follow the on-time of LED1. Similarly, LED3, LED4, and LED5 are grouped together, so they start at PWM slot 3 and follow the on-time of LED3.

If the first LED channel in a polyphase group is disabled through the LED enable register, then all the LEDs in this group are disabled. If any other LED channels in a group are disabled, all of the other LED channels in the group remain enabled, with the PWM on-time of the first LED channel in the group.

## **Boost Output Voltage Regulation**

Output from the boost stage is adaptively adjusted, based on the voltage required by all the enabled LED strings. This ensures minimum power loss at the LED current sinks, and reduces input power consumption.

During operation, the LED string with the highest voltage drop is the dominant string, and it is used to determine the boost output voltage regulation. Because each LED string can be individually enabled/disabled dynamically, which string is dominant can shift at different times.

As an example, assume LED channels 1, 3, and 5 are currently enabled. Further assume that voltage drops across the LED strings are 21 V, 23 V, and 25 V respectively. The boost output voltage will be regulated to the highest LED string voltage (25 V)

Polyphase PWM Operation without Grouping – Each LED channel turns-on at a separate, sequential, periodic time slot. The LED on-times are individually programmable, so any individual phase can overlap later time slots. The LED current for each channel is individually programmed.

Polyphase PWM Operation with Grouping – The starting time slot and the PWM on-time for each group is determined by the time slot and the on-time of the lowest-numbered channel within that group, so all LED channels in the same group turn-on and turn-off together. Each time slot is sequential and periodic, and unused time slots are maintained. Any individual phase can overlap later time slots. The LED current for each channel is individually programmed, regardless of grouping.

## Figure 6: Polyphase Operation

plus the regulation voltage required by the LED current sink (0.85 V typical):

| LED Chan-<br>nel # | LED String<br>Voltage Drop<br>(V) | Boost Output<br>Voltage<br>(V) | LEDx Pin Volt-<br>age<br>(V) |

|--------------------|-----------------------------------|--------------------------------|------------------------------|

| 1                  | 21                                |                                | 4.85 min                     |

| 3                  | 23                                | 25.85 +<br>Hysteresis          | 2.85 min                     |

| 5                  | 25 (dominant)                     | yotor oolo                     | 0.85 min                     |

For LED strings 1 and 3, the extra voltage is absorbed by their current sinks. When the LED string voltages are poorly balanced (as in this example), excessive power loss can build up at the current sinks. Consider adding ballast resistors to the LED strings with lower voltage drops, so that less heat is dissipated by the IC.

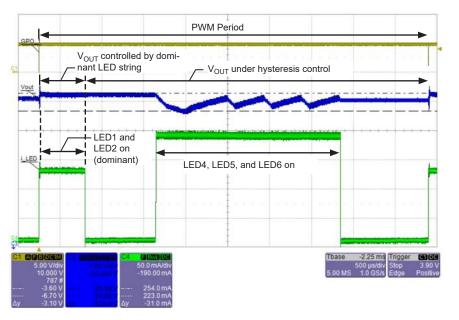

## **Output Hysteresis**

The A8522 superposes a minimum output hysteresis of 0.25 V on top of the LED regulation voltage. The OVP pin provides output voltage feedback during hysteresis control mode. An example of output voltage is show in Figure 7.

When the dominant LED is on, boost stage starts switching to keep the corresponding LEDx pin voltage regulated to  $V_{REG}$ . After the dominant LED is turned off, the switching continues until boost output reaches  $V_{TH(+)}$ . The output is then regulated between  $V_{TH(-)}$  and  $V_{TH(+)}$  through hysteresis control, before the next time dominant LED is on again.

## Soft Start Timing

The soft-start function performs the following sequence of opertion:

- 1. At startup, the boost stage initially switches at the minimum SW on-time continuously. This allows output voltage to build-up, even at the minimum PWM duty cycle.

- 2. The switch on-time increases as the COMP pin voltage starts to rise (the COMP voltage controls the boost stage switching duty cycle, which in turn controls the boost output voltage).

- 3. Soft start ramp duration is 100 ms, which allows the LED to cycle 10 times at a 100 Hz PWM frequency.

- 4. Soft start can finish earlier, either due to the LED current reaching regulation, or because output voltage reaches 90% of OVP.

- 5. To prevent output voltage from reaching 90% of OVP prematurely (while the COMP voltage is still too low), the design should ensure there is sufficient output capacitance, such that it takes longer to build up  $V_{OUT}$  at the minimum SW on-time.

- 6. During soft start, the PWM on-time needs to be at least  $1.5 \ \mu s$  to guarantee reliable detection once LED current reached regulation. If the startup on-time is set lower (at 1  $\mu s$ , for example), soft start may be terminated later when output reached 90% OVP level.

It is important not to set OVP level too much higher than the normal operating voltage of LED strings. In particular, make sure that:

$$V_{LED} + V_{REG} < V_{OVP} < V_{LED} + V_{REG} + V_{SD}$$

where  $V_{LED}$  is the worst-case/highest voltage drop across LED strings.  $V_{REG}$  is the LED pin regulation volatge (around 1 V).  $V_{SD}$  is the LED string short-detect threshold (programmable between 5 and 12 V).

For Boost configuration with 7 to 10 LEDs in series, OVP is typically set at  $\sim$ 5 V above the worst-case LED string voltage. For SEPIC configuration with lower number of LEDs in series, OVP may be set closer to the LED voltage.

## Input Disconnect Switch

The A8522 has a gate driver for an external PMOS that can be used to provide an input disconnect protection function. During normal startup, the PMOS is turned on gradually to avoid large inrush current. In the event there is a direct short at the boost stage (either SW or VOUT shorted to GND), high input current will cause the PMOS to turn off.

The input disconnect current threshold is calculated by:

$$I_{INMAX} = V_{INS(TH)} / R_{INS}$$

<sup>(4)</sup>

where  $V_{INS(TH)} = 105 \text{ mV}$  (typ).

Under normal operation, the input current is protected by the cycle-by-cycle boost switch current limit. Only in case of a direct short at boost output or SW pin will the input disconnect switch be activated. Therefore the input disconnect current threshold is typically set slightly higher than the switch current limit. For example, choose  $R_{INS} = 0.02 \ \Omega$  to set  $I_{INMAX} = 5.25 \ A$  approximately.

During normal power-up sequence, as soon as EN goes high, the GATE pin will start to be pulled low by a  $115 \ \mu A (typ)$  current.

# A8522

# Wide Input Voltage, Fault Tolerant, Independently Controlled Multi-Channel LED Driver with I<sup>2</sup>C Interface

How quickly the external PMOS turns on depends on the gate capacitance,  $C_{GS}$ , of the PMOS. If the gate capacitance is very low, the inrush current may still exceed 5 A momentarily and trip the input disconnect protection. In this case, an external  $C_{GS}$  may be added to slow down the PMOS turn-on. A typical value of 10 nF should be sufficient in most cases.

When selecting the external PMOS, check for the following parameters:

• Drain-source breakdown voltage:  $B_{VDSS} > -50 V$

- Gate threshold voltage: ensure it is fully enhanced at  $V_{GS} = -4$  V, and cut-off at -1 V

- $R_{DS(on)}$ : ensure the on-resistance is rated at  $V_{GS} = -4.5$  V or similar, not at -10 V; derate it for higher temperatures

The PMOS gate voltage is clamped by the A8522 such that  $V_{GS} = V_{IN} - V_{GATE} \leq 8$  V. This is to prevent the gate-source of external PMOS from breaking down due to higher input voltage. In case of very low input voltage, however,  $V_{GS}$  is limited by  $V_{IN}$ . Therefore it is important to select a PMOS with a lower gate threshold voltage.

LED1 and LED2 = 8 series (dominant LED string), LED4, LED5, LED6 = 7 series All other channels disabled 60 mA each enabled channel LED V<sub>REG</sub> = 0.85 V V<sub>IN</sub> = 12 V V<sub>OUT</sub> hysteresis = 0.25 V

#### Scope traces:

C1 (Yellow) =  $V_{GPO1}$  PWM period (5 V/div) C3 (Blue) =  $V_{OUT}$  (1 V/div, offset = 24 V) C4 (Green) = Total I<sub>LEDx</sub> (50 mA/div) Time scale = 500 µs/div

#### A8522 evaluation PCB:

$\begin{array}{l} L_1 = 10 \ \mu\text{H}, \ C_{\text{OUT5}} = 68 \ \mu\text{F}/50 \ \text{V} \ \text{polymer} \\ \text{electrolytic}, \ C_{\text{OUT4}} = 2.2 \ \mu\text{F}/ \\ 50 \ \text{V} \ 1206 \ \text{ceramic}, \ R_Z = 10 \ \text{k}\Omega, \ C_Z = 5.6 \ \text{nF}, \\ C_P = 120 \ \text{pF} \end{array}$

## **System Failure Detection and Protection**

The A8522 is designed to detect and protect against a multitude of system-level failures. Some of those possible faults are illustrated in Figure 8 and the A8522 is described in Table 1.

Figure 8: Examples of System Fault Modes

## Table 1: System Failure Mode

| Failure Mode                                 | Symptom                                                                  | Protected? | A8522 Response                                                    |

|----------------------------------------------|--------------------------------------------------------------------------|------------|-------------------------------------------------------------------|

| Inductor open                                | Output undervoltage fault detected at startup                            | Yes        | Will not proceed with startup                                     |

| Inductor shorted                             | Excessive current through SW pin during switching, secondary OCP tripped | Yes        | Shuts down and will not retry                                     |

| Diode open                                   | Excessive voltage detected at SW pin, secondary OVP tripped              | Yes        | Shuts down and will not retry                                     |

| Diode shorted                                | Excessive current through SW pin during switching                        | Yes        | Shuts down and will not retry                                     |

| Output shorted to GND                        | Input overcurrent protection tripped at startup                          | Yes        | Shuts off input power via input disconnect switch                 |

| LED string open or<br>LEDx pin open          | IC unable to detect LED current, output ramps up and trips OVP           | Yes        | Disable offending LED string, other strings continue to operate   |

| LEDs shorted within one string               | Excessive voltage drop at LEDx pin                                       | Yes        | Disable offending LED string, other strings continue to operate   |

| LEDx pin to GND short<br>at startup          | Detected LED pin to GND short during startup error check                 | Yes        | Will not proceed until fault is removed                           |

| LEDx pin to GND short during operation       | IC unable to detect LED current, output ramps up and trips OVP           | Yes        | Shuts down and rechecks for pin to GND short before restart       |

| FSET pin to GND short<br>or FSET pin open    | IC unable to start switching                                             | Yes        | Will not restart until fault is removed                           |

| External synchronization signal disconnected | Unable to detect logic signal at FSET pin                                | Yes        | Falls back to switching frequency determined by R <sub>FSET</sub> |

## Fault Handling

The A8522 can detect and monitor 12 different fault modes internally. Some can be programmed for latching (flag set, system controller action required) or for auto restart after flag set and condition cleared. Faults are listed in Table 2.

In the event of a fault, registers 0x38 and 0x39 hold the fault status to allow the master to read what type of fault (such as OCP, OVP, open LED, and so forth) has been detected.

## **Internal State Monitoring**

There are two general-purpose output pins, GPO1 and GPO2, that can be programmed to monitor selected internal status bits directly. This allows those pins to be used as special IRQ (interrupt request) lines for the system. The system can also monitor non-critical fault occurrences (such as temperature warning or SW current limit) while the IC continues to run. GPO1 and GPO2 are open-drain outputs, and an external pull-up resistor is required at each pin to set the logic-high level required.

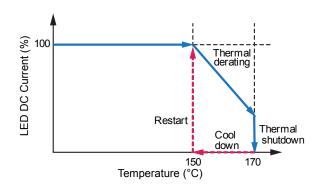

## LED Thermal Shutdown and Derating

The A8522 TSD (Thermal Shutdown) threshold is set to  $170^{\circ}$ C (typ). If the die temperature reaches the TSD threshold, boost and LED drivers are disabled. The IC will restart after the die temperature has fallen to  $20^{\circ}$  C below the TSD threshold.

The A8522 also has an optional thermal derating function controlled by a register bit. The LED derating bit enables or disables the Thermal Derating feature, which cuts-back on LED current when the die temperature gets too close to the thermal shutdown threshold. When enabled, the LED current starts decreasing as die temperature rises above 20°C from TSD. The Thermal Derating feature is disabled by default, which means the IC will continue to operate at full LED current until the TSD threshold is reached. Current derating is illustrated by Figure 9.

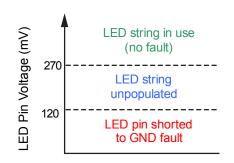

# LED Pin Short to GND Check Before Startup

When the IC is enabled for the first time, it checks to determine if any LED pins are shorted to GND and/or are not used (LED string not populated). An internal 60  $\mu$ A current source pulls all LED pin voltages high. Any LED pin with voltage below 120 mV is considered shorted to GND. Any LED pin with voltage above 270 mV is considered in use (see Figure 9). If any LED channel is unused, that LED pin must be connected to GND through a 4.7 k $\Omega$  resistor (note: there is an internal gated parallel resistor of 8 k $\Omega$ , so the combined sense resistance is 3 k $\Omega$ ). The user can further disable any LED channel through I<sup>2</sup>C programming. All unused LED channels are taken out of regulation at this point and will not contribute to the boost regulation loop. If any LED pin is shorted to ground, the IC will not proceed with soft start until the short is removed for the LED pin. This prevents the A8522 from powering up and putting an uncontrolled amount of current through the LEDs.

## Figure 9: Thermal Derating and Shutdown Protection Features

# Figure 10: A8522 LED Short-to-GND Check Before Startup

## LED Pin Open/Short Fault During Normal Operation

During startup and normal operation, all enabled LED channels are supposed to ramp up in current until each channel regulation target is reached. If any channel is below regulation, it will request the boost output voltage to rise, so the higher voltage can help more current to flow through its LED string. But in the event that an LED pin is either open or shorted to ground, there can be no current flowing through its LED driver. The boost voltage will continue to rise until the OVP fault is tripped.

This function is used in conjunction with general fault 8 (overvoltage protection), so it can be monitored by the I<sup>2</sup>C master. When this bit is set to 0, the corresponding LED channel is within regulation and operating correctly (or the LED channel has been previously disabled). When the OVP fault is tripped the bit is set to 1.

When the OVP fault is tripped, any enabled LED channel that is not in regulation is tested for ground-short again:

• If an unregulated channel is shorted to ground, the boost stage is shutdown completely and will not attempt auto-restart. This

is to prevent uncontrolled current from flowing through the LED string. Fault flag is set to signal an LED to GND short fault (#11). The corresponding bit in the LED Pin Shorted to GND status register is set. The user can then read this register to determine which LED channel is shorted.

• If an unregulated channel is not shorted to ground, the IC will remove the offending channel from regulation, and resume normal operation for other channels. The FLAG pin (which was previously set to signal an OVP fault) is then cleared. The corresponding bit in the Latched Status LEDs in Regulation registers (0x3A and 0x3B) is set. The user can then read this register to determine which LED channel is open.

## Note:

If the OVP level is programmed too low in the OVP Threshold register for the LED string with highest forward voltage, the LED driver may not be able to reach regulation during startup. In this case, the IC will treat the LED pin as open. The offending LED pin is removed from regulation and the rest of the

LED channels will resume normal operation.

## **Table 2: Internal Fault Modes**

| Number and<br>Name                                                                                                                                                                                                                                                | Default Action                                                       | Programmable?                                                            | Input Disconnect<br>Switch                                                                                                      | Boost Switch                                                              | LED Current                                                           | FLAG Set<br>on Fault?                                               |

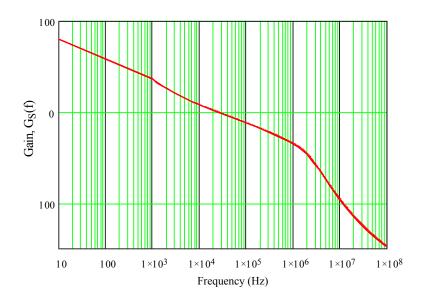

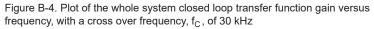

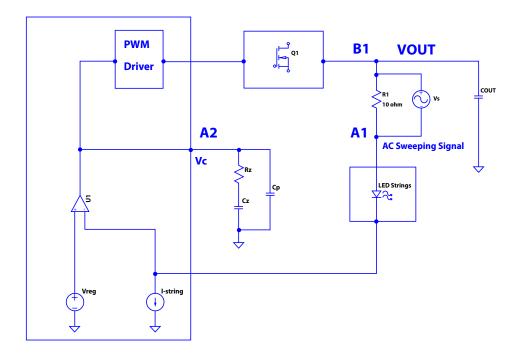

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|