# **1** General description

The VR5500 is an automotive high-voltage multi-output power supply integrated circuit, with focus on Radio, V2X, and Infotainment applications. It includes multiple switch mode and linear voltage regulators. It offers external frequency synchronization input and output, for optimized system EMC performance and it is qualified in compliance with AEC-Q100 rev H (Grade1, MSL3).

Several device versions are available, offering choice in number of output rails, output voltage setting, operating frequency, and power up sequencing, to address multiple applications.

# 2 Features and benefits

- 60 V DC maximum input voltage for 12 V and 24 V applications

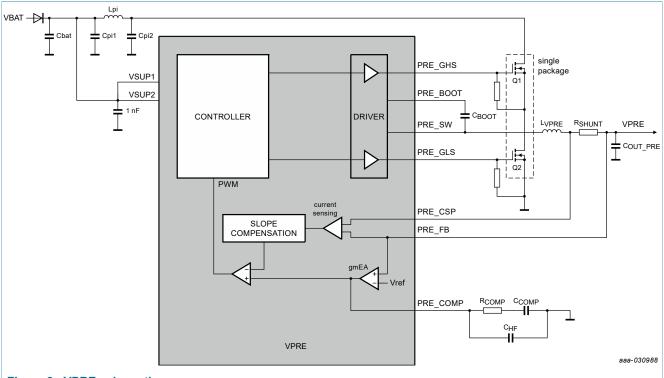

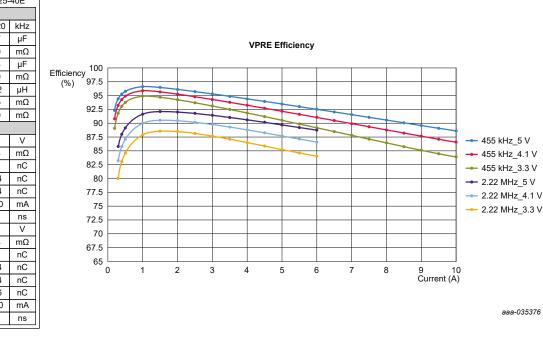

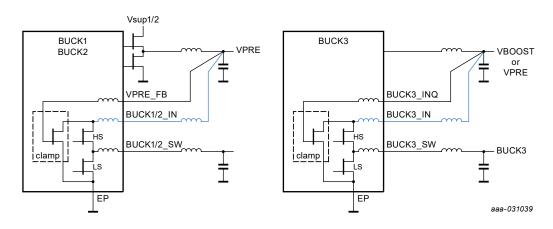

- VPRE synchronous buck controller with external MOSFETs. Configurable output voltage, switching frequency, and current capability up to 10 A peak.

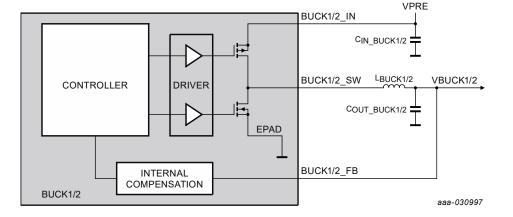

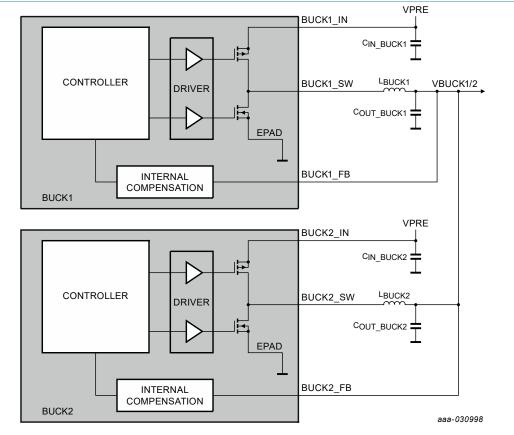

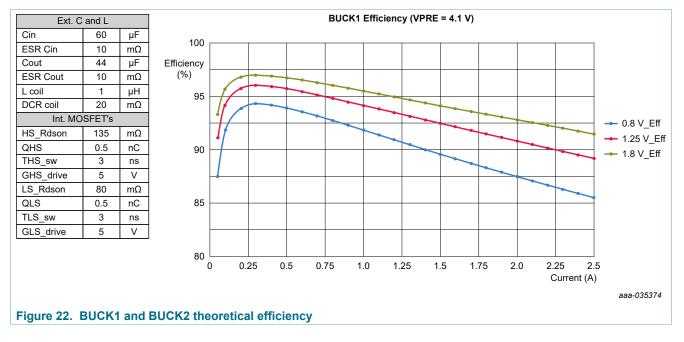

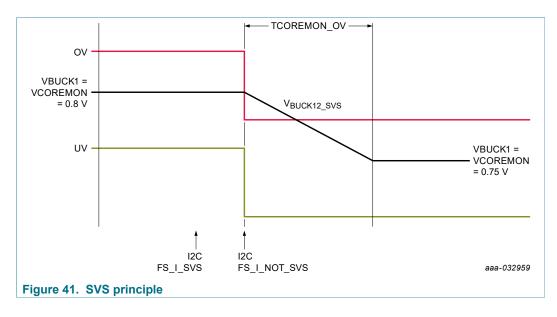

- Low voltage integrated synchronous BUCK1 converter, dedicated to MCU core supply with SVS capability. Configurable output voltage and current capability up to 3.6 A peak.

- Low voltage integrated synchronous BUCK2 converter. Configurable output voltage and current capability up to 3.6 A peak. Multi-phase capability with BUCK1 to extend the current capability up to 7.2 A peak on a single rail. Static voltage scaling capability.

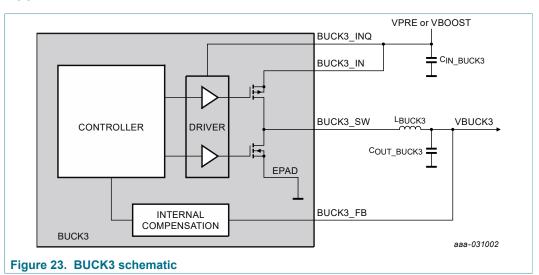

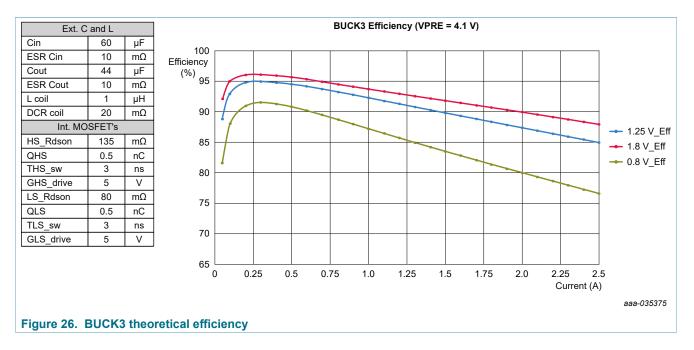

- Low voltage integrated synchronous BUCK3 converter. Configurable output voltage and current capability up to 3.6 A peak.

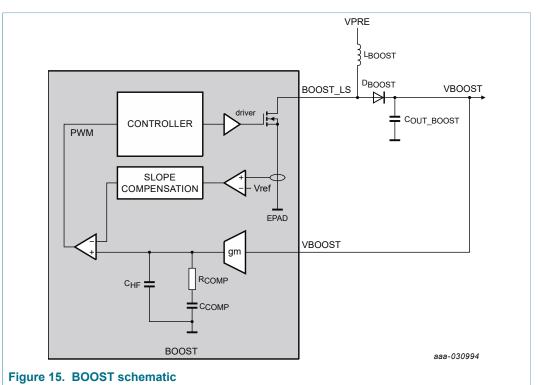

- BOOST converter with integrated low-side switch. Configurable output voltage and max input current up to 1.5 A peak.

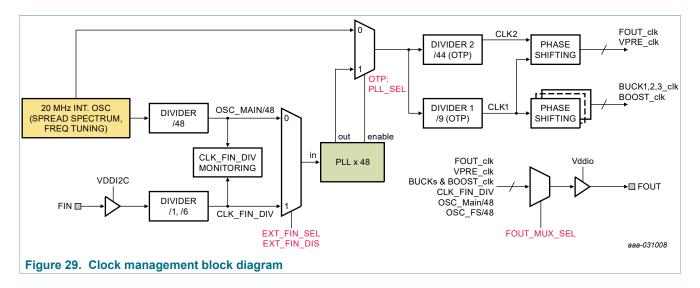

- EMC optimization techniques including SMPS frequency synchronization, spread spectrum, slew rate control, manual frequency tuning

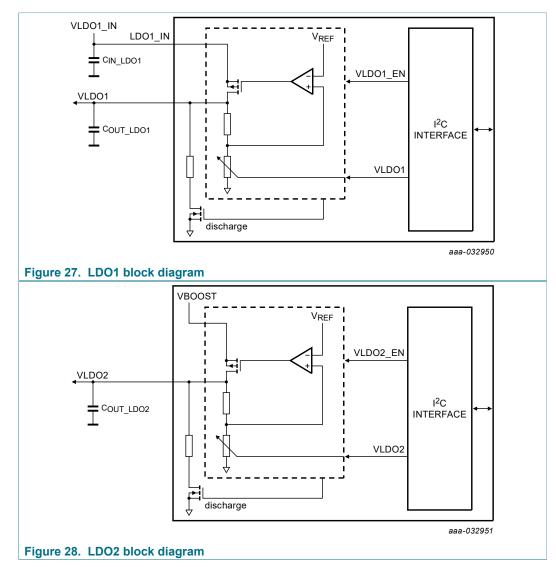

- Two linear voltage regulators for MCU IOs and ADC supply, external physical layer. Configurable output voltage and current capability up to 400 mA DC.

- OFF mode with very low sleep current (10 µA typ)

- Two input pins for wake-up detection and battery voltage sensing

- Device control via I2C interface with CRC

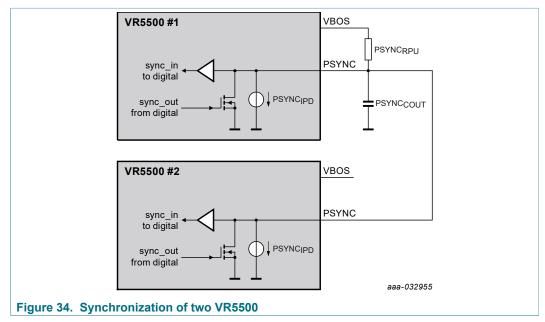

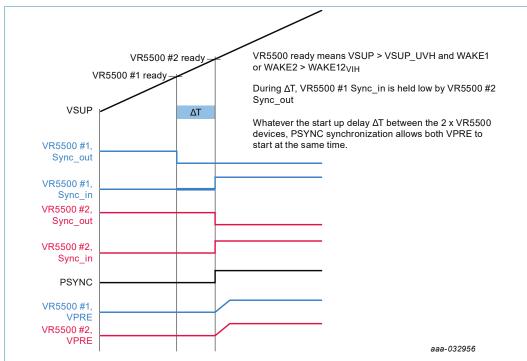

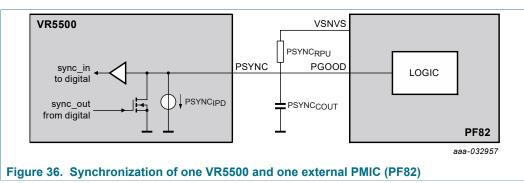

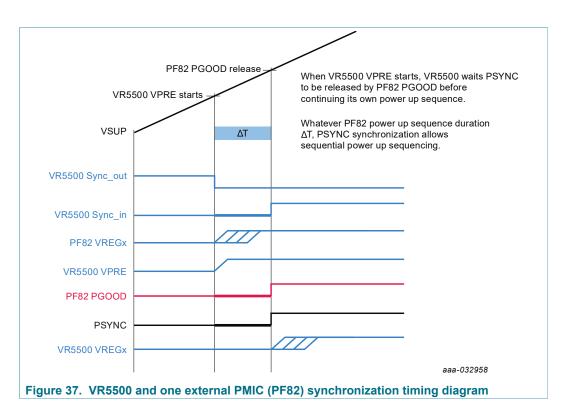

- Power synchronization pin to operate two VR5500 devices or VR5500 plus an external PMIC

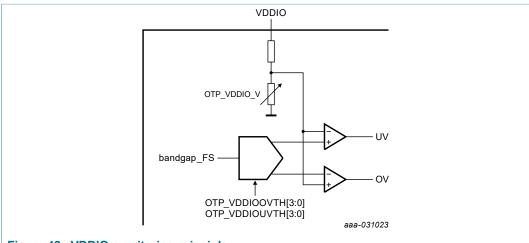

- Three voltage monitoring circuits, dedicated interface for MCU monitoring, power good, reset, and interrupt outputs

- Configuration by OTP programming. Prototype enablement to support custom setting during project development in engineering mode.

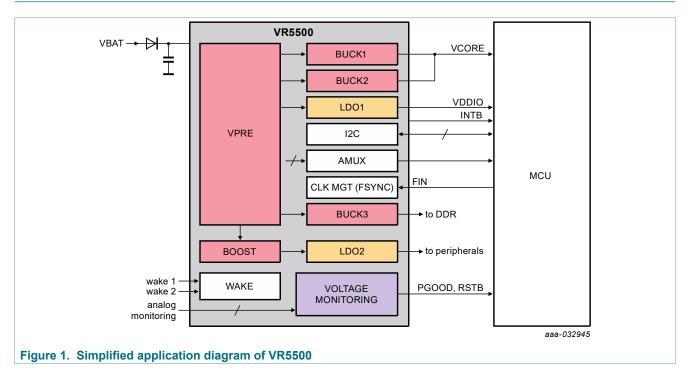

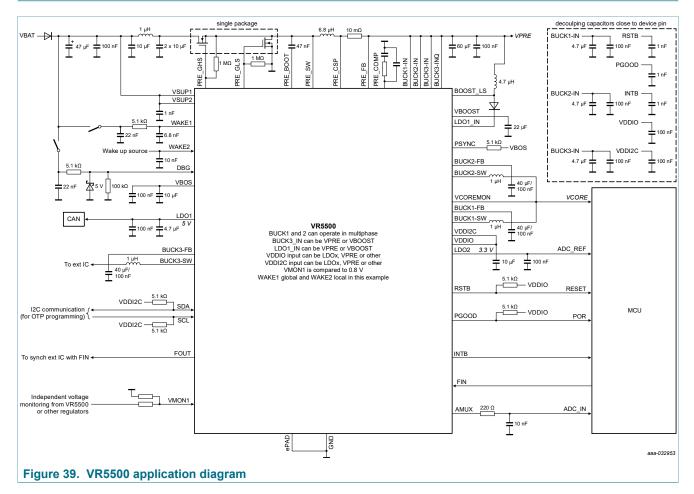

# 3 Simplified application diagram

# 4 Ordering information

#### Table 1. Ordering information

| Part number <sup>[1]</sup> | Package |                                                       | OTP ID     |                                              |

|----------------------------|---------|-------------------------------------------------------|------------|----------------------------------------------|

|                            | Name    | Description                                           | Version    |                                              |

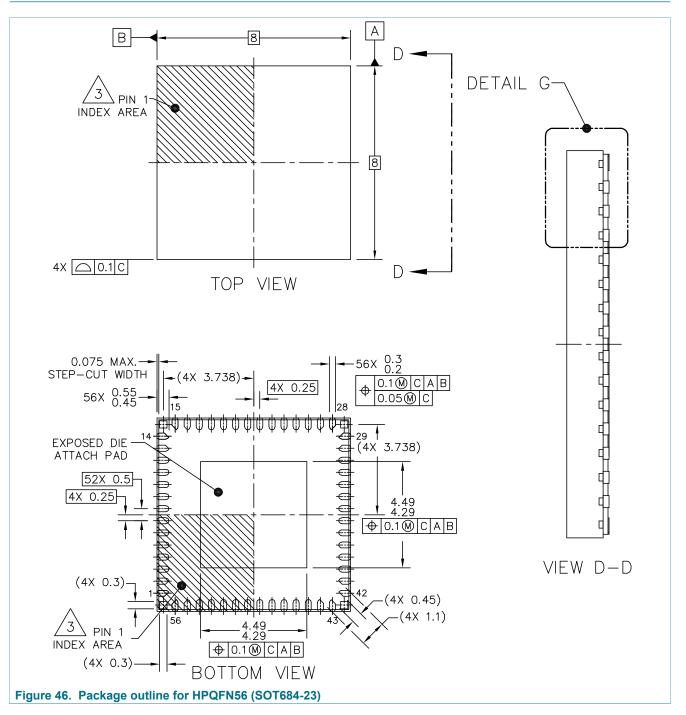

| MC33VR5500V0ES [2]         |         | HPQFN56, plastic, thermally enhanced                  | 0.07004.00 | —                                            |

| MC33VR5500V1ES [3]         | HPQFN56 | very thin quad flat package, no lead, wettable flanks | SOT684-23  | http://www.nxp.com/MC33VR5500V1ES-OTP-Report |

[1] To order parts in tape and reel, add the R2 suffix to the part number.

[2] V0: Non-programmed part

[3] V1: Radio mercury reference design

V0 part is a non-programmed OTP configuration. Pre-programmed OTP configurations (other than BUCK regulators) are managed through suffix V1 to XZ.

# **5** Applications

- Radio

- V2x

- Infotainment

# **VR5500**

High voltage PMIC with multiple SMPS and LDO

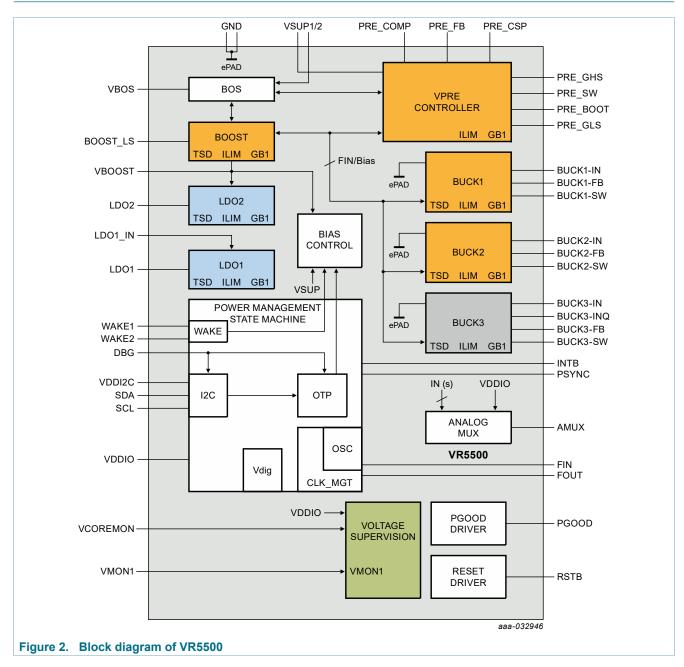

# 6 Block diagram

VR5500 Product data sheet

# **VR5500**

High voltage PMIC with multiple SMPS and LDO

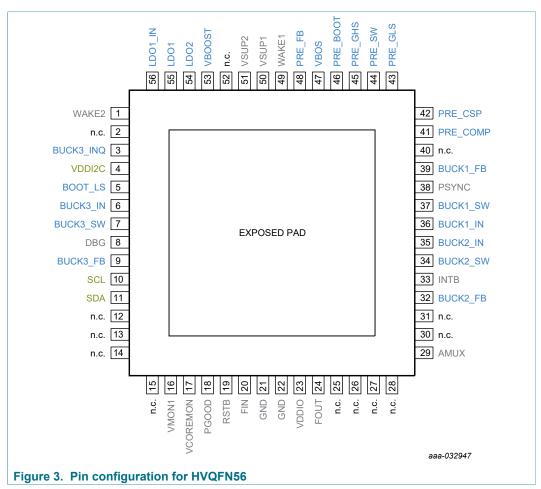

# 7 Pinning information

#### 7.1 Pinning

#### 7.2 Pin description

See <u>Section 8</u> for connection of unused pins.

| Table 2. Pin des | cription |             |                                                                                     |

|------------------|----------|-------------|-------------------------------------------------------------------------------------|

| Symbol           | Pin      | Туре        | Description                                                                         |

| WAKE2            | 1        | A_IN / D_IN | Wake-up input 2<br>An external serial resistor is required if WAKE2 is a global pin |

| n.c.             | 2        | n.c.        | Not connected pin                                                                   |

| BUCK3_INQ        | 3        | A_IN        | Low voltage Buck3 quiet input voltage                                               |

| VDDI2C           | 4        | A_IN        | Input voltage for I2C buffers                                                       |

| BOOST_LS         | 5        | A_IN        | Boost low-side drain of internal MOSFET                                             |

| BUCK3_IN         | 6        | A_IN        | Low voltage Buck3 input voltage                                                     |

| BUCK3_SW         | 7        | A_OUT       | Low voltage Buck3 switching node                                                    |

| DBG              | 8        | A_IN        | Debug mode entry                                                                    |

| BUCK3_FB         | 9        | A_IN        | Low voltage Buck3 voltage feedback                                                  |

#### Table 2. Pin description

VR5500

| Symbol   | Pin | Туре     | Description                                                                                                                                                                          |

|----------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL      | 10  | D_IN     | I2C-bus<br>Clock input                                                                                                                                                               |

| SDA      | 11  | D_IN/OUT | I2C-bus<br>Bidirectional data line                                                                                                                                                   |

| n.c.     | 12  | n.c.     | Not connected pin                                                                                                                                                                    |

| n.c.     | 13  | n.c.     | Not connected pin                                                                                                                                                                    |

| n.c.     | 14  | n.c.     | Not connected pin                                                                                                                                                                    |

| n.c.     | 15  | n.c.     | Not connected pin                                                                                                                                                                    |

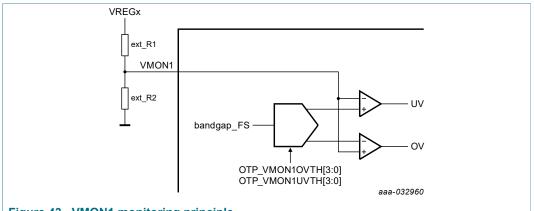

| VMON1    | 16  | A_IN     | Voltage monitoring input 1                                                                                                                                                           |

| VCOREMON | 17  | A_IN     | VCORE monitoring input: Must be connected to Buck1 output voltage                                                                                                                    |

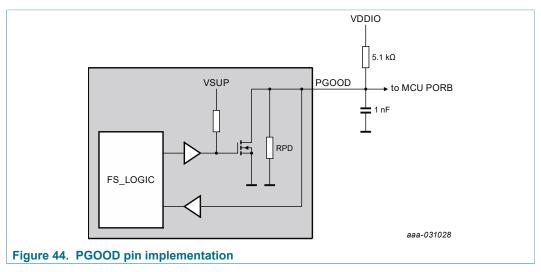

| PGOOD    | 18  | D_OUT    | Power good output<br>Active low<br>Pull up to VDDIO mandatory                                                                                                                        |

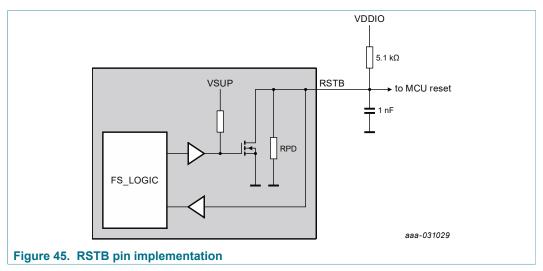

| RSTB     | 19  | D_OUT    | Reset output<br>Active low<br>The main function is to reset the MCU. Reset input voltage is<br>monitored to detect external reset and fault condition.<br>Pull up to VDDIO mandatory |

| FIN      | 20  | D_IN     | Frequency synchronization input                                                                                                                                                      |

| GND      | 21  | GND      | Ground                                                                                                                                                                               |

| GND      | 22  | GND      | Ground                                                                                                                                                                               |

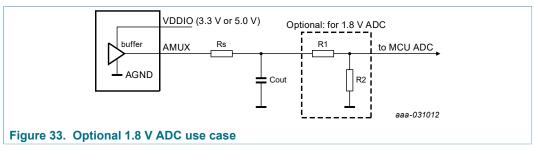

| VDDIO    | 23  | A_IN     | Input voltage FOUT and AMUX buffers<br>Allow voltage compatibility with MCU I/Os                                                                                                     |

| FOUT     | 24  | D_OUT    | Frequency synchronization output                                                                                                                                                     |

| n.c.     | 25  | n.c.     | Not connected pin                                                                                                                                                                    |

| n.c.     | 26  | n.c.     | Not connected pin                                                                                                                                                                    |

| n.c.     | 27  | GND      | External pull down to GND                                                                                                                                                            |

| n.c.     | 28  | n.c.     | Not connected pin                                                                                                                                                                    |

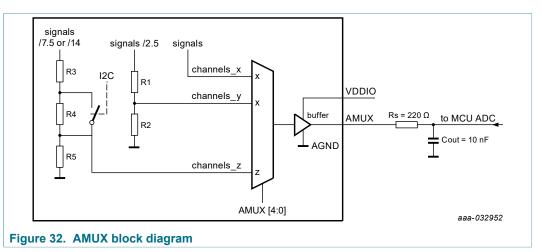

| AMUX     | 29  | A_OUT    | Multiplexed output to connect to MCU ADC<br>Selection of the analog parameter through I2C                                                                                            |

| n.c.     | 30  | n.c.     | Not connected pin                                                                                                                                                                    |

| n.c.     | 31  | n.c.     | Not connected pin                                                                                                                                                                    |

| BUCK2_FB | 32  | A_IN     | Low voltage Buck2 voltage feedback                                                                                                                                                   |

| INTB     | 33  | D_OUT    | Interrupt output                                                                                                                                                                     |

| BUCK2_SW | 34  | A_OUT    | Low voltage Buck2 switching node                                                                                                                                                     |

| BUCK2_IN | 35  | A_IN     | Low voltage Buck2 input voltage                                                                                                                                                      |

| BUCK1_IN | 36  | A_IN     | Low voltage Buck1 input voltage                                                                                                                                                      |

| BUCK1_SW | 37  | A_OUT    | Low voltage Buck1 switching node                                                                                                                                                     |

| PSYNC    | 38  | D_IN/OUT | Power synchronization input/output                                                                                                                                                   |

| BUCK1_FB | 39  | A_IN     | Low voltage Buck1 voltage feedback                                                                                                                                                   |

| n.c.     | 40  | GND      | External pull down to GND                                                                                                                                                            |

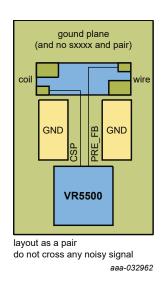

| PRE_COMP | 41  | A_IN     | VPRE compensation network                                                                                                                                                            |

| PRE_CSP  | 42  | A_IN     | VPRE positive current sense input                                                                                                                                                    |

VR5500 Product data sheet All information provided in this document is subject to legal disclaimers.

# **VR5500**

## High voltage PMIC with multiple SMPS and LDO

| Symbol   | Pin | Туре        | Description                                                                                                    |

|----------|-----|-------------|----------------------------------------------------------------------------------------------------------------|

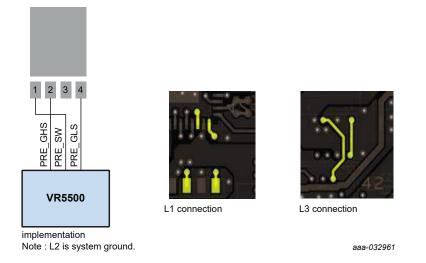

| PRE_GLS  | 43  | A_OUT       | VPRE low-side gate driver for external MOSFET                                                                  |

| PRE_SW   | 44  | A_OUT       | VPRE switching node                                                                                            |

| PRE_GHS  | 45  | A_OUT       | VPRE high-side gate driver for external MOSFET                                                                 |

| PRE_BOOT | 46  | A_IN/OUT    | VPRE bootstrap capacitor                                                                                       |

| VBOS     | 47  | A_OUT       | Best of supply output voltage                                                                                  |

| PRE_FB   | 48  | A_IN        | VPRE voltage feedback and negative current sense input                                                         |

| WAKE1    | 49  | A_IN / D_IN | Wake up input 1<br>An external serial resistor is required if WAKE1 is a global pin                            |

| VSUP1    | 50  | A_IN        | Power supply 1 of the device<br>An external reverse battery protection diode in series is<br>mandatory         |

| VSUP2    | 51  | A_IN        | Power supply 2 of the device<br>An external reverse battery protection diode in series is<br>mandatory         |

| n.c.     | 52  | n.c.        | Not connected pin                                                                                              |

| VBOOST   | 53  | A_IN        | VBOOST voltage feedback                                                                                        |

| LDO2     | 54  | A_OUT       | Linear regulator 2 output voltage                                                                              |

| LDO1     | 55  | A_OUT       | Linear regulator 1 output voltage                                                                              |

| LDO1_IN  | 56  | A_IN        | Linear regulator 1 input voltage                                                                               |

| EP       | 57  | GND         | Exposed pad (BUCK1, BUCK2 and BUCK3 low-side GNDs are connected to the expose pad)<br>Must be connected to GND |

# 8 Connection of unused pins

| Pin | Name      | Туре        | Connection if not used                                          |

|-----|-----------|-------------|-----------------------------------------------------------------|

| 1   | WAKE2     | A_IN / D_IN | External pull down to GND                                       |

| 2   | n.c.      | n.c.        | Open                                                            |

| 3   | BUCK3_INQ | A_IN        | Open                                                            |

| 4   | VDDI2C    | A_IN        | Open                                                            |

| 5   | BOOST_LS  | A_IN        | See Section 21.5 "VBOOST not populated"                         |

| 6   | BUCK3_IN  | A_IN        | Open                                                            |

| 7   | BUCK3_SW  | A_OUT       | Open                                                            |

| 8   | DBG       | A_IN        | Connection mandatory                                            |

| 9   | BUCK3_FB  | A_IN        | Open – 1.5 M $\Omega$ internal resistor bridge pull down to GND |

| 10  | SCL       | D_IN        | External pull down to GND                                       |

| 11  | SDA       | D_IN/OUT    | External pull down to GND                                       |

| 12  | n.c.      | n.c.        | Open                                                            |

| 13  | n.c.      | n.c.        | Open                                                            |

| 14  | n.c.      | n.c.        | Open                                                            |

| 15  | n.c.      | n.c.        | Open                                                            |

| 16  | VMON1     | A_IN        | Open – 2 MΩ internal pull down to GND, OTP_VMON1_EN=0           |

# **VR5500**

## High voltage PMIC with multiple SMPS and LDO

|    | Name     | Туре        | Connection if not used                                          |

|----|----------|-------------|-----------------------------------------------------------------|

| 17 | VCOREMON | A_IN        | Connection mandatory                                            |

| 18 | PGOOD    | D_OUT       | Connection mandatory                                            |

| 19 | RSTB     | D_OUT       | Connection mandatory                                            |

| 20 | FIN      | D_IN        | External pull down to GND                                       |

| 21 | GND      | GND         | Connection mandatory                                            |

| 22 | GND      | GND         | Connection mandatory                                            |

| 23 | VDDIO    | A_IN        | Connection mandatory                                            |

| 24 | FOUT     | D_OUT       | Open – push pull structure                                      |

| 25 | n.c.     | n.c.        | Open                                                            |

| 26 | n.c.     | n.c.        | Open                                                            |

| 27 | n.c.     | GND         | External pull down to GND                                       |

| 28 | n.c.     | n.c.        | Open                                                            |

| 29 | AMUX     | A_OUT       | Open                                                            |

| 30 | n.c.     | n.c.        | Open                                                            |

| 31 | n.c.     | n.c.        | Open                                                            |

| 32 | BUCK2_FB | A_IN        | Open – 1.5 M $\Omega$ Internal resistor bridge pull down to GND |

| 33 | INTB     | D_OUT       | Open – 10 k $\Omega$ internal pull up to VDDIO                  |

| 34 | BUCK2_SW | A_OUT       | Open                                                            |

| 35 | BUCK2_IN | A_IN        | Open                                                            |

| 36 | BUCK1_IN | A_IN        | Connection mandatory                                            |

| 37 | BUCK1_SW | A_OUT       | Connection mandatory                                            |

| 38 | PSYNC    | D_IN/OUT    | External pull up to VBOS                                        |

| 39 | BUCK1_FB | A_IN        | Connection mandatory                                            |

| 40 | n.c.     | n.c.        | External pull down to GND                                       |

| 41 | PRE_COMP | A_IN        | See Section 20.7 "VPRE not populated"                           |

| 42 | PRE_CSP  | A_IN        | See Section 20.7 "VPRE not populated"                           |

| 43 | PRE_GLS  | A_OUT       | See Section 20.7 "VPRE not populated"                           |

| 44 | PRE_SW   | A_OUT       | See Section 20.7 "VPRE not populated"                           |

| 45 | PRE_GHS  | A_OUT       | See Section 20.7 "VPRE not populated"                           |

| 46 | PRE_BOOT | A_IN/OUT    | See Section 20.7 "VPRE not populated"                           |

| 47 | VBOS     | A_OUT       | Connection mandatory                                            |

| 48 | PRE_FB   | A_IN        | See Section 20.7 "VPRE not populated"                           |

| 49 | WAKE1    | A_IN / D_IN | External pull down to GND                                       |

| 50 | VSUP1    | A_IN        | Connection mandatory                                            |

| 51 | VSUP2    | A_IN        | Connection mandatory                                            |

| 52 | n.c.     | n.c.        | Open                                                            |

| 53 | VBOOST   | A_OUT       | See Section 21.5 "VBOOST not populated"                         |

| 54 | LDO2     | A_OUT       | Open – power sequence slot 7, OTP_LDO1S[2:0] = '111'            |

| 55 | LDO1     | A_OUT       | Open – power sequence slot 7, OTP_LDO2S[2:0] = '111'            |

| 56 | LDO1_IN  | A_IN        | Open                                                            |

|    |          |             |                                                                 |

VR5500

# 9 Maximum ratings

#### Table 4. Maximum ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                | Parameter                  | Conditions                                       | Min  | Max  | Unit |

|-----------------------|----------------------------|--------------------------------------------------|------|------|------|

| Voltage ratings       |                            |                                                  | I    |      |      |

| VSUP1/2               | DC voltage                 | power supply VSUP1,2 pins                        | -0.3 | 60   | V    |

| WAKE1/2               | DC voltage                 | WAKE1,2 pins; external serial resistor mandatory | -1.0 | 60   | V    |

| PRE_SW                | DC voltage                 | PRE_SW pin                                       | -2.0 | 60   | V    |

| VMON1, VCOREMON       | DC voltage                 | VMON1, VCOREMON pins                             | -0.3 | 60   | V    |

| PRE_GHS, PRE_<br>BOOT | DC voltage                 | PRE_GHS, PRE_BOOT pins                           | -0.3 | 65.5 | V    |

| DBG                   | DC voltage                 | DBG pin                                          | -0.3 | 10   | V    |

| BOOST_LS              | DC voltage                 | BOOST_LS pin                                     | -0.3 | 8.5  | V    |

| VBOOST, LDO1_IN       | DC voltage                 | VBOOST, LDO1_IN pins                             | -0.3 | 6.5  | V    |

| BUCKx_IN              | DC voltage                 | BUCK1_IN, BUCK2_IN, BUCK3_IN,<br>BUCK3_INQ       | -1.0 | 5.5  | V    |

| BUCKx_IN              | Transient voltage < 3 μs   | BUCK1_IN, BUCK2_IN, BUCK3_IN,<br>BUCK3_INQ       | -1.0 | 6.5  | V    |

| BUCKx_SW              | Transient voltage < 20 ns  | BUCK1_SW, BUCK2_SW, BUCK3_<br>SW                 | -2.0 | 6.5  | V    |

| All other pins        | DC voltage                 | at all other pins                                | -0.3 | 5.5  | V    |

| Current ratings       |                            |                                                  | 1    |      |      |

| I_WAKE                | Maximum current capability | WAKE1,2                                          | -5.0 | 5.0  | mA   |

| I_SUP                 | Maximum current capability | VSUP1,2                                          | -5.0 | _    | mA   |

# **10** Electrostatic discharge

#### 10.1 Human body model (JESD22/A114)

The device is protected up to  $\pm 2$  kV, according to the human body model standard with 100 pF and 1.5 k $\Omega$ . This protection is ensured at all pins.

#### 10.2 Charged device model

The device is protected up to  $\pm 500$  V, according to the AEC-Q100 - 011 charged device model standard. This protection is ensured at all pins.

#### 10.3 Discharged contact test

The device is protected up to ±8 kV, according to the following discharged contact tests.

Discharged contact test (IEC61000-4-2) at 150 pF and 330  $\Omega$ Discharged contact test (ISO10605.2008) at 150 pF and 2 k $\Omega$ Discharged contact test (ISO10605.2008) at 330 pF and 2 k $\Omega$

This protection is ensured at VSUP1, VSUP2, WAKE1, WAKE2 pins.

# **11 Operating range**

| NO<br>OPERATION                                   | EXTER<br>OPER/                                         |              | FULL OPERATION                               |      | EXTENDED<br>OPERATION |    | NO OPERATION<br>RISK OF DAMAGE |  |  |

|---------------------------------------------------|--------------------------------------------------------|--------------|----------------------------------------------|------|-----------------------|----|--------------------------------|--|--|

|                                                   | I<br>CR X I <sub>PRE</sub> +<br>: UVL/D <sub>MAX</sub> | VSUP_<br>5.1 |                                              | 36 \ | /                     | 60 | V VSUP1/2                      |  |  |

|                                                   |                                                        |              |                                              |      |                       |    | aaa-030983                     |  |  |

| Assumptions                                       |                                                        |              |                                              |      |                       |    |                                |  |  |

| L <sub>PI DCR</sub> = 30                          | mΩ                                                     |              |                                              |      |                       |    |                                |  |  |

| _                                                 |                                                        | RE_SW =      | 455 kHz and T <sub>PRE_OFF_MIN</sub> = 40 ns |      |                       |    |                                |  |  |

| I <sub>PRE</sub> = 3.0 A                          | . ,                                                    |              |                                              |      |                       |    |                                |  |  |

| $V_{RBD} = 0.56$                                  |                                                        |              | N/                                           |      |                       |    |                                |  |  |

| VBAT_min = 3.4 V when VPRE = V <sub>PRE_UVL</sub> |                                                        |              |                                              |      |                       |    |                                |  |  |

| Figure 4. Oper                                    | ating range                                            | •            |                                              |      |                       |    |                                |  |  |

- Below VSUP\_UVH threshold, the extended operation range depends on VPRE output voltage configuration and external components.

- When VPRE is configured at 5.0 V, VPRE may not remain in its regulation range

- VSUP minimum voltage depends on external components (L<sub>PI\_DCR</sub>) and application conditions (I<sub>PRE</sub>, F<sub>PRE\_SW</sub>)

- The VR5500 maximum continuous operating voltage is 36 V when VPRE is switching at 455 kHz. It has been validated at 48 V for limited duration of 15 minutes at room temperature to satisfy the jump-start requirement of 24 V applications. It can sustain 58 V load dump without external protection.

- When VPRE is switching at 2.2 MHz, the VR5500 maximum continuous operating voltage is 18 V. It is validated at 26 V for limited duration of 2 minutes at room temperature to satisfy the jump-start requirement of 12 V applications and 35 V load dump.

# **12 Thermal ratings**

| Table 5. 1           | Thermal ratings                            |                                                                    |     |     |      |      |

|----------------------|--------------------------------------------|--------------------------------------------------------------------|-----|-----|------|------|

| Symbol               | Parameter                                  | Conditions                                                         | Min | Max | Unit |      |

| $R_{\theta JA}$      | Thermal resistance junction to ambient     | 2s2p circuit board                                                 | [1] | —   | 31   | °C/W |

| R <sub>θJA</sub>     | Thermal resistance junction to ambient     | 2s6p circuit board                                                 | [1] | —   | 23   | °C/W |

| $R_{\theta JB}$      | Thermal resistance junction to board       | 2s2p circuit board                                                 | [1] | _   | 15   | °C/W |

| $R_{\theta JB}$      | Thermal resistance junction to board       | 2s6p circuit board                                                 | [1] | _   | 10   | °C/W |

| $R_{\theta JC_BOT}$  | Thermal resistance junction to case bottom | between the die and the solder pad<br>on the bottom of the package | [1] | —   | 1    | °C/W |

| $R_{\theta JP\_TOP}$ | Thermal resistance junction to package top | between package top and the junction temperature                   | [1] | —   | 3    | °C/W |

| T <sub>A</sub>       | Ambient temperature (Grade 1)              |                                                                    |     | -40 | 125  | °C   |

| TJ                   | Junction temperature (Grade 1)             |                                                                    |     | -40 | 150  | °C   |

| T <sub>STG</sub>     | Storage temperature                        |                                                                    |     | -55 | 150  | °C   |

[1] per JEDEC JESD51-2 and JESD51-8

VR5500

# **13 Characteristics**

#### Table 6. Electrical characteristics

$T_A = -40$  °C to 125 °C, unless otherwise specified. VSUP = VSUP\_UVH to 36 V, unless otherwise specified. All voltages referenced to ground.

| Symbol                   | Parameter                                                                              | Min | Тур | Мах | Unit |

|--------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|------|

| Power supply             |                                                                                        | -   |     |     | ,    |

| I <sub>SUP_NORMAL</sub>  | Current in Normal mode, all regulators ON (I <sub>OUT</sub> = 0)                       | _   | 15  | 25  | mA   |

| I <sub>SUP_STANDBY</sub> | Current in Standby mode, all regulators OFF except VBOS                                |     | 5   | 10  | mA   |

| I <sub>SUP_OFF1</sub>    | Current in OFF mode (power down), $T_A < 85 ^\circ\text{C}$                            | —   | 10  | 15  | μA   |

| I <sub>SUP_OFF2</sub>    | Current in OFF mode (power down), $T_A$ = 125 °C                                       | —   | —   | 25  | μA   |

| V <sub>SUP_UV7</sub>     | VSUP undervoltage threshold (7.0 V)                                                    | 7.2 | 7.5 | 7.8 | V    |

| V <sub>SUP_UVH</sub>     | VSUP undervoltage threshold high (during power-up and Vsup rising) OTP_VSUP_CFG = 0    | 4.7 | _   | 5.1 | V    |

|                          | VSUP undervoltage threshold high (during power-up and Vsup rising) OTP_VSUP_CFG = 1    | 6.0 |     | 6.4 | V    |

| V <sub>SUP_UVL</sub>     | VSUP undervoltage threshold low (during power-up<br>and Vsup falling) OTP_VSUP_CFG = 0 | 4.0 |     | 4.4 | V    |

|                          | VSUP undervoltage threshold low (during power-up<br>and Vsup falling) OTP_VSUP_CFG = 1 | 5.3 | _   | 5.7 | V    |

| T <sub>SUP_UV</sub>      | $V_{SUP\_UV7},V_{SUP\_UVH},andV_{SUP\_UVL}$ filtering time                             | 6.0 | 10  | 15  | μs   |

# **14 Functional description**

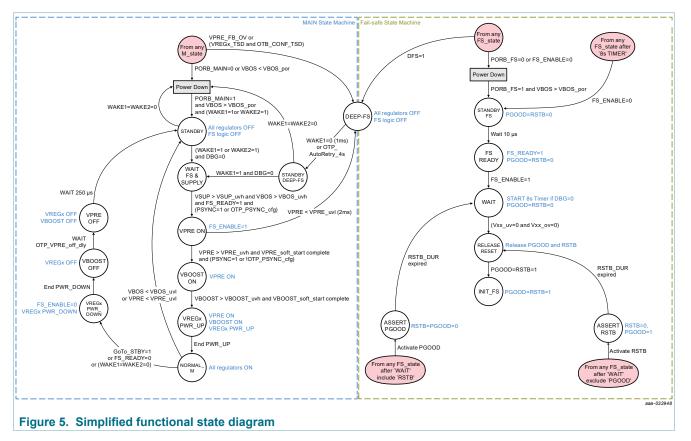

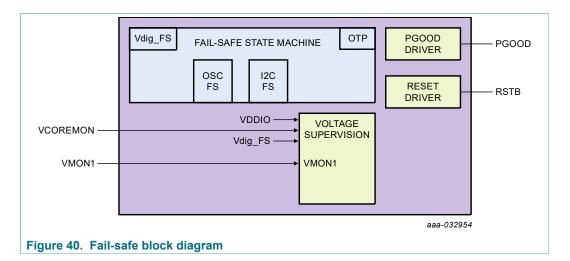

The VR5500 device has two independent logic blocks. The main state machine manages the power management, the Standby mode and the wake-up sources. The fail-safe state machine manages the voltage monitoring of the power management.

#### 14.1 Simplified functional state diagram

#### 14.2 Main state machine

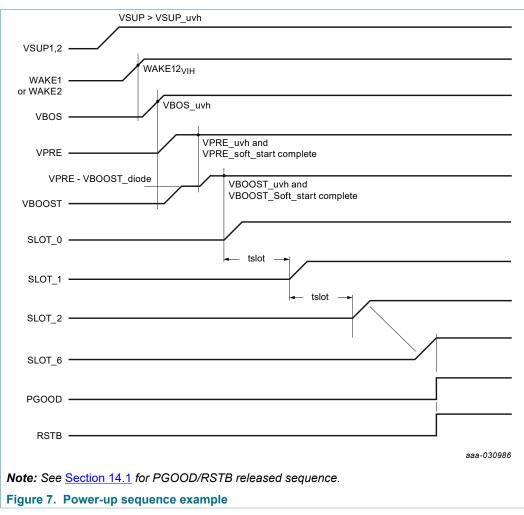

The VR5500 start when VSUP > V<sub>SUP\_UVH</sub> and WAKE1 or WAKE2 > WAKE12<sub>VIH</sub> with VBOS first, followed by VPRE, VBOOST, and the power-up sequencing from the OTP programming for the remaining regulators if PSYNC pin is pulled up to VBOS. If during the power-up sequence VSUP < V<sub>SUP\_UVL</sub>, the device goes back to Standby mode. When the power-up is finished, the main state machine is in Normal\_M mode which is the application running mode with all the regulators ON and V<sub>SUP\_UVL</sub> has no effect even if VSUP < V<sub>SUP\_UVL</sub>. See Figure 4 for the minimum operating voltage.

The power-up sequence can be synchronized with another PMIC using the PSYNC pin in order to stop before or after VPRE is ON and wait for the PMIC feedback on PSYNC pin before allowing VR5500 to continue its power-up sequence. If the power-up sequence from VPRE ON to NORMAL\_M is not completed within 1 second, the device goes back to Standby mode. VPRE restarts when VSUP >  $V_{SUP_UVH}$  and WAKE1 or WAKE2 > WAKE12<sub>VIH</sub>.

The device goes to Standby mode by a I2C command from the MCU. The device goes to Standby mode when both WAKE1 and WAKE 2 = 0. The device goes to Standby mode following the power down sequence to stop all the regulators in the reverse order of the power-up sequence. VPRE shutdown can be delayed from 250  $\mu$ s to 32 ms by OTP\_VPRE\_off\_dly bit in case VPRE is supplying an external PMIC to wait its power down sequence completion.

VR5500

In case of loss of VPRE (VPRE <  $V_{PRE_UVL}$ ) or loss of VBOS (VBOS <  $V_{BOS_UVL}$ ), the device stops and goes directly to Standby mode without power down sequence. VPRE restarts when VSUP >  $V_{SUP_UVH}$  and WAKE1 or WAKE2 > WAKE12<sub>VIH</sub>.

In case of VPRE\_FB\_OV detection, or TSD detection on a regulator depending on OTP\_conf\_tsd[5:0] bits configuration, or deep fail-safe request from the fail-safe state machine when DFS = 1, the device stops and goes directly to DEEP-FS mode without power down sequence.

Exit of DEEP-FS mode is only possible by WAKE1 = 0 or after 4 s if the autoretry feature is activated by OTP\_Autorety\_en bit. The number of autroretry can be limited to 15 or infinite depending on OTP\_Autoretry\_infinite bit. VPRE restarts when VSUP >  $V_{SUP_UVH}$  and WAKE1 > WAKE12<sub>VIH</sub>.

#### 14.3 Fail-safe state machine

The fail-safe state machine starts when VBOS >  $V_{BOS_{POR}}$ . RSTB and PGOOD pins are released and the initialization of the device is opened.

When RSTB and PGOOD pins are released, the device is ready for application running mode with all the selected monitoring activated. From now on, the VR5500 reacts by asserting the pins (PGOOD, RSTB) according to its configuration when a fault is detected.

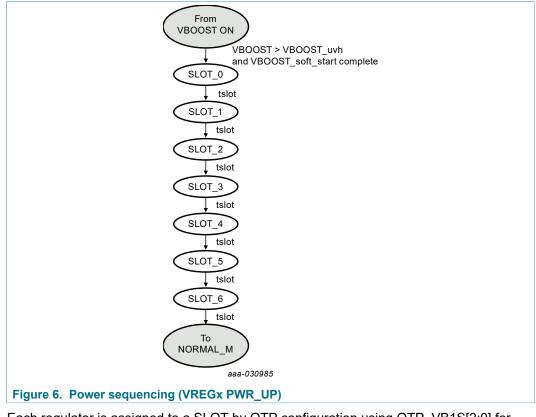

#### 14.4 Power sequencing

VPRE is the first regulator to start automatically, followed by the BOOST, before the SLOT\_0. The other regulators are starting from the OTP power sequencing configuration. Seven slots are available to program the start-up sequence of BUCK1, BUCK 2, BUCK 3, LDO1, and LDO2 regulators. The delay between each slot is configurable to 250 µs or 1 ms by OTP using OTP\_Tslot bit to accommodate the different ramp up speed of BUCK1, BUCK2, BUCK3, BUCK2, and BUCK3.

The power-up sequence starts at SLOT\_0 and ends at SLOT\_7 while the power down sequence is executed in reverse order. All the SLOTs are executed even if there is no regulator assigned to a SLOT. The regulators assigned to SLOT\_7 are not started during the power-up sequence. They can be started (or not) later in Normal\_M mode with a I2C command to write in M\_REG\_CTRL1 register, if enabled by OTP.

VR5500

# **VR5500**

#### High voltage PMIC with multiple SMPS and LDO

Each regulator is assigned to a SLOT by OTP configuration using OTP\_VB1S[2:0] for BUCK1, OTP\_VB2S[2:0] for BUCK2, OTP\_VB3S[2:0] for BUCK3, OTP\_LD01S[2:0] for LD01 and OTP\_LD02S[2:0] for LD02.

The different soft start duration of the BUCKs and the LDOs should be considered in the SLOT assignment to achieve the correct sequence.

VR5500 Product data sheet

# **VR5500**

#### High voltage PMIC with multiple SMPS and LDO

The VR5500\_OTP\_Mapping file used to generate the OTP configuration of the device draws the power-up sequence of an OTP configuration in the OTP\_conf\_summary sheet.

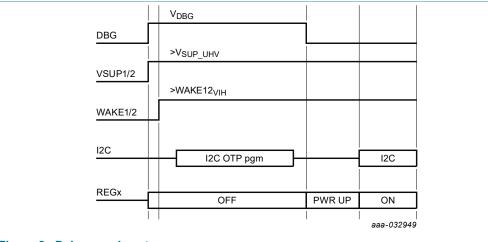

#### 14.5 Debug mode

The VR5500 enters in Debug mode with the sequence described in Figure 8:

- 1. DBG pin =  $V_{DBG}$  and  $VSUP > V_{SUP_UVH}$

- 2. WAKE1 or WAKE2 > WAKE12<sub>VIH</sub>

$V_{\text{DBG}}$  and VSUP can come up at the same time as long as WAKE1 or WAKE2 comes up the last.

#### Figure 8. Debug mode entry

When the DBG pin is asserted low after  $T_{\text{DBG}}$  without I2C command access, the device starts with the internal OTP configuration.

If  $V_{DBG}$  voltage is maintained at DBG pin, a new OTP configuration can be emulated or programmed by I2C communication using NXP FlexGUI interface and NXP socket EVB. When the OTP process is completed, the device starts with the new OTP configuration when DBG pin is asserted low. The OTP emulation/programming is possible for during engineering development only. The OTP programming in production is done by NXP only.

In OTP Debug mode (DBG = 5.0 V), the I2C address is fixed to 0x20 for the main digital access and 0x21 for the fail-safe digital access.

Refer to AN12589 for more details on Debug mode entry implementation.

#### Table 7. Electrical characteristics

$T_A = -40$  °C to 125 °C, unless otherwise specified. VSUP = VSUP\_UVH to 36 V, unless otherwise specified. All voltages referenced to ground.

| Symbol           | Parameter                                                                                                                                                         | Min | Тур | Max | Unit |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>DBG</sub> | Debug mode entry threshold                                                                                                                                        | 4.5 | —   | 5.5 | V    |

| T <sub>DBG</sub> | Debug mode entry filtering time (minimum<br>duration of DBG = V <sub>DBG</sub> after VSUP<br>> V <sub>SUP_UVH</sub> and WAKE1 or WAKE2 ><br>WAKE12 <sub>VIH</sub> | 7.0 |     |     | ms   |

VR5500 Product data sheet

# 15 Register mapping

| Register                     | M/FS | Address |       |       |       |       |       | R/W | Read / Write                        | Reference     |  |

|------------------------------|------|---------|-------|-------|-------|-------|-------|-----|-------------------------------------|---------------|--|

|                              |      | Adr_5   | Adr_4 | Adr_3 | Adr_2 | Adr_1 | Adr_0 | I2C |                                     |               |  |

| M_FLAG                       | 0    | 0       | 0     | 0     | 0     | 0     | 0     | 1/0 | Read / Write                        | Section 16.3  |  |

| M_MODE                       | 0    | 0       | 0     | 0     | 0     | 0     | 1     | 1/0 | Read / Write                        | Section 16.4  |  |

| M_REG_CTRL1                  | 0    | 0       | 0     | 0     | 0     | 1     | 0     | 1/0 | Read / Write                        | Section 16.5  |  |

| M_REG_CTRL2                  | 0    | 0       | 0     | 0     | 0     | 1     | 1     | 1/0 | Read / Write                        | Section 16.6  |  |

| M_AMUX                       | 0    | 0       | 0     | 0     | 1     | 0     | 0     | 1/0 | Read / Write                        | Section 16.7  |  |

| M_CLOCK                      | 0    | 0       | 0     | 0     | 1     | 0     | 1     | 1/0 | Read / Write                        | Section 16.8  |  |

| M_INT_MASK1                  | 0    | 0       | 0     | 0     | 1     | 1     | 0     | 1/0 | Read / Write                        | Section 16.9  |  |

| M_INT_MASK2                  | 0    | 0       | 0     | 0     | 1     | 1     | 1     | 1/0 | Read / Write                        | Section 16.10 |  |

| M_FLAG1                      | 0    | 0       | 0     | 1     | 0     | 0     | 0     | 1/0 | Read / Write                        | Section 16.11 |  |

| M_FLAG2                      | 0    | 0       | 0     | 1     | 0     | 0     | 1     | 1/0 | Read / Write                        | Section 16.12 |  |

| M_VMON_REGX                  | 0    | 0       | 0     | 1     | 0     | 1     | 0     | 1/0 | Read / Write                        | Section 16.13 |  |

| M_LVB1_SVS                   | 0    | 0       | 0     | 1     | 0     | 1     | 1     | 1   | Read only                           | Section 16.14 |  |

| M_MEMORY0                    | 0    | 1       | 0     | 0     | 0     | 1     | 1     | 1/0 | Read / Write                        | Section 16.15 |  |

| M_MEMORY1                    | 0    | 1       | 0     | 0     | 1     | 0     | 0     | 1/0 | Read / Write                        | Section 16.16 |  |

| M_DEVICEID                   | 0    | 1       | 0     | 0     | 1     | 0     | 1     | 1   | Read only                           | Section 16.17 |  |

| FS_GRL_FLAGS                 | 1    | 0       | 0     | 0     | 0     | 0     | 0     | 1   | Read only                           | Section 17.3  |  |

| FS_I_OVUV_SAFE_REACTION1     | 1    | 0       | 0     | 0     | 0     | 0     | 1     | 1/0 | Write during INIT then<br>Read only | Section 17.4  |  |

| FS_I_NOT_OVUV_SAFE_REACTION1 | 1    | 0       | 0     | 0     | 0     | 1     | 0     | 1/0 | Write during INIT then<br>Read only |               |  |

| FS_I_OVUV_SAFE_REACTION2     | 1    | 0       | 0     | 0     | 0     | 1     | 1     | 1/0 | Write during INIT then<br>Read only | Section 17.5  |  |

| FS_I_NOT_OVUV_SAFE_REACTION2 | 1    | 0       | 0     | 0     | 1     | 0     | 0     | 1/0 | Write during INIT then Read only    |               |  |

| FS_I_FSSM                    | 1    | 0       | 0     | 1     | 0     | 0     | 1     | 1/0 | Write during INIT then<br>Read only | Section 17.6  |  |

| FS_I_NOT_FSSM                | 1    | 0       | 0     | 1     | 0     | 1     | 0     | 1/0 | Write during INIT then<br>Read only |               |  |

| FS_I_SVS                     | 1    | 0       | 0     | 1     | 0     | 1     | 1     | 1/0 | Write during INIT then<br>Read only | Section 17.7  |  |

| FS_I_NOT_SVS                 | 1    | 0       | 0     | 1     | 1     | 0     | 0     | 1/0 | Write during INIT then<br>Read only |               |  |

| FS_OVUVREG_STATUS            | 1    | 0       | 1     | 0     | 0     | 0     | 1     | 1/0 | Read / Write                        | Section 17.8  |  |

| FS_SAFE_IOS                  | 1    | 0       | 1     | 0     | 0     | 1     | 1     | 1/0 | Read / Write                        | Section 17.9  |  |

| FS_DIAG                      | 1    | 0       | 1     | 0     | 1     | 0     | 0     | 1/0 | Read / Write                        | Section 17.10 |  |

| FS_INTB_MASK                 | 1    | 0       | 1     | 0     | 1     | 0     | 1     | 1/0 | Read / Write                        | Section 17.11 |  |

| FS_STATES                    | 1    | 0       | 1     | 0     | 1     | 1     | 0     | 1/0 | Read / Write                        | Section 17.12 |  |

# 16 Main register mapping

## 16.1 Main writing registers overview

| ogic | Register name | bit 23           | bit 22                     | bit 21          | bit 20                     | bit 19        | bit 18      | bit 17     | bit 16           |  |

|------|---------------|------------------|----------------------------|-----------------|----------------------------|---------------|-------------|------------|------------------|--|

|      |               | bit 15           | bit 14                     | bit 13          | bit 12                     | bit 11        | bit 10      | bit 9      | bit 8            |  |

| ain  | M_FLAG        | 0                | 0                          | 0               | 0                          | 0             | 0           | 0          | 0                |  |

|      |               | 0                | 0                          | 0               | 0                          | 0             | 0           | I2C_M_CRC  | I2C_M_REQ        |  |

|      | M_MODE        | 0                | 0                          | 0               | 0                          | 0             | 0           | 0          | 0                |  |

|      |               | 0                | EXT_FIN_DIS                | 0               | 0                          | 0             | W2DIS       | W1DIS      | GoToSTBY         |  |

|      | M_REG_CTRL1   | VPRE_PD_DIS      | VPDIS                      | BOOSTDIS        | BUCK1DIS                   | BUCK2DIS      | BUCK3DIS    | LDO1DIS    | LDO2DIS          |  |

|      |               | 0                | VPEN                       | BOOSTEN         | BUCK1EN                    | BUCK2EN       | BUCK3EN     | LDO1EN     | LDO2EN           |  |

|      | M_REG_CTRL2   | VBSTS            | SR[1:0]                    | BOOSTT<br>SDCFG | BUCK1TSDCFG                | BUCK2TSDCFG   | BUCK3TSDCFG | LDO1TSDCFG | LDO2TSDCFG       |  |

|      |               | 0                | 0                          | 0               | VPRESI                     | RLS[1:0]      | 0           | VPRESF     | RHS[1:0]         |  |

|      | M_AMUX        | 0                | 0                          | 0               | 0                          | 0             | 0           | 0          | 0                |  |

|      |               | 0                | 0                          | RATIO           |                            | AMUX[4:0]     |             |            |                  |  |

|      | M_CLOCK       | MOD_CONF         |                            | FOUT_MU         | X_SEL[3:0] FOUT_PHASE[2:0] |               |             |            |                  |  |

|      |               | FOUT_<br>CLK_SEL | EXT_FIN_SEL                | FIN_DIV         | MOD_EN                     | CLK_TUNE[3:0] |             |            |                  |  |

|      | M_INT_MASK1   | 0                | VPREOC_M                   | 0               | BUCK1OC_M                  | BUCK2OC_M     | BUCK3OC_M   | LDO10C_M   | LDO2OC_M         |  |

|      |               | 0                | 0                          | BOOSTTSD_M      | BUCK1TSD_M                 | BUCK2TSD_M    | BUCK3TSD_M  | LDO1TSD_M  | LDO2TSD_M        |  |

|      | M_INT_MASK2   | 0                | 0                          | 0               | 0                          | VBOOSTOV_M    | VBOSUVH_M   | COM_M      | VPRE_<br>FB_OV_M |  |

|      |               | VBOOST_<br>UVH_M | VSUPUV7                    | 0               | VPREUVH                    | VSUPUVL_M     | VSUPUVH_M   | WAKE1_M    | WAKE2_M          |  |

|      | M_FLAG1       | VBOSUVH          | VBOOSTUVH                  | VPREOC          | BUCK1OC                    | BUCK2OC       | BUCK3OC     | LDO10C     | LDO2OC           |  |

|      |               | 0                | VBOOSTOV                   | VBOOSTOT        | BUCK1OT                    | BUCK2OT       | BUCK3OT     | LDO10T     | LDO2OT           |  |

|      | M_FLAG2       | VPRE_FB_OV       | VSUPUV7                    | 0               | 0                          | 0             | 0           | 0          | 0                |  |

|      |               | VPREUVL          | VPREUVH                    | VSUPUVL         | VSUPUVH                    | 0             | 0           | WK2FLG     | WK1FLG           |  |

|      | M_VMON_REGX   | 0                | 0                          | 0               | 0                          | 0             | 0           | 0          | 0                |  |

|      |               | 0                | 0 0 0 0 0 0 VMON1_REG[2:0] |                 |                            |               |             |            |                  |  |

|      | M_MEMORY0     |                  |                            |                 | MEMOR                      | Y0[15:0]      |             |            |                  |  |

|      | M MEMORY1     |                  |                            |                 | MEMOR                      | Y1[15:0]      |             |            |                  |  |

#### VR5500 Product data sheet

leet

| 16.2 | Main | reading | registers | overview |

|------|------|---------|-----------|----------|

|------|------|---------|-----------|----------|

| gic | Register name | bit 23             | bit 22    | bit 21          | bit 20      | bit 19      | bit 18        | bit 17          | bit 16           |  |

|-----|---------------|--------------------|-----------|-----------------|-------------|-------------|---------------|-----------------|------------------|--|

|     |               | bit 15             | bit 14    | bit 13          | bit 12      | bit 11      | bit 10        | bit 9           | bit 8            |  |

| in  | M_FLAG        | COM_ERR            | WU_G      | VPRE_G          | VBOOST_G    | VBUCK1_G    | VBUCK2_G      | VBUCK3_G        | VLDO1_G          |  |

|     |               | VLDO2_G            | 0         | 0               | 0           | 0           | 0             | I2C_M_CRC       | I2C_M_REQ        |  |

|     | M_MODE        | RESERVED           | RESERVED  | RESERVED        | RESERVED    | RESERVED    | RESERVED      | RESERVED        | PLL_LOCK_R       |  |

|     |               | EXT_FIN_<br>SEL_RT | RESERVED  | MAIN_NORMAL     | RESERVED    | RESERVED    | W2DIS         | W1DIS           | RESERVED         |  |

|     | M_REG_CTRL1   | VPRE_PD_DIS        | VPDIS     | BOOSTDIS        | BUCK1DIS    | BUCK2DIS    | BUCK3DIS      | LDO1DIS         | LDO2DIS          |  |

|     |               | 0                  | VPEN      | BOOSTEN         | BUCK1EN     | BUCK2EN     | BUCK3EN       | LDO1EN          | LDO2EN           |  |

|     | M_REG_CTRL2   | VBSTS              | R[1:0]    | BOOSTT<br>SDCFG | BUCK1TSDCFG | BUCK2TSDCFG | BUCK3TSDCFG   | LDO1TSDCFG      | LDO2TSDCFG       |  |

|     |               | RESERVED           | RESERVED  | RESERVED        | VPRESI      | RLS[1:0]    | RESERVED      | VPRESF          | RHS[1:0]         |  |

|     | M_AMUX        | RESERVED           | RESERVED  | RESERVED        | RESERVED    | RESERVED    | RESERVED      | RESERVED        | RESERVED         |  |

|     |               | RESERVED           | RESERVED  | RATIO           |             |             | AMUX[4:0]     |                 |                  |  |

|     | M_CLOCK       | MOD_CONF           |           | FOUT_MU         | X_SEL[3:0]  |             |               | FOUT_PHASE[2:0] |                  |  |

|     |               | FOUT_<br>CLK_SEL   | RESERVED  | FIN_DIV         | MOD_EN      |             | CLK_TU        | CLK_TUNE[3 :0]  |                  |  |

|     | M_INT_MASK1   | RESERVED           | VPREOC_M  | RESERVED        | BUCK1OC_M   | BUCK2OC_M   | BUCK3OC_M     | LDO1OC_M        | LDO2OC_M         |  |

|     |               | RESERVED           | RESERVED  | BOOSTTSD_M      | BUCK1TSD_M  | BUCK2TSD_M  | BUCK3TSD_M    | LDO1TSD_M       | LDO2TSD_M        |  |

|     | M_INT_MASK2   | RESERVED           | RESERVED  | RESERVED        | RESERVED    | VBOOSTOV_M  | VBOSUVH_M     | COM_M           | VPRE_<br>FB_OV_M |  |

|     |               | VBOOST_<br>UVH_M   | VSUPUV7_M | RESERVED        | VPREUVH_M   | VSUPUV_M    | VSUPUVH_M     | WAKE1_M         | WAKE2_M          |  |

|     | M_FLAG1       | VBOSUVH            | VBOOSTUVH | VPREOC          | BUCK1OC     | BUCK2OC     | BUCK3OC       | LDO10C          | LDO2OC           |  |

|     |               | CLK_FIN_<br>DIV_OK | VBOOSTOV  | VBOOSTOT        | BUCK1OT     | BUCK2OT     | BUCK3OT       | LDO10T          | LDO2OT           |  |

|     | M_FLAG2       | VPRE_FB_OV         | VSUPUV7   | BOOST_ST        | BUCK1_ST    | BUCK2_ST    | BUCK3_ST      | LDO1_ST         | LDO2_ST          |  |

|     |               | VPREUVL            | VPREUVH   | VSUPUVL         | VSUPUVH     | WK2RT       | WK1RT         | WK2FLG          | WK1FLG           |  |

|     | M_VMON_REGX   | RESERVED           | RESERVED  | RESERVED        | RESERVED    | RESERVED    | RESERVED      | RESERVED        | RESERVED         |  |

|     |               | RESERVED           | RESERVED  | RESERVED        | RESERVED    | RESERVED    |               | VMON1_REG[2:0]  |                  |  |

|     | M_LVB1_SVS    | RESERVED           | RESERVED  | RESERVED        | RESERVED    | RESERVED    | RESERVED      | RESERVED        | RESERVED         |  |

|     |               | RESERVED           | RESERVED  | RESERVED        |             |             | LVB1_SVS[4:0] |                 |                  |  |

|     | M_MEMORY0     |                    |           |                 | MEMOR       | Y0[15:0]    |               |                 |                  |  |

|     | M_MEMORY1     |                    |           |                 | MEMOR       | Y1[15:0]    |               |                 |                  |  |

|     | M_DEVICEID    |                    | FM_R      | EV[3:0]         |             |             | MM_R          | EV[3:0]         |                  |  |

# 16.3 M\_FLAG register

| Table 10. M_ | FLAG registe | er bit allocatio | on     |          |          |          |           |           |

|--------------|--------------|------------------|--------|----------|----------|----------|-----------|-----------|

| Bit          | 23           | 22               | 21     | 20       | 19       | 18       | 17        | 16        |

| Write        | 0            | 0                | 0      | 0        | 0        | 0        | 0         | 0         |

| Read         | COM_ERR      | WU_G             | VPRE_G | VBOOST_G | VBUCK1_G | VBUCK2_G | VBUCK3_G  | VLDO1_G   |

| Reset        | 0            | 1                | 1      | 0        | 0        | 0        | 0         | 0         |

|              |              |                  |        |          |          |          |           |           |

| Bit          | 15           | 14               | 13     | 12       | 11       | 10       | 9         | 8         |

| Write        | 0            | 0                | 0      | 0        | 0        | 0        | I2C_M_CRC | I2C_M_REQ |

| Read         | VLDO2_G      | 0                | 0      | 0        | 0        | 0        | I2C_M_CRC | I2C_M_REQ |

| Reset        | 0            | 0                | 0      | 0        | 0        | 0        | 0         | 0         |

VR5500 Product data sheet

| Bit | Symbol   | Description                                                                                               |

|-----|----------|-----------------------------------------------------------------------------------------------------------|

| 23  | COM_ERR  | Report an error in the communication (I2C)<br><b>COM_ERR</b> = I2C_M_CRC or I2C_M_REQ or FS_COM_G         |

|     |          | 0 No failure                                                                                              |

|     |          | 1 Failure                                                                                                 |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 22  | WU_G     | Report a wake-up event by WAKE1 or WAKE2<br><b>WU_G</b> = WK1FLG or WK2FLG                                |

|     |          | 0 No wake event                                                                                           |

|     |          | 1 Wake event                                                                                              |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 21  | VPRE_G   | Report an event on VPRE (status change or failure)<br>VPRE_G = VPREOC or VPREUVH or VPREUVL or VPRE_FB_OV |

|     |          | 0 No event                                                                                                |

|     |          | 1 Event occurred                                                                                          |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 20  | VBOOST_G | Report an event on VBOOST (status change or failure)<br>VBOOST_G = VBOOSTOT or BOOSTOV                    |

|     |          | 0 No event                                                                                                |

|     |          | 1 Event occurred                                                                                          |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 19  | VBUCK1_G | Report an event on BUCK1 (status change or failure) <b>VBUCK1_G</b> = BUCK1OC or BUCK1OT                  |

|     |          | 0 No event                                                                                                |

|     |          | 1 Event occurred                                                                                          |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 18  | VBUCK2_G | Report an event on BUCK2 (status change or failure) <b>VBUCK2_G</b> = BUCK2OC or BUCK2OT                  |

|     |          | 0 No event                                                                                                |

|     |          | 1 Event occurred                                                                                          |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 17  | VBUCK3_G | Report an event on BUCK3 (status change or failure)<br><b>VBUCK3_G</b> = BUCK3OC or BUCK3OT               |

|     |          | 0 No event                                                                                                |

|     |          | 1 Event occurred                                                                                          |

|     |          | Reset condition: Real-time information - cleared when all individual bits are cleared                     |

| 16  | VLDO1_G  | Report an event on LDO1 (status change or failure) <b>VLDO1_G</b> = LDO1OC or LDO1OT                      |

|     |          | 0 No event                                                                                                |

|     |          | 1 Event occurred                                                                                          |

|     |          | Reset condition: Real-time information                                                                    |

#### Table 11. M\_FLAG register bit description

# **VR5500**

## High voltage PMIC with multiple SMPS and LDO

| Bit | Symbol    | Description                                                                                                 |

|-----|-----------|-------------------------------------------------------------------------------------------------------------|

| 15  | VLDO2_G   | Report an event on LDO2 (status change or failure)<br>VLDO2_G = LDO2OC or LDO2OT                            |

|     |           | 0 No event                                                                                                  |

|     |           | 1 Event occurred                                                                                            |

|     |           | Reset condition: Real-time information                                                                      |

| 9   | I2C_M_CRC | Main domain I2C communication CRC issue                                                                     |

|     |           | 0 No error                                                                                                  |

|     |           | 1 Error detected in the I2C CRC                                                                             |

|     |           | Reset condition: POR / clear on write (write '1')                                                           |

| 8   | I2C_M_REQ | Invalid main domain I2C access (wrong Write or Read, Write to INIT registers in normal mode, wrong address) |

|     |           | 0 No error                                                                                                  |

|     |           | 1 I2C violation                                                                                             |

|     |           | Reset condition: POR / clear on Write (write '1')                                                           |

# 16.4 M\_MODE register

| Table 12. M_ | MODE regist        | er bit allocati | ion             |          |          |          |          |                 |

|--------------|--------------------|-----------------|-----------------|----------|----------|----------|----------|-----------------|

| Bit          | 23                 | 22              | 21              | 20       | 19       | 18       | 17       | 16              |

| Write        | 0                  | 0               | 0               | 0        | 0        | 0        | 0        | 0               |

| Read         | RESERVED           | RESERVED        | RESERVED        | RESERVED | RESERVED | RESERVED | RESERVED | PLL_<br>LOCK_RT |

| Reset        | 0                  | 0               | 0               | 0        | 0        | 0        | 0        | 0               |

|              |                    | -               |                 |          |          |          | -        |                 |

| Bit          | 15                 | 14              | 13              | 12       | 11       | 10       | 9        | 8               |

| Write        | 0                  | EXT_<br>FIN_DIS | 0               | 0        | 0        | W2DIS    | W1DIS    | GoToSTBY        |

| Read         | EXT_FIN_<br>SEL_RT | RESERVED        | MAIN_<br>NORMAL | RESERVED | RESERVED | W2DIS    | W1DIS    | RESERVED        |

| Reset        | 0                  | 0               | 1               | 0        | 0        | 0        | 0        | 0               |

#### Table 13. M\_MODE register bit description

| Bit | Symbol         | Description                             |

|-----|----------------|-----------------------------------------|

| 16  | PLL_LOCK_RT    | Real-time status of the PPL             |

|     |                | 0 PLL not locked                        |

|     |                | 1 PLL locked                            |

|     |                | Reset condition: POR                    |

| 15  | EXT_FIN_SEL_RT | Real-time status of FIN clock selection |

|     |                | 0 Internal clock oscillator is selected |

|     |                | 1 External FIN clock is selected        |

|     |                | Reset condition: POR                    |

VR5500 Product data sheet

# **VR5500**

## High voltage PMIC with multiple SMPS and LDO

| Bit | Symbol      | Description                                       |

|-----|-------------|---------------------------------------------------|

| 14  | EXT_FIN_DIS | Disable request of EXT FIN selection at PLL input |

|     |             | 0 No effect                                       |

|     |             | 1 Disable FIN selection                           |

|     |             | Reset condition: POR                              |

| 13  | MAIN_NORMAL | Main state machine status                         |

|     |             | 0 Main state machine is not in Normal mode        |

|     |             | 1 Main state machine is in Normal mode            |

|     |             | Reset condition: POR                              |

| 10  | W2DIS       | WAKE2 wake up disable                             |

|     |             | 0 wake up enable                                  |

|     |             | 1 wake up disable                                 |

|     |             | Reset condition: POR                              |

| 9   | W1DIS       | WAKE1 wake up disable                             |

|     |             | 0 Wake up enable                                  |

|     |             | 1 Wake up disable                                 |

|     |             | Reset condition: POR                              |

| 8   | GOTOSTBY    | Standby mode request                              |

|     |             | 0 Device remains in current state                 |

|     |             | 1 Device enters in Standby mode                   |

|     |             | Reset condition: POR                              |

# 16.5 M\_REG\_CTRL1 register

| Table 14. M | REG_CTRL1       | register bit a | llocation |          |          |          |          |          |

|-------------|-----------------|----------------|-----------|----------|----------|----------|----------|----------|

| Bit         | 23              | 22             | 21        | 20       | 19       | 18       | 17       | 16       |

| Write       | VPRE_<br>PD_DIS | VPDIS          | BOOSTDIS  | BUCK1DIS | BUCK2DIS | BUCK3DIS | LDO1DIS  | LDO2DIS  |

| Read        | VPRE_<br>PD_DIS | RESERVED       | RESERVED  | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED |

| Reset       | 0               | 0              | 0         | 0        | 0        | 0        | 0        | 0        |

|             |                 |                | Í.        | Í        | Í        | 1        |          | í -      |

| Bit         | 15              | 14             | 13        | 12       | 11       | 10       | 9        | 8        |

| Write       | 0               | VPEN           | BOOSTEN   | BUCK1EN  | BUCK2EN  | BUCK3EN  | LDO1EN   | LDO2EN   |

| Read        | RESERVED        | RESERVED       | RESERVED  | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED |

| Reset       | 0               | 0              | 0         | 0        | 0        | 0        | 0        | 0        |

#### Table 15. M\_REG\_CTRL1 register bit description

| Bit | Symbol      | Description                                                           |

|-----|-------------|-----------------------------------------------------------------------|

| 23  | VPRE_PD_DIS | Force disable of VPRE pull-down                                       |

|     |             | 0 No effect (VPRE pull-down is automatically controlled by the logic) |

|     |             | 1 VPRE pull-down disable request                                      |

|     |             | Reset condition: POR                                                  |

# **VR5500**

## High voltage PMIC with multiple SMPS and LDO

| Bit | Symbol   | Description                                       |

|-----|----------|---------------------------------------------------|

| 22  | VPDIS    | Disable request of VPRE                           |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 VPRE disable request                            |

|     |          | Reset condition: POR                              |

| 21  | BOOSTDIS | Disable request of BOOST                          |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 BOOST disable request                           |

|     |          | Reset condition: POR                              |

| 20  | BUCK1DIS | Disable request of BUCK1                          |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 BUCK1 disable request                           |

|     |          | Reset condition: POR                              |

| 19  | BUCK2DIS | Disable request of BUCK2                          |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 BUCK2 disable request                           |

|     |          | Reset condition: POR                              |

| 18  | BUCK3DIS | Disable request of BUCK3                          |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 BUCK3 disable request                           |

|     |          | Reset condition: POR                              |

| 17  | LDO1DIS  | Disable request of LDO1                           |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 LDO1 disable request                            |

|     |          | Reset condition: POR                              |

| 16  | LDO2DIS  | Disable request of LDO2                           |

|     |          | 0 no effect (regulator remains in existing state) |

|     |          | 1 LDO2 disable request                            |

|     |          | Reset condition: POR                              |

| 14  | VPEN     | Enable request of VPRE                            |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 VPRE enable request (after a VPDIS request)     |

|     |          | Reset condition: POR                              |

| 13  | BOOSTEN  | Enable request of BOOST                           |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 BOOST enable request                            |

|     |          | Reset condition: POR                              |

| 12  | BUCK1EN  | Enable request of BUCK1                           |

|     |          | 0 No effect (regulator remains in existing state) |

|     |          | 1 BUCK1 enable request                            |

|     |          | Reset condition: POR                              |

# **VR5500**

#### High voltage PMIC with multiple SMPS and LDO

| Bit | Symbol  | Description                                       |

|-----|---------|---------------------------------------------------|

| 11  | BUCK2EN | Enable request of BUCK2                           |

|     |         | 0 No effect (regulator remains in existing state) |

|     |         | 1 BUCK2 enable request                            |

|     |         | Reset condition: POR                              |

| 10  | BUCK3EN | Enable request of BUCK3                           |

|     |         | 0 No effect (regulator remains in existing state) |

|     |         | 1 BUCK3 enable request                            |

|     |         | Reset condition: POR                              |

| 9   | LDO1EN  | Enable request of LDO1                            |

|     |         | 0 No effect (regulator remains in existing state) |

|     |         | 1 LDO1 enable request                             |

|     |         | Reset condition: POR                              |

| 8   | LDO2EN  | Enable request of LDO2                            |

|     |         | 0 no effect (regulator remains in existing state) |

|     |         | 1 LDO2 enable request                             |

|     |         | Reset condition: POR                              |

### 16.6 M\_REG\_CTRL2 register

#### Table 16. M\_REG\_CTRL2 register bit allocation

| Bit   | 23          | 22       | 21              | 20              | 19              | 18              | 17             | 16             |

|-------|-------------|----------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|

| Write | VBSTSR[1:0] |          | BOOSTT<br>SDCFG | BUCK1T<br>SDCFG | BUCK2T<br>SDCFG | BUCK3T<br>SDCFG | LDO1T<br>SDCFG | LDO2T<br>SDCFG |

| Read  | VBSTSR[1:0] |          | BOOSTT<br>SDCFG | BUCK1T<br>SDCFG | BUCK2T<br>SDCFG | BUCK3T<br>SDCFG | LDO1T<br>SDCFG | LDO2T<br>SDCFG |

| Reset | OTP         | OTP      | OTP             | OTP             | OTP             | OTP             | OTP            | OTP            |

|       | 17          |          | 10              | 10              |                 | 10              | •              | •              |

| Bit   | 15          | 14       | 13              | 12              | 11              | 10              | 9              | 8              |

| Write | 0           | 0        | 0               | VPRESF          | RLS[1:0]        | 0               | VPRESRHS[1.0]  |                |

| Read  | RESERVED    | RESERVED | RESERVED        | VPRESF          | RLS[1:0]        | RESERVED        | VPRESRHS[1:0]  |                |

| Reset | 0           | 0        | 0               | 1               | 1               | 0               | OTP            | OTP            |

#### Table 17. M\_REG\_CTRL2 register bit description

| Bit      | Symbol      | Description                       |

|----------|-------------|-----------------------------------|

| 23 to 22 | VBSTSR[1:0] | VBOOST low-side slew rate control |

|          |             | 00 50 V/µs - slow                 |

|          |             | 01 100 V/µs – medium              |

|          |             | 10 300 V/µs – fast                |

|          |             | 11 500 V/µs – ultra fast          |

|          |             | Reset condition: POR              |

VR5500 Product data sheet

# **VR5500**

## High voltage PMIC with multiple SMPS and LDO

| Bit      | Symbol        | Description                                                  |

|----------|---------------|--------------------------------------------------------------|

| 21       | BOOSTTSDCFG   | BOOST behavior in case of TSD                                |

|          |               | 0 Regulator shutdown                                         |

|          |               | 1 Regulator shutdown and state machine transition to DEEP-FS |

|          |               | Reset condition: POR                                         |

| 20       | BUCK1TSDCFG   | BUCK1 behavior in case of TSD                                |

|          |               | 0 Regulator shutdown                                         |

|          |               | 1 Regulator shutdown and state machine transition to DEEP-FS |

|          |               | Reset condition: POR                                         |

| 19       | BUCK2TSDCFG   | BUCK2 behavior in case of TSD                                |

|          |               | 0 Regulator shutdown                                         |

|          |               | 1 Regulator shutdown and state machine transition to DEEP-FS |

|          |               | Reset condition: POR                                         |

| 18       | BUCK3TSDCFG   | BUCK3 behavior in case of TSD                                |

|          |               | 0 Regulator shutdown                                         |

|          |               | 1 Regulator shutdown and state machine transition to DEEP-FS |

|          |               | Reset condition: POR                                         |

| 17       | LDO1TSDCFG    | LDO1 behavior in case of TSD                                 |

|          |               | 0 Regulator shutdown                                         |