#### **FEATURES AND BENEFITS**

- Automotive AEC-Q100 qualified

- 3.5 to 36  $V_{\rm IN}$  operating range, 40  $V_{\rm IN}$  maximum

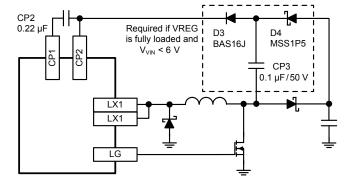

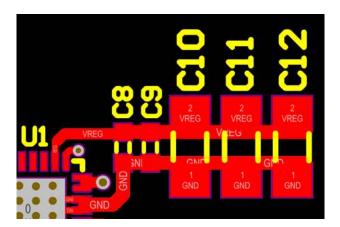

- Buck or buck-boost pre-regulator (VREG)

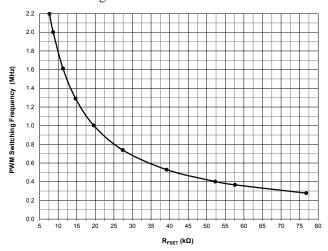

- Adjustable PWM switching frequency: 250 kHz to 2.4 MHz

- PWM frequency can be synchronized to external clock

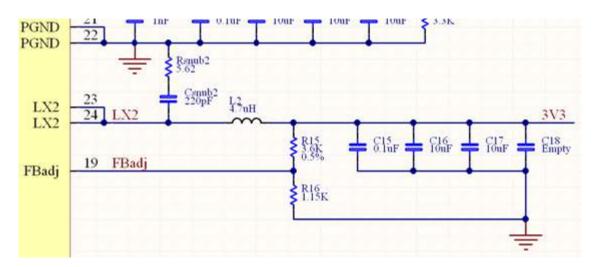

- Synchronous buck regulator (ADJ) delivers 0.8 to 3.3 V

- 5 V internal LDO for remote sensors with foldback shortcircuit and short-to-battery protections (V5P)

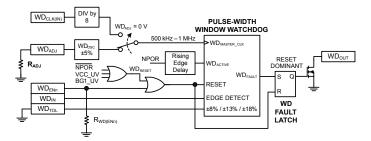

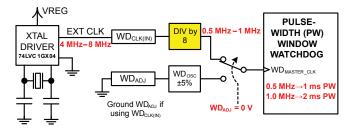

- Programmable pulse-width window watchdog (PWWD) with scalable activation delay and selectable tolerance

- Internal watchdog clock with  $\pm 5\%$  accuracy

- Accepts external WD clock for extreme accuracy

- Active-low Watchdog Enable pin (WD<sub>ENn</sub>)

- Dual bandgaps for increased reliability: BG<sub>VREF</sub>, BG<sub>FAULT</sub>

- Power-on reset (NPOR) with rising delay of 2 ms monitors the synchronous buck output

- PowerOK output monitors the 5 V LDO (POK5V)

- Logic-enable input for microprocessor control (ENB)

- High-voltage ignition enable input (ENBAT)

- ENBAT status indicator output (ENBATS)

- SLEW rate control helps reduce EMI/EMC

- Frequency dithering helps reduce EMI/EMC

- OV and UV protection for both output supply rails

- Pin-to-pin and pin-to-ground tolerant at every pin

- -40°C to 150°C junction temperature range

- Thermal shutdown protection

#### **APPLICATIONS**

- ☐ Electronic power steering (EPS) modules

- ☐ Automotive power trains

- □ CAN power supplies

- ☐ High-temperature applications

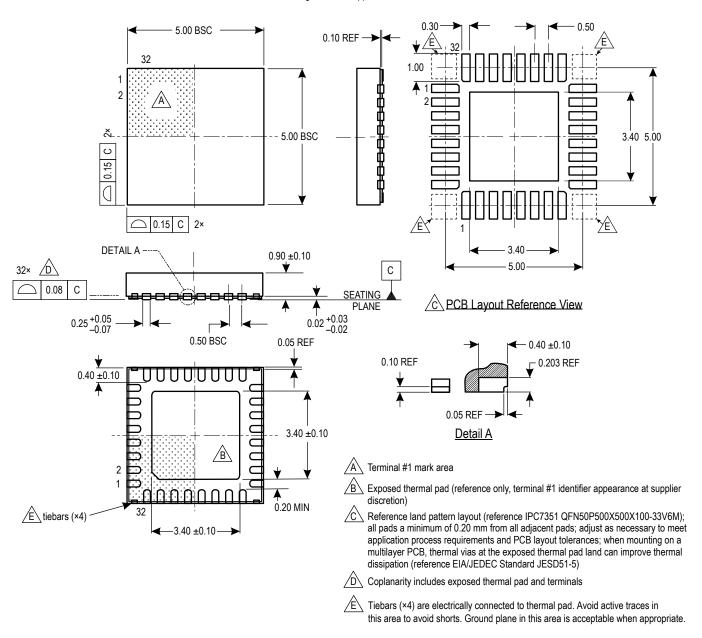

PACKAGE: 32-Pin QFN (suffix ET)

Not to scale

#### DESCRIPTION

The A4413 is a power management IC that can be configured as a buck or buck-boost pre-regulator to efficiently convert automotive battery voltages into a tightly regulated intermediate voltage complete with control, diagnostics, and protections. The output of the pre-regulator supplies both a 5 V, 75  $mA_{MAX}$ high-voltage protected LDO for remote sensors (V5P), and a 0.8 to 3.3 V, 800 mA<sub>MAX</sub> adjustable synchronous buck regulator (ADJ). Designed to supply microprocessor power supplies in high-temperature environments, the A4413 is ideal for under hood and other automotive applications.

The A4413 can be enabled by its logic-level (ENB) or highvoltage (ENBAT) input. Diagnostic outputs from the A4413 include a power-on-reset output (NPOR) with a 2 ms rising delay to monitor the synchronous buck, a PowerOK output to monitor the 5 V LDO (POK5V), and an ENBAT status output (ENBATS). Dual bandgaps—one for regulation and one for fault detection—improve long-term reliability of the A4413.

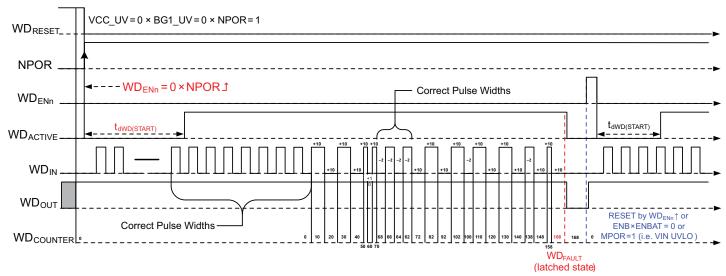

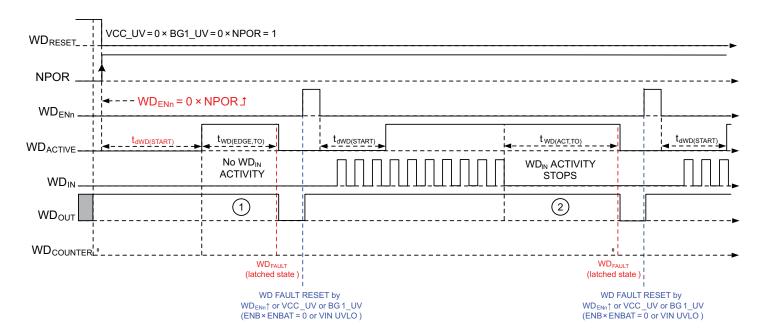

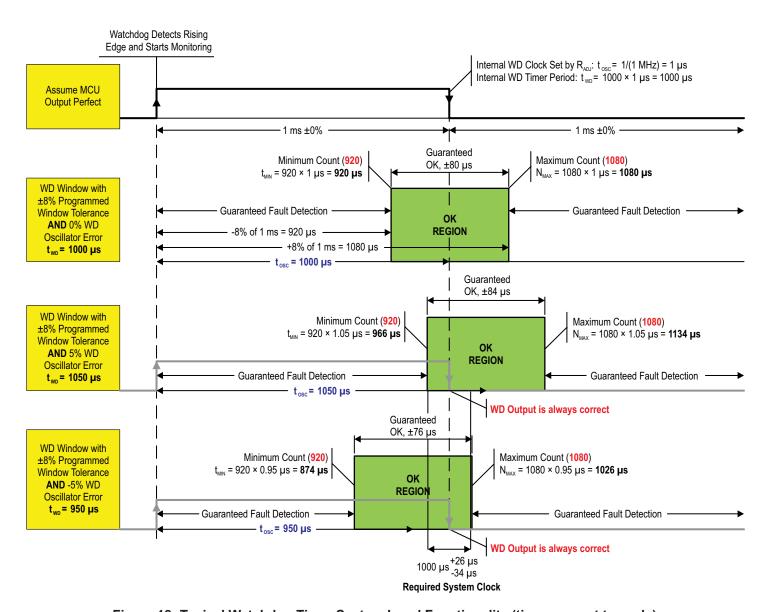

The A4413 contains a pulse-width window watchdog (PWWD) timer that can be programmed to detect pulse widths from 1 to 2 ms (WD<sub>ADI</sub>). The watchdog timer has an activation delay that scales with the pulse-width setting to accommodate processor startup. The tolerance of the watchdog's window can be set to  $\pm 8\%$ ,  $\pm 13\%$ , or  $\pm 18\%$  using the WD<sub>TOL</sub> pin. The watchdog timer has an active-low enable pin  $(WD_{ENn})$  to facilitate initial factory programming or field reflash programming.

Protection features include under- and overvoltage lockout on both output supply rails. In case of a shorted output, the V5P LDO features foldback overcurrent protection. In addition, the V5P output is protected from a short-to-battery event. Both switching regulators include pulse-by-pulse current limit, hiccup mode short-circuit protection, LX short-circuit protection, missing asynchronous diode protection (VREG only), and thermal shutdown (TSD).

The A4413 is supplied in a low-profile 32-lead, 5 mm × 5 mm, 0.5 mm pitch QFN package (suffix "ET") with exposed thermal pad.

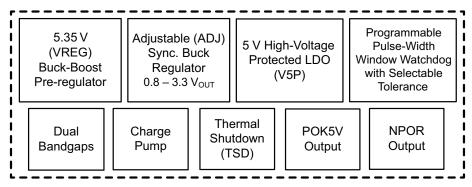

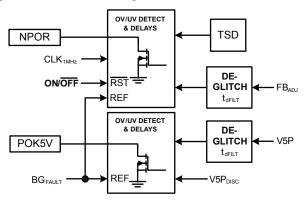

A4413 Simplified Block Diagram

#### **SELECTION GUIDE**

| Part Number  | Temperature Range | Package                     | Packing <sup>1</sup>        | Lead Frame     |

|--------------|-------------------|-----------------------------|-----------------------------|----------------|

| A4413KETTR-J | –40°C to 135°C    | 32-pin QFN with thermal pad | 1500 pieces per 7-inch reel | 100% matte tin |

<sup>&</sup>lt;sup>1</sup> Contact Allegro for additional packing options.

#### **ABSOLUTE MAXIMUM RATINGS<sup>2</sup>**

| Characteristic            | Symbol                                                 | Notes                                       | Rating                         | Unit |

|---------------------------|--------------------------------------------------------|---------------------------------------------|--------------------------------|------|

| VIN                       | V <sub>VIN</sub>                                       |                                             | -0.3 to 40                     | V    |

|                           |                                                        | With current limiting resistor <sup>3</sup> | -13 to 40                      | V    |

| ENBAT                     | V <sub>ENBAT</sub>                                     |                                             | -0.3 to 8                      | V    |

|                           | I <sub>ENBAT</sub>                                     |                                             | ±75                            | mA   |

|                           |                                                        |                                             | -0.3 to V <sub>VIN</sub> + 0.3 | V    |

| LX1                       | $V_{LX1}$                                              | t < 250 ns                                  | -1.5                           | V    |

|                           |                                                        | t < 50 ns                                   | V <sub>VIN</sub> + 3 V         | V    |

| SLEW                      | V <sub>SLEW</sub>                                      |                                             | -0.3 to 18                     | V    |

| VCP, CP1, CP2             | V <sub>VCP</sub> , V <sub>CP1</sub> , V <sub>CP2</sub> |                                             | -0.3 to 50                     | V    |

| V5P                       | V <sub>V5P</sub>                                       | Independent of V <sub>VIN</sub>             | -1 to 40                       | V    |

| All other pins            |                                                        |                                             | -0.3 to 7                      | V    |

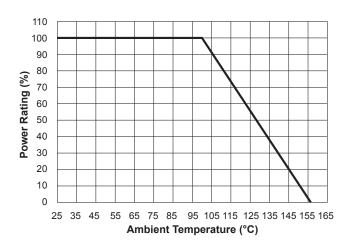

| Ambient Temperature       | T <sub>A</sub>                                         | Range K for automotive                      | -40 to 135                     | °C   |

| Junction Temperature      | T <sub>J</sub>                                         |                                             | -40 to 150                     | °C   |

| Storage Temperature Range | T <sub>stg</sub>                                       |                                             | -40 to 150                     | °C   |

<sup>2</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

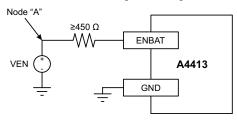

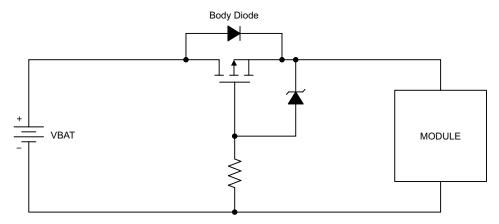

<sup>&</sup>lt;sup>3</sup> The higher ENBAT ratings (–13 V and 40 V) are measured at node "A" in the following circuit configuration:

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

|                                    |                | , 11                                          |       |      |

|------------------------------------|----------------|-----------------------------------------------|-------|------|

| Characteristic                     | Symbol         | Test Conditions 4                             | Value | Unit |

| Junction-to-Pad Thermal Resistance | $R_{	heta JC}$ | 4-layer PCB based on JEDEC standard footprint | 30    | °C/W |

$<sup>^{\</sup>rm 4}$  Additional thermal information available on the Allegro website.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

#### **Table of Contents**

| F | Features and Benefits                                     | 1  | Bias Supply (VCC)                                                                    | 20 |

|---|-----------------------------------------------------------|----|--------------------------------------------------------------------------------------|----|

|   | Description                                               | 1  | Charge Pump (VCP, CP1, CP2)                                                          | 20 |

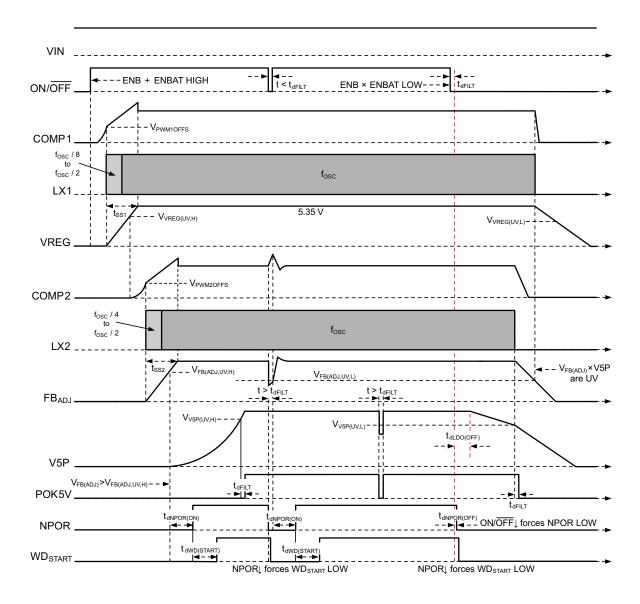

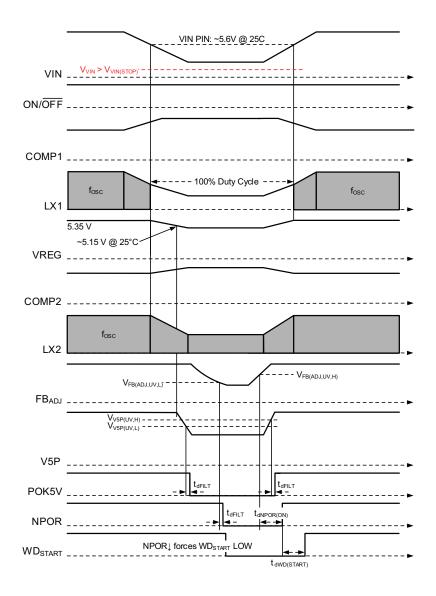

| 1 | Applications                                              | 1  | Startup and Shutdown Sequences                                                       | 21 |

| F | Package                                                   | 1  | Fault Reporting (NPOR, POK5V)                                                        | 21 |

| ç | Simplified Block Diagram                                  | 1  | Startup and Shutdown Logic Table                                                     | 22 |

| ç | Specifications                                            | 2  | Summary of Fault Mode Operation Table                                                | 23 |

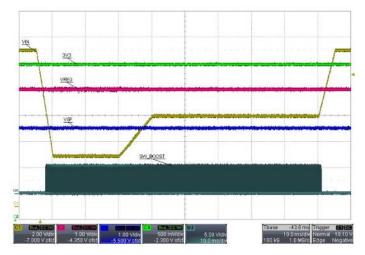

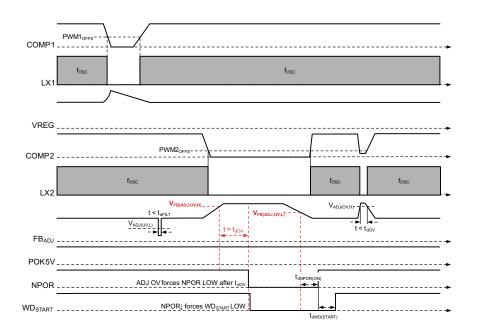

|   | Selection Guide                                           | 2  | Timing Diagrams                                                                      | 26 |

|   | Absolute Maximum Ratings                                  | 2  | Design and Component Selection                                                       | 31 |

|   | Thermal Characteristics                                   | 2  | PWM Switching Frequency (R <sub>FSET</sub> )                                         | 31 |

| F | Functional Block Diagram                                  | 4  | Charge Pump Capacitors                                                               | 31 |

| F | Pinout Diagram and Terminal List Table                    | 6  | Pre-Regulator Output Inductor (L1)                                                   | 31 |

| E | Electrical Characteristics                                | 7  | Pre-Regulator Output Capacitance                                                     | 31 |

|   | Buck and Buck-Boost Pre-Regulator                         | 7  | Pre-Regulator Ceramic Input Capacitance                                              | 32 |

|   | Adjustable Synchronous Buck Regulator                     | 10 | Pre-Regulator Asynchronous Diode (D1)                                                | 32 |

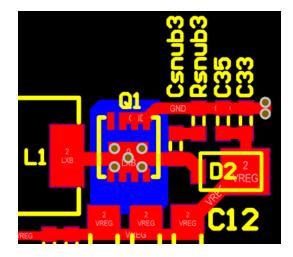

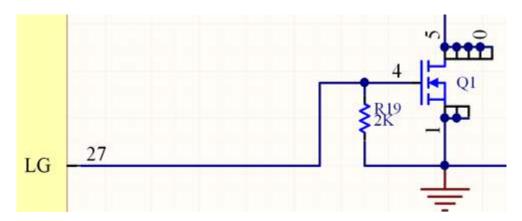

|   | Control Inputs                                            | 12 | Pre-Regulator Boost MOSFET (Q1)                                                      | 32 |

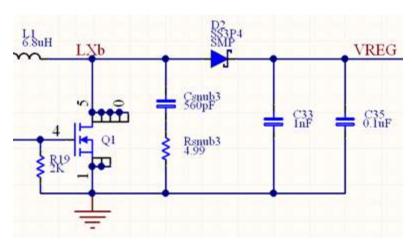

|   | Diagnostic Outputs                                        | 13 | Pre-Regulator Boost Diode (D2)                                                       | 32 |

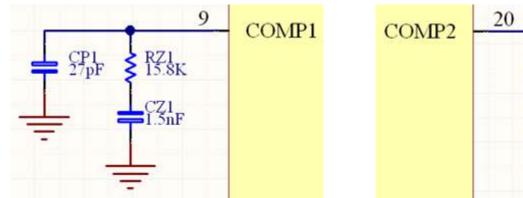

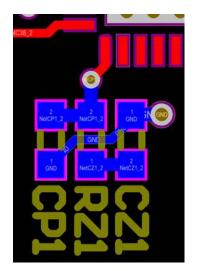

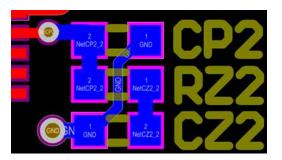

|   | Pulse-Width Window Watchdog (PWWD)                        | 15 | Pre-Regulator Compensation (R <sub>Z1</sub> , C <sub>Z1</sub> , C <sub>P1</sub> )    | 32 |

| F | Functional Description                                    | 16 | Synchronous Buck Component Selection                                                 | 34 |

|   | Overview                                                  | 16 | Synchronous Buck Output Inductor (L2)                                                | 34 |

|   | Buck-Boost Pre-Regulator (VREG)                           | 16 | Synchronous Buck Output Capacitance                                                  | 34 |

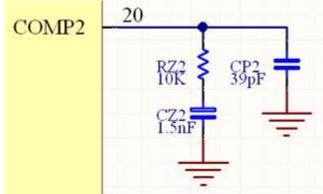

|   | Adjustable Synchronous Buck Regulator (ADJ)               | 17 | Synchronous Buck Compensation (R <sub>Z2</sub> , C <sub>Z2</sub> , C <sub>P2</sub> ) | 35 |

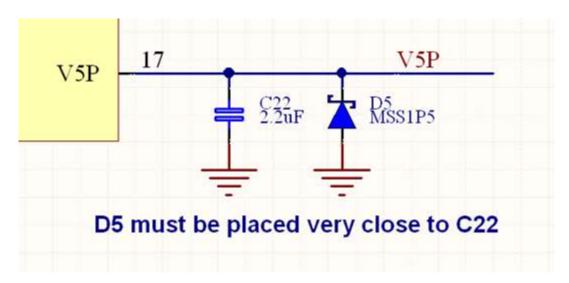

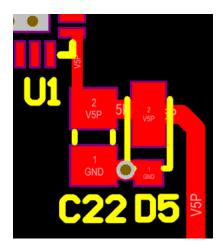

|   | Low-Dropout Linear Regulator (LDO)                        | 18 | Linear Regulator (V5P)                                                               | 36 |

|   | Pulse-Width Window Watchdog (PWWD)                        | 18 | Internal Bias (VCC)                                                                  | 36 |

|   | Dual Bandgaps (BG <sub>VREF</sub> , BG <sub>FAULT</sub> ) | 19 | Signal Pins (NPOR, POK5V, WD <sub>OUT</sub> , ENBATS)                                | 36 |

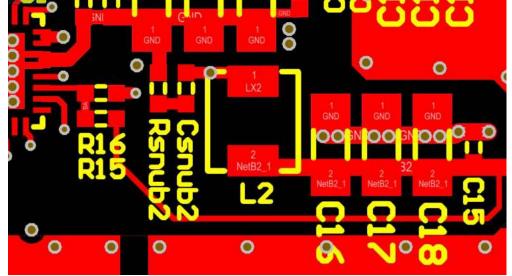

|   | Adjustable Frequency, Sync. (FSET/SYNC)                   | 19 | RC Snubber Calculations (R <sub>SNUBx</sub> , C <sub>SNUBx</sub> )                   | 36 |

|   | Frequency Dithering and LX1 Slew Rate Control             | 20 | PCB Layout Recommendations                                                           | 39 |

|   | Enable Inputs (ENB, ENBAT)                                | 20 | Package Outline Drawing                                                              | 47 |

|   |                                                           |    |                                                                                      |    |

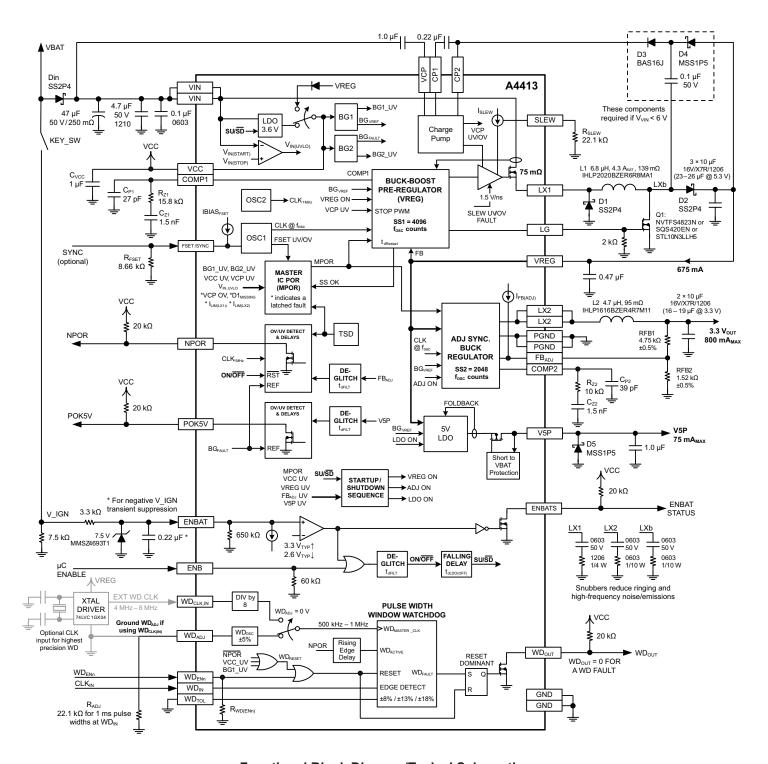

#### **Functional Block Diagram/Typical Schematic**

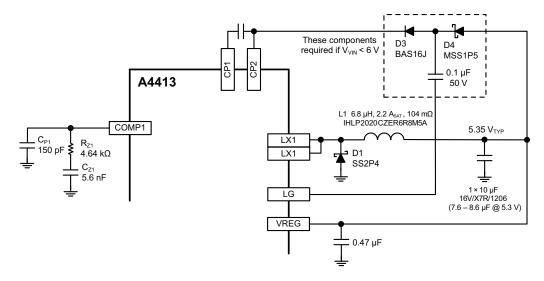

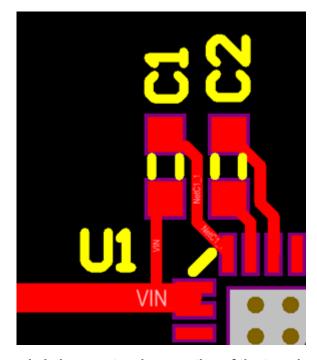

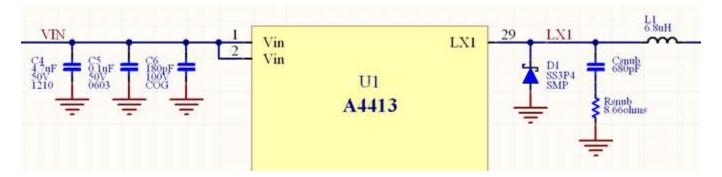

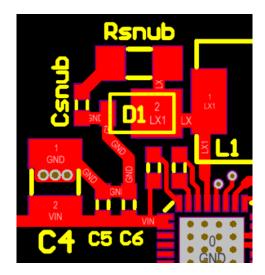

Buck-Boost Mode ( $f_{OSC}$  = 2 MHz), Using a Series Diode for Reverse-Battery Protection ( $D_{IN}$ )

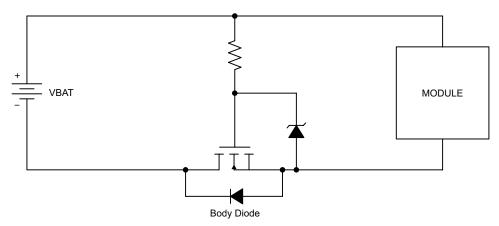

Functional Block Diagram Modifications for Buck-Only Mode (f<sub>OSC</sub> = 2 MHz)

Functional Block Diagram Using a PMOS FET for Reverse-Battery Protection Instead of a Series Schottky Diode ( $D_{\rm IN}$ )

Functional Block Diagram Using an NMOS FET for Reverse-Battery Protection Instead of a Series Schottky Diode  $(D_{\text{IN}})$

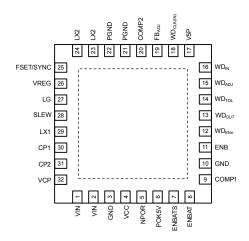

## Package ET, 32-Pin QFN Pinout Diagram

#### **Terminal List Table**

| Number | Name                  | Function                                                                                                                                                   |

|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2   | VIN                   | Input voltage pins                                                                                                                                         |

| 3, 10  | GND                   | Ground pin                                                                                                                                                 |

| 4      | VCC                   | Internal voltage regulator bypass capacitor pin                                                                                                            |

| 5      | NPOR                  | Active-low, open-drain output indicating when the synchronous buck is out of regulation                                                                    |

| 6      | POK5V                 | Open-drain output indicating when the V5P rail is out of regulation                                                                                        |

| 7      | ENBATS                | Open-drain output indicating the status of the ENBAT (IGN) signal                                                                                          |

| 8      | ENBAT                 | Ignition enable input from the key/switch via a series resistor                                                                                            |

| 9      | COMP1                 | Error amplifier compensation network pin for the buck-boost pre-regulator                                                                                  |

| 11     | ENB                   | Logic compatible enable input from a microcontroller or DSP                                                                                                |

| 12     | WD <sub>ENn</sub>     | Active-low watchdog enable input from a microcontroller or DSP; open/low = WD is enabled, high = WD is disabled                                            |

| 13     | WD <sub>OUT</sub>     | Open-drain watchdog output; normally high impedance; latched low if a watchdog fault occurs                                                                |

| 14     | WD <sub>TOL</sub>     | Selectable watchdog tolerance: low = ±8%, float = ±13%, high (to VCC) = ±18%                                                                               |

| 15     | WD <sub>ADJ</sub>     | The watchdog window time is set by connecting R <sub>ADJ</sub> from this pin to ground                                                                     |

| 16     | WD <sub>IN</sub>      | Watchdog pulse train input from a microcontroller or DSP                                                                                                   |

| 17     | V5P                   | 5 V protected regulator output                                                                                                                             |

| 18     | WD <sub>CLK(IN)</sub> | WD clock input for highest WD accuracy; if this pin is used, the WD <sub>ADJ</sub> pin must be grounded. If this pin is unused it should be left floating. |

| 19     | FB <sub>ADJ</sub>     | Feedback pin for the adjustable synchronous buck regulator                                                                                                 |

| 20     | COMP2                 | Error amplifier compensation network pin for the adjustable synchronous buck regulator                                                                     |

| 21, 22 | PGND                  | Power ground for the adjustable synchronous regulator and its gate driver                                                                                  |

| 23, 24 | LX2                   | Switching node for the adjustable synchronous buck regulator                                                                                               |

| 25     | FSET/SYNC             | Frequency setting and synchronization input                                                                                                                |

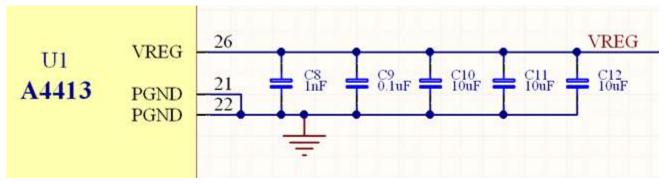

| 26     | VREG                  | Output of the pre-regulator and input to the LDO and adjustable synchronous buck                                                                           |

| 27     | LG                    | Boost gate drive output for the buck-boost pre-regulator                                                                                                   |

| 28     | SLEW                  | Slew rate adjustment for the rise time of LX1                                                                                                              |

| 29     | LX1                   | Switching node for the buck-boost pre-regulator                                                                                                            |

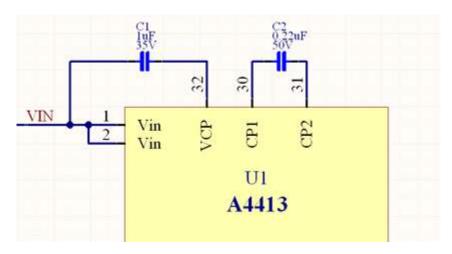

| 30     | CP1                   | Charge pump capacitor connection                                                                                                                           |

| 31     | CP2                   | Charge pump capacitor connection                                                                                                                           |

| 32     | VCP                   | Charge pump reservoir capacitor                                                                                                                            |

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

### ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS 1:

Valid at 3.5 V  $^{(4)}$  < V<sub>VIN</sub> < 36 V, -40°C < T<sub>A</sub> = T<sub>J</sub> < 150°C, unless otherwise specified

| Characteristic                           | Symbol                       | Test Conditions                                                                                                                                                                                                     | Min. | Тур. | Max. | Unit |

|------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| GENERAL SPECIFICATIONS                   |                              |                                                                                                                                                                                                                     |      |      |      |      |

| Operating Input Voltage                  | V                            | Buck-Boost mode, after $V_{VIN} > V_{VIN(START)}$ , and $V_{ENB} > 2$ V, NPOR = 1, POK5V = 1                                                                                                                        | 3.5  | 13.5 | 36   | V    |

| Operating input voltage                  | V <sub>VIN</sub>             | Buck Only mode, after $V_{VIN} > V_{VIN(START)}$ , and $V_{ENB} > 2$ V, NPOR = 1, POK5V = 1                                                                                                                         | 5.7  | 13.5 | 36   | V    |

| VIN UVLO Start Voltage                   | V <sub>VIN(START)</sub>      | V <sub>VIN</sub> rising, Buck or Boost mode                                                                                                                                                                         | 5.10 | 5.40 | 5.70 | V    |

| VIN UVLO Stop Voltage                    | V <sub>VIN(STOP)</sub>       | V <sub>VIN</sub> falling, Buck or Boost mode                                                                                                                                                                        | 2.88 | 3.04 | 3.20 | V    |

| VIN UVLO Hysteresis                      | V <sub>VIN(HYS)</sub>        | V <sub>VIN(START)</sub> – V <sub>VIN(STOP)</sub>                                                                                                                                                                    | _    | 2.36 | _    | V    |

| VIN Dropout Voltages,                    | V <sub>VIN(STOP1,BUCK)</sub> | NPOR = 1, POK5V ↓                                                                                                                                                                                                   | -    | 5.0  | 5.3  | V    |

| Buck Mode, V <sub>VIN</sub> Falling      | V <sub>VIN(STOP2,BUCK)</sub> | $V_{VCP} < V_{CPUV(L)}$ and NPOR $\downarrow$ , POK5V = 0                                                                                                                                                           | -    | 4.0  | 4.4  | V    |

| Supply Quippent Current 1                | IQ                           | $V_{VIN} = 13.5 \text{ V}, V_{IGN} \ge 3.6 \text{ V or} $<br>$V_{ENB} \ge 2 \text{ V}, V_{VREG} = 5.6 \text{ V (no PWM)}$                                                                                           | -    | 10   | _    | mA   |

| Supply Quiescent Current <sup>1</sup>    | I <sub>Q(SLEEP)</sub>        | V <sub>VIN</sub> = 13.5 V, V <sub>IGN</sub> ≤ 2.2 V and V <sub>ENB</sub> ≤ 0.8 V                                                                                                                                    | -    | _    | 10   | μA   |

| PWM SWITCHING FREQUENC                   | Y AND DITHERIN               | IG                                                                                                                                                                                                                  |      |      |      |      |

|                                          |                              | $R_{FSET}$ = 8.66 k $\Omega$                                                                                                                                                                                        | 1.8  | 2.0  | 2.2  | MHz  |

| Switching Frequency                      | f <sub>osc</sub>             | $R_{FSET} = 19.6 \text{ k}\Omega^{(2)}$                                                                                                                                                                             | _    | 1.0  | _    | MHz  |

|                                          |                              | $R_{FSET} = 52.3 \text{ k}\Omega^{(2)}$                                                                                                                                                                             | 343  | 400  | 457  | kHz  |

| Frequency Dithering                      | Δf <sub>OSC</sub>            | As a percent of f <sub>OSC</sub>                                                                                                                                                                                    | _    | ±12  | _    | %    |

| Dither/Slew Start Threshold 1            | V <sub>VIN(DS,ON1)</sub>     | V <sub>VIN</sub> rising                                                                                                                                                                                             | 16.9 | 18.0 | 19.1 | V    |

| Dither/Slew Stop Threshold 1             | V <sub>VIN(DS,OFF1)</sub>    | V <sub>VIN</sub> falling                                                                                                                                                                                            | _    | 16.6 | _    | V    |

| Dither/Slew Start Threshold 2            | V <sub>VIN(DS,ON2)</sub>     | V <sub>VIN</sub> rising                                                                                                                                                                                             | _    | 9.0  | _    | V    |

| Dither/Slew Stop Threshold 2             | V <sub>VIN(DS,OFF2)</sub>    | V <sub>VIN</sub> falling                                                                                                                                                                                            | 7.8  | 8.3  | 8.8  | V    |

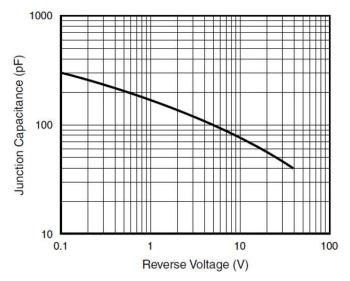

| CHARGE PUMP (VCP)                        |                              |                                                                                                                                                                                                                     |      |      |      |      |

| Output Voltage                           | V                            | $\begin{aligned} & V_{VCP} - V_{VIN},  V_{VIIN} = 13.5   \text{V},  V_{VREG} = 5.50   \text{V}, \\ & I_{VCP} = 5.0   \text{mA},  V_{COMP1} = V_{COMP2} = 0   \text{V}, \\ & V_{ENB} = 3.3   \text{V} \end{aligned}$ | 4.1  | 6.6  | _    | V    |

| Output voltage                           | V <sub>VCP</sub>             | $\begin{aligned} & V_{VCP} - V_{VIN}, V_{VIN} = 4.0 \; V, V_{VREG} = 5.25 \; V, \\ & I_{VCP} = 5.0 \; mA, \; V_{COMP1} = V_{COMP2} = 0 \; V, \\ & V_{ENB} = 3.3 \; V \end{aligned}$                                 | 3.3  | _    | _    | V    |

| Switching Frequency                      | f <sub>SW(CP)</sub>          |                                                                                                                                                                                                                     | -    | 65   | -    | kHz  |

| VCC PIN VOLTAGE                          |                              |                                                                                                                                                                                                                     |      |      |      |      |

| Output Voltage                           | V <sub>VCC</sub>             | V <sub>VREG</sub> = 5.35 V                                                                                                                                                                                          | _    | 4.65 | _    | V    |

| Thermal Protection                       |                              |                                                                                                                                                                                                                     |      |      |      |      |

| Thermal Shutdown Threshold <sup>2</sup>  | T <sub>TSD</sub>             | $T_J$ rising                                                                                                                                                                                                        | 155  | 170  | 185  | °C   |

| Thermal Shutdown Hysteresis <sup>2</sup> | T <sub>HYS</sub>             |                                                                                                                                                                                                                     | _    | 20   | _    | °C   |

|                                          |                              |                                                                                                                                                                                                                     |      |      |      |      |

<sup>&</sup>lt;sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>&</sup>lt;sup>2</sup> Ensured by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>4</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG} > V_{VREG(UV,H)}$  are satisfied before  $V_{VIN}$  is reduced.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

## ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS $^1$ (continued): Valid at 3.5 V $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$

| Characteristic                            | Symbol                    | Test Conditions                                                                                                          | Min. | Тур. | Max. | Unit |

|-------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUTPUT VOLTAGE SPECIFICAT                 | IONS                      |                                                                                                                          | •    | •    |      |      |

| Buck Output Voltage – Regulating          | V <sub>VREG</sub>         | V <sub>VIN</sub> = 13.5 V, ENB = 1, 0.1 A < I <sub>VREG</sub> < 1 A                                                      | 5.25 | 5.35 | 5.45 | V    |

| PULSE-WIDTH MODULATION (P                 | WM)                       |                                                                                                                          |      |      |      |      |

| PWM Ramp Offset                           | V <sub>PWM1OFFS</sub>     | V <sub>COMP1</sub> for 0% duty cycle                                                                                     | _    | 400  | _    | mV   |

| LX1 Rising Slew Rate Control <sup>2</sup> | I V1                      | $V_{VIN}$ = 13.5 V, 10% to 90%, $I_{VREG}$ = 1 A, $R_{SLEW}$ = 22.1 k $\Omega$                                           | _    | 0.90 | _    | V/ns |

| LAT RISHING SIEW Rate Control 2           | LX1 <sub>RISE</sub>       | $V_{VIN}$ = 13.5 V, 10% to 90%, $I_{VREG}$ = 1 A, $R_{SLEW}$ = 150 k $\Omega$                                            | _    | 0.23 | _    | V/ns |

| LX1 Falling Slew Rate <sup>2</sup>        | LX1 <sub>FALL</sub>       | V <sub>VIN</sub> = 13.5 V, 90% to 10%, I <sub>VREG</sub> = 1 A                                                           | _    | 1.0  | _    | V/ns |

| Buck Minimum On-Time                      | t <sub>ON(BUCK,MIN)</sub> |                                                                                                                          | _    | 85   | 150  | ns   |

| Buck Maximum Duty Cycle                   | D <sub>MAX(BUCK)</sub>    | t <sub>OFF(BUCK)</sub> < 50 ns                                                                                           | _    | 100  | _    | %    |

| Boost Duty Cycle <sup>2</sup>             | D <sub>MIN(BST)</sub>     | After V <sub>VIN</sub> > V <sub>VIN(START)</sub> , V <sub>VIN</sub> = 6.5 V                                              | _    | 20   | _    | %    |

| Boost Buty Cycle-                         | D <sub>MAX(BST)</sub>     | After V <sub>VIN</sub> > V <sub>VIN(START)</sub> , V <sub>VIN</sub> = 3.5 V                                              | 57   | 62   | 67   | %    |

| COMP1 to LX1 Current Gain                 | gm <sub>POWER1</sub>      |                                                                                                                          | _    | 3.6  | _    | A/V  |

| Slope Compensation <sup>2</sup>           | 9                         | f <sub>OSC</sub> = 2.0 MHz                                                                                               | 0.73 | 1.04 | 1.34 | A/µs |

| Slope Compensation -                      | S <sub>E1</sub>           | f <sub>OSC</sub> = 400 kHz                                                                                               | 0.15 | 0.23 | 0.31 | A/µs |

| INTERNAL MOSFET                           |                           |                                                                                                                          |      |      |      |      |

|                                           |                           | $V_{VIN} = 13.5 \text{ V}, T_{J} = -40^{\circ}\text{C}^{(2)}, I_{DS} = 0.1 \text{ A}$                                    | _    | 75   | 95   | mΩ   |

| MOSFET On-Resistance                      | R <sub>DSon</sub>         | $V_{VIN} = 13.5 \text{ V}, T_{J} = 25^{\circ}\text{C}$ (3), $I_{DS} = 0.1 \text{ A}$                                     | _    | 110  | 135  | mΩ   |

|                                           |                           | $V_{VIN} = 13.5 \text{ V}, T_{J} = 150^{\circ}\text{C}, I_{DS} = 0.1 \text{ A}$                                          | _    | 220  | 265  | mΩ   |

| MOSEET Lookage                            |                           | IC disabled, $V_{LX1} = 0 \text{ V}$ , $V_{VIN} = 16 \text{ V}$ , $-40^{\circ}\text{C} < T_{J} < 85^{\circ}\text{C}$ (3) | _    | _    | 10   | μА   |

| MOSFET Leakage                            | I <sub>FET(LKG)</sub>     | IC disabled, V <sub>LX1</sub> = 0 V, V <sub>VIN</sub> = 16 V,<br>-40°C < T <sub>J</sub> < 150°C                          | _    | 50   | 150  | μA   |

| ERROR AMPLIFIER                           |                           |                                                                                                                          | •    |      |      |      |

| Open-Loop Voltage Gain                    | A <sub>VOL1</sub>         |                                                                                                                          | _    | 60   | _    | dB   |

| Transconductance                          | am                        | V <sub>VREG</sub> > 2.7 V                                                                                                | 550  | 750  | 950  | μA/V |

| Transconductance                          | gm <sub>EA1</sub>         | V <sub>VREG</sub> < 2.7 V                                                                                                | 275  | 375  | 475  | μA/V |

| Output Current                            | I <sub>EA1</sub>          |                                                                                                                          | _    | ±75  | _    | μA   |

| Maximum Output Valtaga                    |                           | V <sub>VIN</sub> = 12 V                                                                                                  | 1.0  | 1.3  | 1.6  | V    |

| Maximum Output Voltage                    | V <sub>EA1(out,max)</sub> | V <sub>VIN</sub> = 8 V                                                                                                   | 1.3  | 1.7  | 2.1  | V    |

| Minimum Output Voltage                    | V <sub>EA1(out,min)</sub> |                                                                                                                          | _    | _    | 300  | mV   |

| COMP1 Pull-Down Resistance                | R <sub>COMP1</sub>        | HICCUP1 = 1 or FAULT1 = 1 or IC disabled, latched until V <sub>SS1</sub> < V <sub>SS1(RST)</sub>                         | _    | 1    | _    | kΩ   |

<sup>&</sup>lt;sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>&</sup>lt;sup>2</sup> Ensured by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>4</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG} > V_{VREG(UV,H)}$  are satisfied before  $V_{VIN}$  is reduced.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

## ELECTRICAL CHARACTERISTICS – BUCK AND BUCK-BOOST PRE-REGULATOR SPECIFICATIONS $^1$ (continued): Valid at 3.5 V $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$ < $^{(4)}$

| Characteristic                  | Symbol                     | Test Conditions                                                                          | Min. | Тур.                | Max. | Unit                       |

|---------------------------------|----------------------------|------------------------------------------------------------------------------------------|------|---------------------|------|----------------------------|

| BOOST MOSFET (LG) GATE DRIVE    | R                          |                                                                                          | `    | `                   |      |                            |

| LG High Output Voltage          | V <sub>LG(ON)</sub>        | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V                                       | 4.6  | _                   | 5.5  | V                          |

| LG Low Output Voltage           | V <sub>LG(OFF)</sub>       | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> = 5.35 V                                    | _    | 0.2                 | 0.4  | V                          |

| LG Source Current <sup>1</sup>  | I <sub>LG(ON)</sub>        | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V, V <sub>LG</sub> = 1 V                | _    | -300                | _    | mA                         |

| LG Sink Current <sup>1</sup>    | I <sub>LG(OFF)</sub>       | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> = 5.35 V, V <sub>LG</sub> = 1 V             | _    | 150                 | _    | mA                         |

| SOFT-START                      |                            |                                                                                          |      |                     |      |                            |

| SS1 Ramp Time                   | t <sub>SS1</sub>           |                                                                                          | _    | 4096                | _    | f <sub>OSC</sub><br>cycles |

|                                 |                            | V <sub>VREG</sub> < 0.65 V <sub>TYP</sub>                                                | _    | f <sub>OSC</sub> /8 | _    | _                          |

| SS1 PWM Frequency Foldback      | f                          | 0.65 V < V <sub>VREG</sub> < 1.3 V <sub>TYP</sub>                                        | _    | f <sub>OSC</sub> /4 | -    | _                          |

| 331 FWW Frequency Foluback      | f <sub>SW1(SS)</sub>       | 1.3 V < V <sub>VREG</sub> < 2.7 V <sub>TYP</sub>                                         | _    | f <sub>OSC</sub> /2 | -    | _                          |

|                                 |                            | $V_{VREG} > 2.7 V_{TYP}$                                                                 | _    | f <sub>OSC</sub>    | _    | _                          |

| HICCUP MODE                     |                            |                                                                                          |      |                     |      |                            |

| Hiccup1 Enable Delay            | t <sub>HIC1(EN)</sub>      |                                                                                          | _    | 512                 | _    | f <sub>OSC</sub><br>cycles |

| Hiccup1 Recovery Time           | t <sub>HIC1(REC)</sub>     | HICCUP1 = 1                                                                              | _    | 4096                | -    | f <sub>OSC</sub><br>cycles |

| Hiccup1 OCP Counts              |                            | V <sub>VREG</sub> < 1.3 V <sub>TYP</sub> , V <sub>COMP</sub> = V <sub>EA1(out,max)</sub> | _    | 30                  | _    | _                          |

| HICCUPT OCF Counts              | t <sub>HIC1(OCP)</sub>     | $V_{VREG} > 1.3 V_{TYP}, V_{COMP} = V_{EA1(out,max)}$                                    | _    | 120                 | ı    | _                          |

| CURRENT PROTECTIONS             |                            |                                                                                          |      |                     |      |                            |

| Pulse-by-Pulse Current Limit    |                            | $V_{VIN}$ < 9 V, $t_{ON}$ = $t_{ON(MIN)}$                                                | 2.6  | 2.8                 | 3.3  | А                          |

| Fulse-by-Fulse Current Limit    | I <sub>LIM1(ton,min)</sub> | $V_{VIN} > 9 \text{ V}, t_{ON} = t_{ON(MIN)}$                                            | 1.8  | 2.0                 | 2.2  | Α                          |

| LX1 Short-Circuit Current Limit | I <sub>LIM(LX1)</sub>      | Hiccup mode after 1 × I <sub>LIM(LX1)</sub> detection                                    | 5    | 7                   | _    | Α                          |

| MISSING ASYNCHRONOUS DIODE      | (D1) PROTE                 | CTION                                                                                    |      |                     |      |                            |

| Detection Level                 | V <sub>D(OPEN)</sub>       |                                                                                          | -1.8 | -1.6                | -1.2 | V                          |

| Time Filtering <sup>2</sup>     | t <sub>D(OPEN)</sub>       |                                                                                          | 50   | _                   | 250  | ns                         |

<sup>&</sup>lt;sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing),

positive current is defined as going into the node or pin (sinking). <sup>2</sup> Ensured by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

$<sup>^4</sup>$  The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG} > V_{VREG(UV,H)}$  are satisfied before  $V_{VIN}$  is reduced.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

#### ELECTRICAL CHARACTERISTICS - ADJUSTABLE SYNCHRONOUS BUCK REGULATOR1:

Valid at 3.5 V  $^{(4)}$  < V<sub>VIN</sub> < 36 V, -40°C < T<sub>A</sub> = T<sub>J</sub> < 150°C, unless otherwise specified

| Characteristic                            | Symbol                    | Test Conditions                                                                                                 | Min. | Тур. | Max. | Unit |

|-------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| FEEDBACK REFERENCE VOLTAGE                |                           |                                                                                                                 |      |      | ,    |      |

| Reference Voltage                         | V <sub>FB(ADJ)</sub>      |                                                                                                                 | 787  | 800  | 813  | mV   |

| PULSE-WIDTH MODULATION (PWM               |                           |                                                                                                                 |      |      | `    |      |

| PWM Ramp Offset                           | V <sub>PWM2OFFS</sub>     | V <sub>COMP2</sub> for 0% duty cycle                                                                            | -    | 350  | _    | mV   |

| High-Side MOSFET Minimum On-Time          | t <sub>ON(MIN)</sub>      |                                                                                                                 | -    | 65   | 105  | ns   |

| High-Side MOSFET Minimum Off-Time         | t <sub>OFF(MIN)</sub>     | Does not include total gate driver non-overlap time, t <sub>NO</sub>                                            | -    | 80   | 110  | ns   |

| Gate Driver Non-Overlap Time <sup>2</sup> | t <sub>NO</sub>           |                                                                                                                 | -    | 15   | _    | ns   |

| COMP2 to LX2 Current Gain                 | gm <sub>POWER2</sub>      |                                                                                                                 | -    | 2.5  | _    | A/V  |

| Clara Carrananation 2                     |                           | f <sub>OSC</sub> = 2.0 MHz                                                                                      | 0.45 | 0.63 | 0.81 | A/µs |

| Slope Compensation <sup>2</sup>           | S <sub>E2</sub>           | f <sub>OSC</sub> = 400 kHz                                                                                      | 0.12 | 0.14 | 0.19 | A/µs |

| INTERNAL MOSFETS                          | ,                         |                                                                                                                 |      |      | ,    |      |

| ULL OIL MODEST O. D                       | _                         | T <sub>A</sub> = 25°C (3), I <sub>DS</sub> = 100 mA                                                             | -    | 120  | 150  | mΩ   |

| High-Side MOSFET On-Resistance            | R <sub>DSon(HS)</sub>     | I <sub>DS</sub> = 100 mA                                                                                        | _    | 150  | 200  | mΩ   |

| LX2 Node Rise/Fall Time <sup>2</sup>      | t <sub>R/F(LX2)</sub>     | V <sub>VREG</sub> = 5.5 V                                                                                       | -    | 12   | -    | ns   |

|                                           | I <sub>DSS(HS)</sub>      | IC disabled, V <sub>LX2</sub> = 0 V, V <sub>VREG</sub> = 5.5 V,<br>-40°C < T <sub>J</sub> < 85°C <sup>(3)</sup> | -    | _    | 2    | μА   |

| High-Side MOSFET Leakage <sup>1</sup>     |                           | IC disabled, V <sub>LX2</sub> = 0 V, V <sub>VREG</sub> = 5.5 V,<br>-40°C < T <sub>J</sub> < 150°C               | -    | 3    | 15   | μΑ   |

| Law Cide MOOFFT On Basistana              | _                         | T <sub>A</sub> = 25°C <sup>(3)</sup> , I <sub>DS</sub> = 100 mA                                                 | -    | 65   | 75   | mΩ   |

| Low-Side MOSFET On-Resistance             | R <sub>DSon(LS)</sub>     | I <sub>DS</sub> = 100 mA                                                                                        | _    | 80   | 110  | mΩ   |

|                                           |                           | IC disabled, V <sub>LX2</sub> = 5.5 V, –40°C < T <sub>J</sub> < 85°C <sup>(3)</sup>                             | _    | -    | 1    | μA   |

| Low-Side MOSFET Leakage <sup>1</sup>      | I <sub>DSS(LS)</sub>      | IC disabled, V <sub>LX2</sub> = 5.5 V, -40°C < T <sub>J</sub> < 150°C                                           | _    | 4    | 10   | μA   |

| ERROR AMPLIFIER                           | ,                         |                                                                                                                 |      |      |      |      |

| Feedback Input Bias Current <sup>1</sup>  | I <sub>FB(ADJ)</sub>      | V <sub>COMP2</sub> = 0.8 V, V <sub>FB(ADJ)</sub> regulated so that I <sub>COMP2</sub> = 0 A                     | -    | -150 | -350 | nA   |

| Open-Loop Voltage Gain <sup>2</sup>       | A <sub>VOL2</sub>         |                                                                                                                 | -    | 60   | _    | dB   |

| Tuesdandustana                            |                           | $I_{COMP2} = 0 \mu A, V_{FB(ADJ)} > 500 \text{ mV}$                                                             | 550  | 750  | 950  | μA/V |

| Transconductance                          | gm <sub>EA2</sub>         | 0 V < V <sub>FB(ADJ)</sub> < 500 mV                                                                             | _    | 250  | _    | μA/V |

| Source and Sink Current                   | I <sub>EA2</sub>          | V <sub>COMP2</sub> = 1.5 V                                                                                      | -    | ±50  | -    | μA   |

| Maximum Output Voltage                    | V <sub>EA2(out,max)</sub> |                                                                                                                 | 1.00 | 1.25 | 1.50 | V    |

| Minimum Output Voltage                    | V <sub>EA2(out,min)</sub> |                                                                                                                 | _    | _    | 150  | mV   |

| COMP2 Pull-Down Resistance                | R <sub>COMP2</sub>        | HICCUP2 = 1 or FAULT2 = 1 or IC disabled, latched until SS2 resets                                              | -    | 1.5  | -    | kΩ   |

<sup>&</sup>lt;sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>&</sup>lt;sup>2</sup> Ensured by design and characterization, not production tested.

<sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>4</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> > V<sub>VREG(UV,H)</sub> are satisfied before V<sub>VIN</sub> is reduced.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

## ELECTRICAL CHARACTERISTICS – ADJUSTABLE SYNCHRONOUS BUCK REGULATOR<sup>1</sup> (continued): Valid at 3.5 V $^{(4)}$ < $V_{VIN}$ < 36 V, –40°C < $T_A$ = $T_J$ < 150°C, unless otherwise specified

| Characteristic                            | Symbol                 | Test Conditions                                                                                                   | Min. | Тур.                        | Max. | Unit                       |

|-------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------|------|-----------------------------|------|----------------------------|

| SOFT-START                                |                        |                                                                                                                   |      |                             |      |                            |

| V <sub>FB(ADJ)</sub> Soft-Start Ramp Time | t <sub>SS2</sub>       |                                                                                                                   | -    | 2048                        | -    | f <sub>OSC</sub><br>cycles |

|                                           |                        | $V_{FB(ADJ)}$ < 200 m $V_{TYP}$                                                                                   | _    | f <sub>OSC</sub> /4         | -    | _                          |

| SS2 PWM Frequency Foldback                | f <sub>SW2(SS)</sub>   | $200 \text{ mV}_{\text{TYP}} < \text{V}_{\text{FB(ADJ)}} < 500 \text{ mV}_{\text{TYP}}$                           | -    | f <sub>OSC</sub> /2         | -    | _                          |

|                                           |                        | $V_{FB(ADJ)} > 500 \text{ mV}_{TYP}$                                                                              | _    | f <sub>OSC</sub>            | _    | _                          |

| HICCUP MODE                               |                        |                                                                                                                   |      |                             |      |                            |

| Hiccup2 Enable Delay                      | t <sub>HIC2(EN)</sub>  |                                                                                                                   | _    | 512                         | ı    | f <sub>OSC</sub><br>cycles |

| Hiccup2 Recovery Time                     | t <sub>HIC2(REC)</sub> | HICCUP2 = 1                                                                                                       | _    | 2048                        | _    | f <sub>OSC</sub><br>cycles |

| Library a COD Counts                      |                        | $t > t_{HIC2(EN)}, V_{FB(ADJ)} < 200 \text{ mV}_{TYP}$                                                            | _    | 32                          | _    | f <sub>OSC</sub><br>cycles |

| Hiccup2 OCP Counts                        | t <sub>HIC2(OCP)</sub> | t > t <sub>HIC2(EN)</sub> , V <sub>FB(ADJ)</sub> > 200 mV <sub>TYP</sub>                                          | _    | 120                         | -    | f <sub>OSC</sub><br>cycles |

| CURRENT PROTECTIONS                       |                        |                                                                                                                   |      |                             |      |                            |

| Pulse-by-Pulse Current Limit              | I <sub>LIM2(5%)</sub>  | Duty cycle = 5%                                                                                                   | 1.8  | 2.1                         | 2.4  | А                          |

| Pulse-by-Pulse Guiterit Limit             | I <sub>LIM2(90%)</sub> | Duty cycle = 90%                                                                                                  | 1.2  | 1.6                         | 2.0  | Α                          |

| LX2 Short-Circuit Protection              | V <sub>LIM(LX2)</sub>  | V <sub>LX2</sub> stuck low for more than 60 ns,<br>Hiccup mode after 1× detection                                 | _    | V <sub>VREG</sub><br>-1.2 V | -    | V                          |

| V5P LINEAR REGULATORS                     |                        |                                                                                                                   |      |                             |      |                            |

| V5P Accuracy and Load Regulation          | $V_{V5P}$              | 10 mA < I <sub>V5P</sub> < 80 mA, V <sub>VREG</sub> = 5.25 V                                                      | 4.9  | 5.0                         | 5.1  | V                          |

| V5P Output Capacitance <sup>2</sup>       | C <sub>OUT(V5P)</sub>  |                                                                                                                   | 0.7  | 1.0                         | 1.9  | μF                         |

| V5P Minimum Output Voltage <sup>2</sup>   | V <sub>V5P(MIN)</sub>  | $V_{VIN}$ = 4.0 V, $V_{VREG}$ = 5.25 V, $V_{VCP}$ = 7.3 V, $I_{V5P}$ = 75 mA, $I_{3V3}$ = 800 mA (510 mA to VREG) | 4.86 | 4.95                        | -    | V                          |

| V5P OVERCURRENT PROTECTION                |                        |                                                                                                                   |      |                             |      |                            |

| V5P Current Limit <sup>1</sup>            | I <sub>LIM(V5P)</sub>  | V <sub>V5P</sub> = 5 V                                                                                            | -90  | -130                        | _    | mA                         |

| V5P Foldback Current <sup>1</sup>         | I <sub>FBK(V5P)</sub>  | V <sub>V5P</sub> = 0 V                                                                                            | -20  | -45                         | -70  | mA                         |

| V5P STARTUP TIMING                        |                        |                                                                                                                   |      |                             |      |                            |

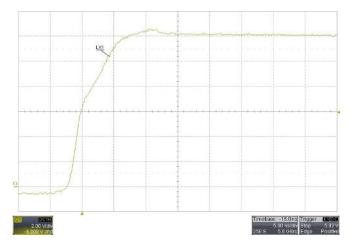

| V5P Startup Time <sup>2</sup>             | t <sub>SS(V5P)</sub>   | $C_{V5P} \le 1.0 \ \mu\text{F}, \text{ Load} = 66 \ \Omega \pm 5\% \ (75 \ \text{mA})$                            | _    | 0.21                        | 1.1  | ms                         |

<sup>&</sup>lt;sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>&</sup>lt;sup>2</sup> Ensured by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>&</sup>lt;sup>4</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> > V<sub>VREG(UV,H)</sub> are satisfied before V<sub>VIN</sub> is reduced.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

#### **ELECTRICAL CHARACTERISTICS – CONTROL INPUTS 1:**

Valid at 3.5 V  $^{(4)}$  < V<sub>VIN</sub> < 36 V, -40°C < T<sub>A</sub> = T<sub>J</sub> < 150°C, unless otherwise specified

| Characteristic                                          | Symbol                     | Test Conditions                                                                                                | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| IGNITION ENABLE (ENBAT) INPU                            | JTS                        |                                                                                                                |      |      |      |      |

| ENDAT Through alide                                     | V <sub>ENBAT(H)</sub>      | V <sub>ENBAT</sub> rising                                                                                      | 2.9  | 3.1  | 3.5  | V    |

| ENBAT Thresholds                                        | V <sub>ENBAT(L)</sub>      | V <sub>ENBAT</sub> falling                                                                                     | 2.2  | 2.6  | 2.9  | V    |

| ENBAT Hysteresis                                        | V <sub>ENBAT(HYS)</sub>    | V <sub>ENBAT(H)</sub> - V <sub>ENBAT(L)</sub>                                                                  | _    | 500  | _    | mV   |

| ENBAT Bias Current <sup>1</sup>                         |                            | T <sub>J</sub> = 25°C <sup>(3)</sup> , V <sub>ENBAT</sub> = 3.51 V                                             | _    | 40   | 65   | μA   |

| ENDAT Blas Current                                      | I <sub>ENBAT(BIAS)</sub>   | T <sub>J</sub> = 150°C, V <sub>ENBAT</sub> = 3.51 V                                                            | _    | 50   | 80   | μA   |

| ENBAT Pull-Down Resistance                              | R <sub>ENBAT</sub>         | V <sub>ENBAT</sub> < 1.2 V                                                                                     | _    | 650  | _    | kΩ   |

| LOGIC ENABLE (ENB) INPUT                                |                            |                                                                                                                |      |      |      |      |

| END Throubolds                                          | V <sub>ENB(H)</sub>        | V <sub>ENB</sub> rising                                                                                        | _    | -    | 2.0  | V    |

| ENB Thresholds                                          | V <sub>ENB(L)</sub>        | V <sub>ENB</sub> falling                                                                                       | 0.8  | _    | _    | V    |

| ENB Bias Current <sup>1</sup>                           | I <sub>ENB(IN)</sub>       | V <sub>ENB</sub> = 3.3 V                                                                                       | _    | _    | 175  | μA   |

| ENB Resistance                                          | R <sub>ENB</sub>           | V <sub>ENB</sub> = 0.8 V                                                                                       | _    | 60   | _    | kΩ   |

| ENB/ENBAT FILTER/DEGLITCH                               |                            |                                                                                                                |      |      |      |      |

| Enable Filter/Deglitch Time                             | t <sub>dFILT</sub>         |                                                                                                                | 10   | 15   | 20   | μs   |

| ENB/ENBAT RESTART DELAY                                 |                            |                                                                                                                | ·    |      | `    |      |

| Enable Restart Delay Time                               | t <sub>dRestart</sub>      | Measured from the time when ENBAT = ENB = 0 and V <sub>VREG</sub> < V <sub>VREG(UV,L)</sub>                    | 460  | 512  | 565  | μs   |

| ENB/ENBAT SHUTDOWN DELAY                                |                            |                                                                                                                |      |      | ,    |      |

| LDO Shutdown Delay                                      | t <sub>dLDO(OFF)</sub>     | Measure t <sub>dLDO(OFF)</sub> from the falling edge of ENB and ENBAT to the time when all LDOs begin to decay | 15   | 50   | 100  | μs   |

| FSET/SYNC INPUTS                                        |                            |                                                                                                                |      |      | `    |      |

| FSET/SYNC Pin Voltage                                   | V <sub>FSET/SYNC</sub>     | No external SYNC signal                                                                                        | _    | 800  | _    | mV   |

| FSET/SYNC Bias Current                                  | I <sub>BIAS(FSET)</sub>    |                                                                                                                | _    | -100 | _    | nA   |

| FSET/SYNC Open-Circuit<br>(Undercurrent) Detection Time | t <sub>FSET/SYNC(UC)</sub> | 1 MHz PWM operation if open                                                                                    | _    | 3    | _    | μs   |

| FSET/SYNC Short-Circuit<br>(Overcurrent) Detection Time | t <sub>FSET/SYNC(OC)</sub> | 1 MHz PWM operation if shorted                                                                                 | _    | 3    | _    | μs   |

| Sync. High Threshold                                    | V <sub>SYNC(HI)</sub>      | V <sub>SYNC</sub> rising                                                                                       | _    | _    | 2.0  | V    |

| Sync. Low Threshold                                     | V <sub>SYNC(LO)</sub>      | V <sub>SYNC</sub> falling                                                                                      | 0.5  | _    | _    | V    |

| Sync. Input Duty Cycle                                  | DC <sub>SYNC</sub>         |                                                                                                                | _    | _    | 80   | %    |

| Sync. Input Pulse Width                                 | t <sub>WSYNC</sub>         |                                                                                                                | 200  | _    | _    | ns   |

| Sync. Input Transition Times <sup>2</sup>               | t <sub>TSYNC</sub>         |                                                                                                                | _    | 10   | 15   | ns   |

| SLEW Inputs                                             |                            |                                                                                                                |      |      |      |      |

| SLEW Pin Operating Voltage                              | V <sub>SLEW</sub>          |                                                                                                                | _    | 800  | _    | mV   |

| SLEW Pin Open-Circuit<br>(Undercurrent) Detection Time  | V <sub>SLEW(UC)</sub>      | LX1 defaults to 1.5 V/ns if fault                                                                              | _    | 3    | -    | μs   |

| SLEW Pin Short-Circuit<br>(Overcurrent) Detection Time  | V <sub>SLEW(OC)</sub>      | LX1 defaults to 1.5 V/ns if fault                                                                              | -    | 3    | _    | μs   |

| SLEW Bias Current <sup>1</sup>                          | i                          |                                                                                                                |      | -100 | T    |      |

<sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

$<sup>^4</sup>$  The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG} > V_{VREG(UV,H)}$  are satisfied before  $V_{VIN}$  is reduced.

<sup>&</sup>lt;sup>2</sup> Ensured by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

# Adjustable Frequency Buck or Buck-Boost Pre-Regulator with Synchronous Buck, 5 V Protected LDO, Pulse-Width Window Watchdog, and NPOR

#### **ELECTRICAL CHARACTERISTICS – DIAGNOSTIC OUTPUTS 1:**

Valid at 3.5 V  $^{(4)}$  < V<sub>VIN</sub> < 36 V, -40°C < T<sub>A</sub> = T<sub>J</sub> < 150°C, unless otherwise specified

| Characteristic                    | Symbol                      | Test Conditions                                                                                    | Min. | Тур. | Max. | Unit |

|-----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------|------|------|------|------|

| NPOR OV/UV PROTECTION TH          | RESHOLDS                    |                                                                                                    |      |      | •    |      |

| FD OV Throubolds                  | V <sub>FB(ADJ,OV,H)</sub>   | V <sub>FB(ADJ)</sub> rising                                                                        | 835  | 855  | 875  | mV   |

| FB <sub>ADJ</sub> OV Thresholds   | $V_{FB(ADJ,OV,L)}$          | V <sub>FB(ADJ)</sub> falling                                                                       | _    | 848  | _    | mV   |

| FB <sub>ADJ</sub> OV Hysteresis   | V <sub>FB(ADJ,OV,HYS)</sub> | $V_{FB(ADJ,OV,H)} - V_{FB(ADJ,OV,L)}$                                                              | 3    | 7    | 14   | mV   |

| FB <sub>AD,J</sub> UV Thresholds  | $V_{FB(ADJ,UV,H)}$          | V <sub>FB(ADJ)</sub> rising, triggers turn on of LDOs                                              | _    | 752  | _    | mV   |

| T D <sub>ADJ</sub> OV Tillesholds | $V_{FB(ADJ,UV,L)}$          | V <sub>FB(ADJ)</sub> falling                                                                       | 725  | 745  | 765  | mV   |

| FB <sub>ADJ</sub> UV Hysteresis   | $V_{FB(ADJ,UV,HYS)}$        | $V_{FB(ADJ,UV,H)} - V_{FB(ADJ,UV,L)}$                                                              | 3    | 7    | 14   | mV   |

| NPOR TURN-ON AND TURN-OF          | F DELAYS                    |                                                                                                    |      |      |      |      |

| NPOR Turn-On Delay                | t <sub>dNPOR(ON)</sub>      | $V_{FB(ADJ)} > V_{FB(ADJ,UV,H)}$ , see Figure 12 for timing details                                | 1.6  | 2    | 2.4  | ms   |

| NPOR Turn-Off Delay               | t <sub>dNPOR(OFF)</sub>     | ENB and ENBAT low for t > t <sub>dFILT</sub> , see Figure 12 for timing details                    | _    | _    | 3    | μs   |

| NPOR OUTPUT VOLTAGES              |                             |                                                                                                    |      |      |      |      |

| NIDOD Outsut Law Valtage          |                             | ENB or ENBAT high, $V_{VIN} \ge 2.5 \text{ V}$ , $I_{NPOR} = 4 \text{ mA}$                         | _    | 150  | 400  | mV   |

| NPOR Output Low Voltage           | $V_{NPOR(L)}$               | ENB or ENBAT high, V <sub>VIN</sub> = 1.5 V,<br>I <sub>NPOR</sub> = 2 mA                           | -    | _    | 800  | mV   |

| NPOR Leakage Current <sup>1</sup> | I <sub>NPOR(LKG)</sub>      | V <sub>NPOR</sub> = 3.3 V                                                                          | _    | _    | 2    | μA   |

| NPOR AND POK5V OV DELAY 1         | IME                         |                                                                                                    |      |      |      |      |

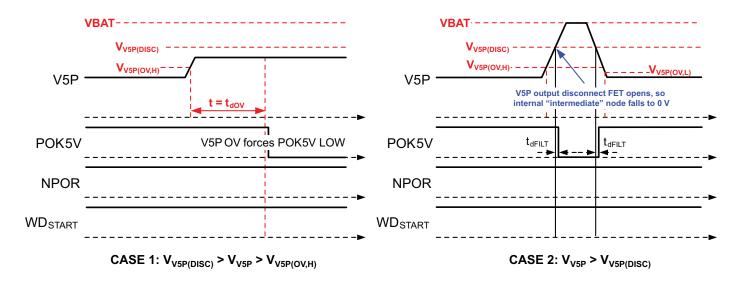

| Overvoltage Detection Delay       | t <sub>dOV</sub>            | V5P or FB <sub>ADJ</sub> overvoltage detection delay time (two independent timers, NPOR and POK5V) | 3.2  | 4.0  | 4.8  | ms   |

| NPOR AND POK5V UV FILTERII        | NG/DEGLITCH                 |                                                                                                    |      |      |      |      |

| UV Filter/Deglitch Times          | t <sub>dFILT</sub>          | Applies to undervoltage of the FB <sub>ADJ</sub> and V5P voltages                                  | 10   | 15   | 20   | μs   |

| POK5V OV/UV PROTECTION TH         | RESHOLDS                    |                                                                                                    |      |      |      |      |

| V5P OV Thresholds                 | V <sub>V5P(OV,H)</sub>      | V <sub>V5P</sub> rising                                                                            | 5.15 | 5.33 | 5.50 | V    |

| VOI OV IIIIESIIUIUS               | V <sub>V5P(OV,L)</sub>      | V <sub>V5P</sub> falling                                                                           | _    | 5.30 | _    | V    |

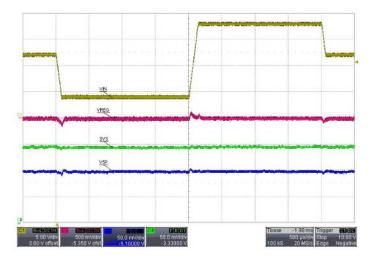

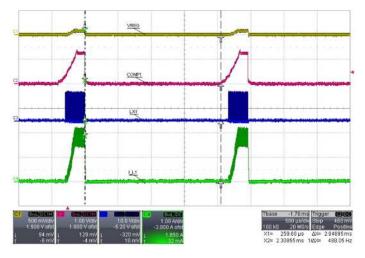

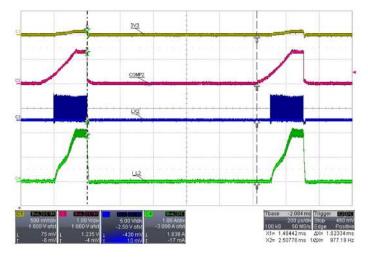

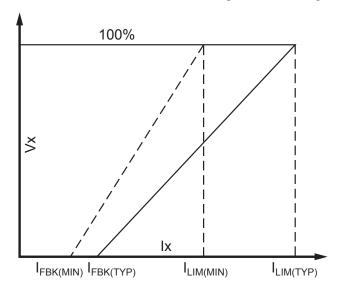

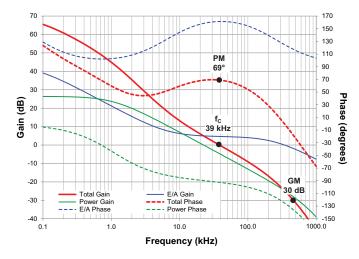

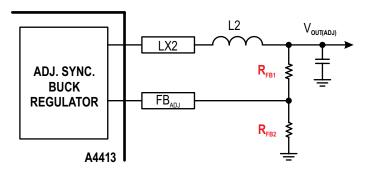

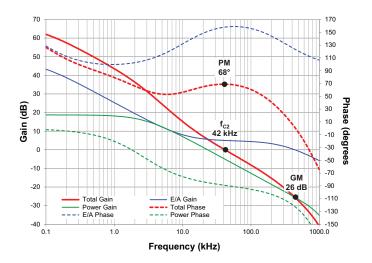

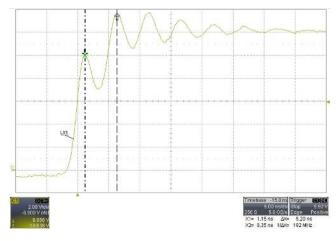

| V5P OV Hysteresis                 | V <sub>V5P(OV,HYS)</sub>    | $V_{V5P(OV,H)} - V_{V5P(OV,L)}$                                                                    | 15   | 30   | 50   | mV   |