# Digital Discovery: Portable USB Logic Analyzer and Digital Pattern Generator

SKU:240-127

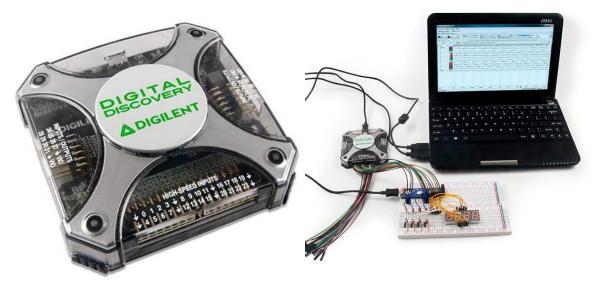

The Digilent Digital Discovery™ is a combined logic analyzer and pattern generator instrument that was created to be the ultimate embedded development companion. Digital Discovery was designed to optimize channels, speed, and portability. A small form factor facilitates easy storage and provides a whole suite of advanced features to allow you to debug, visualize, and simulate digital signals for most embedded projects. Digital inputs and outputs can be connected to a circuit using simple wire probes or breadboard wires; alternatively, the Digital Discovery High Speed Adapter and impedance-matched probes can be used to connect and utilize the inputs and outputs for more advanced projects. The Digital Discovery is driven by the free WaveForms software and can be configured to be any of the below instruments:

- 32-channel digital logic analyzer (1.2...3.3V CMOS, 8 channels at 800MS/s\*, 16 channels at 400MS/s\*, and 32 channels at 200MS/s)

- Digital Bus Analyzers (SPI, I<sup>2</sup>C, UART, CAN, Parallel)

- 16-channel pattern generator (1.2...3.3V CMOS, 100MS/s)

- 16-channel virtual digital I/O including buttons, switches, and LEDs perfect for logic training applications

- A programmable power supply of 1.2...3.3V/100mA. The same voltage supplies the Logic Analyzer input buffers and the Pattern Generator input/output buffers, for keeping the logic level compatibility with the circuit under test.

\*Note: to obtain speeds of 200MS/s and higher, the High Speed Adapter must be used.

The Digital Discovery is designed for anyone embarking on embedded development; with features and specifications deliberately chosen to maintain a small and portable form factor, withstand use in a variety of environments, and keep costs down while balancing the requirements of operating on USB Power.

Digital Discovery packaged in a regular-sized project box

## What's

#### Included:

- 2x6 flywire assembly

- 2x16 flywire assembly

- USB A to Micro-B cable

# Digital Discovery

800 MS/s Logic Analyzer and Protocol Analyzer

Software

WaveForms Resource

Center

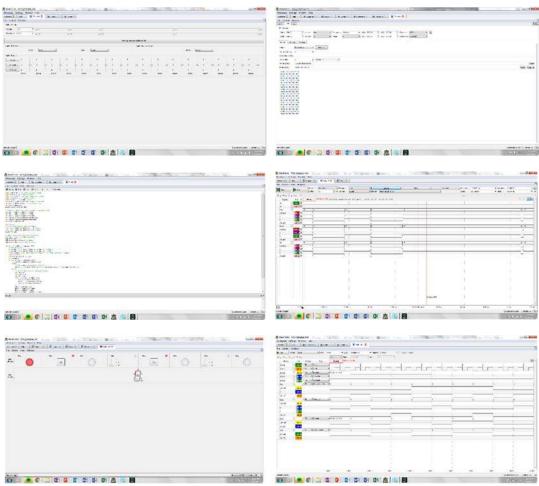

**Digital Logic Analyzer**

Channels 24

Sample Rate 800 MS/s

(with the High Speed

Adapter)

Bandwidth 100 MHz+

**Voltage Range** 1.2V to 3.3V (5V compatible

when used as inputs)

Buffer 2Gbit DDR3 acquisition

Bus Analyzers SPI, I<sup>2</sup>C, UART, CAN, I2S,

Parallel and Custom

**Digital Pattern Generator**

Channels 16

Sample Rate 100 MS/s

Bandwidth 50MHz

Voltage Range 1.2V to 3.3V

**Bus Output** Counters and Custom

# Multi-purpose Digital I/O

Channels 16

Sample Rate 100 MS/s

(50 MHz max output

frequency)

**Voltage Range** 1.2V to 3.3V (5V compatible

when used as inputs)

**Buffer** Algorithmic pattern

generator (no buffers used)

# **Protocol Analyzer**

Channels 16-32

Voltage Range 1.2V to 3.3V (inputs 5V

compatible)

**Bus Analyzers** UART: send and receive

SPI: read and write

12C: read and write

CAN: rx and tx

# **Programmable Power Supplies**

Voltage Range 1.2V to 3.3V

Current Limit 100 mA max available in

each of the two 2×6 MTE

connectors

|    | rin |      | . A 1 | tor |

|----|-----|------|-------|-----|

| 20 |     | ,, , | .uı   | tor |

|    |     |      |       |     |

Supported All

Instruments

**Language** Javascript

# **Cross Triggering**

**Supported** Logic Analyzer, Pattern

**Instruments** Generator

#### **Provided Hardware**

- USB A to Micro B Cable

- 2×6 MTE Cable

- 2×16 MTE cable

- High-speed Adapter (Optional)

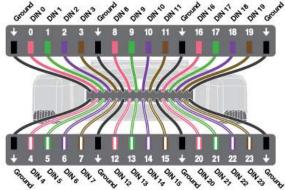

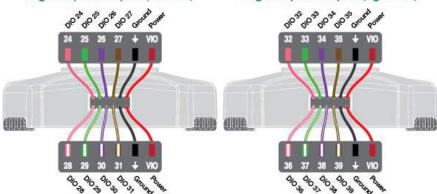

#### **Pinout**

High-Speed Digital Inputs

Digital Inputs/Outputs (left side)

Digital Inputs/Outputs (right side)

The Digital Discovery™ is a combined logic analyzer and pattern generator instrument that was created to be the ultimate embedded development companion. The Digital Discovery was designed to optimize channels, speed, and portability. The small form factor facilitates easy storage and provides a whole suite of advanced features to allow you to debug, visualize, and simulate digital signals for most embedded projects. The digital inputs and outputs can be connected to a circuit using simple wire probes or breadboard wires; alternatively, the Digital Discovery High Speed Adapter and impedance-matched probes can be used to connect and utilize the inputs and outputs for more advanced projects. The Digital Discovery is driven by the free <a href="WaveForms">WaveForms</a> (3.5.4 or later) software and can be configured to be any of the instruments below:

- 24-channel digital logic analyzer (1.2...3.3V CMOS, up to 800MS/s(with the High Speed Adapter))

- 16-channel pattern generator (1.2...3.3V CMOS, 100MS/s)

- 16-channel virtual digital I/O including buttons, switches, and LEDs perfect for logic training applications

- A programmable power supply of 1.2...3.3V/100mA. The same voltage supplies the Logic Analyzer input buffers and the Pattern Generator input/output buffers, for keeping the logic level compatibility with the circuit under test.

- Digital Bus Analyzers (SPI, I<sup>2</sup>C, UART, I2S, CAN, Parallel)

The Digital Discovery was designed for anyone embarking on embedded development. Its features and specifications were deliberately chosen to maintain a small and portable form factor, withstand use in a variety of environments, and keep costs down, while balancing the requirements of operating on USB Power.

### **Digital Discovery Reference Manual**

The Digital Discovery™ is a combined logic analyzer and pattern generator instrument that was created to be the ultimate embedded development companion. The Digital Discovery was designed to optimize channels, speed, and portability. The small form factor facilitates easy storage and provides a whole suite of advanced features to allow you to debug, visualize, and simulate digital signals for most embedded projects. The digital inputs and outputs can be connected to a circuit using simple wire probes or breadboard wires; alternatively, the Digital Discovery High Speed Adapter and impedance-matched probes can be used to connect and utilize the inputs and outputs for more advanced projects. The Digital Discovery is driven by the free <a href="WaveForms">WaveForms</a> (3.5.4 or later) software and can be configured to be any of the instruments below:

- 24-channel digital logic analyzer (1.2...3.3V CMOS, up to 800MS/s(with the High Speed Adapter))

- 16-channel pattern generator (1.2...3.3V CMOS, 100MS/s)

- 16-channel virtual digital I/O including buttons, switches, and LEDs perfect for logic training applications

- A programmable power supply of 1.2...3.3V/100mA. The same voltage supplies the Logic Analyzer input buffers and the Pattern Generator input/output buffers, for keeping the logic level compatibility with the circuit under test.

- Digital Bus Analyzers (SPI, I<sup>2</sup>C, UART, I2S, CAN, Parallel)

The Digital Discovery was designed for anyone embarking on embedded development. Its features and specifications were deliberately chosen to maintain a small and portable form factor, withstand use in a variety of environments, and keep costs down, while balancing the requirements of operating on USB Power.

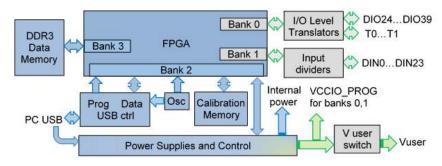

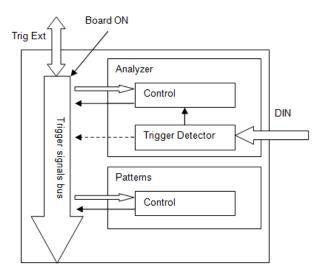

# 1.1 Architectural Overview and Block Diagram

Digital Discovery's high-level block diagram is presented in Figure 2, below. The core of the Digital Discovery 2 is the Xilinx® Spartan®-6 FPGA (specifically, the XC6SLX25-2 device). The WaveForms application automatically programs the Discovery's FPGA at start-up with a configuration file designed to implement a multi-function test and measurement instrument. Once programmed, the FPGA inside the Discovery communicates with the PC-based WaveForms application via a USB 2.0 connection. The WaveForms software works with the FPGA to control all the functional blocks of the Digital Discovery, including setting parameters, acquiring data, and transferring and storing data into the DDR3 memory. Signals and equations also use certain naming conventions. Signals in the Input block use "DIN" prefix to indicate these are inputs only. Signals in the Input/Output block use "DIO" prefix. Signals at the user connectors include "USR" in their names, while signals at the FPGA pins include "FPGA". Signals at the FPGA pins driving the pull resistors for DIO signals, include "PULL" in their names. DIN inputs are indexed 0 to 23, DIO input/outputs are indexed 24 to 39. Memory signals have the "DDR" prefix. Supply rails show the voltage with the VCC prefix. Referring to the block diagram in Figure 2 below:

- The I/O Level Translators build the bidirectional interface for input/output pins (used in the Pattern Generator, Static IO, and Logic Analyzer)

- The Input Dividers are the conditioning circuits for the input pins (used in the Logic Analyzer)

- The FPGA banks are supplied at different voltages:

- Bank 0, Bank1: VCCIO\_PROG, a variable voltage, settable in the range 1.2V...3.3V. The logic standard is set to: LVCMOS18\_JEDEC. The threshold voltage is about 0.45\*VCCIO\_PROG.

- Bank 2: VCC3V3, a fixed voltage of 3.3V.

- Bank 3: VCC1V5, a fixed voltage of 1.5V.

- A replica of VCCIO\_PROG is also available to the user, as VCCIO\_USR, under the V user switch control.

- The DDR3 Data Memory block stores the Logic analyzer acquired data.

- The Power Supplies and Control block generates all internal supply voltages as well as user supply programmable voltage. The control block also monitors the device power consumption for USB compliance.

- The USB Controller interfaces with the PC for programming the volatile FPGA memory after power on or when a new configuration is requested. After that, it performs the data transfer between the PC and FPGA.

The Calibration Memory stores all calibration parameters. The Digital Discovery includes

no analog calibration circuitry. Instead, a calibration operation is performed at

manufacturing (or by the user), and parameters are stored in memory. The WaveForms

software uses these parameters to adjust the acquired data and the generated signals.

In the sections that follow, schematics are not shown separately for identical blocks. For example, the Input Divider is only shown for DIN0 since the schematic for all other DIN1...DIN23 is identical.

Figure 2. Digital Discovery Hardware block diagram.

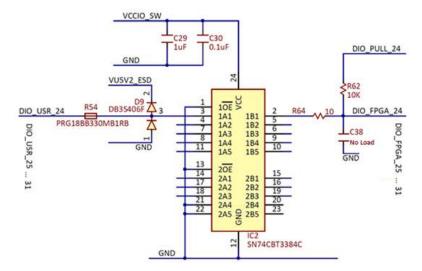

#### 2. I/O Level Translators

Figure 3 shows the DIO user connectors and Figure 4 shows the I/O level translator for DIO24. DIO25 to DIO31 use similar discrete components, connected to pins 1A2...2A3, respectively 1B2...2B3 of IC2.

The I/O Level Translators block includes: - Input protection: series PTC ( $33\Omega$ , positive thermal coefficient thermistor) and parallel ESD/overvoltage diodes to 5.2V and GND. - Voltage level translators, SN74CBT3384C. When DIO\_USR signals are driven by the DUT, the voltage at the FPGA pins is limited at VCCIO\_SW-1V = 3.3V. When the FPGA drives DIO\_USR signals, they pass unlimited trough the low impedance SN74CBT3384C buffer. - Pull resistors: 10k, individually settable as Pull-Up, Pull-Down or High-Z. This is done with a second FPGA pin associated to each DIO, which can be driven High, Low or HiZ. The Pull-Up voltage is VCCIO\_PROG. - DIO\_FPGA pin: the bank supply voltage is VCCIO\_PROG> The WaveForms software can set VCCIO\_PROG from 1.2 to 3.3V. The FPGA input threshold level is about 45% of VCCIO\_PROG. The output strength can be set from 2mA to 16mA. The output slew rate can be set as: Quiet, Slow or Fast.

| DIO_USR_24 | Pmod 2x6         | DIO_USR_28 | DIO_USR_32 | Pmod 2x6 | DIO_USR_36 |

|------------|------------------|------------|------------|----------|------------|

| DIO_USR_25 | 7 15 15 15 15 15 | DIO_USR_29 | DIO_USR_33 | 0 1 7 0  | DIO_USR_37 |

| DIO_USR_26 | 0 2 8 0          | DIO_USR_30 | DIO_USR_34 | 0 2 8 9  | DIO_USR_38 |

| DIO_USR_27 | 0 410 0          | DIO_USR_31 | DIO_USR_35 | 9 410 9  | DIO_USR_39 |

| GND        | 9 511 0          | GND        | GND        | 9 511 9  | GND        |

| VCCIO_USR  | 0 612 0          | VCCIO_USR  | VCCIO_USR  | 0 612 0  | VCCIO_USR  |

|            | 12               |            |            | 13       |            |

Figure 3. DIO user connectors.

Figure 4. I/O level translator.

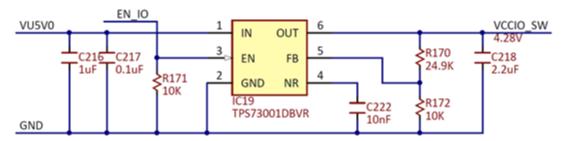

The LDO in Figure 5 generates the 4.3V to supply the level translator in Figure 4.

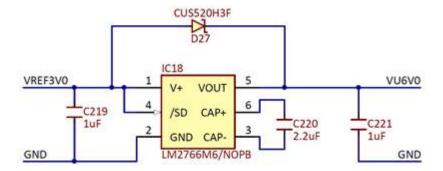

The charge-pump in Figure 6 provides the the 6V reference for the clipper in Figure 7.

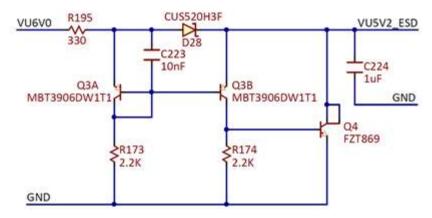

When all ESD diodes protecting DIO\_USR in Figure 3 are OFF, Q3B is OFF, and also Q4. If overvoltage is applied on some DIO\_USR pins, rising VU5V2\_ESD in Figure 7 above 5.2V, Q3B and Q4 turn ON, clipping VU5V2\_ESD at approximately 5V.

Figure 5. VCCIO SW supply.

Figure 6. VU6V0 supply.

Figure Figure 7. Backpowering voltage clipper.

#### 3. Input Dividers

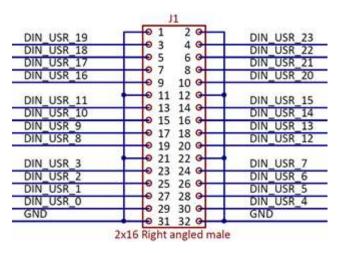

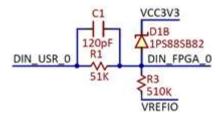

Figure 8 shows the DIN user connector and Figure 9 shows the Input Divider for DIN0. DIN1 to DIN23 use similar input circuitry.

The Input Dividers block includes:

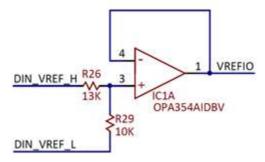

Frequency compensated voltage dividers: 10/11 resistive dividers with compensation for FPGA input capacitance. All the dividers together have the settable reference voltage VREFIO. Setting VREFIO close to the logical threshold voltage provides the highest sensitivity, while setting VREFIO at GND or logical supply voltage increase the noise immunity. The voltage at the FPGA pin:

VDIN\_FPGA=1011·VDIN\_USR+111·VREFIO(1)(1)VDIN\_FPGA=1011·VDIN\_USR+111·VREFIO

- The reference voltage VREFIO is generated as in Figure 10. DIN\_VREF\_H and DIN\_VREF\_L are connected to FPGA pins in bank 1. Bank1 is supplied at VCCIO. VREFIO can be set at:

- o 0V, when DIN VREF H = DIN VREF L = low

- o 0.43\*VCCIO PROG, when DIN VREF H = high, DIN VREF L = low

- VCCIO PROG, when DIN VREF H = DIN VREF L = high.

- ESD/Overvoltage protection: Shottky diodes to VCC3V3.

- DIN\_FPGA pin: the bank supply voltage is VCCIO\_PROG. The WaveForms software can set VCCIO\_PROG from 1.2 to 3.3V. The FPGA input threshold level is about 45% of VCCIO\_PROG.

Figure 8. DIN user connector.

Figure 9. Input Divider.

Figure 10 VREFIO reference.

## 4. Power supplies and control

# 4.1 Internal power supplies

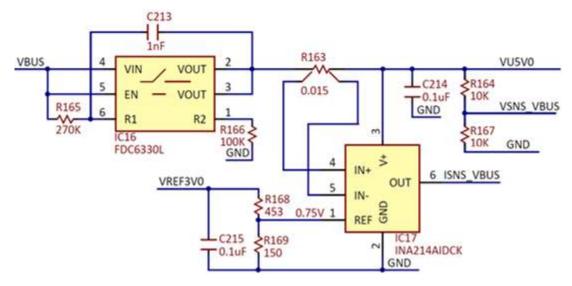

In Figure 11, IC16 limits the in-rush current when the device is connected to the USB port. INA214 is a current shunt amplifier, with a gain of 100. With Vref = 0.75V and R163 =  $15m\Omega$ , the output voltage is:

$V_{ISNS\_VBUS}=100 \cdot (V_{IN+}-V_{IN-})+0.75V=1.5 \cdot I_{VU5V0}+0.75V(2)(2)VISNS\_VBUS=100 \cdot (VIN+-VIN-)+0.75V=1.5 \cdot I_{VU5V0}+0.75V$

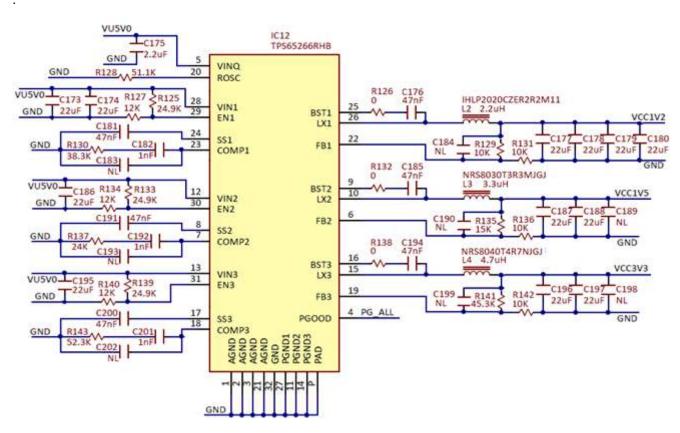

The VBUS voltage is halved to VSNS\_VBUS, for being also monitored. IC12 in Figure 11 is a triple power supply, generating the rails of 1.2V for the FPGA core, 1.5V for Bank 3 and DDR3 memory and 3.3V, for various circuits.

Figure 11 VBUS monitoring.

Figure 12. Internal voltage supplies.

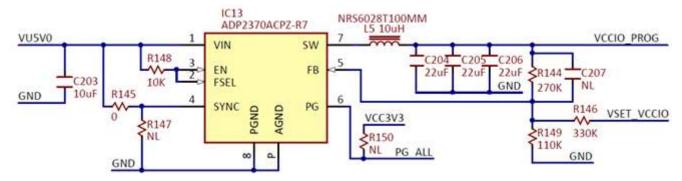

# 4.2 Programmable power supply

IC13 in Figure 13 generates the VCCIO\_PROG, the variable voltage to supply the input and IO banks of the

FPGA:Vvccio\_prog=VfB·(1+R144R146+R144R149)-Vvset\_vccio·R144R146=3.42V-Vvset\_vccio·0.82(3)(3)VVCCIO\_PROG=VFB·(1+R144R149)-Vvset\_vccio·R144R149)-VVSET\_VCCIO·R144R146=3.42V-VVSET\_VCCIO·R144R146=3.42V-VVSET\_VCCIO·0.82

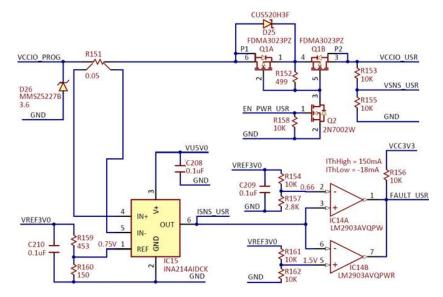

With VVSET\_VCCIO  $\epsilon$  (0...3V), VCCIO\_PROG could be theoretically set in the range: VCCIO\_PROG  $\epsilon$  (1.02V...3.42V). IC15 is a current shunt amplifier, with a gain of 100. With Vref = 0.75V and R115 = 50m $\Omega$ , the output voltage

is: $V_{ISNS\_USR}=100\cdot(V_{IN+}-V_{IN-})+0.75V=5\cdot I_{VCCIO\_USR}+0.75V(4)(4)VISNS\_USR=100\cdot(VIN+-VIN-)+0.75V=5\cdot I_{VCCIO\_USR}+0.75V$

IC14 is a window comparator: FAULT\_USR is logical LOW, when VISNS\_USR is either more than 1.5V (IVCCIO\_USR>150mA) or less than 0.66V (IVCCIO\_USR←18mA). If this happens, the FPGA turns EN\_PWR\_USR to LOW, which turns both Q1A and Q1B OFF, to protect VCCIO\_USR against overcurrent and reverse current respectively. VCCIO\_USR is halved to VSNS\_USR, for being monitored.

Figure 13. VCCIO PROG supply.

Figure 14. VCCIO\_USR protection and switch.

## 4.3. Monitoring the power supplies

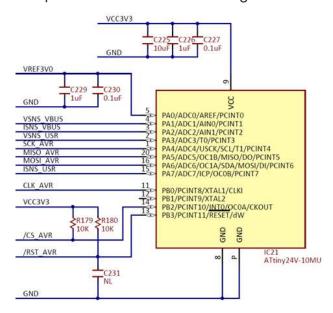

The microcontroller in Figure 15 has two roles:

- A/D Conversion of VVSNS\_VBUS, VISNS\_VBUS, VVSNS\_USR, VISNS\_USR, representing the voltages and currents consumed from VBUS and VCCIO\_USR respectively. The digital results are passed to the FPGA via an SPI interface.

- 2. Storing the calibration parameters computed as a part of the manufacturing test. During regular behavior, the WaveForms Software reads the parameters and corrects both generated and acquired signals.

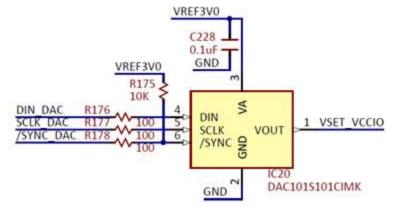

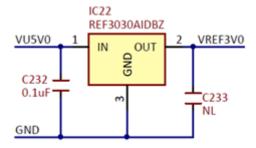

The DAC in Figure 16 generates the setting voltage for programming the value of VCCIO. IC22 in Figure 17 provides 3V reference voltage for both ADC and DAC above.

Figure 15. ATtiny microcontroller.

Figure 16. VSET\_VCCIO setting DAC.

Figure 17. VREF3V0.

## 5. LEDs and DDR3 Memory

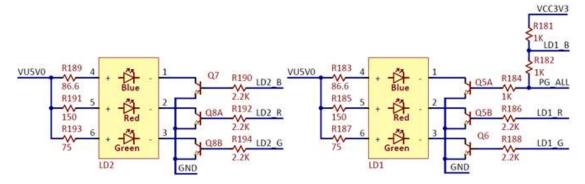

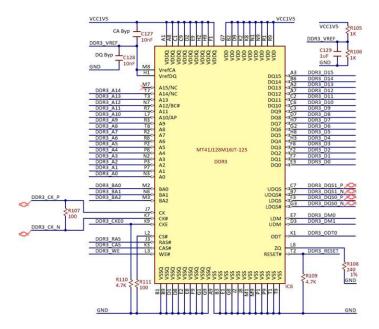

Figure 18 shows the two tricolor LEDs used to symbolize the Digital discovery status. Figure 19 shows the DDR3 memory for the Logic Analyzer buffer.

Figure 18. LEDs.

Figure 19. DDR3 memory.

#### 6. USB Controller

The USB interface performs two tasks:

- **Programming the FPGA:** There is no non-volatile FPGA configuration memory on the Digital Discovery. The WaveForms software identifies the connected device and downloads an appropriate .bit file at power-up, via a Digilent USB-JTAG interface. Adept run-time is used for low level protocols.

- Data exchange: All instrument configuration data, acquired data and status information is handled via a Digilent synchronous parallel bus and USB interface. Speed up to 20MB/sec. is reached, depending on USB port type and load as well as PC performance.

#### 7. FPGA

The core of the Digital Discovery is the Xilinx Spartan6 FPGA circuit XC6SLX25. The configured logic performs:

- Clock management (12MHz and 60 MHz for USB communication, 100MHz and 800MHz for data sampling)

- Acquisition control and Data Storage (Logic Analyzer)

- Digital signal synthesis (for pattern generator and bus protocol controllers)

- Trigger system (trigger detection and distribution for all instruments)

- Power supplies control and instruments enabling

- Power and temperature monitoring

- Calibration memory control

- Communication with the PC (settings, status data)

Block RAM of the FPGA is used for signal synthesis. External DDR3 memory is used for data acquisition.

Detail of the trigger system is shown in Figure 20. Each instrument generates a trigger signal when a trigger condition is met. Each trigger signal (including external triggers) can trigger any instrument and drive the external trigger outputs. This way, all the instruments can synchronize to each other.

Figure 20. FPGA configuration trigger block diagram.

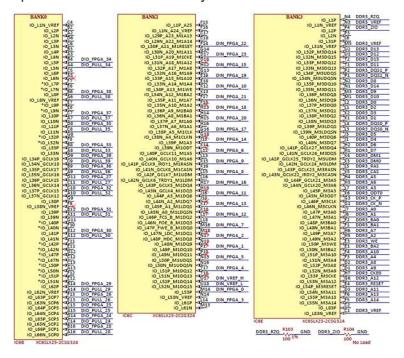

Figure 21 shows the connections to the FPGA banks 0, 1 and 3.

Bank 0 is used for IOs. DIO\_FPGA pins are the actual input/output pins to be used with the Pattern Generator, Static IO and Logic Analyzer. A DIO\_PULL pin can add Pull-Up or Pull-Down resistors to the associated DIO\_FPGA pin (see Figure 4).

Bank 1 is used for high speed Logic Analyzer inputs. DIN\_FPGA are the actual input pins, while DIN\_VREF\_H and DIN\_VREF\_L set the reference voltage for the input dividers (see Figure 9).

Bank 3 is used as port for the DDR3 memory.

Figure 21. FPGA banks 0, 1 and 3.

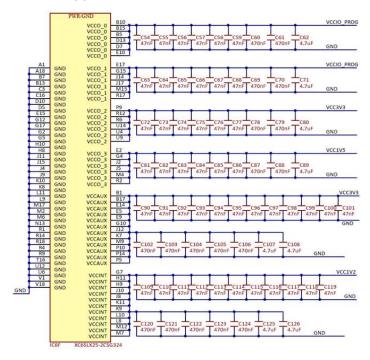

Figure 22 shows the voltage rails and decoupling for the FPGA.

The internal core of the FPGA is supplied 1.2V.

Banks 0 and 1 are supplied with the programmable VCCIO\_PROG. By setting this from 1.2V to 3.3V, both inputs and IOs are set to be compatible with the I/O standard LVCMOS of the respective voltage. Notice that a protected version of VCCIO\_PROG is also available to the user, as VCCIO\_USR. This can be used to supply the Device/Circuit Under Test.

Bank 3 is supplied 1.5V, for compatibility with the DDR3 IC.

Bank 2 and VCCAUX are supplied 3.3V.

Figure 22. FPGA powering and decoupling.

#### 8. Accessories

The Digital Discovery package includes;

- One 2×16 fly-wire assembly (<u>datasheet</u>), for the DIN\_USR connector. 24DIN signals (various colors), 8 GND wires (black). The connector is keyed so that the correct pins are connected to the correct color wires.

- One 2×6 fly-wire assembly (<u>datasheet</u>), for the DIO connectors. Each one includes two VCCIO\_USR (red) wires, two GND (black) wires and 8 (colored) signal wires. It has a 2×6 female connector for the Digital Discovery DIN connector, and 1 pin female connectors for the device under test.

Additional Accessories that can be added at checkout;

• One High Speed Adapter, for the DIN\_USR connector. The High Speed Adapter is an alternative to the 2×16 fly-wire assembly. It provides access for 24 twisted cables. The adapter is not keyed, and both orientations can be used as the twisted wires are not color coded. However, if the adapter is plugged in with the ground arrows pointing down, the pins will be located as shown below:

High Speed Logic Probes (<u>datasheet</u>). Each twisted cable has a GND (black) wire twisted to a DIN\_USR (colored) wire. The wire connects to the High Speed Adapter via a 2 pin female header, and two 1 pin female connectors to the device under test. A 100Ω resistor is embedded in the signal wire, on the end closest to the device under test. All GND wires should be connected to Ground of the device under test.

#### 9. Features and Performances

This chapter shows the features and performances as described in the Digital Discovery Datasheet. Footnotes add detailed information and annotate the HW description in this Manual.

# 9.1. Logic Analyzer

- 24 high-speed input channels (DIN0...23), accessible through one 2×16 connector, used with the Logic Analyzer in WaveForms (560kΩ||10pF)

- 16 digital I/Os (DIO24...39) arranged in two Pmod-style (2×6) connectors, used with the Logic Analyzer in WaveForms 1

- 800MSps input sample rate when using maximum 8 inputs (and the High Speed Adapter), 400 MSps with maximum 16 inputs (with the High Speed Adapter), 200MSps and lower with maximum 32 inputs 21

- User programmable input and output LVCMOS voltage levels from 1.2V to 3.3V <sup>31</sup> (5V compatible <sup>41</sup>)

- 100MHz signal input bandwidth

- 2Gbit DDR3 acquisition buffer for Logic Analyzer

- Multiple trigger options including pin change, bus pattern, etc 51

- Digital Bus Analyzers (SPI, I<sup>2</sup>C, UART, Parallel)

# 9.2. Multi-purpose Digital I/O

- 16 digital I/Os arranged in two Pmod-style (2×6) connectors.

- Each of the 16 pins can be configured for input (Logic analyzer) or set as output <u>a</u>.

- Algorithmic pattern generator (no buffers used) <sup>1</sup>

- Custom pattern buffer/ch.: 32Ksamples

- ROM Logic for implementing user defined Boolean functions and State Machines

- Bus Protocol Controllers (SPI, UART, I<sup>2</sup>C)

- 100MSps max. output sample rate (50MHz maximum output frequency).

- Automatic or manual strength and slew settings for outputs. 81

- User programmable logic I/O levels from 1.2V to 3.3V (5V compatible) 9,10.

#### 9.3. Other features

- USB bus powered

- User power supplies, 1.2V to 3.3V, available in the two Pmod-style connectors (100mA max)

- Twisted wire high-speed cable option for input channels to insure signal integrity

- Free WaveForms software runs on Windows, MacOS, and Linux

- Cross-triggering between Logic Analyzer, Pattern Generator or external trigger

- Data file import/export using standard formats

- 80X80X25mm, 80g (without accessories)

- includes: USB cable, fly-wire accessory

#### Written by Mircea Dabacan, PhD, Technical University of Cluj-Napoca Romania

- <sup>11</sup> The 16 DIO lines are primarily intended for the Pattern Generator, protocol controllers and Static IO instruments. For user convenience, some or all of them can be used by the Logic Analyzer also (see footnote 2). However, DIO input circuitry is different compared to DIN. Even more, when driving a DIO pin with the Pattern Generator and reading it back with the Logic Analyzer, the signal is read at the FPGA pin and does not propagate trough the external DIO circuitry. Consequently, when combining DIN and DIO pins in the Logic Analyzer, misalignments can be observed, at high acquisition rate.

- <sup>2</sup> Available combinations in WaveForms: 200MHz, DIN0...23, DIO24...31 200MHz, DIO24...39, DIN0...15 400MHz, DIN0...15 400MHz, DIO24...39 800MHz, DIO24...31

- <sup>a</sup> The FPGA DIN and DIO pins are set to LVCMOS18\_JEDEC IOSTANDARD. The supply voltage of the associated FPGA banks is set (by user) to any value from 1.2V to 3.3V. The threshold level (at the FPGA pins) is about 45% of the bank supply voltage. For standard voltages of: 1.2V, 1.5V,

- 1.8V, 2.5V, 3.3V, the threshold levels (at the FPGA pins) are: 0.58V, 0.7V, 0.82V, 1.1V and 1.42V respectively.

- <sup>4</sup> Setting the voltage to 3.3V, 5V logic inputs are tolerated but the input threshold is 1.42V. LVCMOS 3.3V output signals are compatible to most external logical circuits supplied with 5V.

- <sup>9</sup> Trigger Detectors and Trigger Distribution Networks are implemented in the FPGA. This allows real time triggering and cross-triggering of different instruments within the Digital Discovery device. Using external Trigger inputs/outputs, cross-triggering between multiple Digital Discovery devices is possible.

- In the 16 DIO lines are primarily intended for the Pattern Generator, protocol controllers and Static IO instruments. For user convenience, some or all of them can be used by the Logic Analyzer also (see footnote 2). However, DIO input circuitry is different compared to DIN. Even more, when driving a DIO pin with the Pattern Generator and reading it back with the Logic Analyzer, the signal is read at the FPGA pin and does not propagate trough the external DIO circuitry. Consequently, when combining DIN and DIO pins in the Logic Analyzer, misalignments can be observed, at high acquisition rate.

- <sup>12</sup> Real time implemented in the FPGA configuration.

- The FPGA DIN and DIO pins are set to LVCMOS18\_JEDEC IOSTANDARD. The supply voltage of the associated FPGA banks is set (by user) to any value from 1.2V to 3.3V. The threshold level (at the FPGA pins) is about 45% of the bank supply voltage. For standard voltages of: 1.2V, 1.5V, 1.8V, 2.5V, 3.3V, the threshold levels (at the FPGA pins) are: 0.58V, 0.7V, 0.82V, 1.1V and 1.42V respectively.

- The FPGA DIN and DIO pins are set to LVCMOS18\_JEDEC IOSTANDARD. The supply voltage of the associated FPGA banks is set (by user) to any value from 1.2V to 3.3V. The threshold level (at the FPGA pins) is about 45% of the bank supply voltage. For standard voltages of: 1.2V, 1.5V, 1.8V, 2.5V, 3.3V, the threshold levels (at the FPGA pins) are: 0.58V, 0.7V, 0.82V, 1.1V and 1.42V respectively.

- <sup>™</sup> Setting the voltage to 3.3V, 5V logic inputs are tolerated but the input threshold is 1.42V. LVCMOS 3.3V output signals are compatible to most external logical circuits supplied with 5V.