# ISO70xx Low-Power Digital Isolator Evaluation Module

This user's guide describes the ISO7041 Low-Power Isolator Digital Isolator Evaluation Module (EVM). This EVM allows designers to evaluate device performance for fast development and analysis of isolated systems. The EVM supports evaluation of any of the quad-channel Low-Power digital isolators in a 16-pin SSOP (DBQ) package.

#### CAUTION

This evaluation module is made available for isolator parameter performance evaluation only and is not intended for isolation voltage testing. To prevent damage to the EVM, any voltage applied as a supply or digital input/output must be maintained within the 0 V to 3.63 V recommended operating range.

#### Contents

| Introduction                                                | 2                                                                                                                                                                       |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview                                                    | 2                                                                                                                                                                       |

| Pin Configuration of the ISO7041 Low-Power Digital Isolator | 2                                                                                                                                                                       |

| ISO7041DBQ EVM Board Block Diagram and Image                |                                                                                                                                                                         |

| EVM Setup and Operation                                     | 4                                                                                                                                                                       |

| Bill of Materials                                           |                                                                                                                                                                         |

| EVM Schematics and Layout                                   | 6                                                                                                                                                                       |

|                                                             | Overview<br>Pin Configuration of the ISO7041 Low-Power Digital Isolator<br>ISO7041DBQ EVM Board Block Diagram and Image<br>EVM Setup and Operation<br>Bill of Materials |

#### List of Figures

| 1 | ISO7041 Low-Power Digital Isolator Pin Configurations | 2 |

|---|-------------------------------------------------------|---|

| 2 | ISO7041DBQ EVM Configuration                          | 3 |

| 3 | ISO7041DBQ EVM Photograph                             | 3 |

| 4 | Basic EVM Operation                                   | 4 |

| 5 | Typical Input and Output Waveforms                    |   |

| 6 | ISO7041DBQ EVM Schematic                              |   |

| 7 | ISO7041DBQ PCB Layout                                 | 7 |

|   |                                                       |   |

|   |                                                       |   |

## List of Tables

| 1 | Bill of Materials | <br>5 |

|---|-------------------|-------|

|   |                   |       |

# Trademarks

All trademarks are the property of their respective owners.

#### 1 Introduction

This user's guide describes EVM operation with respect to the ISO7041 Low-Power digital isolator. However, the EVM may be reconfigured for evaluation of any of TI's quad-channel digital isolators in a 16pin SSOP (DBQ) package. This guide also describes the EVM schematic, and typical laboratory setup. A typical input and output waveform is also presented.

## 2 Overview

The ISO7041 is TI's new low-power digital isolator device capable of a galvanic isolation rating of up to 4000  $V_{PK}$ . This device is certified to meet reinforced isolation requirements by VDE and CSA. This isolator provides high electromagnetic immunity and low emissions at low power consumption, while isolating CMOS or LVCMOS digital I/Os. The ISO7041 digital isolator has logic input and output buffers separated by a silicon oxide (SiO2) insulation barrier. Used with isolated power supplies, this device blocks high voltages, isolates grounds, and prevents noise currents on a data bus or other circuits from entering the local ground and interfering with, or damaging sensitive circuitry. Additionally, the ISO7041 operates on very low power. ISO7041DBQEVM is designed to allow users to evaluate the ISO7041. The 2-channel ISO7021 performance can also be evaluated using the ISO7041 installed on the ISO7041DBQEVM. The ISO7721DEVM can be used to install the ISO7021 for further 2-channel evaluation.

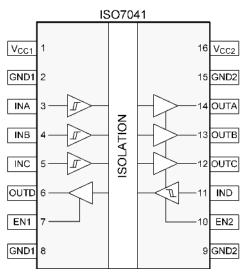

# 3 Pin Configuration of the ISO7041 Low-Power Digital Isolator

Figure 1 shows the ISO7041 low-power quad-channel digital isolator pin configuration.

Figure 1. ISO7041 Low-Power Digital Isolator Pin Configurations

www.ti.com

#### ISO7041DBQ EVM Board Block Diagram and Image

# 4 ISO7041DBQ EVM Board Block Diagram and Image

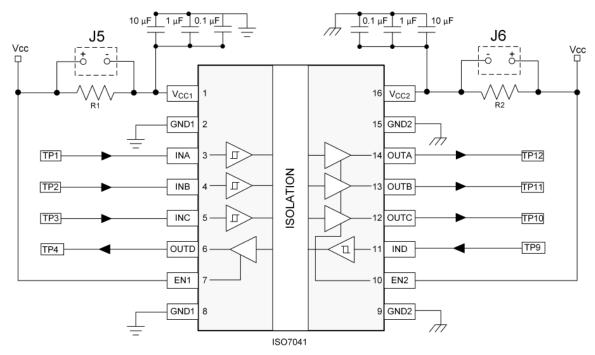

Figure 2 shows the board configuration for evaluation of the ISO7041 quad-channel digital isolator.

Figure 2. ISO7041DBQ EVM Configuration

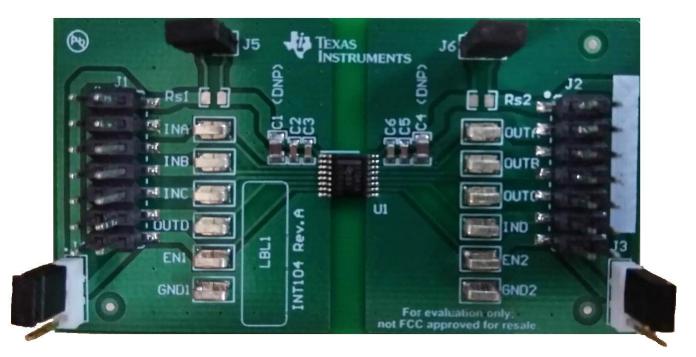

Figure 3 shows the photograph of the EVM.

## 5 EVM Setup and Operation

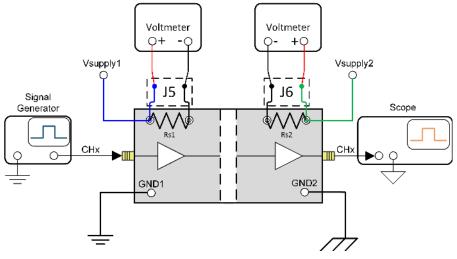

This section describes the setup and operation of the EVM for parameter performance evaluation. Figure 4 shows the configuration for operating the ISO70xx triple and quad digital isolator EVM using two power supplies and two voltmeter. Rs1 and Rs2 allow the user to easily measure the low current consumed by the ISO7041 without the need for specialized equipment. Current consumed by a particular side of the ISO7041 can simply be calculated by measuring the voltage drop across the respective Rs resistor and dividing that value by it's resistance. Rs1 and Rs2 will need to be populated with a resistance that allows the user to accurately measure the voltage across them. This value will typically range between 400 and 600 ohms. Higher resistances can be used but Vsupply will have to be increased in order to compensate for the increased voltage drop over Rs1 and Rs2. Please be sure to use high accuracy resistors of 0.1% tolerance or better for the most accurate measurements and calculations.

Figure 4. Basic EVM Operation

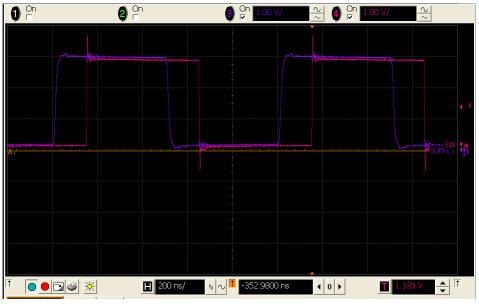

Figure 5 shows typical input and output waveforms of the EVM for a 1-MHz clock. The input is shown as channel 3, and the output is shown as channel 4.

Figure 5. Typical Input and Output Waveforms

www.ti.com

# 6 Bill of Materials

Table 1 shows the bill of materials (BOM) for this EVM.

| Item | Designator                                                                    | Description                                      | Manufacturer      | PartNumber              | Quantity |

|------|-------------------------------------------------------------------------------|--------------------------------------------------|-------------------|-------------------------|----------|

| 1    | J1, J2                                                                        | Header, 2.54 mm, 7 x 2, Gold, SMT                | Wurth             | 61001421121             | 2        |

| 2    | C1, C4                                                                        | CAP, CERM, 10 uF, 35 V, +/- 10%, X5R, 0805       | MuRata            | GRM21BR6YA106KE<br>43L  | 2        |

| 2    | C2, C5                                                                        | CAP, CERM, 1 μF, 50 V, ±10%,<br>X5R, 0603        | ТDК               | C1608X5R1E105K08<br>0AC | 2        |

| 3    | C3, C6                                                                        | CAP, CERM, 0.1 μF, 25 V, ±5%,<br>X7R, 0603       | AVX               | 06033C104JAT2A          | 2        |

| 4    | H1, H2, H3, H4                                                                | Bumpon, Hemisphere, $0.44 \times 0.20$ , Clear   | ЗМ                | SJ-5303 (CLEAR)         | 4        |

| 5    | J5, J6                                                                        | Header, 2.54 mm, 2 x 1, Gold, TH                 | Wurth Elektronik  | 61300211121             | 2        |

| 6    | J3, J4                                                                        | Header, 100 mil, 3 × 1, Gold, TH                 | Samtec            | HTSW-103-07-G-S         | 2        |

| 7    | TP1, TP2, TP3,<br>TP4, TP5, TP6,<br>TP7, TP8, TP9,<br>TP10, TP11, and<br>TP12 | Test Point, Miniature, SMT                       | Keystone          | 5019                    | 12       |

| 8    | U1                                                                            | Ultra-Low Power Four-Channel<br>Digital Isolator | Texas Instruments | ISO7041DBQ              | 1        |

## Table 1. Bill of Materials

## 7 EVM Schematics and Layout

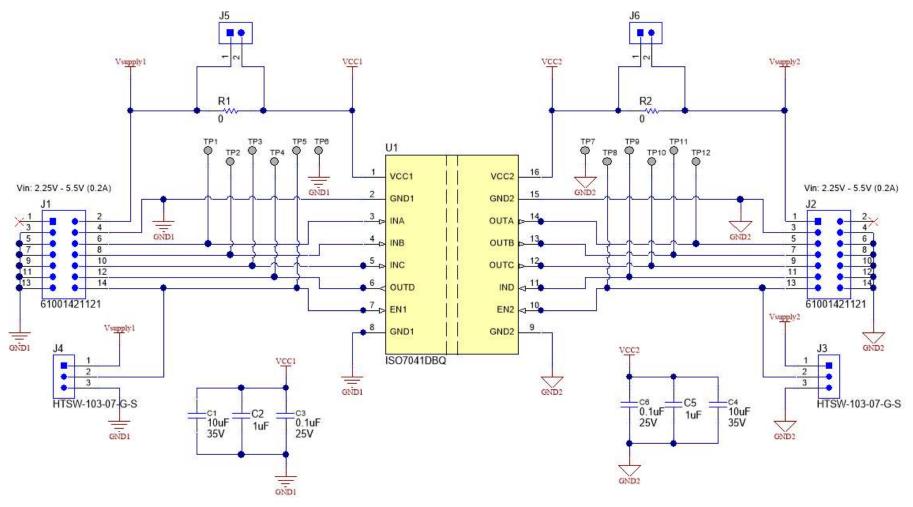

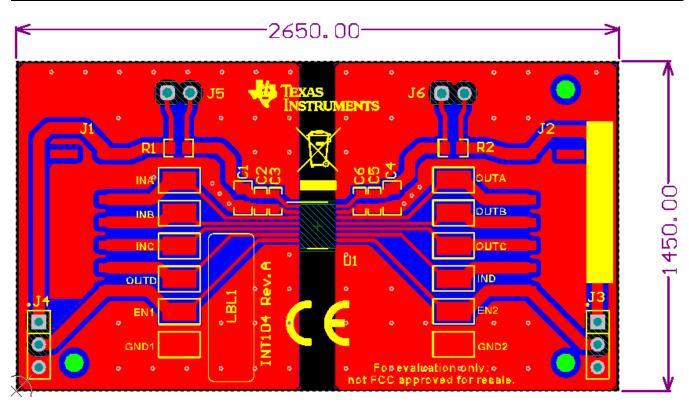

The ISO7041DBQ EVM is designed to accommodate any of the ISO70xx Low-Power devices in a 16-pin SSOP. To evaluate any of the ISO70xx Low-Power devices in a 16-pin SSOP package, replace ISO7741DBQ with the device of interest on the ISO7041DBQ EVM PCB. No other component requires any modification. Figure 6 shows the ISO7041DBQEVM schematic and Figure 7 shows the printed-circuit board (PCB) layout.

Figure 6. ISO7041DBQ EVM Schematic

www.ti.com

Figure 7. ISO7041DBQ PCB Layout

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated