## 9319 • 9320

## DECADE SEQUENCERS

**DESCRIPTION** — The '19 and '20 are high speed counters with ten decoded active LOW outputs. The '19 has standard TTL totem pole outputs, and the '20 has resistor pull-up outputs for wired-AND applications. The devices provide a 1-of-10 sequential output pattern by the application of ten pulses to the Clock input. Shorter sequences can be obtained by using external feedback, either hard-wired or programmable via multiplexing.

- COMBINATION DECADE COUNTER AND 1-OF-10 DECODER

- GLITCHLESS, SEQUENTIAL 1-OF-10 OUTPUT PATTERN

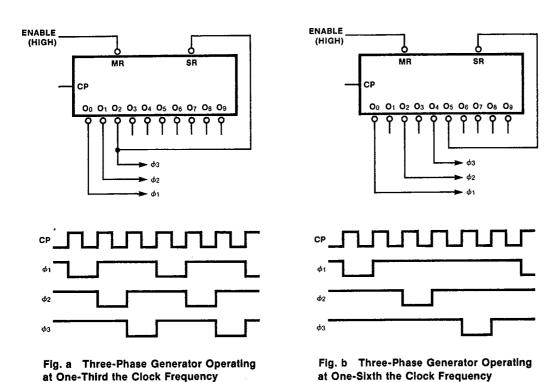

- IDEAL FOR MULTIPHASE CLOCK GENERATION

- ANY SEQUENCE BETWEEN TWO AND TEN OBTAINABLE

- HIGH SPEED CLOCK INPUTS TYPICALLY 50 MHz

- WIRED-AND CAPABILITY (9320 ONLY)

**ORDERING CODE:** See Section 9

| CP 1         |   | 16] 400       |

|--------------|---|---------------|

| CE 2         |   | 15 Ō₀         |

| SR 3         |   | 14 Ō1         |

| MR 4         |   | 13 <b>O</b> 2 |

| <b>ō</b> ₃ 5 |   | 12 <b>O</b> 3 |

| ნ₃ 6         |   | 11 0₄         |

| ō, 7         |   | 10 <b>O</b> ₅ |

| GND 8        |   | 9 0₀          |

| _            | L | 1             |

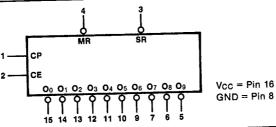

CONNECTION DIAGRAM PINOUT A

|                    |            |                                                                                          |                                                                                                 | 1    |

|--------------------|------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|

|                    | BIN        | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                  | PKG  |

| PKGS               | PIN<br>OUT | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to } +125^{\circ} \text{ C}$ | TYPE |

| Plastic<br>DIP (P) | Α          | 9319PC, 9320PC                                                                           |                                                                                                 | 9В   |

| Ceramic<br>DIP (D) | Α          | 9319DC, 9320DC                                                                           | 9319DM, 9320DM                                                                                  | 6B   |

| Flatpak<br>(F)     | А          | 9319FC, 9320FC                                                                           | 9319FM, 9320FM                                                                                  | 4L   |

INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES            | DESCRIPTION                                                                                                                                                              | 9319 (U.L.)<br>HIGH/LOW                           | <b>9320 (U.L.)</b><br>HIGH/LOW                     |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

| CP<br>CE<br>SR<br>MR | Clock Pulse Input (Active Rising Edge) Clock Enable Input Synchronous Reset Input (Active LOW) Asynchronous Master Reset Input (Active LOW) Decoded Outputs (Active LOW) | 1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>20/10 | 1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>3.0/10 |

LOGIC SYMBOL

F-06 1551

093/9-1X 6-59

TRUTH TABLE

|                                   |                       |        |           | INUIN            |             |                         |             | _  |      |      |    |               |                |                       |

|-----------------------------------|-----------------------|--------|-----------|------------------|-------------|-------------------------|-------------|----|------|------|----|---------------|----------------|-----------------------|

| OPERATING                         |                       | IN     | PUTS      | 3                |             |                         |             |    | UTP  | UTS  |    |               |                |                       |

| MODE                              | MR                    | SR     | CE        | CP               | Ō           | Ō <sub>1</sub>          | Ō₂          | •  | •    | •    | •  | Ō7            | Ō <sub>8</sub> | <u>О</u> 9            |

| Initialize,<br>Asynchronous Reset | L<br>L <del>→</del> H | X<br>X | X<br>(qui | X<br>iescent)    | H           | H                       | H           |    |      |      |    | H             | H<br>H         | H                     |

| Synchronous Reset                 | Н                     | L      | Н         | 7                | L           | Н                       | Н           |    |      |      |    | Н             | Н              | Н                     |

| Hold                              | Н                     | Х      | L         | Х                |             |                         |             | (N | o Ch | ange | 9) |               |                |                       |

| Sequence/Count                    | 111                   |        | 111       | \\\ · · · · \\\\ | L H H H H L | H L H · · · · · H H H H | H H L H H H | •  | •    | •    | •  | H H H L H H H | H H H H L H H  | H H H · · · · H H L H |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

states  $\overline{O}_0 - \overline{O}_9$ , successively.

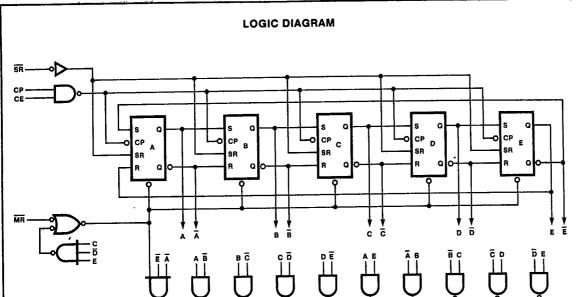

FUNCTIONAL DESCRIPTION — The '19 and '20 are decade shift counters with active LOW 1-of-10 decoded outputs. The decoded shift counter technique provides ten mutually exclusive, glitchless outputs. The edgetriggered counter is advanced on each LOW-to-HIGH transition of the Clock input (CP). When the Clock Enable (CE), Synchronous Reset (SR), Master Reset (MR) are HIGH, the device is sequenced via the Clock thru output

The active HIGH Count Enable (CE) input is gated with the Clock and can be interchanged with Clock for layout convenience. A LOW on the CE input inhibits the Clock and stops the counter. By returning one of the outputs to the CE input, the device will sequence up to that output state and stop until reset with the Master Reset. Because the CE input is gated with the CP input, it cannot be changed from LOW to HIGH while the CP is HIGH.

The active LOW Synchronous Reset (SR) is used to reset the counter to zero (returning the output to the Oo state) in response to the LOW-to-HIGH transition of the Clock. Any sequence between "two" and "ten" can be obtained by connecting the last desired output to the SR input. This method of truncating the sequence produces a series of pulses of equal duration as long as the clock frequency remains constant.

A LOW on the Master Reset (MR) overrides all other input conditions and resets the counter to zero. As long as the MR is LOW, all of the outputs are HIGH. When the MR goes from LOW to HIGH, the zero output 100 goes LOW. This MR gating with the 00 output insures complete system resetting or initialization before the first output in the sequencer is activated. For low frequency applications (below 1.0 MHz) the MR can be used in lieu of the  $\overline{SR}$  for truncating the count sequence. If the input CP rise time is very slow (over 100 ns), the  $\overline{MR}$  input should be used to reset the counter to avoid mis-triggering. This is accomplished by returning the next higher output to the MR pin. After the desired sequence is completed, the next clock pulse will reset the counter and enable the first output within 50 ns.

The outputs of the '19 are standard TTL totem pole type which can drive up to ten standard TTL unit loads. The outputs of the '20 are DTL resistor pull-up type for applications requiring wired-AND connections. The on-chip pull-up resistors, (about 3 k $\Omega$ ) of the '20 eliminate the need for external resistors normally required by opencollector outputs. Up to eight '20 outputs can be tied together with enough sink current capability left to drive one standard TTL input or five 93L or 54LS/74LS inputs.

The '19 and '20 will normally require initialization after power is first applied. A LOW pulse on the Master Reset (or a LOW on the Synchronous Reset in conjunction with a clock pulse) will reset the 5-bit register and activate output  $\overline{O}_0$ . If initialization is not possible or not required, an error correction circuit is provided to detect some of the 22 unused states and return the counter to the proper sequence within ten clock cycles.

at One-Third the Clock Frequency

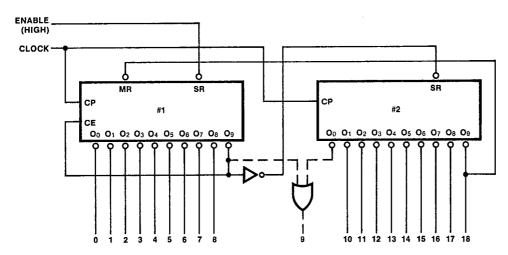

Fig. c Expansion for longer sequences. The first sequencer locks up after  $\overline{O}_9$  goes LOW because of the feedback to CE. Simultaneously, SR of the second sequencer is released and it starts counting on the next clock. When  $\overline{O}_9$  of the second sequencer goes LOW, the feedback to  $\overline{MR}$  causes  $\overline{O}_9$  of the first sequencer to go HIGH, which then makes \$\overline{SR}\$ of the second sequencer go HIGH. On the next clock the second sequencer goes to the  $\overline{O}_0$  state, releasing  $\overline{MR}$  of the first sequencer, making its  $\overline{O}_0$  go LOW. On the next clock the first sequencer starts its counting sequence again.

|        | PARAMETER                    | 9:  | 319 | 9:   | 320  | UNITS | CONDITIONS                                    |

|--------|------------------------------|-----|-----|------|------|-------|-----------------------------------------------|

| SYMBOL | PANAMEIEN                    | Min | Max | Min  | Max  |       |                                               |

| Voн    | Output HIGH Voltage          |     |     | 2.4  |      | V     | ioH = -120 μA                                 |

| los    | Output Short Circuit Current |     |     | -1.3 | -3.7 | mA    | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 0 \ |

| loc    | Power Supply Current         | 1   | 60  |      | 60   | mA    | V <sub>CC</sub> = Max                         |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C (See Section 3 for waveforms and load configurations)

|                  | CTERISTICS. VOC. 1919 1, IX | 9;                     | 319      | 9320                                |          |       |                 |  |

|------------------|-----------------------------|------------------------|----------|-------------------------------------|----------|-------|-----------------|--|

| SYMBOL           | PARAMETER                   | C <sub>L</sub> = 15 pF |          | $C_L = 15 pF$<br>$R_L = 400 \Omega$ |          | UNITS | CONDITIONS      |  |

|                  |                             | Min                    | Max      | Min                                 | Max      |       |                 |  |

| f <sub>max</sub> | Maximum Count Frequency     | 35                     |          | 35                                  |          | MHz   | Figs. 3-1, 3-8  |  |

| tPLH<br>tPHL     | Propagation Delay           |                        | 40<br>30 |                                     | 40<br>30 | ns    | Figs. 3-1, 3-8  |  |

| tPLH<br>tPHL     | Propagation Delay           |                        | 50<br>33 |                                     | 50<br>33 | ns    | Figs. 3-1, 3-16 |  |

AC OPERATING REQUIREMENTS:  $V_{CC} = +5.0 \text{ V}$ ,  $T_A = +25^{\circ} \text{ C}$

|                                          | DADAMETED                          | 9319       | •   _    | 93 | 20  | UNITS | CONDITIONS |

|------------------------------------------|------------------------------------|------------|----------|----|-----|-------|------------|

| SYMBOL                                   | PARAMETER                          | Min M      | /lax Mi  | n  | Max |       |            |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>SR to CP | 10<br>10   | 1:       |    |     | ns    | Fig. 3-6   |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW              | 5.0<br>5.0 | 5.<br>5. |    |     | ns    |            |

| tw                                       | CP Pulse Width                     | 15         | 1        | 5  |     | ns    | Fig. 3-16  |

| tw (L)                                   | MR or SR Pulse Width LOW           | 9.0        | 9.       | 0  |     | ns    | Fig. 3-16  |

| trec                                     | Recovery Time MR to CP             | 35         | 3        | 5  |     | ns    | Fig. 3-16  |