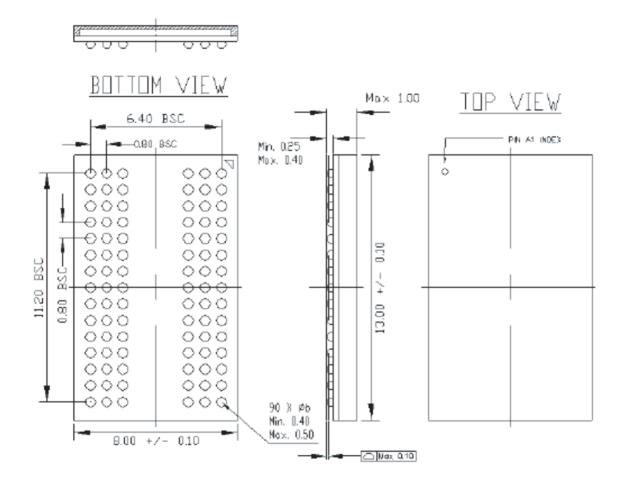

## Revision History AS4C32M32MD1 - 90-ball FBGA PACKAGE

| Revision | Details               | Date           |

|----------|-----------------------|----------------|

| Rev 1.0  | Preliminary datasheet | September 2014 |

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 610-6800 FAX: (650) 620-9211 Alliance Memory Inc. reserves the right to change products or specification without notice

# AS4C32M32MD1

# 32M x 32 bit MOBILE DDR Synchronous DRAM (SDRAM)

## Confidential

Advanced (Rev. 1.0, Sep. /2014)

## Feature

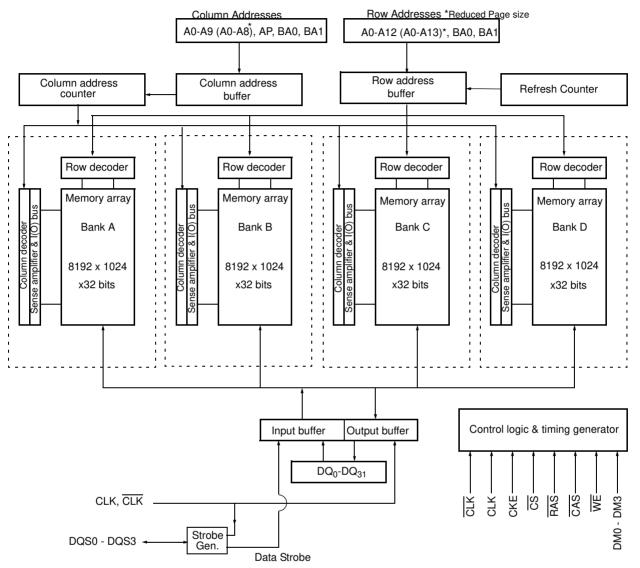

- 4 banks x 8M x 32 organization

- Data Mask for Write Control (DM)

- Four Banks controlled by BA0 & BA1

- Programmable CAS Latency: 2, 3

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length: 2, 4, 8, 16 for Sequential Type 2, 4, 8, 16 for Interleave Type

- Automatic and Controlled Precharge Command

- Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 8192 cycles/64ms

- Available in 90-ball BGA

- Double Data Rate (DDR)

- Bidirectional Data Strobe (DQS) for input and output data, active on both edges

- Differential clock inputs CLK and /CLK

- Power Supply 1.7V 1.95V

- Drive Strength (DS) Option:Full, 1/2, 1/4, 3/4

- Auto Temperature-Compensated Self Refresh (Auto TCSR)

- Partial-Array Self Refresh (PASR) Option: Full, 1/2, 1/4, 1/8, 1/16

- Deep Power Down (DPD) mode

- Operating Temperature Range

- Commercial -25°C to 85°C (Extended)

- Industrial -40°C to 85°C

## Description

The AS4C32M32MD1 is a four bank mobile DDR DRAM organized as 4 banks x 8M x 32. It achieves high speed data transfer rates by employing a chip architecture that pre-fetches multiple bits and then synchronizes the output data to a system clock.

All of the controls, address, circuits are synchronized with the positive edge of an externally sup-plied clock. I/O transactions are possible on both edges of DQS.

Operating the four memory banks in an interleaved fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate is possible depending on burst length, CAS latency and speed grade of the device.

Additionally, the device supports low power saving features like PASR, Auto-TCSR, DPD as well as options for different drive strength. It's ideally suit-able for mobile application.

## Table 1. Speed Grade Information

| Speed Grade – Data rate | <b>Clock Frequency</b> | CAS Latency | t <sub>RCD</sub> (ns) | t <sub>RP</sub> (ns) |

|-------------------------|------------------------|-------------|-----------------------|----------------------|

| 400Mbps (max)           | 200 MHz (max)          | 3           | 15                    | 15                   |

## Table 2 – Ordering Information for ROHS Compliant Products

| Product part No   | Org      | Temperature                                 | Package     |

|-------------------|----------|---------------------------------------------|-------------|

| AS4C32M32MD1-5BCN | 32M x 32 | <b>Commercial - 25°C to 85°C</b> (Extended) | 90-ball BGA |

| AS4C32M32MD1-5BIN | 32M x 32 | Industrial -40°C to 85°C                    | 90-ball BGA |

## Block Diagram (32M x 32)

## 32MX32 90 BALL BGA CONFIGURATION

| A                                       |

|-----------------------------------------|

| C C C C C C C C C C C C C C C C C C C   |

| C                                       |

| E                                       |

| F • • • • • • • • • • • • • • • • • • • |

| G                                       |

| G                                       |

| J                                       |

|                                         |

|                                         |

| +                                       |

|                                         |

|                                         |

|                                         |

| P 🌒 🌑 🌑 👘 🌑                             |

| R 🔂 - 🔂 - 🔂 🔂 - 🔂 -                     |

## Top View

|   | 90Ball (6X15) CSP |        |        |                    |        |         |  |  |  |

|---|-------------------|--------|--------|--------------------|--------|---------|--|--|--|

|   | 1                 | 2      | 3      | 7                  | 8      | 9       |  |  |  |

| A | VSS               | DQ 31  | VSSQ   | V D D Q            | DQ16   | V D D   |  |  |  |

| В | V D D Q           | D Q 29 | D Q 30 | DQ 17              | DQ18   | VSSQ    |  |  |  |

| С | VSSQ              | DQ 27  | D Q 28 | DQ 19              | D Q 20 | V D D Q |  |  |  |

| D | V D D Q           | DQ 25  | DQ 26  | DQ 21              | DQ 22  | Tesť    |  |  |  |

| E | VSSQ              | DQS3   | DQ24   | DQ 23              | DQS2   | V D D Q |  |  |  |

| F | V D D             | D M 3  | N C    | A 1 3 <sup>1</sup> | DM 2   | VSS     |  |  |  |

| G | C K E             | C K    | CK     | WE                 | CAS    | RAS     |  |  |  |

| H | A 9               | A 1 1  | A 1 2  | CS                 | B A O  | BA1     |  |  |  |

| J | A 6               | A 7    | A 8    | A 1 0 /A P         | A 0    | A 1     |  |  |  |

| K | A 4               | DM 1   | A 5    | A 2                | DM O   | A 3     |  |  |  |

| L | VSSQ              | DQS1   | DQ8    | DQ7                | DQSO   | V D D Q |  |  |  |

| M | V D D Q           | DQ9    | DQ10   | DQ5                | DQ6    | VSSQ    |  |  |  |

| N | VSSQ              | DQ11   | DQ12   | DQ3                | DQ4    | V D D Q |  |  |  |

| Р | V D D Q           | DQ13   | DQ14   | DQ1                | D Q 2  | VSSQ    |  |  |  |

| R | VSS               | DQ15   | VSSQ   | VDDQ               | DQO    | V D D   |  |  |  |

Note 1:A13 is only available for reduced page-size configuration. Note 2:Test must be tied to VSS or VSSQ in norm al operations.

## Pin Names

| CLK, CLK                        | Differential Clock Input    |

|---------------------------------|-----------------------------|

| CKE                             | Clock Enable                |

| CS                              | Chip Select                 |

| RAS                             | Row Address Strobe          |

| CAS                             | Column Address Strobe       |

| WE                              | Write Enable                |

| DQS0, DQS1,<br>DQS2, DQS3       | Data Strobe (Bidirectional) |

| A <sub>0</sub> -A <sub>13</sub> | Address Inputs              |

| BA0, BA1                          | Bank Select                    |

|-----------------------------------|--------------------------------|

| DQ <sub>0</sub> -DQ <sub>31</sub> | Data Input/Output              |

| DM0, DM1, DM3,<br>DM3             | Data Mask                      |

| V <sub>DD</sub>                   | Power (1.7V - 1.95V)           |

| V <sub>SS</sub>                   | Ground                         |

| V <sub>DDQ</sub>                  | Power for I/O's (1.7V - 1.95V) |

| V <sub>SSQ</sub>                  | Ground for I/O's               |

| NC                                | No Connect                     |

F

IANCE M O R Y

| Pin                       | Туре             | Signal | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------|------------------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK<br>CLK                | Input            | Pulse  | Positive<br>Edge | The system clock input. All inputs except DQs and DMs are sampled on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                     |

| CKE                       | Input            | Level  | Active High      | Activates the CLK signal when high and deactivates the CLK signal when low, thereby initiates either the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                |

| CS                        | Input            | Pulse  | Active Low       | $\overline{\text{CS}}$ enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                         |

| RAS, CAS<br>WE            | Input            | Pulse  | Active Low       | When sampled at the positive rising edge of the clock, $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ define the command to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                 |

| A0 - A13                  | Input            | Level  | _                | During a Bank Activate command cycle, A0-A12 defines the row address (RA0-RA12) and A0-A13 defines the row address (RA0-RA13) for 32Mx32 reduced page size when sampled at the rising clock edge.<br>During a Read or Write command cycle, A0-A9 defines the column address (CA0-CA9) and A0-A8 defines the column address (CA0-CA8) for 32Mx32 reduced page size when sampled at the rising clock edge.                                                                                         |

|                           |                  |        |                  | In addition to the column address, A10 is used to invoke autoprecharge operation at the end of the burst read or write cycle. If A10 is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is disabled. During a Precharge command cycle, A10(=AP) is used in conjunction with BA0 and BA1 to control which bank(s) to precharge. If A10 is high, all four banks will be precharged simultaneously regardless of state of BA0 and BA1. |

| DQx                       | Input/<br>Output | Level  |                  | Data Input/Output pins operate in the same manner as conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BA0,<br>BA1               | Input            | Level  | —                | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LDQS,<br>UDQS<br>(DQS0~3) | Input/<br>Output | Level  | _                | Data Input/Output are synchronous edges of the DQS. LDQS for DQ0-DQ7, UDQS for DQ8-DQ15 in 32Mx16. DQS0 for DQ0-DQ7, DQS1 for DQ8-DQ15, and DQS2 for DQ16-DQ23, DQS3 for DQ24-DQ31 in 16Mx32. Active on both edges for data input/output. Center aligned to input data and edge aligned to output data.                                                                                                                                                                                          |

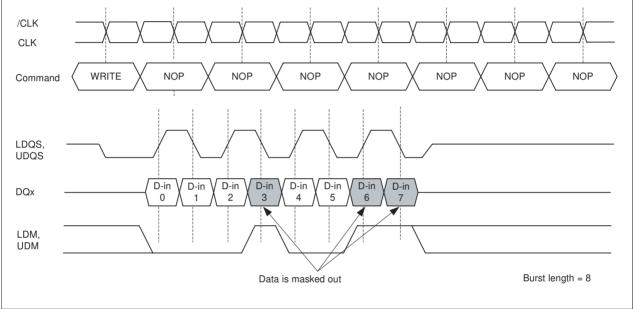

| UDM,<br>LDM<br>(DM0~3)    | Input            | Pulse  | Active High      | In Write mode, DQM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if is high. If it's high, LDM corresponds to DQ0-DQ7, and UDM corresponds to data on DQ8-DQ15 in 32Mx16. DM0 corresponds to DQ0-DQ7, DM1 corresponds to data on DQ8-DQ15, DM2 corresponds to DQ16-DQ23, and DM3 corresponds to data on DQ24-DQ31 in 16Mx32.                                                                                |

| VDD, VSS                  | Supply           |        |                  | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDDQ<br>VSSQ              | Supply           | —      | —                | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC                        | Input            | _      | _                | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           |                  |        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

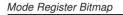

#### Mode Register Set

The mode register stores the data for controlling the various operating modes of the mobile DDR, includes CAS latency, addressing mode, burst length, test mode, and various vendor specific options. The default value of the mode register is not defined. Therefore the mode register must be written after power up to operate the mobile DDR. The device should be activated with the CKE already high prior to writing into the Mode Register. The Mode Register is written by using the MRS command. The state of the address signals registered in the same cycle as MRS command is written in the mode register. The value can be changed as long as all banks are in the idle state.

The mode register is divided into various fields depending on functionality. The burst length uses A2.. A0, CAS latency (read latency from column address) uses A6.. A4. BA0 must be set to low for normal operation. A9.. A12 is reserved for future use. BA1 selects Extended Mode Register Setup operation when set to 1. Refer to the table for specific codes for various burst length, addressing modes and CAS latencies.

#### EMRS

The Extended Mode Register is responsible for setting the Drive strength options and Partial array Self Refresh. The EMRS can be programmed by performing a normal Mode Register Setup operation and setting the BA1=1 and BA0=0. In order to save power consumption, the mobile DDR Sdram has five (PASR) options: Full array, 1/2, 1/4, 3/4 of Full Array. Additionally, the device has internal temperature sensor to control self refresh cycle atuomatically according to the two temperature range; Max. 45 deg C, and Max. 85 deg C. This is the device internal Temperature Compensated Self Refresh(TCSR). The device has four drive strength options: Full, 1/2, 1/4, 3/4.

Extended Mode Reaister Set

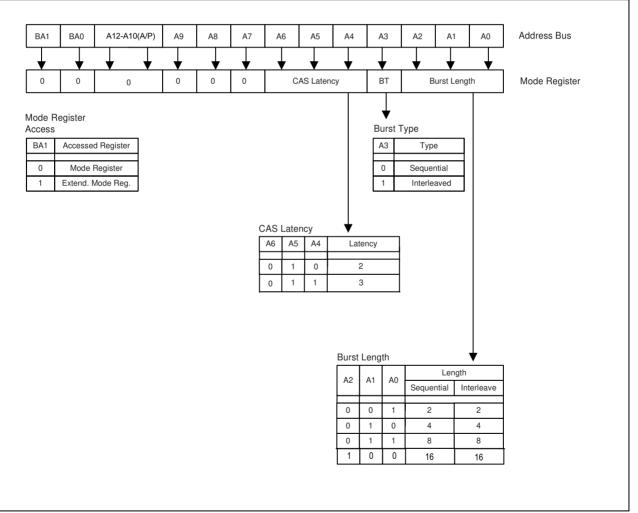

## Signal and Timing Description

### **General Description**

The 1Gbit mobile DDR is a 128M byte mobile DDR SDRAM. It consists of four banks. Each bank is organized as 8192 rows x 1024 columns x 32 bits.

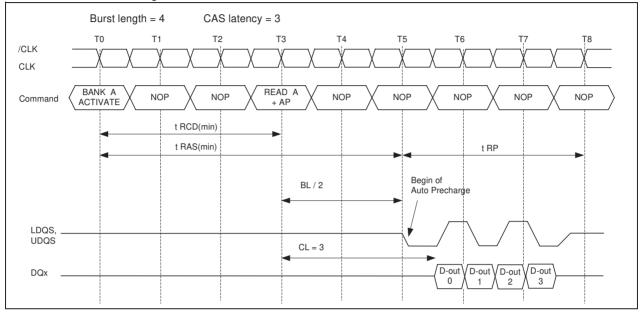

Read and Write accesses are burst oriented. Accesses begin with the registration of an Activate command, which is then followed by a Read or Write command. The address bits registered coincident with the Activate command are used to select the bank and the row to be accessed. BA1 and BA0 select the bank, address bits A13.. A0 select the row. Address bits A9.. A0 registered coincident with the Read or Write command are used to select the starting column location for the burst access.

The regular Single Data Rate SDRAM read and write cycles only use the rising edge of the external clock input. For the mobile SDRAM the special signals DQSx (Data Strobe) are used to mark the data valid window. During read bursts, the data valid window coincides with the high or low level of the DQSx signals. During write bursts, the DQSx signal marks the center of the valid data window. Data is available at every rising and falling edge of DQSx, therefore the data transfer rate is doubled.

For Read accesses, the DQSx signals are aligned to the clock signal CLK.

## Special Signal Description

#### Clock Signal

The mobile DDR operates with a differential clock (CLK and  $\overline{\text{CLK}}$ ) input. CLK is used to latch the address and command signals. Data input and DMx signals are latched with DQSx. The minimum and maximum clock cycle time is defined by  $t_{\text{CK}}$ .

The minimum and maximum clock duty cycle are specified using the minimum clock high time  $t_{CH}$  and the minimum clock low time  $t_{CI}$  respectively.

#### **Command Inputs and Addresses**

Like single data rate SDRAMs, each combination of  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  input in conjunction with  $\overline{CS}$  input at a rising edge of the clock determines a mobile DDR command.

## Data Strobe and Data Mask

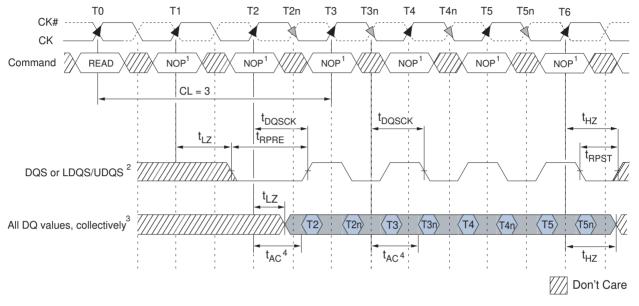

## **Operation at Burst Reads**

The Data Strobes provide a 3-state output signal to the receiver circuits of the controller during a read burst. The data strobe signal goes 1 clock cycle low before data is driven by the mobile DDR and then toggles low to high and high to low till the end of the burst. CAS latency is specified to the first low to high transition. The edges of the Output Data signals and the edges of the data strobe signals during a read are nominally coincident with edges of the input clock. The tolerance of these edges is specified by the parameters  $t_{AC}$  and  $t_{DQSCK}$  and is referenced to the crossing point of the CLK and /CLK signal. The  $t_{DQSQ}$  timing parameter describes the skew between the data strobe edge and the output data edge.

The following table summarizes the mapping of LDQS, UDQS(DQS0  $\sim$  DQS3) and LDM, UDM(DM0  $\sim$  DM3) signals to the data bus.

| Data strobe signal | Data mask signal | Controlled data bus |

|--------------------|------------------|---------------------|

| LDQS, DQS0         | LDM, DM0         | DQ7 DQ0             |

| UDQS, DQS1         | UDM, DM1         | DQ8 DQ15            |

| DQS2               | DM2              | DQ16 DQ23           |

| DQS3               | DM3              | DQ24 DQ31           |

## Mapping of DQS0~DQS3 and DM0~DM3

The minimum time during which the output data is valid is critical for the receiving device. This also applies to the Data Strobe DQS during a read since it is tightly coupled to the output data. The parameters  $t_{QH}$  and  $t_{DQSQ}$  define the minimum output data valid window. Prior to a burst of read data, given that the device is not currently in burst read mode, the data strobe signals transit from Hi-Z to a valid logic low. This is referred to as the data strobe "read preamble"  $t_{RPRE}$ . This transition happens one clock prior to the first edge of valid data.

Once the burst of read data is concluded, given that no subsequent burst read operation is initiated, the data strobe signals transit from a valid logic low to Hi-Z. This is referred to as the data strobe "read postamble" t<sub>RPST</sub>.

## Data Output Timing - t<sub>AC</sub> and t<sub>DQSCK</sub>

Notes: 1. Commands other than NOP can be valid during this cycle.

- 2. DQ transitioning after DQS transitions define  $t_{DQSQ}$  window.

- 3. All DQ must transition by  $\,{}^t_{\text{DQSQ}}$  after DQS transitions, regardless of  $\,{}^t_{\text{AC}.}$

- 4.  $t_{\rm AC}$  is the DQ output window relative to CK and is the long-term component of DQ skew.

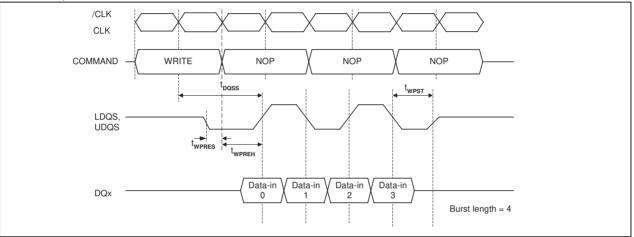

#### **Operation at Burst Write**

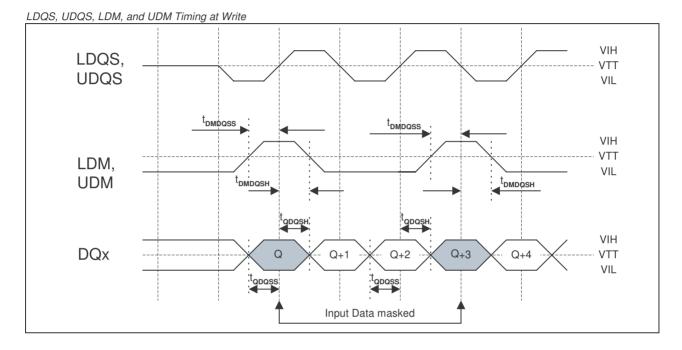

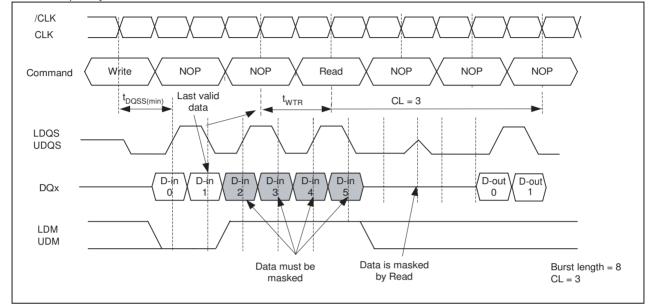

During a write burst, control of the data strobe is driven by the memory controller. The LDQS, UDQS signals are centered with respect to data and data mask. The tolerance of the data and data mask edges versus the data strobe edges during writes are specified by the setup and hold time parameters of data (t<sub>QDQSS</sub> & t<sub>QDQSH</sub>) and data mask (t<sub>DMDQSS</sub> & t<sub>DMDQSH</sub>). The input data is masked in the same cycle when the corresponding LDM, UDM signal is high (i.e. the LDM,UDM mask to write latency is zero.)

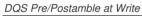

Prior to a burst of write data, given that the controller is not currently in burst write mode, the data strobe signal LDQS, UDQS changes from Hi-Z to a valid logic low. This is referred to as the data strobe Write Preamble. Once the burst of write data is concluded, given no subsequent burst write operation is initiated, the data strobe signal LDQS,UDQS transits from a valid logic low to Hi-Z. This is referred the data strobe Write Postamble, twpst. For mobile DRR data is written with a delay which is defined by the parameter tpQSS, write latency). This is different than the single data rate SDRAM where data is written in the same cycle as the Write command is issued.

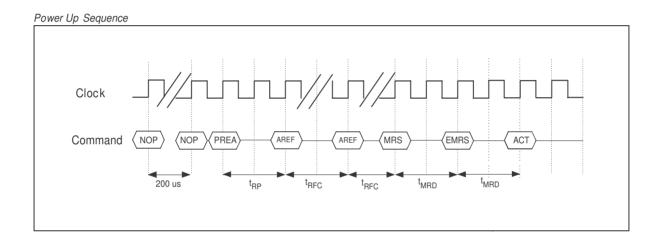

### **Power-Up Sequence**

The following sequence is highly recommended for Power-Up :

- 1. Apply power and start clock. Maintain CKE and the other pins are in NOP conditions at the input

- 2. Apply V<sub>DD</sub> before or at the same time as V<sub>DDQ</sub>, apply V<sub>DDQ</sub> before or at the same time as V<sub>REF</sub>, V<sub>TT</sub>

- 3. Start clock, maintain stable conditions for 200 us

- 4. Apply NOP and set CKE to high

- 5. Apply All Bank Precharge command

- 6. Issue Auto Refresh command twice and must satisfy minimum tRFC

- 7. Issue MRS (Mode Register Set command)

- 8. Issue a EMRS (Extended Mode Register Set command), not necessary

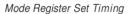

#### Mode Register Set Timing

The mobile DDR should be activated with CKE already high prior to writing into the mode register. Two clock cycles are required complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state.

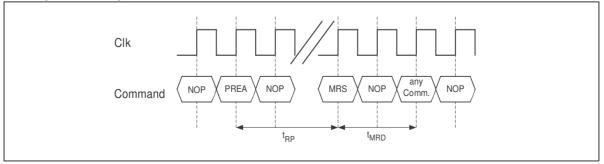

#### Bank Activation Command (ACT)

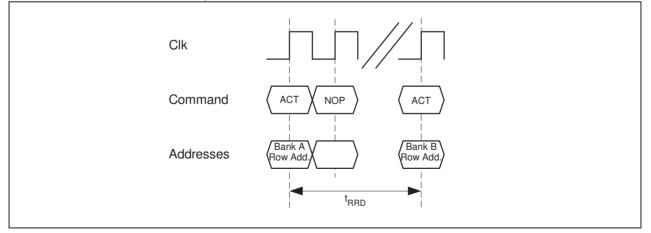

The Bank Activation command is initiated by issuing an ACT command at the rising edge of the clock. The mobile DDR has 4 independent banks which are selected by the two Bank select Addresses (BA0, BA1). The Bank Activation command must be applied before any Read or Write operation can be executed. The delay from the Bank Activation command to the first read or write command must meet or exceed the minimum of RAS to CAS delay time ( $t_{RCDRD}$  min. for read commands and  $t_{RCDWR}$  min. for write commands). Once a bank has been activated, it must be precharged before another Bank Activate command can be applied to the same bank. The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank activation delay time ( $t_{RCD}$  min).

#### Activate to Read or Write Command Timing (one bank)

#### Activate Bank A to Activate Bank B Timing

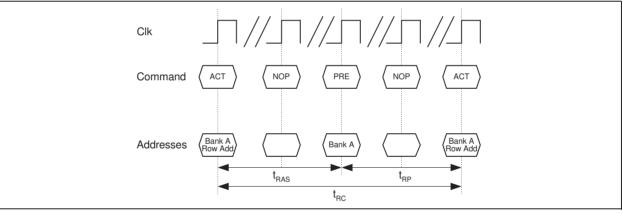

#### Precharge Command

This command is used to precharge or close a bank that has been activated. Precharge is initiated by issuing a Precharge command at the rising edge of the clock. The Precharge command can be used to precharge each bank respectively or all banks simultaneously. The Bank addresses BA0 and BA1 select the bank to be precharged. After a Precharge command, the analog delay t<sub>RP</sub> has to be met until a new Activate command can be initiated to the same bank.

#### Table

Precharge Control

| A10/AP | BA1 | BA0 | Precharged  |

|--------|-----|-----|-------------|

| 0      | 0   | 0   | Bank A Only |

| 0      | 0   | 1   | Bank B Only |

| 0      | 1   | 0   | Bank C Only |

| 0      | 1   | 1   | Bank D Only |

| 1      | Х   | Х   | All Banks   |

#### Precharge Command Timing

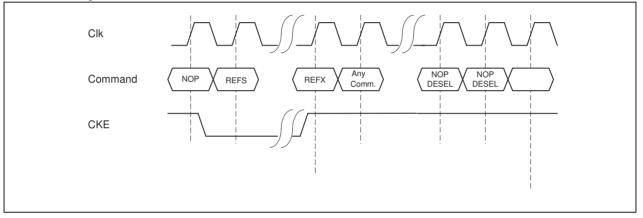

#### Self Refresh

The Self Refresh mode can be used to retain the data in the mobile DDR if the chip is powered down. To set the mobile DDR into a Self Refreshing mode, a Self Refresh command must be issued and CKE held low at the rising edge of the clock. Once the Self Refrest command is initiated, CKE must stay low to keep the device in Self Refresh mode. During the Self Refresh mode, all of the external control signals are disabled except CKE. The clock is internally disabled during Self Refresh operation to reduce power. An internal timing generator guarantees the self refreshing of the memory content.

#### Self Refresh timing

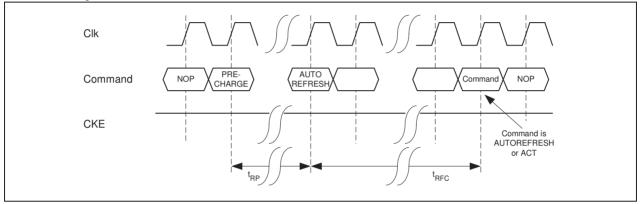

#### Auto Refresh

The auto refresh function is initiated by issuing an Auto Refresh command at the rising edge of the clock. All banks must be precharged and idle before the Auto Refresh command is applied. No control of the external address pins is required once this cycle has started. All necessary addresses are generated in the device itself. When the refresh cycle has completed, all banks will be in the idle state. A delay between the Auto Refresh command and the next Activate Command or subsequent Auto Refresh Command must be greater than or equal to the t <sub>RFC</sub>(min).

#### Autorefresh timing

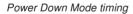

#### Power Down Mode

The Power Down Mode is entered when CKE is set low and exited when CKE is set high. The CKE signal is sampled at the rising edge of the clock. Once the Power Down Mode is initiated, all of the receiver circuits except CLK and the CKE circuits are gated off to reduce power consumption. All banks can be set to idle state or stay activate during Power Down Mode, but burst activity may not be performed. After exiting from Power Down Mode, at least one clock cycle of command delay must be inserted before starting a new command. During Power Down Mode, refresh operations cannot be performed; therefore, the device cannot remain in Power Down Mode longer than the refresh period (t REF) of the device.

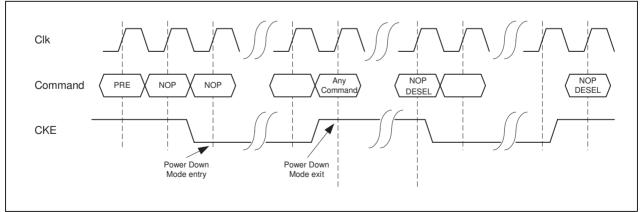

#### Deep Power Down Mode

The Deep Power Down mode is an unique function with very low standby currents. All internal volatge generators inside the mobile DDR are stopped and all memory data is lost in this mode. To enter the Deep Power Down mode all banks must be precharged.

## **Deep Power Down Mode Entry**

The deep power down mode has to be maintained for a minimum of 100µs.

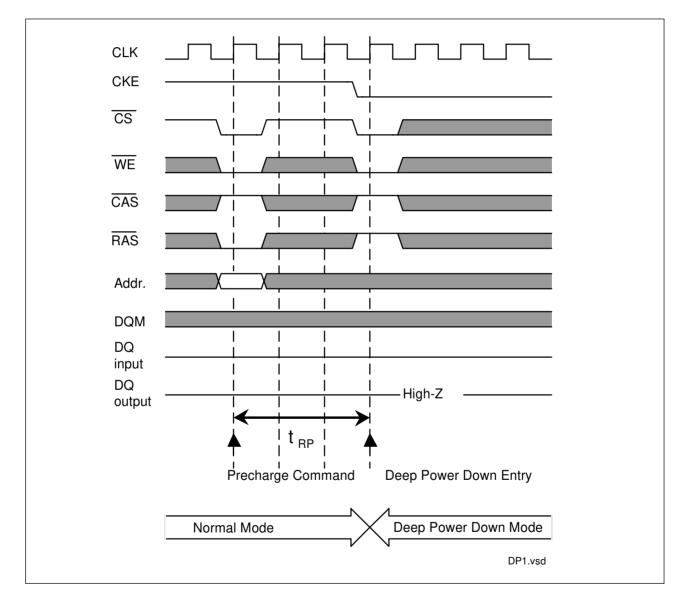

### Deep Power Down Exit

The deep power down mode is exited by asserting CKE high.

- After the exit, the following sequence is needed to enter a new command :

- 1. Maintain NOP input conditions for a minimum of 200 us

- 2. Issue precharge commands for all banks of the device

- 3. Issue two or more auto refresh commands and satisfy minimum  $t_{\mbox{RFC}}$

- 4. Issue a mode register set command to initialize the mode register

- 5. Issue an extended mode register set command to initialize the extende mode register

#### **Burst Mode Operation**

Burst mode operation is used to provide a constant flow of data to the memory (write cycle) or from the memory (read cycle). The burst length is programmable and set by address bits A0 - A3 during the Mode Register Setup command. The burst length controls the number of words that will be output after a read command or the number of words to be input after a write command. One word is 32 bits wide. The sequential burst length can be set to 2, 4 or 8 data words.

| Burst Length | Starting Column Address |    | Address | Order of Access within a Burst |  |  |

|--------------|-------------------------|----|---------|--------------------------------|--|--|

| Buist Length | A2                      | A1 | A0      | Type = Sequential              |  |  |

| 2            |                         |    | 0       | 0 - 1                          |  |  |

| 2            |                         |    | 1       | 1 - 0                          |  |  |

|              |                         | 0  | 0       | 0 - 1 - 2 - 3                  |  |  |

| 4            |                         | 0  | 1       | 1 - 2 - 3 - 0                  |  |  |

| 4            |                         | 1  | 0       | 2 - 3 - 0 - 1                  |  |  |

|              |                         | 1  | 1       | 3 - 0 - 1 - 2                  |  |  |

| 8            | 0                       | 0  | 0       | 0 - 1 - 2 - 3 - 4 - 5 - 6 - 7  |  |  |

|              | 0                       | 0  | 1       | 1 - 2 - 3 - 4 - 5 - 6 - 7 - 0  |  |  |

|              | 0                       | 1  | 0       | 2 - 3 - 4 - 5 - 6 - 7 - 0 - 1  |  |  |

|              | 0                       | 1  | 1       | 3 - 4 - 5 - 6 - 7 - 0 - 1 - 2  |  |  |

|              | 1                       | 0  | 0       | 4 - 5 - 6 - 7 - 0 - 1 - 2 - 3  |  |  |

|              | 1                       | 0  | 1       | 5 - 6 - 7 - 0 - 1 - 2 - 3 - 4  |  |  |

|              | 1                       | 1  | 0       | 6 - 7 - 0 - 1 - 2 - 3 - 4 - 5  |  |  |

|              | 1                       | 1  | 1       | 7 - 0 - 1 - 2 - 3 - 4 - 5 - 6  |  |  |

Burst Mode and Sequence

Note: standard interleaved burst mode also available but not specified here.

#### Burst Read Operation: (READ)

The Burst Read operation is initiated by issuing a READ command at the rising edge of the clock after  $t_{RCD}$  from the bank activation. The address inputs (A8.. A0) determine the starting address for the burst. The burst length (2, 4 or 8) must be defined in the Mode Register. The first data after the READ command is available depending on the CAS latency. The subsequent data is clocked out on the rising and falling edge of LDQS, UDQS until the burst is completed. The LDQS, UDQS signals are generated by the mobile DDR during the Burst Read Operation.

Burst Read Operation

#### Burst Write Operation (WRITE)

The Burst Write is initiated by issuing a WRITE command at the rising edge of the clock. The address inputs (A8 .. A0) determine starting column address. Data for the first burst write cycle must be applied on the DQ pins on the first rise edge of LDQS, UDQS follow WRITE command. The time between the WRITE command and the first corresponding edge of the data strobe is tDQSS. The remaining data inputs must be supplied on each subsequent rising and falling edge of the data strobe until the burst length is completed. When the burst has been finished, any additional data supplied to the DQ pins will be ignored.

#### Burst Write Operation

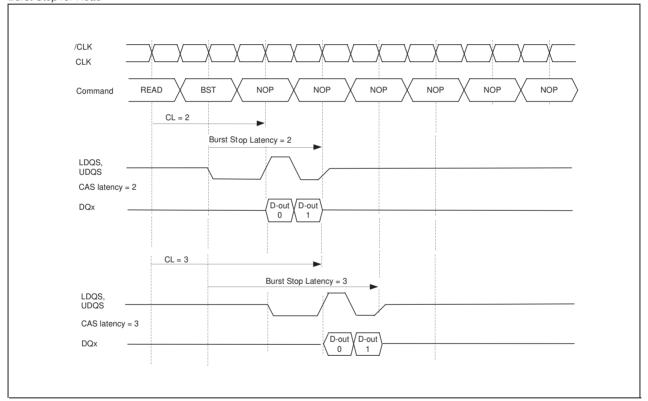

## Burst Stop Command (BST)

A Burst Stop is initiated by issuing a BURST STOP command at the rising edge of the clock. The Burst Stop Command has the fewest restrictions, making it the easiest method to terminate a burst operation before it has been completed. When the Burst Stop Command is issued during a burst read cycle, read data and LDQS, UDQS go to a high-Z state after a delay which is equal to the CAS latency set in the Mode Register. The Burst Stop latency is equal to the CAS latency CL. The Burst Stop command is not supported during a write burst operation. Burst Stop is also illegal during Read with Auto-Precharge.

#### Burst Stop for Read

#### Data Mask (LDM, UDM) Function

The mobile DDR has a Data Mask function that can be used only during write cycles. When the Data Mask is activated, active high during burst write, the write operation is masked immediately. The LDM, UDM to data-mask latency zero. LDM and UDM can be issued at the rising or negative edge of Data Strobe.

#### Read Concurrent Auto Precharge

#### Concurrent Read Auto Precharge Support

| Asserted  |     | For same Bank |    | For different Bank |     |     |

|-----------|-----|---------------|----|--------------------|-----|-----|

| Command   | T4  | Т5            | Т6 | T4                 | T5  | Т6  |

| READ      | NO  | NO            | NO | NO                 | YES | YES |

| READ+AP   | YES | YES           | NO | NO                 | YES | YES |

| ACTIVATE  | NO  | NO            | NO | YES                | YES | YES |

| PRECHARGE | YES | YES           | NO | YES                | YES | YES |

Note: This table is for the case of Burst Length = 4, CAS Latency =3 and  $t_{WR}$ =2 clocks

When READ with Auto Precharge is asserted, new commands can be asserted at T4,T5 and T6 as shown in Table

An Interrupt of a running READ burst with Auto Precharge i.e. at T4 and T5 to the same bank with another READ+AP command is allowed, it will extend the begin of the internal Precharge operation to the last READ+AP command.

Interrupts of a running READ burst with Auto Precharge i.e. at T4 are not allowed when doing concurrent command to another active bank. ACTIVATE or PRECHARGE commands to another bank are always possible while a READ with Auto Precharge operation is in progress.

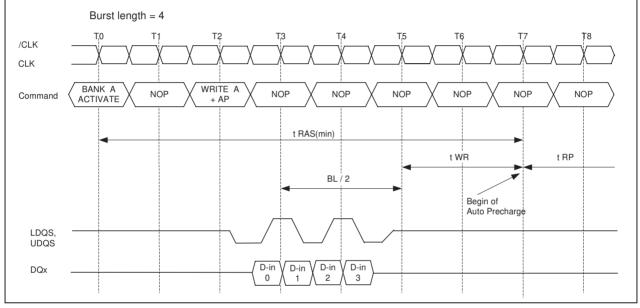

#### Write with Autoprecharge (WRITEA)

If A8 is high when a Write command is issued, the Write with Auto-Precharge function is performed. The internal precharge begins after the write recovery time t<sub>WR</sub> and t<sub>RAS</sub>(min) are satisfied.

If a Write with Auto Precharge command is initiated, the mobile DDR automatically enters the precharge operation at the first rising edge of CLK after the last valid edge of DQS (completion of the burst) plus the write recovery time  $t_{WR}$ . Once the precharge operation has started, the bank cannot be reactivated and the new command can not be asserted until the Precharge time ( $t_{RP}$ ) has been satisfied. If  $t_{RAS}$ (min) has not been satisfied yet, an internal interlock will delay the precharge operation until it is satisfied.

Write Burst with Auto Precharge

Note: tWR starts at the first rising edge of clock after the last valid edge of the 4 DQSx.

#### Table

Concurrent Write Auto Precharge Support

| Asserted  |     |    | For san | ne Bank |    |    | For different Bank |     |     |     |     |

|-----------|-----|----|---------|---------|----|----|--------------------|-----|-----|-----|-----|

| Command   | Т3  | T4 | T5      | T6      | T7 | T8 | Т3                 | T4  | T5  | T6  | T7  |

| WRITE     | NO  | NO | NO      | NO      | NO | NO | NO                 | YES | YES | YES | YES |

| WRITE+AP  | YES | NO | NO      | NO      | NO | NO | NO                 | YES | YES | YES | YES |

| READ      | NO  | NO | NO      | NO      | NO | NO | NO                 | NO  | NO  | NO  | YES |

| READ+AP   | NO  | NO | NO      | NO      | NO | NO | NO                 | NO  | NO  | NO  | YES |

| ACTIVATE  | NO  | NO | NO      | NO      | NO | NO | YES                | YES | YES | YES | YES |

| PRECHARGE | NO  | NO | NO      | NO      | NO | NO | YES                | YES | YES | YES | YES |

When Write with Auto Precharge is asserted, new commands can be asserted at T3.. T8 as shown in Table .

An Interrupt of a running WRITE burst with Auto Precharge i.e. at T3 to the same bank with another WRITE+AP command is allowed as long as the burst is running, it will extend the begin of the internal Precharge operation to the last WRITE+AP command.

Interrupts of a running WRITE burst with Auto Precharge i.e. at T3 are not allowed when doing concurrent WRITE s to another active bank. Consecutive WRITE or WRITE+AP bursts (T4.. T7) to other open banks are possible. ACTIVATE or PRECHARGE commands to another bank are always possible while a WRITE with Auto Precharge operation is in progress.

Write interrupted by Read

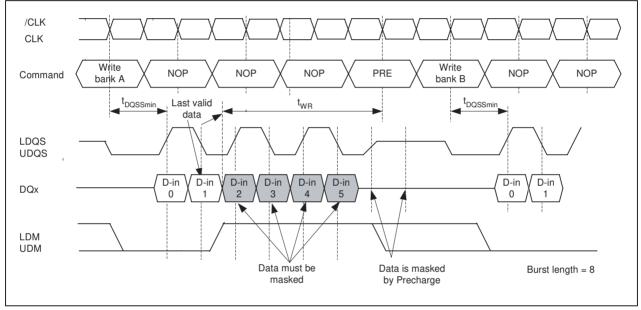

#### Write Interrupted by a Precharge

A Burst Write operation can be interrupted before completion of the burst by a Precharge of the same bank. Random column access is allowed. A Write Recovery time ( $t_{WR}$ ) is required from the last data to Precharge command. When Precharge command is asserted, any residual data from the burst write cycle must be masked by LDM, UDM.

Write interrupted by Precharge

#### Command Table

#### Table Command Overview

| Operation                         | Code                 | CKE<br>n-1 | CKE<br>n | CS#    | RAS#       | CAS#       | WE#        | BA0    | BA1    | A10    | A0-9<br>A11,12 |

|-----------------------------------|----------------------|------------|----------|--------|------------|------------|------------|--------|--------|--------|----------------|

| Device Deselect                   | DESEL                | Н          | Х        | Н      | Х          | Х          | Х          | Х      | Х      | Х      | Х              |

| No operation                      | NOP                  | Н          | Х        | L      | Н          | Н          | Н          | Х      | Х      | Х      | Х              |

| Mode Register Setup               | MRS                  | Н          | Х        | L      | L          | L          | L          | 0      | 0      | OPC    | ODE            |

| Extended Mode Register Setup      | EMRS                 | Н          | Х        | L      | L          | L          | L          | 0      | 1      | OPC    | ODE            |

| Bank Activate                     | ACT                  | Н          | Х        | L      | L          | Н          | Н          | BA     | BA     | Row A  | ddress         |

| Read                              | READ                 | Н          | Х        | L      | Н          | L          | Н          | BA     | BA     | L      | Col.           |

| Read with Auto Precharge          | READA                | Н          | Х        | L      | Н          | L          | Н          | BA     | BA     | Н      | Col.           |

| Write Command                     | WRITE                | Н          | Х        | L      | Н          | L          | L          | BA     | BA     | L      | Col.           |

| Write Command with Auto Precharge | WRITEA               | Н          | Х        | L      | Н          | L          | L          | BA     | BA     | Н      | Col.           |

| Burst Stop                        | BST                  | Н          | Х        | L      | Н          | Н          | L          | Х      | Х      | Х      | Х              |

| Precharge Single Bank             | PRE                  | Н          | Х        | L      | L          | Н          | L          | BA     | BA     | L      | Х              |

| Precharge All Banks               | PREAL                | Н          | Х        | L      | L          | Н          | L          | Х      | Х      | Н      | Х              |

| Autorefresh                       | REF                  | Н          | Н        | L      | L          | L          | Н          | Х      | Х      | Х      | Х              |

| Self Refresh Entry                | REFX                 | Н          | L        | L      | L          | L          | Н          | Х      | Х      | Х      | Х              |

| Self Refresh Exit                 | SREFEX               | L<br>L     | H<br>H   | H<br>L | X<br>H     | X<br>H     | X<br>H     | X<br>X | X<br>X | X<br>X | X<br>X         |

| Power Down Mode Entry (Note 1)    | PWDNEN               | H<br>H     | L        | H<br>L | X<br>H     | X<br>H     | X<br>H     | X<br>X | X<br>X | X<br>X | X<br>X         |

| Power Down Mode Exit              | PWDNEX               | L          | Н        | H<br>L | X<br>valid | X<br>valid | X<br>valid | Х      | х      | х      | х              |

| Deep Power Down Mode Entry        | Idle                 | Н          | L        | L      | Н          | Н          | L          | Х      | х      | х      | х              |

| Deep Power Down Mode Exit         | Deep pow-<br>er down | L          | Н        | Х      | Х          | Х          | Х          | Х      | Х      | Х      | Х              |

Note: 1: The Power Down Mode Entry command is illegal during Burst Read or Burst Write operations.

#### Function Truth Table I

| Current<br>State | Command        | Address     | Action                                                         | Notes |

|------------------|----------------|-------------|----------------------------------------------------------------|-------|

|                  | DESEL          | Х           | NOP                                                            | 3     |

|                  | NOP            | Х           | NOP                                                            | 3     |

|                  | BST            | Х           | NOP                                                            | 3     |

|                  | READ / READA   | BA,CA,A10   | ILLEGAL                                                        | 1     |

| IDLE             | WRITE / WRITEA | BA,CA,A10   | ILLEGAL                                                        | 1     |

|                  | ACT            | BA, RA      | Bank Active                                                    |       |

|                  | PRE / PREAL    | BA, A10     | NOP                                                            |       |

|                  | AREF / SREF    | Х           | AUTO-Refresh or Self-Refresh                                   | 4     |

|                  | MRS / EMRS     | Op-Code     | Mode Register Set or Extended Mode Register Set                |       |

|                  | DESEL          | Х           | NOP                                                            |       |

|                  | NOP            | Х           | NOP                                                            |       |

|                  | BST            | Х           | NOP                                                            |       |

|                  | READ / READA   | BA, CA, A10 | Begin Read, Determine Auto Precharge                           | 9     |

| ROW<br>ACTIVE    | WRITE / WRITEA | BA, CA, A10 | Begin Write, Determine Auto Precharge                          | 9     |

|                  | ACT            | BA, RA      | ILLEGAL                                                        | 1, 5  |

|                  | PRE / PREAL    | BA, A10     | Precharge / Precharge All                                      | 6     |

|                  | AREF / SREF    | х           | ILLEGAL                                                        |       |

|                  | MRS / EMRS     | OP-Code     | ILLEGAL                                                        |       |

|                  | DESEL          | Х           | Continue burst to end                                          |       |

|                  | NOP            | Х           | Continue burst to end                                          |       |

|                  | BST            | х           | Terminate Burst                                                |       |

|                  | READ / READA   | BA, CA, A10 | Terminate burst, Begin New Read, Determine Auto-<br>Prechgarge | 7     |

| READ             | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                                        | 2, 7  |

|                  | ACT            | BA, RA      | ILLEGAL                                                        | 1     |

|                  | PRE / PREAL    | BA ,A10     | Terminate Burst / Precharge                                    |       |

|                  | AREF / SREF    | х           | ILLEGAL                                                        |       |

|                  | MRS / EMRS     | Op-Code     | ILLEGAL                                                        |       |

|                  | DESEL          | Х           | Continue burst to end, Precharge                               |       |

|                  | NOP            | х           | Continue burst to end, Precharge                               |       |

|                  | BST            | Х           | ILLEGAL                                                        |       |

| READ with        | READ / READA   | BA, CA, A10 | ILLEGAL                                                        |       |

| Auto             | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                                        |       |

| Precharge        | ACT            | BA, RA      | ILLEGAL                                                        | 1     |

|                  | PRE / PREAL    | BA ,A10     | ILLEGAL                                                        | 1     |

|                  | AREF / SREF    | х           | ILLEGAL                                                        |       |

|                  | MRS / EMRS     | Op-Code     | ILLEGAL                                                        |       |

#### Function Truth Table I

| Current<br>State  | Command        | Address     | Action                                                         | Notes |

|-------------------|----------------|-------------|----------------------------------------------------------------|-------|

|                   | DESEL          | X           | Continue burst to end                                          |       |

|                   | NOP            | х           | Continue burst to end                                          |       |

|                   | BST            | х           | ILLEGAL                                                        |       |

|                   | READ / READA   | BA, CA, A10 | Terminate Burst, Begin Read, Determine Auto-<br>Precharge.     | 7, 8  |

| WRITE             | WRITE / WRITEA | BA, CA, A10 | Terminate Burst, Begin new Write, Determine Auto-<br>Precharge | 2, 7  |

|                   | ACT            | BA, RA      | ILLEGAL                                                        | 1     |

|                   | PRE / PREAL    | BA, A10     | Terminate Burst , Precharge                                    | 8     |

|                   | AREF / SREF    | X           | ILLEGAL                                                        |       |

|                   | MRS / EMRS     | OP-Code     | ILLEGAL                                                        |       |

|                   | DESEL          | Х           | Continue burst to end, Precharge                               |       |

|                   | NOP            | Х           | Continue burst to end, Precharge                               |       |

|                   | BST            | Х           | ILLEGAL                                                        |       |

| WRITE with        | READ / READA   | BA, CA, A10 | ILLEGAL                                                        |       |

| Auto              | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                                        |       |

| Precharge         | ACT            | BA, RA      | ILLEGAL                                                        | 1     |

|                   | PRE / PREAL    | BA, A10     | ILLEGAL                                                        |       |

|                   | AREF / SREF    | Х           | ILLEGAL                                                        |       |

|                   | MRS / EMRS     | OP-Code     | ILLEGAL                                                        |       |

|                   | DESEL          | Х           | NOP ( Row Active after t <sub>RCD</sub> )                      |       |

|                   | NOP            | Х           | NOP ( Row Active after t <sub>RCD</sub> )                      |       |

|                   | BST            | Х           | NOP ( Row Active after t <sub>RCD</sub> )                      |       |

|                   | READ / READA   | BA, CA, A10 | ILLEGAL                                                        | 1, 9  |

| ROW<br>ACTIVATING | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                                        | 1, 9  |

|                   | ACT            | BA, RA      | ILLEGAL                                                        | 1, 5  |

|                   | PRE / PREAL    | BA, A10     | ILLEGAL                                                        | 1, 6  |

|                   | AREF / SREF    | Х           | ILLEGAL                                                        |       |

|                   | MRS / EMRS     | OP-Code     | ILLEGAL                                                        |       |

|                   | DESEL          | Х           | NOP ( Row Idle after t <sub>RP</sub> )                         |       |

|                   | NOP            | Х           | NOP ( Row Idle after t <sub>RP</sub> )                         |       |

|                   | BST            | Х           | NOP ( Row Idle after t <sub>RP</sub> )                         |       |

|                   | READ / READA   | BA, CA, A10 | ILLEGAL                                                        | 1     |

| PRECHARGE         | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                                        | 1     |

|                   | ACT            | BA, RA      | ILLEGAL                                                        | 1     |

|                   | PRE / PREAL    | BA, A10     | NOP ( Row Idle after t <sub>RP</sub> ) 1                       | 1     |

|                   | AREF / SREF    | X           | ILLEGAL                                                        | 1     |

|                   | MRS / EMRS     | OP-Code     | ILLEGAL                                                        |       |

#### Function Truth Table I

| Current<br>State         | Command        | Address     | Action                                  | Notes |

|--------------------------|----------------|-------------|-----------------------------------------|-------|

|                          | DESEL          | X           | NOP (Row Active after tWR)              |       |

|                          | NOP            | X           | NOP (Row Active after tWR)              |       |

|                          | BST            | X           | NOP (Row Active after t <sub>WR</sub> ) |       |

|                          | READ / READA   | BA, CA, A10 | Begin Read, Determine Auto-Prechgarge   | 2     |

| WRITE<br>RECOVERING      | WRITE / WRITEA | BA, CA, A10 | Begin Write, Determine Auto-Prechgarge  |       |

|                          | ACT            | BA, RA      | ILLEGAL                                 | 2     |

|                          | PRE / PREAL    | BA ,A10     | ILLEGAL                                 | 1, 10 |

|                          | AREF / SREF    | Х           | ILLEGAL                                 |       |

|                          | MRS / EMRS     | OP-Code     | ILLEGAL                                 |       |

|                          | DESEL          | Х           | NOP (Precharge after tWR)               |       |

|                          | NOP            | Х           | NOP (Precharge after tWR)               |       |

|                          | BST            | Х           | NOP (Precharge after t <sub>WR</sub> )  |       |

| WRITE                    | READ / READA   | BA, CA, A10 | ILLEGAL                                 | 1, 2  |

| RECOVERING<br>with AUTO- | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                 | 1     |

| PRECHARGE                | ACT            | BA, RA      | ILLEGAL                                 | 1     |

|                          | PRE / PREAL    | BA ,A10     | ILLEGAL                                 | 1     |

|                          | AREF / SREF    | х           | ILLEGAL                                 |       |

|                          | MRS / EMRS     | OP-Code     | ILLEGAL                                 |       |

|                          | DESEL          | Х           | NOP (Idle after t <sub>RC</sub> )       |       |

|                          | NOP            | Х           | NOP (Idle after t <sub>RC</sub> )       |       |

|                          | BST            | Х           | NOP (Idle after t <sub>RC</sub> )       |       |

|                          | READ / READA   | BA, CA, A10 | ILLEGAL                                 |       |

| REFRESH                  | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                 |       |

|                          | ACT            | BA, RA      | ILLEGAL                                 | 11    |

|                          | PRE / PREAL    | BA ,A10     | ILLEGAL                                 |       |

|                          | AREF / SREF    | X           | ILLEGAL                                 |       |

|                          | MRS / EMRS     | OP-Code     | ILLEGAL                                 |       |

|                          | DESEL          | X           | NOP (Idle after two clocks)             |       |

|                          | NOP            | Х           | NOP (Idle after two clocks)             |       |

|                          | BST            | Х           | NOP (Idle after two clocks)             |       |

| (EXTENDED)               | READ / READA   | BA, CA, A10 | ILLEGAL                                 |       |

| MODE<br>REGISTER         | WRITE / WRITEA | BA, CA, A10 | ILLEGAL                                 |       |

| SET                      | ACT            | BA, RA      | ILLEGAL                                 |       |

|                          | PRE / PREAL    | BA ,A10     | ILLEGAL                                 |       |

|                          | AREF / SREF    | X           | ILLEGAL                                 |       |

|                          | MRS / EMRS     | OP-Code     | ILLEGAL                                 |       |

- Note: All entries assume the CKE was High during the preceding clock cycle

- Note: 1. Illegal to bank specified states; function may be legal in the bank indicated by BAx, depending on the state of that bank

- Note: 2. Must satisfy bus contention, bus turn around, write recovery requirements.

- Note: 3. If both banks are idle, and CKE is inactive, the device will enter Power Down Mode. All input buffers except CKE, CLK and CLK# will be disabled.

- Note: 4. If both banks are idle, and CKE is deactivated coincidentally with an AutoRefresh command, the device will enter SelfRefresh Mode. All input buffers except CKE will be disabled.

- Note: 5. Illegal, if t<sub>RRD</sub> is not satisfied.

- Note: 6. Illegal, if t<sub>RAS</sub> is not satisfied.

- Note: 7. Must satisfy burst interrupt condition.

- Note: 8. Must mask two preceding data bits with the DM pin.

- Note: 9. Illegal, if t<sub>RCD</sub> is not satisfied.

- Note: 10. Illegal, if t<sub>WR</sub> is not satisfied.

- Note: 11. Illegal, if t<sub>RC</sub> is not satisfied.

#### Abbreviations:

| Н   | High Level       |

|-----|------------------|

| L   | Low Level        |

| Х   | Don't Care       |

| V   | Valid Data Input |

| RA  | Row Address      |

| ВА  | Bank Address     |

| PA  | Precharge All    |

| NOP | No Operation     |

| CA  | Column Address   |

| Ax  | Address Line x   |

### FUNCTION TRUTH TABLE for CKE

| Current<br>State | CKE<br>n-1 | CKE<br>n | CS# | RAS# | CAS# | WE# | Address | Action                                           | Notes |

|------------------|------------|----------|-----|------|------|-----|---------|--------------------------------------------------|-------|

|                  | Н          | L        | L   | L    | L    | Н   | Х       | Self Refresh Entry                               | 1     |

|                  | L          | Н        | Н   | Х    | Х    | Х   | Х       | Exit Self-Refresh                                | 1     |

|                  | L          | Н        | L   | Н    | Н    | Н   | Х       | Exit Self-Refresh                                | 1     |

| SELF<br>REFRESH  | L          | Н        | L   | Н    | Н    | L   | Х       | ILLEGAL                                          | 1     |

|                  | L          | Н        | L   | н    | Н    | Х   | Х       | ILLEGAL                                          | 1     |

|                  | L          | Н        | L   | L    | L    | Х   | Х       | ILLEGAL                                          | 1     |

|                  | L          | L        | Х   | Х    | Х    | Х   | Х       | NOP ( Maintain Self Refresh)                     | 1     |

|                  | Н          | Х        | Х   | Х    | Х    | Х   | Х       | INVALID                                          |       |

| POWER<br>DOWN    | L          | Н        | Х   | Х    | Х    | Х   | Х       | Exit Power Down ( Idle after t <sub>PDEX</sub> ) | 1     |

|                  | L          | L        | Х   | Х    | Х    | Х   | Х       | NOP ( Maintain Power Down)                       |       |

|                  | Н          | Н        | Х   | Х    | Х    | Х   | Х       | Refer to Function Truth Table                    | 2     |

|                  | Н          | L        | L   | L    | L    | Н   | Х       | Enter Self Refresh                               | 3     |

|                  | Н          | L        | Н   | Х    | Х    | Х   | Х       | Enter Power-Down                                 | 2     |

| ALL<br>BANKS     | Н          | L        | L   | н    | Н    | Н   | Х       | Enter Power-Down                                 | 2     |

| IDLE             | Н          | L        | L   | н    | Н    | L   |         | ILLEGAL                                          | 2     |

|                  | Н          | L        | L   | Н    | L    | Х   |         | ILLEGAL                                          | 2     |

|                  | Н          | L        | L   | L    | Х    | Х   |         | ILLEGAL                                          | 2     |

|                  | L          | Х        | Х   | Х    | Х    | Х   | Х       | Refer to Power Down in this table                |       |

| All other states | Н          | Н        | Х   | Х    | Х    | Х   | Х       | Refer to Funtion Truth Table                     |       |

Note: 1. CKE low-to-high transition re-enables inputs asynchronously. A minimum setup time to CLK must be satisfied before any commands other than EXIT are executed.

Note: 2. Power Down can be entered when all banks are idle (banks can be active or precharged)

Note: 3. Self Refresh can be entered only from the Precharge / Idle state.

Abbreviations:

| Н   | High Level       |

|-----|------------------|

| L   | Low Level        |

| х   | Don't Care       |

| V   | Valid Data Input |

| RA  | Row Address      |

| ВА  | Bank Address     |

| PA  | Precharge All    |

| NOP | No Operation     |

| CA  | Column Address   |

Mobile DDR SDRAM

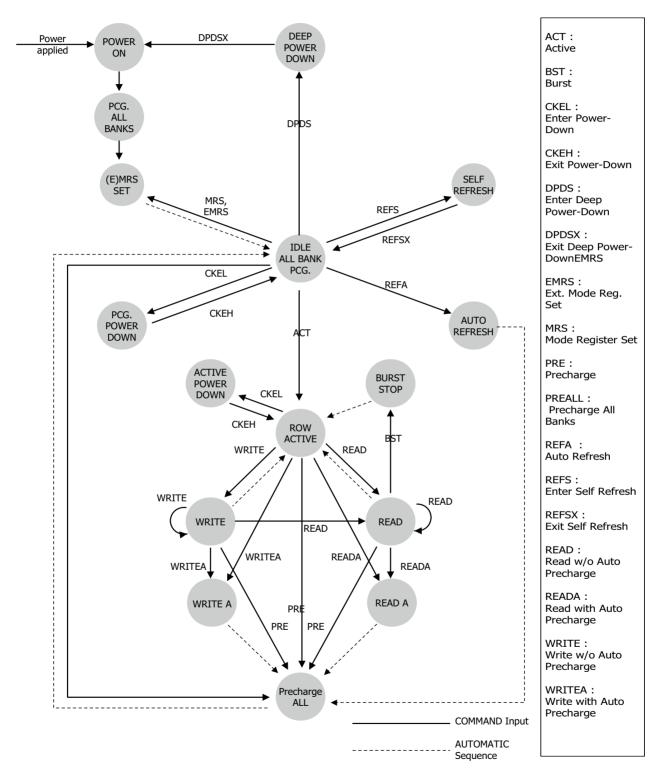

## operation State Diagram

## IDD Max Specifications and Conditions

| <b>2</b>                                                                                                                                                                                           |              | Version |       |    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-------|----|--|

| Conditions                                                                                                                                                                                         | Symbol       | -5      | Unit  |    |  |

| <b>Operating current - One bank Active-Precharge;</b> tRC = tRC (mir CKE = High; CS = High between valid command; Address inputs ar 2 clock cycles; Data bus inputs are stable                     | IDD0         | 100.0   | mA    |    |  |

| <b>Precharge power-down standby current;</b> All banks idle; CKE = L tCK = tCK (min); Address and control inputs are switching; Data bu                                                            |              | IDD2P   | 600   | uA |  |

| Precharge power-down standby current; Clock stopped; All banl<br>CS = High; CK = Low; CK# = High; Address and control inputs are<br>Data bus inputs are stable                                     |              | IDD2PS  | 600   | uA |  |

| Precharge nonpower-down standby current; All banks idle; CKE tCK = tCK (min); Address and control inputs are switching; Data bu                                                                    |              | IDD2N   | 18.0  | mA |  |

| Precharge nonpower-down standby current; Clock stopped; All<br>CKE = High; CS = High; CK = Low; CK# = High; Address and control<br>Data bus inputs are stable                                      | IDD2NS       | 14.0    | mA    |    |  |

| Active power-down standby current; One bank active; CKE = Lc<br>tCK = tCK (min); Address and control inputs are switching; Data bu                                                                 | -            | IDD3P   | 5.0   | mA |  |

| Active power-down standby current; Clock stopped; One bank a<br>CS = High; CK = Low; CK# = High; Address and control inputs are<br>Data bus inputs are stable                                      |              | IDD3PS  | 5.0   | mA |  |

| Active nonpower-down standby current; One bank active; CKE tCK = tCK (min); Address and control inputs are switching; Data bu                                                                      |              | IDD3N   | 20.0  | mA |  |

| Active nonpower-down standby current; Clock stopped; One ban<br>CS = High; CK = Low; CK# = High; Address and control inputs are<br>Data bus inputs are stable                                      | -            | IDD3NS  | 16.0  | mA |  |

| <b>Operating current - burst read;</b> One bank active; Burst length = 4<br>Continuous Read burst; Address inputs are switching every 2 clock<br>50% of data changing at every burst; lout = 0 m A |              | IDD4R   | 150.0 | mA |  |

| <b>Operating current - burst write;</b> One bank active; Burst length = 4<br>Continuous Write burst; Address inputs are switching every 2 clock<br>50% of data changing at every burst             | IDD4W        | 150.0   | mA    |    |  |

| Auto refresh current; Burst refresh; CKE = High; Address and                                                                                                                                       | tRFC = 110ns | IDD5    | 100.0 | mA |  |

| control inputs are switching; Data bus inputs are stable                                                                                                                                           | tRFC = tREFI | IDD5A   | 15.0  | mA |  |

| Deep Power Down Current; Address and control inputs are stable<br>Data bus inputs are stable                                                                                                       | ;            | IDD8    | 10.0  | uA |  |

## Partial Array Self Refresh Current (PASR)

| Parameter & Test Condition                             | Extended Mode<br>Register A[2:0]<br>Tcase [ <sup>o</sup> C] | Symb. | max. | Unit | Note |

|--------------------------------------------------------|-------------------------------------------------------------|-------|------|------|------|

| Self Refresh Current<br>Self Refresh Mode              | 85°C max.                                                   | ICC6  | 1200 | uA   |      |

| CKE=Low, tck=min,<br>full array activations, all banks | 45°C max.                                                   | ICC6  | 500  | uA   |      |

| Self Refresh Current<br>Self Refresh Mode              | 85ºC max.                                                   | ICC6  | 900  | uA   |      |

| CKE=Low, tck=min,<br>1/2 array activations             | 45°C max.                                                   | ICC6  | 300  | uA   |      |

| Self Refresh Current<br>Self Refresh Mode              | 85ºC max.                                                   | ICC6  | 760  | uA   |      |

| CKE=Low, tck=min,<br>1/4 array activation              | 45ºC max.                                                   | ICC6  | 220  | uA   |      |

## Absolute Maximum Ratings

| Parameter                                                     | Symbol                             | Value      | Unit |

|---------------------------------------------------------------|------------------------------------|------------|------|

| Voltage on any pin relative to $V_{SS}$                       | V <sub>IN</sub> , V <sub>OUT</sub> | -0.5 ~ 2.7 | V    |

| Voltage on $V_{\text{DD}}$ supply relative to $V_{\text{SS}}$ | V <sub>DD</sub> , V <sub>DDQ</sub> | -0.5 ~ 2.7 | V    |

| Storage temperature                                           | T <sub>STG</sub>                   | -55 ~ +150 | °C   |

| Power dissipation                                             | P <sub>D</sub>                     | 1.0        | W    |

| Short circuit current                                         | I <sub>OS</sub>                    | 50         | mA   |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to recommended operating condition. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

## *Capacitance* ( $V_{DD}$ = 1.8V, $T_A$ = 25°C, f = 1MHz)

| Parameter                                                                                                                                  | Symbol           | Min | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|------|

| Input capacitance ( $A_0 \sim A_{12}$ , $BA_0 \sim BA_{1,}$ CKE, $\overline{CS}$ , $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ ) | C <sub>IN1</sub> | 1.5 | 3.0 | pF   |

| Input capacitance ( CK, CK,)                                                                                                               | C <sub>IN2</sub> | 1.5 | 3.0 | pF   |

| Data & DQS input/output capacitance (DQ0~DQ15)                                                                                             | C <sub>OUT</sub> | 3.0 | 5.0 | pF   |

| Input capacitance (DMs)                                                                                                                    | C <sub>IN3</sub> | 3.0 | 5.0 | pF   |

## Power & DC Operating Conditions (LVCMOS In/Out)

Recommended operating conditions ( Voltage referenced to  $V_{SS}\text{=}$  0V )

| Parameter                | Symbol           | Min                  | Тур | Мах                    | Unit |

|--------------------------|------------------|----------------------|-----|------------------------|------|

| Device Supply voltage    | V <sub>DD</sub>  | 1.7                  | 1.8 | 1.95                   | V    |

| Output Supply voltage    | V <sub>DDQ</sub> | 1.7                  | 1.8 | 1.95                   | V    |

| Input logic high voltage | V <sub>IH</sub>  | 0.7*V <sub>DDQ</sub> | -   | V <sub>DDQ</sub> +0.30 | V    |

| Input logic low voltage  | V <sub>IL</sub>  | -0.3                 | -   | 0.3*V <sub>DDQ</sub>   | V    |

| Input Leakage current    | - II             | -2                   | -   | 2                      | uA   |

| Output Leakage current   | IOZ              | -5                   | -   | 5                      | uA   |

## AC Input Operating Conditions

Recommended operating conditions ( Voltage referenced to  $V_{SS}$ = 0V,  $V_{DD}$ = 1.7V-1.9V )

| Parameter                                                         | Symbol          | Min                   | Тур | Max                   | Unit |

|-------------------------------------------------------------------|-----------------|-----------------------|-----|-----------------------|------|

| Input High (Logic 1) Voltage; DQ                                  | V <sub>IH</sub> | V <sub>CCQ</sub> *0.8 | -   | V <sub>CCQ</sub> +0.3 | V    |

| Input Low (Logic 0) Voltage; DQ                                   | V <sub>IL</sub> | -0.3                  | -   | 0.2* V <sub>DDQ</sub> | V    |

| Clock Input Crossing Point Voltage; CK and $\overline{\text{CK}}$ | V <sub>IX</sub> | 0.4*V <sub>DDQ</sub>  | -   | 0.6*V <sub>DDQ</sub>  | V    |

## AC Operating Test Conditions

Recommended operating conditions ( Voltage referenced to  $V_{SS}\text{=}$  0V,  $V_{DD}\text{=}$  1.7V-1.9V )

| Parameter                                 | Value               | Unit |

|-------------------------------------------|---------------------|------|

| AC input levels (Vih/Vil)                 | 0.8*VDDQ / 0.2*VDDQ | V    |

| Input timing measurement reference level  | 0.5*VDDQ            | V    |

| Input signal minimum slew rate            | 1.0                 | V/ns |

| Output timing measurement reference level | 0.5*VDDQ            | V    |

| Output load condition                     | See below figures   |      |

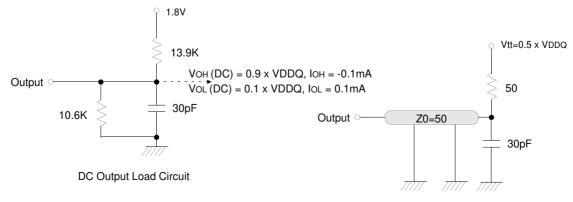

AC Output Load Circuit

# AC Timing Parameters & Specification

| AC CHARACTERISTICS                                         |             |                     | -                                     | -5   |                 |       |

|------------------------------------------------------------|-------------|---------------------|---------------------------------------|------|-----------------|-------|

| PARAMETER                                                  |             | SYMBOL              | MIN                                   | МАХ  | UNITS           | NOTES |

| Output data access time from CK/CK                         |             | <sup>t</sup> AC     | 2                                     | 5    | ns              | 3     |

| CK high-level width                                        |             | <sup>t</sup> CH     | 0.45                                  | 0.55 | <sup>t</sup> CK |       |

| CK low-level width                                         |             | <sup>t</sup> CL     | 0.45                                  | 0.55 | <sup>t</sup> CK |       |

| Clock cycle time                                           | CL = 3      | <sup>t</sup> CK (3) | 5                                     | -    | ns              | 1     |

| DQ and DM input hold time relative                         | e to DQS    | <sup>t</sup> DH     | 0.4                                   |      | ns              | 5,6   |

| DQ and DM input setup time relativ                         | ve to DQS   | <sup>t</sup> DS     | 0.4                                   |      | ns              | 5,6   |

| DQ and DM input pulse width (for e                         | each input) | <sup>t</sup> DIPW   | 1.4                                   |      | ns              |       |

| Access window of DQS from CK/C                             | ĸ           | <sup>t</sup> DQSCK  | 2                                     | 5    | ns              |       |

| DQS input high pulse width                                 |             | <sup>t</sup> DQSH   | 0.4                                   | 0.6  | <sup>t</sup> CK |       |

| DQS input low pulse width                                  |             | <sup>t</sup> DQSL   | 0.4                                   | 0.6  | <sup>t</sup> CK |       |

| DQS-DQ skew, DQS to last DQ valid, per group, per access   |             | <sup>t</sup> DQSQ   |                                       | 0.4  | ns              | 1     |

| Write command to first DQS latching transition             |             | <sup>t</sup> DQSS   | 0.75                                  | 1.25 | <sup>t</sup> CK |       |

| Half clock period                                          |             | <sup>t</sup> HP     | <sup>t</sup> CH,<br><sup>t</sup> CL   |      | ns              |       |

| Data-out high-impedance window from CK/CK                  |             | <sup>t</sup> HZ     | 0.4                                   | 0.6  | <sup>t</sup> CK |       |

| Data-out low-impedance window from CK/CK                   |             | <sup>t</sup> LZ     | 1                                     |      | ns              |       |

| Address and control input hold time                        | e           | tIH                 | 0.9                                   |      | ns              | 1     |

| Address and control input setup tin                        | ne          | <sup>t</sup> IS     | 0.9                                   |      | ns              | 1     |

| LOAD MODE REGISTER comman cycle time                       | nd          | <sup>t</sup> MRD    | 2                                     |      | <sup>t</sup> CK |       |

| DQ-DQS hold, DQS to first DQ to g<br>non-valid, per access | ĵo          | <sup>t</sup> QH     | <sup>t</sup> HP<br>- <sup>t</sup> QHS |      | ns              |       |

| Data hold skew factor                                      |             | <sup>t</sup> QHS    |                                       | 0.5  | ns              |       |

| ACTIVE to PRECHARGE comman                                 | ld          | <sup>t</sup> RAS    | 40                                    | 70K  | ns              |       |

| ACTIVE to READ with Auto precharge command                 |             | <sup>t</sup> RAP    | 15                                    |      | ns              |       |

| ACTIVE to ACTIVE/AUTO REFRE command period                 | SH          | <sup>t</sup> RC     | 55                                    |      | ns              |       |

| AUTO REFRESH command period                                | ł           | <sup>t</sup> RFC    | 72                                    |      | ns              |       |

| ACTIVE to READ or WRITE delay                              |             | <sup>t</sup> RCD    | 15                                    |      | ns              |       |

| PRECHARGE command period                                   |             | <sup>t</sup> RP     | 15                                    |      | ns              |       |

| AC CHARACTERISTICS                     | -5                 |                                        |     |                 |       |

|----------------------------------------|--------------------|----------------------------------------|-----|-----------------|-------|

| PARAMETER                              | SYMBOL             | MIN                                    | МАХ | UNITS           | NOTES |

| DQS read preamble                      | <sup>t</sup> RPRE  | 0.9                                    | 1.1 | <sup>t</sup> CK |       |