# International

## μHVIC<sup>™</sup>

#### Features

- VDS(on) or VCE(on) sensing

- Eliminates external current sensing resistors

- Enables inductance-less current sensing

- 600V blocking capability

- Programmability and temperature compensation possible

- No VCC required

- Gate drive on/off sync input

- Filter delay at GATE turn-on (200nsec typ.)

- 20.8V zener clamps on GATE and CS pins

- Integrated ESD protection and latch immunity on all pins

- Tiny 5-pin SOT-23 package

#### Applications

- MOSFET, DirectFET, or IGBT current sensing

- Over-current protection

- Industrial applications

- Motor control

- Power tools

- Brick converters

- Forklifts

- Induction heating

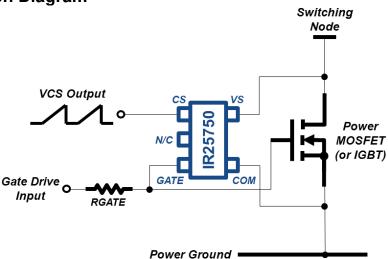

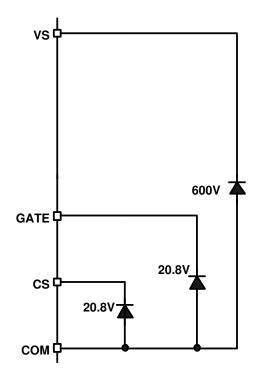

#### Typical Connection Diagram

#### Description

The IR25750L is a novel current sensing IC that extracts the VDS(on) of a power MOSFET, or the VCE(on) of an IGBT, during the switch on-time. IR's proprietary 600V HVIC technology then blocks the high drain voltage to during the MOSFET or IGBT off-time. This IC allows for external current sensing resistors to be eliminated for reducing power losses and increasing overall system efficiency. The IC includes a gate drive input that provides VCC supply voltage to the IC and synchronizes the internal sensing circuit to and off times the the on of switch. Programmability and temperature compensation are also possible.

SOT-23 Current Sensing IC

**IR25750LPBF**

#### Package Options

#### **Ordering Information**

| Dees Deut Number | Deskens Ture | Standard Pack |          | Ordenakla Davi Number |

|------------------|--------------|---------------|----------|-----------------------|

| Base Part Number | Package Type | Form          | Quantity | Orderable Part Number |

| IR25750LPBF      | SOT23-5L     | Tape and Reel | 3000     | IR25750LTRPBF         |

### IR25750LPBF

| Table of Contents                              | Page |

|------------------------------------------------|------|

| Description                                    | 1    |

| Ordering Information                           | 1    |

| Typical Connection Diagram                     | 1    |

| Absolute Maximum Ratings                       | 3    |

| Recommended Operating Conditions               | 3    |

| Electrical Characteristics                     | 4    |

| Functional Block Diagram                       | 5    |

| Timing Diagram                                 | 6    |

| Pin Definitions                                | 7    |

| Pin Assignments                                | 7    |

| Input / Output Pin Equivalent Circuit Diagrams | 8    |

| Functional Description                         | 9    |

| Package Details: 5L SOT-23                     | 13   |

| Tape and Reel Details: 5L SOT-23               | 14   |

| Part Marking Information                       | 16   |

| Qualification Information                      | 17   |

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any pin. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Definition                                 |           | Min              | Max                   | Units |

|-------------------|--------------------------------------------|-----------|------------------|-----------------------|-------|

| Vs                | VS pin voltage                             |           | -20 <sup>†</sup> | 625                   |       |

| V <sub>GATE</sub> | GATE pin voltage                           |           | 0.0              | , tt                  | V     |

| V <sub>CS</sub>   | CS pin voltage                             |           | 0.3              | V <sub>CLAMP</sub> '' |       |

| R <sub>OJA</sub>  | Thermal resistance, junction to ambient    | 5L SOT-23 | _                | 191                   | ºC/W  |

| TJ                | Junction temperature                       |           | 55               | 150                   |       |

| Ts                | Storage temperature                        |           | -00              | 150                   | °C    |

| TL                | IC pin temperature (soldering, 10 seconds) |           | _                | 300                   |       |

† The test condition for the minimum –VS rating is for a pulse width of 1usec. Larger pulse widths will result in a lower –VS voltage rating.

†† This IC contains a 20.8V voltage clamp structure between the GATE and COM pins, and, between the CS and COM pins. Please note that this pin should not be driven by a DC, low impedance power source greater than the VCLAMP specified in the Electrical Characteristics section.

#### **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

| Symbol            | Definition           | Min  | Max                | Units |

|-------------------|----------------------|------|--------------------|-------|

| Vs                | VS pin voltage       | -5.0 | 600                |       |

| V <sub>GATE</sub> | GATE pin voltage     | 0014 | M                  | V     |

| V <sub>CS</sub>   | CS pin voltage       | COM  | V <sub>CLAMP</sub> |       |

| TJ                | Junction temperature | -40  | 125                | °C    |

#### **Electrical Characteristics**

$T_A = 25$  °C unless otherwise specified. All parameters are referenced to COM.

| Symbol                 | Definition                                                 | Min  | Тур  | Max  | Units | Test<br>Conditions                  |  |

|------------------------|------------------------------------------------------------|------|------|------|-------|-------------------------------------|--|

| GATE Pin C             | GATE Pin Characteristics                                   |      |      |      |       |                                     |  |

| t <sub>DLY</sub>       | GATE-to-CS rising-edge blank delay time                    | _    | 200  | _    | nsec  | V <sub>GATE</sub> = rising<br>edge  |  |

| V <sub>CLAMP1</sub>    | GATE pin internal Zener clamp voltage                      | 21.1 | 22.5 | 24.0 | V     | $I_{GATE} = 1mA$                    |  |

| High-Voltag            | High-Voltage Switching Node Input (VS Pin) Characteristics |      |      |      |       |                                     |  |

| I <sub>LK</sub>        | Offset supply leakage current                              | _    | _    | 50   | μA    | $V_{GATE} = COM,$<br>$V_{S} = 600V$ |  |

| R <sub>vs_cs</sub>     | VS-to-CS 'ON' resistance                                   | _    | 6.2  | _    | kΩ    | $V_{GATE} = 15V$                    |  |

| CS Pin Characteristics |                                                            |      |      |      |       |                                     |  |

| V <sub>CS_LOW</sub>    | CS pin voltage during GATE pin 'low' state                 | _    | COM  | _    | V     | $V_{GATE} = COM$                    |  |

| V <sub>CLAMP2</sub>    | CS pin internal Zener clamp voltage                        | _    | 20.8 | _    |       | I <sub>CS</sub> = 1mA               |  |

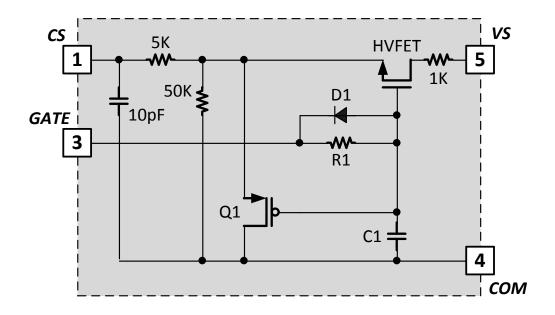

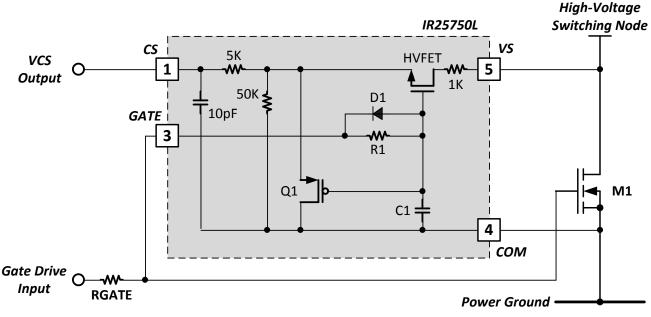

#### **Functional Block Diagram**

IR25750LPBF

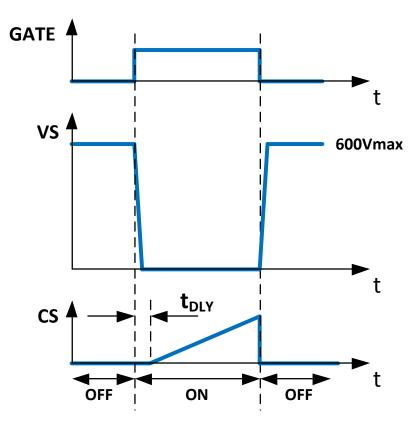

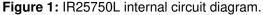

#### **Timing Diagram**

#### **Pin Definitions**

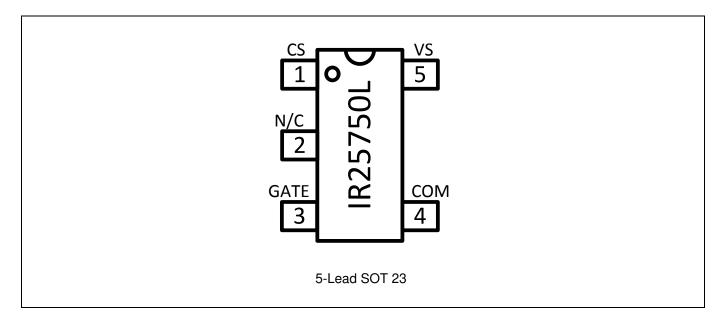

| Pin | Symbol | Description                                  |  |  |

|-----|--------|----------------------------------------------|--|--|

| 1   | CS     | Current sense output                         |  |  |

| 2   | N/C    | No connect                                   |  |  |

| 3   | GATE   | /CC supply and on/off sync input             |  |  |

| 4   | СОМ    | IC ground                                    |  |  |

| 5   | VS     | Switch drain or collector input sensing node |  |  |

#### **Pin Assignments**

#### Input / Output Pin Equivalent Circuit Diagrams

#### **Functional Description**

#### I. General Description

The IR25750L current sensing circuit eliminates the traditional series-connected sensing resistor and is connected instead in parallel to the power switch. The circuit measures the VDS(on) of the switching power MOSFET or VCE(on) of an IGBT. The IC has four external connection nodes (VS, GATE, CS, COM) and includes (Figure 1): a 600V MOSFET (HVFET); an RC-delay circuit (R1, C1, D1); and a PMOS hold-down transistor (Q1). The circuit does not require a VCC supply node and instead utilizes the existing gate drive signal for powering and turning the circuit on and off. During the off-time of the external power switch (M1), the gate drive signal is at COM, the HVFET is off, Q1 is on, and the CS node is held at COM. Since the internal HVFET is off, any high voltage occurring at the drain of the power MOSFET (600Vmax) will be safely blocked by the HVFET from the rest of the low-voltage circuitry. When M1 is turned on by the gate drive signal, the drain voltage of M1 will decrease to a level given by the VDS(on) of M1. After a short delay time (200nsec, typical) set by the internal R-C delay block (R1, C1), the gate voltage of the HVFET rises up and turns the HVFET on. Q1 turns off, therefore releasing the CS output pin. The VDS(on) of M1 is then transmitted from the VS pin, through the HVFET, to the CS output pin. There is an internal voltage divider formed by a 1Kohm resistor at the VS pin, the RDS(on) of the HVFET (0.2Kohm), and a 50Kohm resistor from the source of HVFET to COM. The ratio of this resistor divider is approximately unity (50/51.2), resulting an excellent matching from the VS pin to the CS pin. A small series R-C filter (5K and 10pF) also exists at the CS pin to help suppress high-frequency noise. Also, important to note, to avoid internal high-voltage damage to the IC, the IR25750L must always turn on after a slight delay from M1 (as set by the internal 200nsec delay block). To ensure this delay, the gate resistor (RGATE) must be placed before the GATE pin of the IR25750L and the gate of M1. The GATE pin of the IR25750L and the gate of M1 are then connected together to form a single gate node.

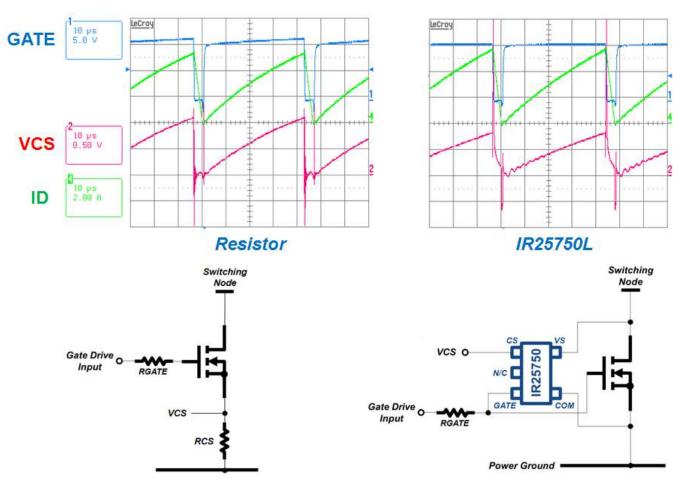

When the gate drive signal of M1 goes low again, M1 turns off, and the gate of the HVFET gets discharged quickly through D1. The HVFET turns off again and blocks any high voltage occurring at the drain of M1. The CS output pin is then held at COM again through Q1. Assuming the drain of M1 is a typical high-voltage switching node that is connected to an inductor, the voltage signal produced at the CS output node will be the same sawtooth waveform that would result from using a traditional current sensing resistor placed at the source of M1 (**Figure 2**). The CS output pin can then be connected to a comparator circuit or used for any other desired current-sensing functions of a PWM controller or MCU circuit.

Figure 2: IR25750L timing diagram.

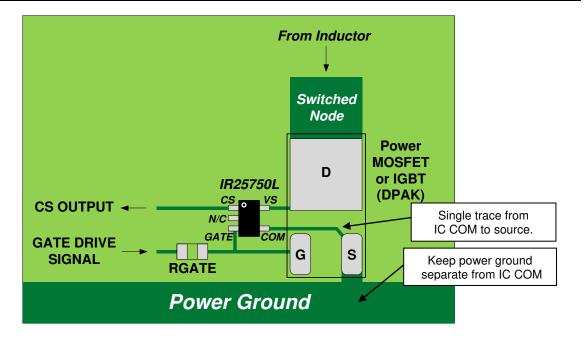

#### **II. PCB Layout Guidelines**

Since no VCC node is required for this circuit, the pcb layout becomes very simple to design (**Figure 3**). The IR25750L can be placed conveniently next to the power MOSFET or IGBT and connected easily to the existing pcb traces that are already used for the power switch (GATE, DRAIN, SOURCE). Only the CS trace needs to be routed back to the main PWM controller or MCU of the power supply circuit. Also, important to note, the power ground of the switching circuit must be separate from the COM connection of the IR25750L. The COM pin of the IR25750L should be connected to the source of the power MOSFET with a *single trace only*, and, the power ground *should not* be routed through the COM pin of the IR25750L.

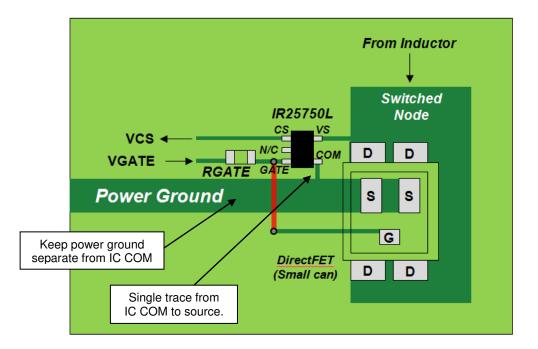

A typical pcb layout is also shown for a DirectFET footprint (**Figure 4**). Again, the IR25750L can be placed directly next to the MOSFET and connected to the existing traces.

#### IR25750LPBF

Figure 3: IR25750L typical pcb surface-mount layout (DPAK or D2PAK MOSFET or IGBT).

Figure 4: IR25750L typical pcb surface-mount layout (DirectFET).

#### **III. Current Sensing Functionality**

With the IR25750L connected properly in a switching circuit application, the waveforms (**Figure 4**) show the functionality of the circuit and the desired current sense signal at the CS pin. Compared to the conventional resistor sensing method, both methods match the actual current shape and both exhibit noise spikes due to switching. Proper filtering or digital blanking of the final PWM or MCU current sensing circuit will easily ignore these noise spikes to prevent any false triggering.

Figure 4: IR25750L switching waveforms vs. resistor method (green=IDRAIN, red=VCS, blue=GATE). (RCS=0.21 ohms, RDS(on)=0.18 ohms)

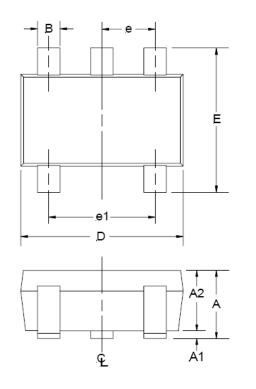

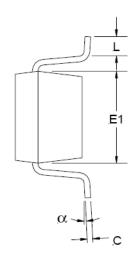

#### Package Details: 5L SOT-23

| SYMBOL | MIN      | MAX  |  |

|--------|----------|------|--|

| А      | 0.90     | 1.45 |  |

| A1     | 0.00     | 0.15 |  |

| A2     | 0.90     | 1.30 |  |

| В      | 0.25     | 0.50 |  |

| С      | 0.09     | 0.20 |  |

| D      | 2.80     | 3.00 |  |

| E      | 2.60     | 3.00 |  |

| E1     | 1.50     | 1.75 |  |

| е      | 0.95 REF |      |  |

| e1     | 1.90 REF |      |  |

| L      | 0.35     | 0.55 |  |

| α      | 08       | 108  |  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

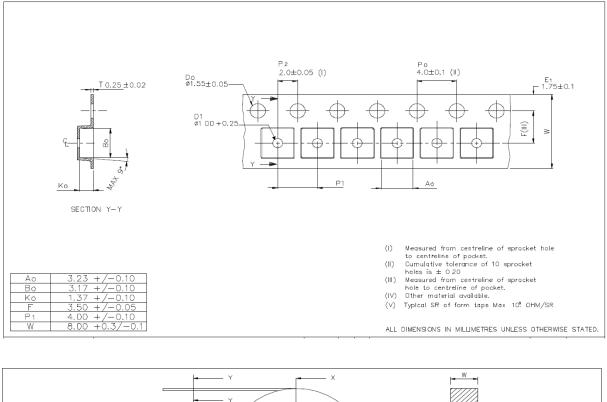

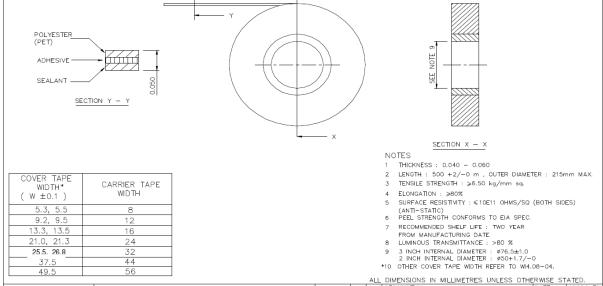

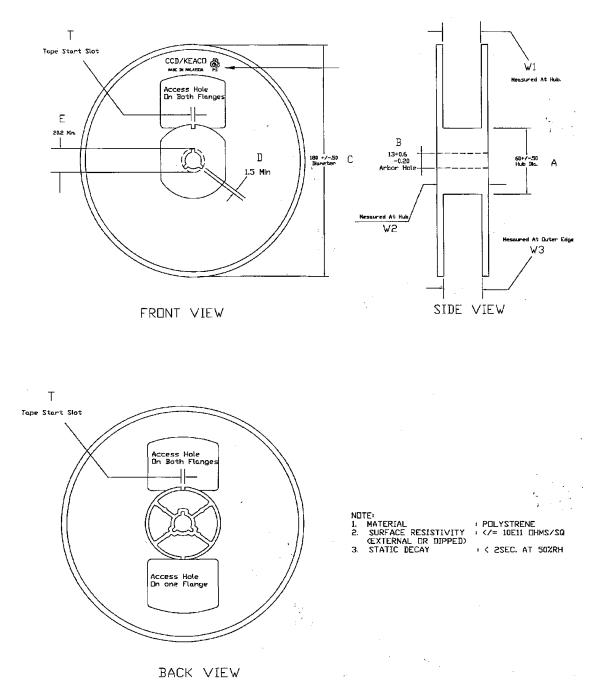

#### Tape and Reel Details: 5L SOT-23

#### Tape and Reel Details: 5L SOT-23

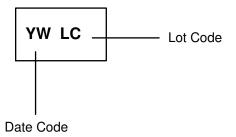

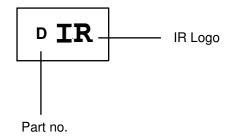

#### Part Marking Information: 5L SOT-23

#### **Top Marking**

#### **Bottom Marking**

#### **Qualification Information**<sup>†</sup>

| Qualification Level        |                  | Industrial <sup>††</sup><br>(per JEDEC JESD 47)                                                                                                                           |                                                        |  |  |

|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|

|                            |                  | Comments: This family of ICs has passed JEDEC's<br>Industrial qualification. IR's Consumer qualification level is<br>granted by extension of the higher Industrial level. |                                                        |  |  |

| Moisture Sensitivity Level |                  | SOT-23                                                                                                                                                                    | MSL1 <sup>†††</sup><br>(per IPC/JEDEC J-STD-020)       |  |  |

| ESD                        | Machine Model    | Class A<br>(per JEDEC standard EIA/JESD22-A115-A)                                                                                                                         |                                                        |  |  |

| ESD                        | Human Body Model | (per ANSI/ESD                                                                                                                                                             | Class 1B<br>(per ANSI/ESDA/JEDEC standard JS-001-2012) |  |  |

| IC Latch-Up Test           |                  |                                                                                                                                                                           | Class I, Level A<br>(per JESD78)                       |  |  |

| RoHS Compliant             |                  |                                                                                                                                                                           | Yes                                                    |  |  |

+ Qualification standards can be found at International Rectifier's web site <u>http://www.irf.com/</u>

- ++ Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- +++ Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center http://www.irf.com/technical-info/

> WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245