# LC898213XC

Advance Information

# AF Controller

### Overview

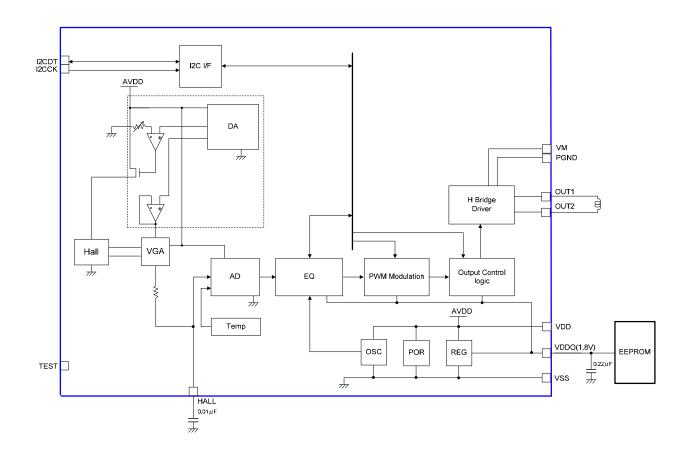

This LSI is AF control LSI. It consists of 1 system of feed back circuit for AF control.

#### Features

- Built-in equalizer circuit using digital operation

- AF control equalize circuit

- Any coefficient can be specified by  $I^2 C \ I/F$

- I<sup>2</sup>C Interface

- Built-in A/D converter

- Maximum 10-bit

- Input 2 channel

- Built-in D/A converter

- 8-bit

- Output 2-channel (Hall offset, Constant current Bias)

- Built-in Hall Sensor

Si Hall sensor

- Built-in VGAHall Amp

- Built-in OSC

48MHz (Frequency adjustment function)

- Built-in PWM pulse generator circuit

PWM circuit for AF control

- 1-chip motor driver

Saturation drive H bridge 1 channel

- Package

- WL-CSP 11-pin

- Lead-free, halogen-free

- Supply voltage

- Logic unit : Internal core (1.7V to 1.98V), AVDD (2.6V to 3.6V)

- Driver unit : VM (2.6V to 3.6V)

- \* I<sup>2</sup>C Bus is a trademark of Philips Corporation.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 5 of this data sheet.

WLCSP11, 1.10x2.20

## **Pin Description**

| ТҮРЕ                               |                                      |                    |                      |                      |             |  |  |

|------------------------------------|--------------------------------------|--------------------|----------------------|----------------------|-------------|--|--|

| I                                  | INPUT                                | Ρ                  | Power supply,<br>GND | NC                   | NOT CONNECT |  |  |

| 0                                  | OUTPUT                               |                    |                      |                      |             |  |  |

| В                                  | BIDIRECTION                          |                    |                      |                      |             |  |  |

|                                    |                                      |                    |                      |                      |             |  |  |

| $\blacksquare$ I <sup>2</sup> C in | nterface                             |                    | 2                    |                      |             |  |  |

|                                    | I2CCK                                | B $I^2C$ Clock pin |                      |                      |             |  |  |

| I2CDT B I <sup>2</sup> C Data pin  |                                      |                    |                      |                      |             |  |  |

|                                    |                                      |                    |                      |                      |             |  |  |

| ∎ Hall                             | <ul> <li>Hall interface</li> </ul>   |                    |                      |                      |             |  |  |

|                                    | HALL                                 |                    | Hall amp output      |                      |             |  |  |

| D.                                 |                                      |                    |                      |                      |             |  |  |

| ■ Drive                            | <ul> <li>Driver interface</li> </ul> |                    | • • • •              |                      |             |  |  |

|                                    | OUT1                                 | 0                  | _                    | Actuator output pin  |             |  |  |

|                                    | OUT2                                 | 0                  | Actuator outpu       | Actuator output pin  |             |  |  |

| - Douv                             | an annalt, ain                       |                    |                      |                      |             |  |  |

| Powe                               | Power supply pin                     |                    | Digital norman       |                      |             |  |  |

|                                    | VDD                                  |                    |                      | Digital power supply |             |  |  |

|                                    | VSS                                  | P Digital GND      |                      |                      |             |  |  |

|                                    | VDDO                                 | Р                  | LDO power supply out |                      |             |  |  |

|                                    | VM                                   | Р                  | Motor power supply   |                      |             |  |  |

|                                    | PGND                                 | Р                  | Power GND            | Power GND            |             |  |  |

| - Tosta                            | nin                                  |                    |                      |                      |             |  |  |

| ■ Test pin                         |                                      |                    |                      |                      |             |  |  |

|                                    | TEST O Test pin                      |                    |                      |                      |             |  |  |

|                                    |                                      |                    |                      |                      |             |  |  |

\*Process when pins are not used

PIN TYPE "O" – Ensure that it is set to OPEN.

PIN TYPE "I" – OPEN is inhibited. Ensure that it is connected to the Vdd or Vss even when it is unused. (Please contact ON Semiconductor company for more information about selection of Vdd or Vss.) PIN TYPE "B" – If you are unsure about processing method on the pin description of pin layout table, please contact us.

Note that incorrect processing of unused pins may result in defects.

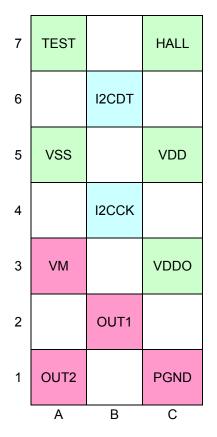

# Pin Layout

| Circuit Name | Number of Pins | Circuit Name | Number of Pins |

|--------------|----------------|--------------|----------------|

| Analog       | 5              | Driver       | 4              |

| Logic        | 2              |              |                |

Backside pin layout diagram (Top View from the mold side)

# **Block Diagram**

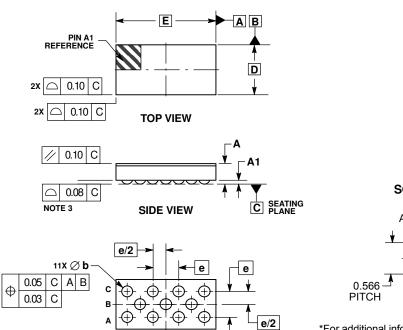

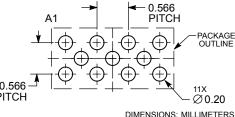

#### **Package Dimensions**

unit : mm

### WLCSP11, 1.10x2.20

CASE 567HP ISSUE O

NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS. MILLIMETERS MIN MAX DIM 0.45 Α A1 0.03 0.13 b D 0.15 0.25 1.10 BSC 20 BS 0.566 BS e RECOMMENDED

NOTES

# SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **ORDERING INFORMATION**

2 3 4 5 6

**BOTTOM VIEW**

| Device        | Package                                      | Shipping (Qty / Packing) |

|---------------|----------------------------------------------|--------------------------|

| LC898213XC-MH | WLP11(2.20X1.10)<br>(Pb-Free / Halogen Free) | 5000 / Tape & Reel       |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees ansing out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.