# VC-02 Specification

Version V1.0.0

Copyright ©2022

# **Document resume**

| Version | Date       | Development/revision content | Formulate | Approval  |

|---------|------------|------------------------------|-----------|-----------|

| V1.0.0  | 2022.03.03 | First Edition                | Jiye Yang | Ning Guan |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

|         |            |                              |           |           |

# Content

| 1. Product overview                         | 4  |

|---------------------------------------------|----|

| 1.1. Characteristics                        | 5  |

| 2. Main parameters                          | 6  |

| 2.1. Static requirements                    | 6  |

| 2.2. Electrical characteristics.            | 7  |

| 2.3. Power consumption                      | 7  |

| 3. Appearance size                          | 8  |

| 4. Pin definition                           | 9  |

| 5. Schematic diagram                        | 11 |

| 6. Design guidance                          | 12 |

| 6.1. Module application guide circuit       | 12 |

| 6.2. Power supply                           | 12 |

| 6.3. GPIO level conversion                  | 12 |

| 7. Reflow soldering graph                   | 13 |

| 8. Product related model                    | 14 |

| 9. Description of the firmware program mode | 14 |

| 10. Product packaging information           | 15 |

| 11. Contact US                              | 15 |

| Disclaimer and copyright notice             | 16 |

| Notice                                      | 16 |

#### 1. Product overview

VC-02 is a low-cost pure offline speech recognition module developed by Shenzhen Ai-Thinker Technology Co., Ltd. The module uses the voice chip US516P6 launched by Unisound, and continuously optimizes and innovates algorithms in speech recognition technology. The offline recognition algorithm and chip architecture are deeply integrated to provide customers with ultra-low-cost offline speech recognition solutions. It can be widely and quickly applied to smart home, all kinds of smart small household appliances, 86 boxes, toys, lamps and other products that need voice control.

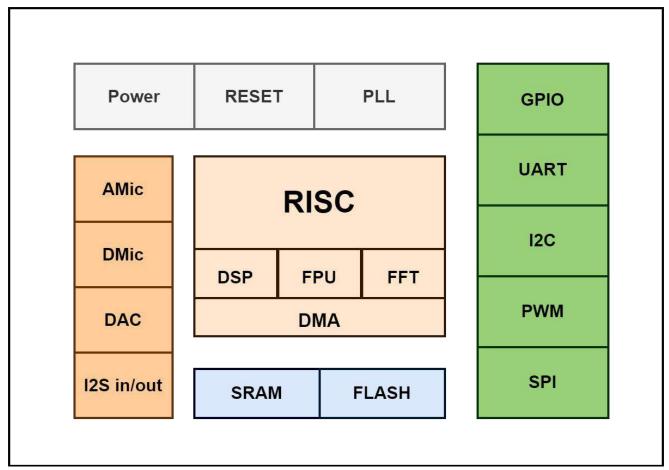

The US516P6 chip uses a 32-bit RSIC architecture core and incorporates a DSP instruction set specifically for signal processing and speech recognition, an FPU arithmetic unit that supports floating-point operations, and an FFT accelerator.

VC-02 supports offline identification of 150 local instructions, RTOS lightweight system, rich peripheral interfaces, and simple and friendly custom tools.

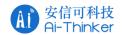

Figure 1 Main chip architecture diagram

#### 1.1. Characteristics

#### ■ Kernel

- ✓ 32bit RISC core, running at 240MHz

- ✓ Support DSP instruction set and FPU floating-point operation Unit

- ✓ FFT Accelerator: Support 1024-point complex FFT/IFFT operations, or 2048-point real FFT/IFFT operations

- ✓ Unisound customized speech algorithm operator

#### **■** Storage

- ✓ Built-in 242KB high-speed SRAM

- ✓ Built-in 2MB FLASH

#### ■ Audio input and output

- ✓ Supports 1 analog Mic input,  $SNR \ge 94dB$

- ✓ Support 4-channel digital Mic input

- ✓ Support dual-channel DAC output

- ✓ Supports I2S input/output

#### ■ Power supply and clock

- ✓ Support 3.6 V-5V Range Power Input

- ✓ Built-in 5V to 3.3V,3.3V to 1.2V LDO power the chip

- ✓ RC 12MHz clock source and PLL locked loop clock source

- ✓ Built-in POR(Power on Reset), low voltage detection and watchdog

#### Peripheral

- ✓ All GPIOs can be configured as external interrupt input and wake-up source

- ✓ 1 full-duplex UART with a maximum rate of 3Mbps.

- ✓ Support SPI, I2C, ADC, PWM interface

### ■ SDK

- ✓ Provides complete RTOS-based SDK

- ✓ Support fast and convenient UART, I2C and other control protocol development

# 2. Main parameters

**Table 1 Description of the main parameters**

| Model                            | VC-02                                           |  |

|----------------------------------|-------------------------------------------------|--|

| Package                          | SMD-20                                          |  |

| Size                             | 18*17*3.2 (± 0. 2) mm                           |  |

| Working<br>temperature           | -40 °C ~ 85 °C                                  |  |

| Storage environment              | -40 °C ~ 125 °C, <90% RH                        |  |

| Power supply                     | Supply Voltage 3.6 V-5 V, Supply Current> 500mA |  |

| Interfaces UART/I2C/PWM/SPI/GPIO |                                                 |  |

| Ю                                | 10                                              |  |

| <b>UART Rate</b>                 | Default 115200 bps                              |  |

| SPI Flash                        | 2MB (built-in)                                  |  |

## 2.1. Static requirements

VC-02 module is an electrostatic sensitive device that requires special precautions during handling.

Figure 2 ESD anti-static diagram

### 2.2. Electrical characteristics

**Table 2 Electrical Characteristics Table**

| Parameters                               | Conditions  | Min.<br>value | Typical value | Max.<br>value | Unit |

|------------------------------------------|-------------|---------------|---------------|---------------|------|

| Supply voltage                           | VCC         | 3.6           | -             | 5             | V    |

| Analog module power supply               | AVDD        | -             | 3.3           | -             | V    |

| Built-in LDO digital module power supply | LDO33DO     | -             | 3.3           | -             | V    |

| Core operating voltage                   | LDO12O      | -             | 1.2           | -             | V    |

| IO                                       | US_SPK_MUTE | -0.047        | -             | 3.3           | V    |

# 2.3. Power consumption

The following power consumption data are measured based on a 5V power supply and an ambient temperature of 25°C.

■ In the configuration of the speaker and microphone under the measured active state VC-02 power consumption.

**Table 3 Power consumption table**

| Mode                                                           | Min.<br>value | Average | Max.<br>value | Unit |

|----------------------------------------------------------------|---------------|---------|---------------|------|

| Active (response broadcast), the command word "turn on the air | 56.1          | 115.1   | 232           | mA   |

| Standby status                                                 | 55.7          | 56.1    | 56.6          | mA   |

| Hibernation state                                              | 0.6           | -       | 0.7           | mA   |

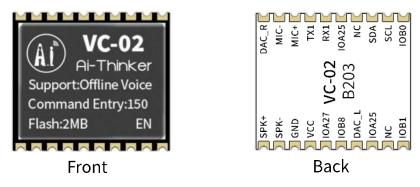

# 3. Appearance size

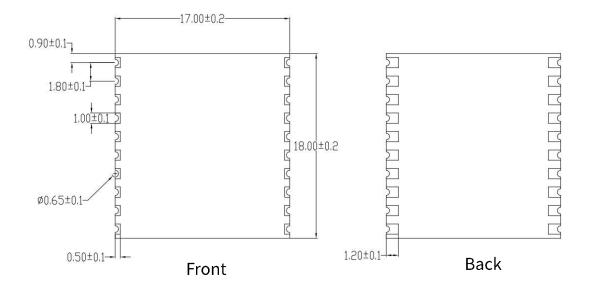

Figure 3 Module appearance diagram (For reference only)

**Figure 4 Module Size**

### 4. Pin definition

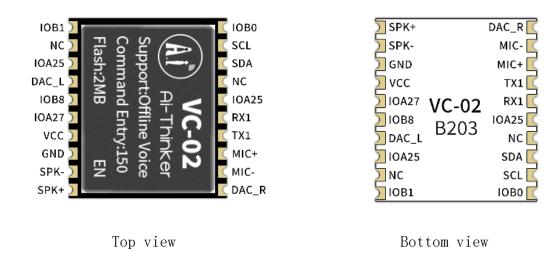

The VC-02 module has a total of 20 pins, As shown in below pin diagram, the pin function definition table is the interface definition.

Figure 5 Module pin diagram

**Table 4 Pin function definition table**

| Foot sequence | Name  | Function description                                                       |  |

|---------------|-------|----------------------------------------------------------------------------|--|

| 1             | DAC_R | Reserved R-channel audio output. This function is not currently supported. |  |

| 2             | MIC-  | MIC-Input                                                                  |  |

| 3             | MIC+  | MIC + input                                                                |  |

| 4             | TX1   | GPIO_B6/UART1_TXD,3.3V level                                               |  |

| 5             | RX1   | GPIO_B7/UART1_RXD,3.3V level                                               |  |

| 6             | IOA25 | IO/ADC4/SPI_MISO                                                           |  |

| 7             | NC    | Hanging                                                                    |  |

| 8             | SDA   | GPIO_B3/I2C_SDA/TIM4_PWM,3.3V level                                        |  |

| 9             | SCL   | GPIO_B2/I2C_SCL/TIM3_PWM,3.3V level                                        |  |

| 10            | IOB0  | IO/UART1_TXD/I2C_SCL/TIM3_PWM                                              |  |

| 11            | IOB1  | IO/UART1_RXD/I2C_SDA/TIM4_PWM                                              |  |

| 12            | NC    | Hanging                                                                    |  |

| 13            | IOA26 | IO/ADC5/SPI_CLK                                                            |  |

| 14            | DAC_L | Reserved audio L-channel output. This function is not currently supported. |  |

| 15            | IOB8  | IO/Virtual Software UART-TX(Log Output Pin)                                |  |

| 16            | IOA27 | IO/US_SPIM_MOSI                                                            |  |

| 17            | VCC   | 3.6-5V power input                                                         |  |

| 18            | GND   | GND ground                                                                 |  |

| 19            | SPK-  | SPK-8 Ω 2W                                                                 |  |

| 20            | SPK + | SPK +8 Ω 2W                                                                |  |

# 5. Schematic diagram

Figure 6 Module schematic diagram

## 6. Design guidance

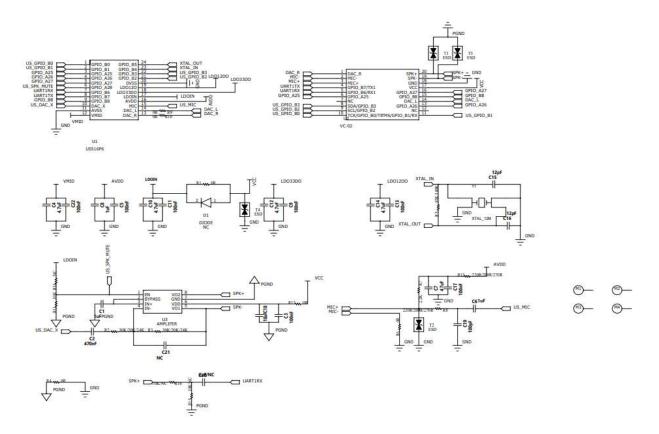

### 6.1. Module application guide circuit

(>= 500mA, it is recommended to use DC-DC or LDO for independent power supply)

Figure 7 Application circuit diagram

### 6.2. Power supply

- Recommended 3.6-5V voltage, peak current above 500mA.

- It is recommended to use LDO for power supply; if you use DC-DC, it is recommended to control the ripple within 50mV.

- The DC-DC power supply circuit suggests that the position of the dynamic response capacitor can be optimized when the load changes greatly.

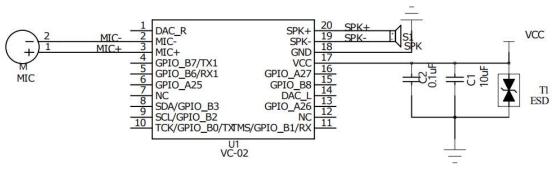

#### 6.3. GPIO level conversion

- Some IO ports are drawn out from the periphery of the module. If you need to use it, it is recommended to connect a 10-100 ohm resistor in series on the IO port. This can suppress overshoot and make the level on both sides more stable. It helps both EMI and ESD.

- For the special IO port to be pulled up and down, refer to the instructions in the specification, which will affect the startup configuration of the module.

- The IO port of the module is 3.3V. If the master control does not match the IO port level of the module, a level conversion circuit needs to be added.

- If the IO port is directly connected to the peripheral interface, or the terminal such as the pin, it is recommended to reserve the ESD device near the terminal.

**Figure 8 Level Conversion Circuit**

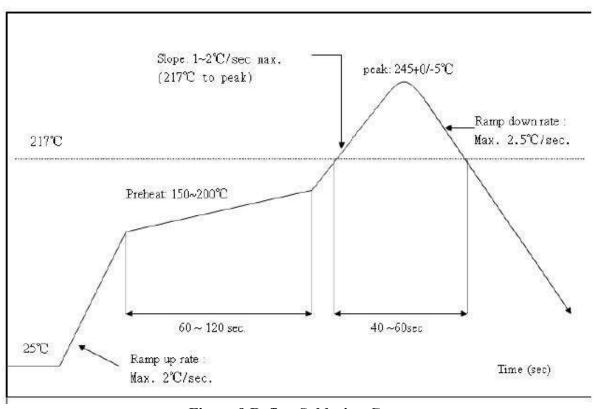

# 7. Reflow soldering graph

Figure 9 Reflux Soldering Curve

### 8. Product related model

**Table 6 Product related model list**

| Model                                                    | Power Supply    | Package | Size                | Default communication interface |

|----------------------------------------------------------|-----------------|---------|---------------------|---------------------------------|

| VC-01                                                    | 3.6-5V, I>500mA | SMD-24  | 25.5*24*3.2(±0.2)mm | UART1                           |

| VC-02                                                    | 3.6-5V, I>500mA | SMD-20  | 18*17*3.2(±0.2)mm   | UART1                           |

| VC-01-Kit                                                | 5V, I>500mA     | DIP-19  | 42.2*35.6(±0.2)mm   | UART1                           |

| VC-02-Kit                                                | 5V, I>500mA     | DIP-19  | 42.2*35.6(±0.2)mm   | UART1                           |

| Product related information: https://docs.ai-thinker.com |                 |         |                     |                                 |

# 9. Description of the firmware program mode

VC-02 has two methods for firmware upgrade , JTAG debugger program and serial port program.

- JJTAG debugger uses VC series dedicated JTAG debugger, Jlink series debugger are not supported, The firmware file name being used is:uni app release.bin

- Serial port program is USB program mode (module requires external TTL to USB module access to TX1 and RX1), the firmware file name being used must be: uni\_app\_release\_update.bin (cannot rename for 'uni\_app\_release.bin'), make sure to use the "build.sh update" instruction to compile.

# 10. Product packaging information

The VC-02 module adopts tape packaging, 800pcs/reel. As shown in the following figure:

Figure 10 Packaging tape drawing

### 11.Contact US

<u>Ai-Thinker official website</u> <u>Office forum</u> <u>Develop DOCS</u>

<u>LinkedIn</u> <u>Tmall shop</u> <u>Taobao shop</u> <u>Alibaba shop</u>

Technical support email: support@aithinker.com

Domestic business cooperation: sales@aithinker.com

Overseas business cooperation: overseas@aithinker.com

Company Address: Room 403,408-410, Block C, Huafeng Smart Innovation Port, Gushu 2nd Road, Xixiang, Baoan District, Shenzhen.

Tel: 0755-29162996

Wechat mini program

Wechat official account

### Disclaimer and copyright notice

The information in this article, including the URL address for reference, is subject to change without notice.

The document is provided "as is" without any guarantee responsibility, including any guarantee for merchantability, suitability for a specific purpose, or non-infringement, and any guarantee mentioned elsewhere in any proposal, specification or sample. This document does not bear any responsibility, including the responsibility for infringement of any patent rights arising from the use of the information in this document. This document does not grant any license for the use of intellectual property rights in estoppel or other ways, whether express or implied.

The test data obtained in the article are all obtained from Ai-Thinker's laboratory tests, and the actual results may vary slightly.

All brand names, trademarks and registered trademarks mentioned in this article are the property of their respective owners, and it is hereby declared.

The final interpretation right belongs to Shenzhen Ai-Thinker Technology Co.,Ltd.

### **Notice**

Due to product version upgrades or other reasons, the contents of this manual may be changed.

Shenzhen Ai-Thinker Technology Co.,Ltd. reserves the right to modify the contents of this manual without any notice or prompt.

This manual is only used as a guide. Shenzhen Ai-Thinker Technology Co.,Ltd. makes every effort to provide accurate information in this manual. However, Shenzhen Ai-Thinker Technology Co.,Ltd. does not guarantee that the contents of the manual are completely free of errors. All statements and information in this manual and the suggestion does not constitute any express or implied guarantee.