#

## Digitally Controlled CCFL Backlight Power Supplies

### General Description

The MAX1610/MAX1611 are fully integrated, highefficiency drivers for cold-cathode fluorescent lamps (CCFLs). They operate from a 4.5V to 26V power source. An on-board, high-switching-frequency power MOSFET reduces external component count and magnetics size. The MAX1610/MAX1611 protect against open or shorted lamps. The CCFL can be driven from an isolated transformer secondary winding to improve efficiency and avoid flicker at dim tube settings. Brightness is adjusted by scaling the lamp current, or by operating with a fixed lamp current and chopping the CCFL on and off at a rate faster than the eye can detect.

The MAX1610's digital inputs increment, decrement, or clear an internal, 5-bit up/down counter, which sets CCFL brightness. The MAX1611 uses a System Management Bus (SMBus) 2-wire serial interface to directly set CCFL brightness. Both devices include micropower shutdown and a linear regulator that eliminates the need for a separate logic supply. The digital interface remains active in shutdown, preserving the brightness setting.

## **Applications**

Notebook/Laptop Computers Point-of-Sale Terminals Portable Medical Equipment Instrument Displays

#### **Features**

MAX1610/MAX1611

- ♦ Direct Digital Control of CCFL Brightness

- ♦ Low Supply Current: 3mA Max Operating 20µA Max Shutdown

- ♦ Low-Voltage Operation, Down to 4.5V

- Internal 26V, 0.7Ω Power Switch

- Protection Against Open or Shorted Lamps

- ♦ Supports Isolated Transformer Secondary Winding

- ♦ SMBus Serial Interface (MAX1611)

- ♦ No Flicker at Low Brightness (internal 280Hz) current chopping)

- ♦ High Power-to-Light Efficiency

- ♦ Selectable 290kHz/145kHz Switching Frequency

- ♦ Oscillator SYNC Input

- ♦ 16-Pin Narrow SO Package

## Ordering Information

| PART       | TEMP. RANGE  | PIN-PACKAGE  |

|------------|--------------|--------------|

| MAX1610CSE | 0°C to +70°C | 16 Narrow SO |

| MAX1611CSE | 0°C to +70°C | 16 Narrow SO |

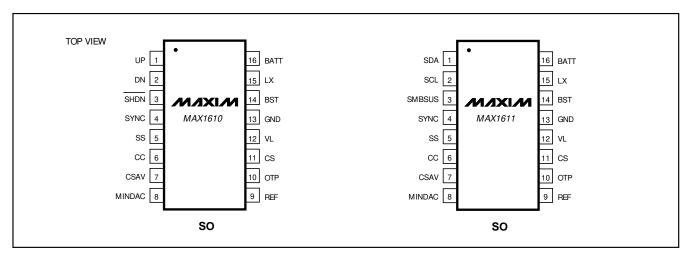

## Pin Configurations

### **ABSOLUTE MAXIMUM RATINGS**

| BATT to GND                      |                       |

|----------------------------------|-----------------------|

| BST to GND                       | 0.3V to 30V           |

| BST to LX                        | 0.3V to 6V            |

| LX to GND                        | 0.6V to (BATT + 0.3V) |

| VL to GND                        | 0.3V to 6V            |

| CS, CSAV, CC, SYNC, REF, MINDAC, |                       |

| SS, OTP to GND                   | 0.3V to (VL + 0.3V)   |

| SHDN, UP, DN to GND              | 0.3V to 6V            |

| SMBSUS, SDA, SCL to GND          | 0.3V to 6V            |

| BATT, LX Current                               | 1A           |

|------------------------------------------------|--------------|

| SDA Current                                    |              |

| VL Current                                     | 50mA         |

| Continuous Power Dissipation ( $T_A = +70$ °C) |              |

| SO (derate 8.70mW/°C above +70°C)              | 696mW        |

| Operating Temperature Range                    |              |

| MAX1610CSE/MAX1611CSE                          | 0°C to +70°C |

| Storage Temperature Range                      |              |

| Lead Temperature (soldering, 10sec)            | +300°C       |

|                                                |              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(TA = 0°C to +70°C, BATT = 8.2V, MINDAC = 0V, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                       | CONDITIONS         | MIN  | TYP | MAX  | UNITS |  |

|-------------------------------------------------|--------------------|------|-----|------|-------|--|

| SUPPLY AND REFERENCE                            |                    |      |     |      | •     |  |

| BATT Input Voltage Range                        |                    | 4.75 |     | 26   | V     |  |

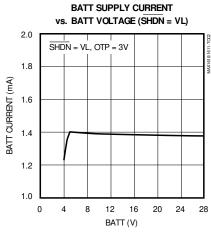

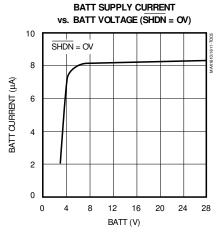

| BATT Quiescent Supply Current,<br>Operate Mode  | BATT = 25V         |      | 1.5 | 3    | mA    |  |

| BATT Quiescent Supply Current,<br>Shutdown Mode |                    |      | 10  | 20   | μА    |  |

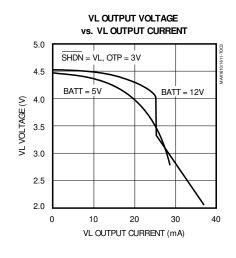

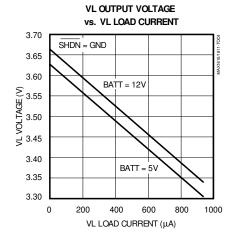

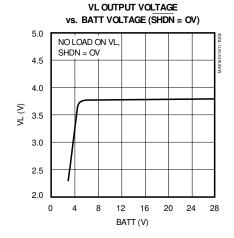

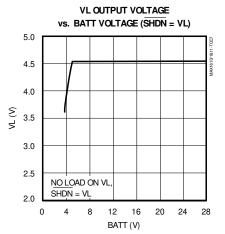

| VL Output Voltage, Operate Mode                 | 4.75V < BATT < 26V | 4.25 | 4.5 | 4.75 | V     |  |

| VL Output Voltage, Shutdown Mode                |                    | 3.0  | 3.6 | 4.75 | V     |  |

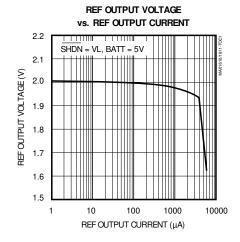

| REF Output Voltage                              | No load            | 1.92 | 2.0 | 2.08 | V     |  |

| REF Load Regulation                             | ISOURCE = 100μA    |      | 6   | 20   | mV    |  |

| SWITCHING REGULATOR                             |                    |      |     |      |       |  |

| BATT-to-LX Switch On-Resistance                 | BST - LX = 4.1V    |      | 0.7 | 1.0  | Ω     |  |

| LX Switch Off-Leakage Current                   |                    |      |     | 10   | μΑ    |  |

| Ossillator Francisco                            | SYNC = REF         | 250  | 290 | 330  | 1.11= |  |

| scillator Frequency                             | SYNC = GND         | 125  | 145 | 165  | kHz   |  |

| Oscillator SYNC Pin Synchronization Range       |                    | 240  |     | 350  | kHz   |  |

| SYNC High Pulse Width                           |                    | 200  |     |      | ns    |  |

| SYNC Low Pulse Width                            |                    | 200  |     |      | ns    |  |

| SYNC Input Current                              | SYNC = GND or VL   | -1   |     | 1    | μΑ    |  |

| SYNC Input Low Voltage                          |                    |      |     | 0.5  | V     |  |

| SYNC Input High Voltage                         |                    | 4.0  |     |      | V     |  |

| Power-Switch Maximum Duty Cycle                 | SYNC = REF         | 89   | 91  |      | %     |  |

| SS Source Current                               | SS = GND           | 2.5  | 4.0 | 5.5  | μΑ    |  |

| SS Sink Current                                 | SS = 0.5V          | 2    |     |      | mA    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = 0^{\circ}C \text{ to } + 70^{\circ}C, \text{ BATT} = 8.2 \text{V}, \text{ MINDAC} = 0 \text{V}, \text{ unless otherwise noted}. \text{ Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                                   | CON                     | DITIONS                         | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------|-------------------------|---------------------------------|-----|-----|-----|-------|

| DAC AND ERROR AMPLIFIER                                     |                         |                                 | •   |     |     |       |

| DAC Resolution                                              | Guaranteed monotor      | nic                             | 5   |     |     | Bits  |

| MINDAC Input Voltage Range                                  |                         |                                 |     |     | 1   | V     |

| MINDAC Input Bias Current                                   |                         |                                 | -1  |     | 1   | μΑ    |

| MINDAC Digital PWM Threshold                                |                         |                                 |     | 3   |     | V     |

| CSAV Input Voltage Range                                    |                         |                                 | 0   |     | 1.0 | V     |

| CSAV Degulation Point                                       | D/A at full scale       |                                 | 232 | 247 | 260 | mV    |

| CSAV Regulation Point                                       | D/A at 1LSB             |                                 |     | 12  |     | IIIV  |

| CSAV Input Bias Current                                     |                         |                                 | -5  |     | 5   | μΑ    |

| CSAV to CC Voltage-to-Current Converter<br>Transconductance | CC = 2V, CSAV = 1V      | CC = 2V, CSAV = 1V, D/A at 1LSB |     | 85  |     | μmho  |

| CC Sink Current                                             | CC = 2V, CSAV = 1V      | , D/A at 1LSB                   |     | 80  |     | μΑ    |

| CC Source Current                                           | CC = 2V, CSAV = 0V      | , D/A at full scale             |     | 20  |     | μΑ    |

| OPEN AND SHORTED TUBE PROTECTIO                             | N                       |                                 |     |     |     |       |

| OTP Voltage Trip Point                                      | Referred to REF         | OTP rising                      | -20 |     | 20  | mV    |

| OTP Input Bias Current                                      | GND < OTP < VL          |                                 | -1  |     | 1   | μΑ    |

| CS Overcurrent Cutoff Threshold                             |                         |                                 |     | 500 |     | mV    |

| MAX1610 LOGIC LEVELS                                        | -1                      |                                 |     |     |     |       |

| SHDN, UP, DN Input Low Voltage                              |                         |                                 |     |     | 0.8 | V     |

| SHDN, UP, DN Input High Voltage                             |                         |                                 | 2.4 |     |     | V     |

| SHDN, UP, DN Input Bias Current                             |                         |                                 | -1  |     | 1   | μΑ    |

| MAX1611 LOGIC LEVELS                                        |                         |                                 |     |     |     |       |

| SMBSUS, SDA, SCL Input Low Voltage                          |                         |                                 |     |     | 0.8 | V     |

| SMBSUS, SDA, SCL Input High Voltage                         |                         |                                 | 2.2 |     |     | V     |

| SMBSUS, SDA, SCL Input Bias Current                         |                         |                                 | -1  |     | 1   | μА    |

| SDA Output Low Sink Current                                 | V <sub>SDA</sub> = 0.6V |                                 | 6   |     |     | mA    |

### **TIMING CHARACTERISTICS—MAX1610**

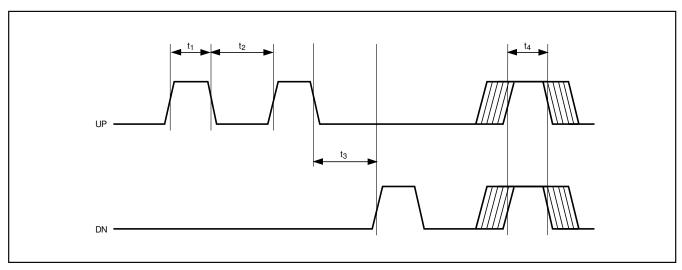

(Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER               | SYMBOL         | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------|----------------|------------|-----|-----|-----|-------|

| UP, DN Pulse Width High | t <sub>1</sub> |            | 1   |     |     | μs    |

| UP, DN Pulse Width Low  | t <sub>2</sub> |            | 1   |     |     | μs    |

| UP, DN Pulse Separation | t <sub>3</sub> |            | 1   |     |     | μs    |

| Counter Reset Time      | t <sub>4</sub> |            | 1   |     |     | μs    |

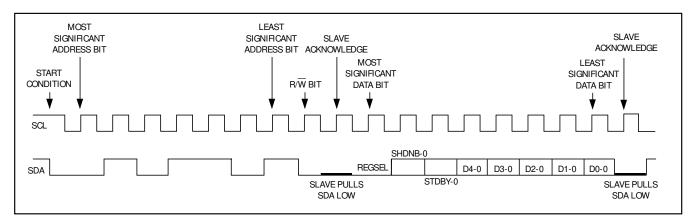

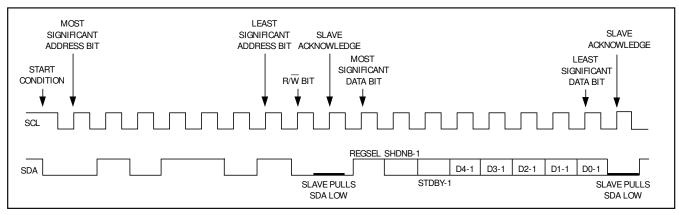

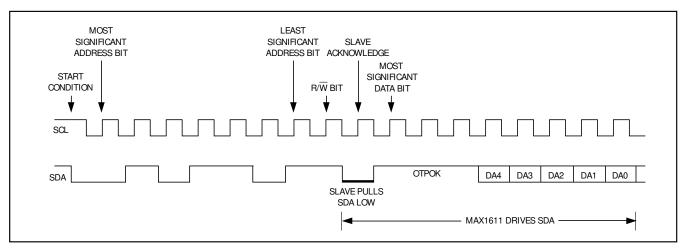

### **TIMING CHARACTERISTICS—MAX1611**

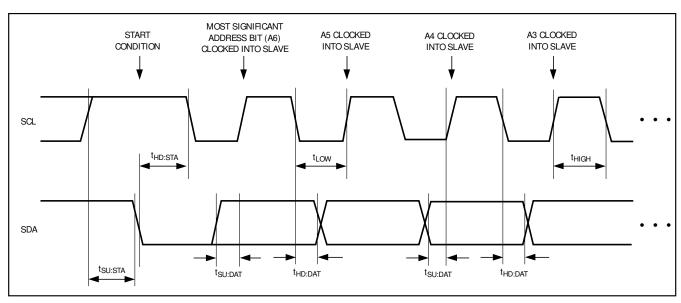

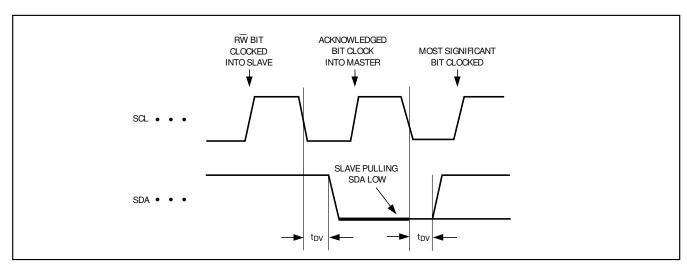

(Figures 2 and 3,  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                                                          | SYMBOL         | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------------------|----------------|------------|-----|-----|-----|-------|

| SCL Serial Clock High Period                                       | thigh          |            | 4   |     |     | μs    |

| SCL Serial Clock Low Period                                        | tLOW           |            | 4.7 |     |     | μs    |

| SCL, SCA Rise Time                                                 | t <sub>R</sub> | (Note 1)   |     |     | 1   | μs    |

| SCL, SDA Fall Time                                                 | tF             | (Note 1)   |     |     | 0.3 | μs    |

| Start Condition Setup Time                                         | tsu:sta        |            | 4.7 |     |     | μs    |

| Start Condition Hold Time                                          | thd:Sta        |            | 4   |     |     | μs    |

| SDA Valid to SCL Rising Edge<br>Setup Time, Slave Clocking in Data | tsu:DAT        |            | 500 |     |     | ns    |

| SCL Falling Edge to SDA<br>Transition                              | thd:dat        | (Note 1)   | 0   |     |     | ns    |

| SCL Falling Edge to SDA Valid,<br>Reading Out Data                 | tDV            |            |     |     | 1   | μs    |

Note 1: Guaranteed by design.

## Typical Operating Characteristics

(T<sub>A</sub> = +25°C, unless otherwise noted.)

Pin Description

| PIN     |         |        |                                                                                                                                                                                            |

|---------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1610 | MAX1611 | NAME   | FUNCTION                                                                                                                                                                                   |

| 1       | _       | UP     | Logic-Level Input. A rising edge on UP increments the 5-bit counter for the 5-bit DAC. UP = DN = 1 presets the counter to mid-scale.                                                       |

| _       | 1       | SDA    | System Management Bus Serial Data Input and Open-Drain Output                                                                                                                              |

| 2       | _       | DN     | Logic-Level Input. A rising edge on DN decrements the 5-bit counter for the 5-bit DAC. UP = DN = 1 presets the counter to mid-scale.                                                       |

| _       | 2       | SCL    | System Management Bus Serial Clock Input                                                                                                                                                   |

| 3       | _       | SHDN   | Logic-Level Shutdown Input Pin. Applying a logic low to SHDN places the chip in a low-supply-current shutdown mode.                                                                        |

| _       | 3       | SMBSUS | System Management Bus Suspend Mode Input. SMBSUS Selects one of two chip-configuration settings, which are preprogrammed serially.                                                         |

| 4       | 4       | SYNC   | Oscillator Synchronization Input. Tying SYNC to REF sets the oscillator frequency to 290kHz. Tying SYNC to GND or VL lowers the oscillator frequency to 145kHz.                            |

| 5       | 5       | SS     | Soft-Start Pin. A 4µA current source feeds the capacitor placed on SS. The voltage on this pin limits the peak current in the switch. When the lamp is turned off, SS pulls to GND.        |

| 6       | 6       | CC     | Output of the Voltage-to-Current Converter; Input to the PWM Comparator, which sets the current limit. A capacitor placed at CC sets the current-regulator-loop bandwidth.                 |

| 7       | 7       | CSAV   | Input to the Voltage-to-Current Converter, which averages the voltage on CSAV using the capacitor on CC.                                                                                   |

| 8       | 8       | MINDAC | The voltage at MINDAC sets the DAC's minimum-scale output voltage. Tying MINDAC to VL enables the internal 280Hz current-chopping mode.                                                    |

| 9       | 9       | REF    | 2.0V Reference Output. Bypass with 0.1μF to GND.                                                                                                                                           |

| 10      | 10      | ОТР    | Open-Tube Protection Comparator. As long as OTP exceeds the reference voltage, the N-channel BATT-to-LX switch is forced off.                                                              |

| 11      | 11      | CS     | Low-Side Current-Sense Input. The current-mode regulator terminates the switch cycle when the voltage at CS exceeds REF - CC.                                                              |

| 12      | 12      | VL     | Output of the Internal Linear Regulator. VL can be overdriven by a voltage greater than 4.75V to operate the chip from $+5V\pm5\%$ , and to conserve power. Bypass with $0.1\mu F$ to GND. |

| 13      | 13      | GND    | System Ground                                                                                                                                                                              |

| 14      | 14      | BST    | Power Input to the High-Side Gate Driver, which switches the internal N-channel MOSFET on and off.                                                                                         |

| 15      | 15      | LX     | Ground Connection for the Internal High-Side Gate Driver; source-connection point for the internal N-channel MOSFET                                                                        |

| 16      | 16      | BATT   | 4.5V to 25V Battery-Voltage Input Point. Connects to the internal N-channel power MOSFET's drain, and to the input of the internal linear regulator that powers the chip.                  |

Figure 1. MAX1610 UP and DN Signal Timing

Figure 2. MAX1611 SMB Serial-Interface Timing—Address

Figure 3. MAX1611 SMB Serial-Interface Timing—Acknowledge

### \_Detailed Description

#### **Getting Started**

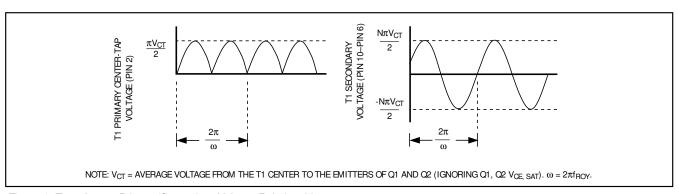

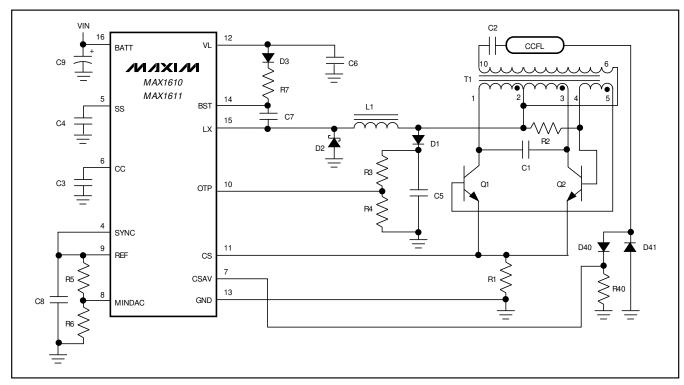

A cold-cathode fluorescent lamp (CCFL) has two terminals. For the CCFL to emit light, the two lamp terminals must be driven with a high-voltage (approximately 550V AC RMS) and high-frequency (approximately 45kHz) sine wave. The MAX1610/MAX1611 use a varying DC input voltage to create this high-voltage, high-frequency sine-wave drive. To select the correct component values for the MAX1610/MAX1611 circuit, several CCFL parameters and the minimum DC input voltage must be specified; these are listed in Table 1.

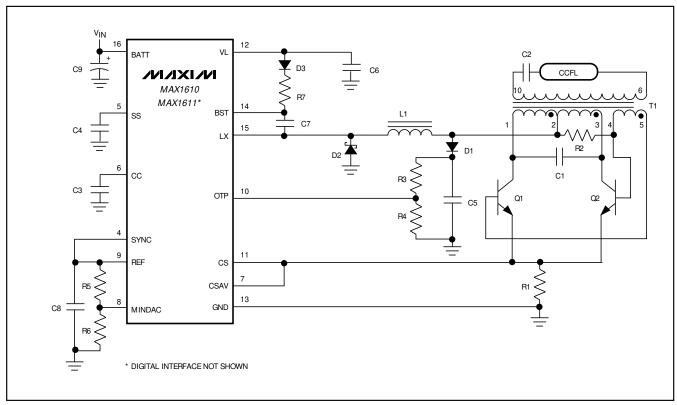

Table 3 shows the recommended component values to use with the circuit of Figure 4, depending on the particular CCFL parameters. The C2 values in Table 3 have been selected such that the normal operating voltage on the secondary of T1 is as close as possible to the CCFL strike voltage (where the strike voltage (Vs) is assumed to be approximately 1.8 times the CCFL operating voltage (VL)).

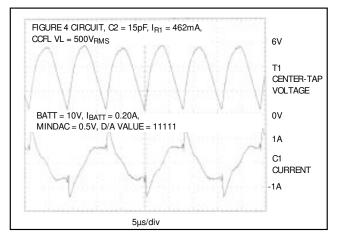

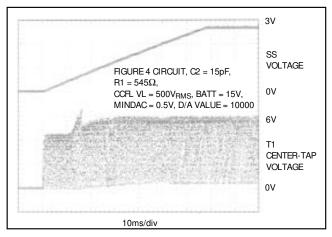

Components T1, C1, R2, Q1, and Q2 form a Royer oscillator. A Royer oscillator is a resonant tank circuit that oscillates at a frequency dependent on C1, the primary magnetizing inductance of T1 (LP), and the impedance seen by the T1 secondary. The MAX1610/MAX1611 regulate the current fed into the Royer oscillator by sensing the voltage on R1. For a given current through the Royer oscillator (IR1), the power delivered to the CCFL depends on the Royer oscillator frequency. The R1 values in Table 3 have been selected to ensure that the power into the CCFL

does not exceed its maximum rating, despite T1, C1, and C2 component-value variations. The Royer oscillator waveforms for the circuit of Figure 4 are shown in Figures 5 and 6.

#### Analog Circuitry

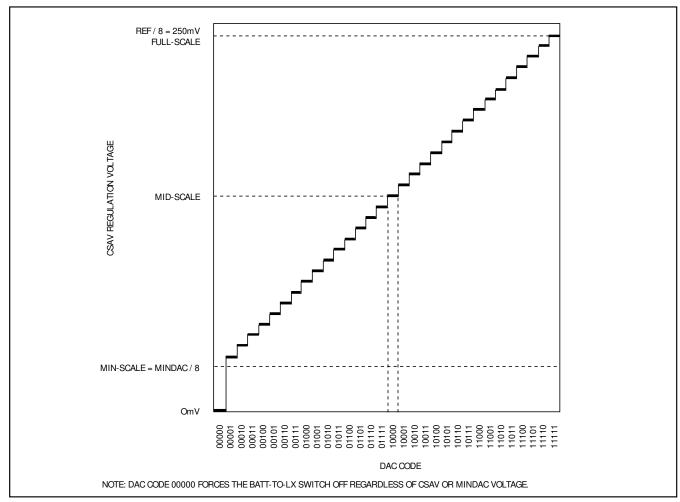

The MAX1610/MAX1611 maintain fixed CCFL brightness with varying input voltages on BATT by regulating the current fed into the Royer oscillator. This current is sensed via resistor R1 between CSAV and GND. An internal switch from BATT-to-LX pulse-width modulates at a fixed frequency to servo the CSAV pin to its regulation voltage. The CSAV regulation voltage can be adjusted via the digital interface to set CCFL brightness. The MAX1610 and MAX1611 differ only in the digital interface they use to adjust the internal 5-bit digital-to-analog converter (DAC) that sets the CSAV regulation voltage. The minimum-scale (min-scale) CSAV regulation voltage is resistor adjustable using the MIN-DAC pin, setting the minimum CCFL brightness. The D/A setting at MAX1610/MAX1611 power-up is preset to mid-scale (10000 binary) (Figure 7).

#### MINDAC Sets the Minimum Scale

The MINDAC pin sets the lowest CCFL brightness level. The voltage at MINDAC is divided by eight, and sets the minimum CSAV regulation voltage. For example, in the circuit of Figure 4, R5 (150k $\Omega$ ) and R6 (51k $\Omega$ ) form a resistor divider from REF, which sets MINDAC to 507mV (REF = 2.0V). This sets a minimum CSAV regulation voltage of 63mV with a full-scale CSAV regulation voltage of 247mV.

Figure 4. Typical Floating-Lamp Application Circuit

## **Table 1. Necessary CCFL Specifications**

| SPECIFICATION                                      | UNITS             | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                   |

|----------------------------------------------------|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCFL Minimum Strike Voltage ("Kick-Off Voltage")   | V <sub>RMS</sub>  | VS     | Although CCFLs typically operate at 550V <sub>RMS</sub> , a higher voltage is required initially to light up the tube.                                                                                                                                                        |

| CCFL Typical Operating Voltage ("Lamp Voltage")    | V <sub>RMS</sub>  | VL     | Once a CCFL has been struck, the voltage required to maintain light output falls to approximately $550V_{RMS}$ . Small tubes may operate on as little as $250V_{RMS}$ . The operating voltage of the CCFL stays relatively constant, even as the tube's brightness is varied. |

| CCFL Maximum Operating<br>Current ("Lamp Current") | mA <sub>RMS</sub> | ΙL     | The maximum root-mean-square AC current through a CCFL is almost always 5mA <sub>RMS</sub> . No DC current is allowed through any CCFL.                                                                                                                                       |

| CCFL Maximum Frequency ("Lamp Frequency")          | kHz               | fL     | The maximum AC-lamp-current frequency.                                                                                                                                                                                                                                        |

| DC Power Source Minimum<br>Input Voltage           | V                 | Vmin   | The minimum DC input voltage to the MAX1610/MAX1611 circuit determines the turns ratio required for the DC-AC conversion transformer. Decreasing the minimum input voltage increases the size of the transformer required for a given output power.                           |

**Table 2. Typical Application Circuit Component Values**

### a) Resistors

#### **POWER TOLERANCE SYMBOL VALUE RATING** R1 1/8W (Note) ±1% 510Ω R2 ±10% 1/8W R3 $51k\Omega$ ±5% 1/16W R4 $8.2k\Omega$ 1/16W ±5% R5 $150 k\Omega$ 1/16W ±5% R6 $51k\Omega$ ±5% 1/16W R7 $20\Omega$ ±10% 1/16W

### b) Capacitors

| SYMBOL            | VALUE            | TOLER-<br>ANCE | WORKING<br>VOLTAGE | NOTES                             |

|-------------------|------------------|----------------|--------------------|-----------------------------------|

| C1                | 0.1μF            | ±20%           | ±25V               | δF ≤ 0.001 @1kHz                  |

| C2                | (Note 1)<br>(pF) | ±10%           | ±3kV               | High voltage                      |

| C3, C5            | 27nF             | ±20%           | 25V                |                                   |

| C4, C6,<br>C7, C8 | 0.1μF            | -20%           | 25V                | Ceramic, larger values acceptable |

| C9                | 10μF             | -50%           | 35V                | Tantalum, low ESR                 |

### c) Other Components

| SYMBOL | DESCRIPTION                                                                                                                                            | GENERIC<br>PART | SURFACE-MOUNT<br>PART | MANUFACTURER |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------|

| Q1, Q2 | 1A NPN switching transistor,<br>V <sub>CEO</sub> ≥ 50V                                                                                                 | 2N2222A         | FMMT619, SOT23        | Zetex        |

| D1, D3 | 50mA silicon diode, V <sub>BR</sub> ≥ 40V                                                                                                              | 1N4148          | CMPD4448, SOT23       | Central      |

| D2     | 1A Schottky diode, V <sub>BR</sub> ≥ 30V                                                                                                               | 1N5818          | EC10QS04              | Nihon        |

| L1     | 100μH, 1A inductor                                                                                                                                     |                 | CDR125-101            | Sumida       |

| T1     | 6W Royer oscillator transformer, turns ratio 67:1, secondary (pins 10 and 6): primary (pins 1 and 3), primary magnetizing inductance (LP) of 44μH ±20% |                 | CTX110605             | Coiltronics  |

Note: Component values depend on lamp characteristics. See Table 3 to select values.

**Table 3. Selecting Circuit Values for Figure 4**

| VL                  | V <sub>L</sub> I <sub>L</sub> |      | Ca     | C2 R1               | VCT  | f <sub>ROY</sub> (kHz) |      |  |

|---------------------|-------------------------------|------|--------|---------------------|------|------------------------|------|--|

| (V <sub>RMS</sub> ) | (mA <sub>RMS</sub> )          | G2   | KI     | (V <sub>MAX</sub> ) | MIN  | TYP                    | MAX  |  |

| 250                 | 3                             | 22pF | 1.21Ω  | 3.63V               | 50.3 | 58.6                   | 71.8 |  |

| 250                 | 5                             | 43pF | 0.715Ω | 3.61V               | 43.3 | 49.7                   | 60.3 |  |

| 300                 | 3                             | 18pF | 1.18Ω  | 4.30V               | 52.1 | 61.0                   | 75.1 |  |

| 300                 | 5                             | 36pF | 0.681Ω | 4.14V               | 45.6 | 52.8                   | 64.7 |  |

| 450                 | 5                             | 20pF | 0.732Ω | 6.55V               | 51.1 | 59.7                   | 73.3 |  |

| 500                 | 5                             | 18pF | 0.715Ω | 7.17V               | 52.1 | 61.0                   | 75.1 |  |

| 550                 | 5                             | 18pF | 0.665Ω | 7.29V               | 52.5 | 61.8                   | 76.7 |  |

| 600                 | 5                             | 15pF | 0.698Ω | 8.41V               | 53.6 | 63.1                   | 78.1 |  |

Note: f<sub>ROY</sub> = Royer oscillator damped resonant oscillation frequency. T1 primary magnetizing inductance (Lp) = 44μH ±20%.

VCT = average voltage from the T1 center tap to the emitters of Q1 and Q2 (ignoring Q1, Q2 V<sub>CE,SAT</sub>).

C1 = 0.1μF ± 20%; C2 = ±10% tolerance; R1 = ±1% tolerance.

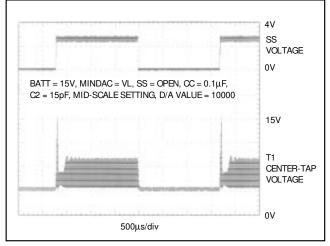

Figure 5. Royer Oscillator Typical Operating Waveforms for Circuit of Figure 4

Figure 6. Start-Up Waveforms for Circuit of Figure 4

Figure 7. CSAV Regulation Voltage Range

#### Open-Tube Protection (OTP)

Any real transformer used in a Royer oscillator will have a maximum-allowed secondary voltage. If the maximum-allowed secondary voltage is exceeded, the winding insulation can break down, leading to permanent transformer damage. The maximum-allowed secondary voltage can be exceeded either when the CCFL drive circuit is turned on without the CCFL being in place, or when the CCFL becomes disconnected during normal operation due to a mechanical failure. To protect against these fault conditions, use the OTP pin to sense the voltage on the transformer center tap (pin 2 of Figure 4). Whenever the voltage on OTP exceeds the REF reference voltage, the BATT-to-LX power switch is forced off.

For example, in Figure 4, the CTX110605 transformer has a maximum-allowed continuous secondary voltage of 1340VRMS. D1 and C5 detect the peak voltage on the center tap of T1. R3 and R4 determine the limit on the center tap peak voltage. The relationship between the voltage on the center tap of T1 and the secondary voltage is diagrammed in Figure 8. Neglecting the Q1/Q2 saturation voltage and the voltage on the R1 current-sense resistor yields Equation 1:

$$V_{CTPK} = \frac{V_{SEC}\sqrt{2}}{2N}$$

where  $V_{SEC}$  is the maximum root-mean-square voltage allowed on the secondary, N is the secondary-to-primary turns ratio, and  $V_{CTPK}$  is the peak voltage on the transformer center tap.

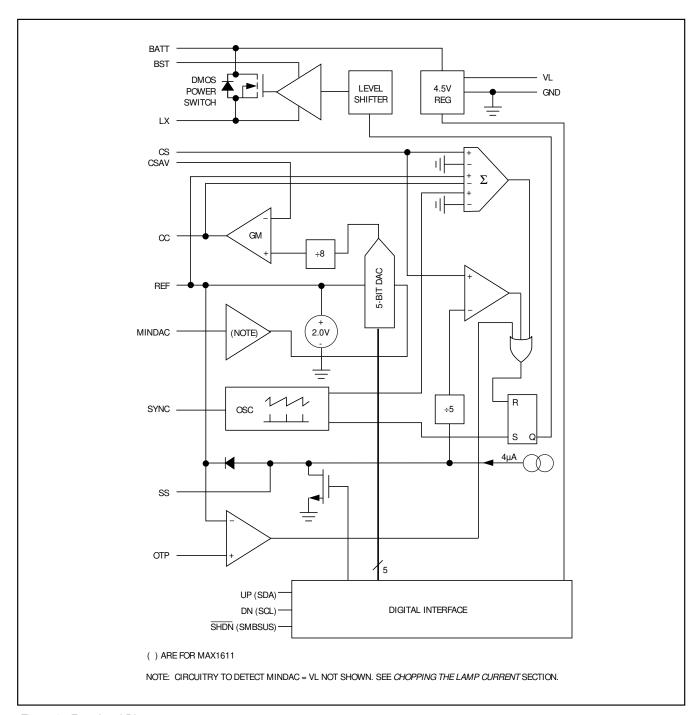

### Block Diagram of the Analog Section

Figure 9 shows a functional diagram of the analog circuitry in the MAX1610/MAX1611. The chips have identical analog circuitry, and differ only in their digital interface.

#### Loop-Compensation Capacitor (CC)

The BATT-to-LX switch turns on at fixed frequency, and turns off when the current-sense voltage on the CS pin exceeds CC - REF. As the CC pin voltage rises, the CS current limit rises as well. A transconductance amplifier compares the voltage on CSAV to the desired regulation voltage and outputs a current proportional to this error to the CC pin. A capacitor from CC to GND sets the bandwidth of this regulation loop, as shown in Equation 2:

$$BW = \frac{85}{2\pi C3}$$

where BW is the bandwidth of the CSAV regulation loop in kHz, and C3 is the capacitance from CC to GND in nF.

#### Soft Start (SS)

Soft start prevents the triggering of OTP upon power-up. Placing a capacitor from SS to GND soft starts the Royer oscillator by slowly raising the CS current-limit voltage. Internal circuitry pulls SS to GND during power-on reset, or whenever the lamp is turned off (DAC = 00000, shutdown mode, ON-1 = 0, or ON-0 = 0) (Figures 10 and 11). When SS is not pulled to GND, an internal  $4\mu A$  current sources into the capacitor at the SS pin. This pin is internally diode clamped to REF so that it rises to a maximum voltage of about 2.7V. Regardless of the voltage on CC, the CS current-sense voltage is never allowed to exceed the voltage on SS divided by 5.

#### Frequency Selection and Synchronization

The SYNC pin performs two functions: it sets the BATT-to-LX switching frequency, and it allows the BATT-to-LX switching frequency to be synchronized to an external oscillator. SYNC tied to GND or VL sets a 145kHz switching frequency; SYNC tied to REF sets a 290kHz

Figure 8. Transformer Primary/Secondary Voltage Relationship

Figure 9. Functional Diagram

Figure 10. MAX1611 Serial-Interface Single-Byte Write Example (REGSEL = 0)

Figure 11. MAX1611 Serial-Interface Single-Byte Write Example (REGSEL = 1)

switching frequency. Any rising edge on SYNC restarts a BATT-to-LX switch cycle by forcing the switch on.

## \_MAX1610 Digital Interface

The MAX1610 contains an internal 5-bit up/down counter that sets the value of the internal 5-bit DAC. At power-on, or when both the UP and DN pins are held high simultaneously, the 5-bit up/down counter is preset to 10000 binary, which corresponds to mid-scale. A rising edge on UP increments the 5-bit up/down counter. A rising edge on DN decrements the 5-bit up/down counter. The counter will not roll over on either underflow or overflow. For example, if the CCFL is at maximum intensity level, rising edges on UP will not change the output.

The  $\overline{SHDN}$  pin provides a way to lower the MAX1610 supply current to  $10\mu A$  without resetting the 5-bit up/down counter. With  $\overline{SHDN}=1$ , the MAX1610 operates normally with VL at 4.5V. When the BATT-to-LX power switch operates, an additional 3mA of current

(other than the supply current) is consumed through the BST pin, requiring VL to source at least 4.5mA of current. With  $\overline{SHDN}=0$ , all analog circuitry turns off, except for a coarse regulator that can source up to 500µA from VL. The coarse regulator preserves the state of the internal logic and keeps the digital interface active during shutdown ( $\overline{SHDN}=0$ ).

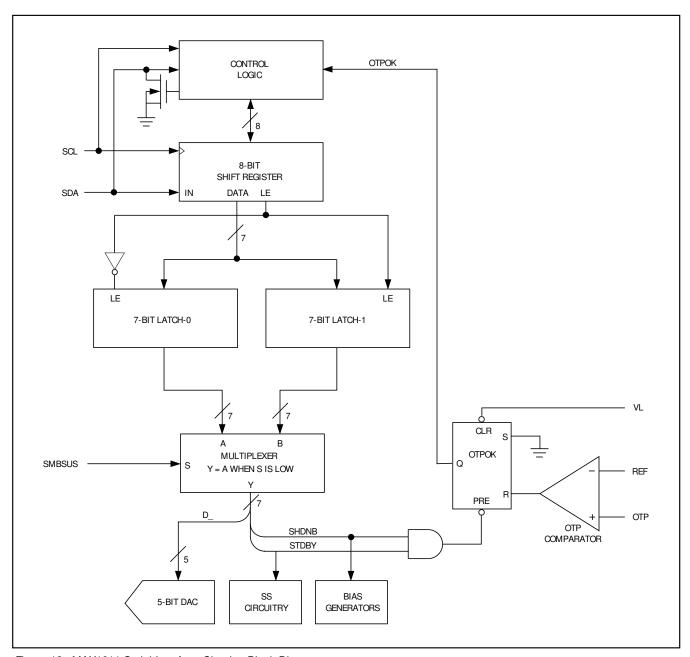

## MAX1611 Digital Interface

A single byte of data written over the Intel System Management Bus (SMBus™) controls the MAX1611. Figures 10 and 11 show example single-byte writes. The MAX1611 contains two 7-bit latches for storing configuration data. Only one of the 7-bit latches is active at a time. The MAX1611 responds only to its own address, 0101101 binary. The SMBSUS pin selects which of the two sets of configuration data is used. Figure 12 shows a schematic diagram of the MAX1611's digital circuitry. Notice that the SMBSUS pin selects which one of the

Figure 12. MAX1611 Serial-Interface Circuitry Block Diagram

Table 4. MAX1611 Configuration Byte with REGSEL = 0

| ВІТ | NAME    | POR<br>STATE* | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | REGSEL  | _             | Register Select. A zero in this bit writes the remaining seven bits into the 7-bit latch-0 (Figure 13).                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 6   | SHDNB-0 | 0             | Complete Shutdown. Pulling SMBSUS low with SHDNB-0 = 0 places the MAX1611 into a low-quiescent-current shutdown mode, with the reference off and the VL linear-regulator output switched to a low-current, coarse regulation mode. Pulling SMBSUS low with SHDNB-0 = 1 puts the MAX1611 into its normal operational mode, with the reference and internal VL linear regulator fully on. SHDNB-0 supersedes STDBY-0. As long as SHDNB-0 = 0 and SMBSUS = 0, it doesn't matter what STDBY-0 is; the MAX1611 still shuts down. |  |  |

| 5   | STDBY-0 | 0             | Standby, disables CCFL supply only. As long as SMBSUS stays low and STDBY-0 = 0, the internal power switch is kept off and SS is held shorted to GND; neither the internal reference nor the linear regulator is affected. With STDBY = 1 and SMBSUS low, the MAX1611 operates normally.                                                                                                                                                                                                                                    |  |  |

| 4   | D4-0    | 1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 3   | D3-0    | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 2   | D2-0    | 0             | DAC Input Data. With the SMBSUS pin low, bits D4-0 through D0-0 set the DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 1   | D1-0    | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 0   | D0-0    | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

<sup>\*</sup> Initial register state after power-up.

Table 5. MAX1611 Configuration Byte with REGSEL = 1

| BIT | NAME    | POR<br>STATE* | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | REGSEL  | _             | Register Select. A one in this bit writes the remaining seven bits into the 7-bit latch-1 (Figure 13).                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 6   | SHDNB-1 | 1             | Complete Shutdown. Pulling SMBSUS high with SHDNB-1 = 0 places the MAX1611 into a low-quiescent-current shutdown mode, with the reference off and the VL linear regulator output switched to a low-current coarse regulation mode. Pulling SMBSUS high with SHDNB-1 = 1 puts the MAX1611 into its normal operational mode, with the reference and internal VL linear regulator fully on. SHDNB-1 supersedes STDBY-1. As long as SHDNB-1 = 0 and SMBSUS = 0, it doesn't matter what STDBY-1 is; the MAX1611 still shuts down. |  |  |

| 5   | STDBY-1 | 1             | Standby, disables CCFL supply only. As long as SMBSUS stays high and STDBY-1 = 0, the internal power switch is kept off and SS is held shorted to GND; neither the internal reference nor the linear regulator is affected. With STDBY-1 = 1 and SMBSUS high, the MAX1611 operates normally.                                                                                                                                                                                                                                 |  |  |

| 4   | D4-1    | 1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 3   | D3-1    | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 2   | D2-1    | 0             | DAC Input Data. With the SMBSUS pin high, bits D4-1 through D0-1 set the DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 1   | D1-1    | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 0   | D0-1    | 0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

<sup>\*</sup> Initial register state after power-up.

Figure 13. MAX1611 Serial-Interface Read Example

#### Table 6. MAX1611 Status Bits

| BIT                   | NAME                            | POR<br>STATE* | FUNCTION                                                                                                                                                                                                                        |  |  |

|-----------------------|---------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7                     | ОТРОК                           | 1             | Latched Open-Tube Detection. OTPOK = 0 indicates that open-tube detection has been triggered. As soon as the voltage on the OTP pin exceeds REF, the OTPOK bit is cleared. Reset the OTPOK pin by entering shutdown or standby. |  |  |

| 6<br>5                |                                 |               | Unused. These bits always return a logic one.                                                                                                                                                                                   |  |  |

| 4<br>3<br>2<br>1<br>0 | DA4<br>DA3<br>DA2<br>DA1<br>DA0 |               | Displays the DAC setting selected by SMBSUS.                                                                                                                                                                                    |  |  |

<sup>\*</sup> Initial register state after power-up.

two 7-bit registers is used. Tables 4 and 5 describe the data format for the configuration data.

Status information can be read from the MAX1611 using the SMBus read-byte protocol. Figure 13 shows an example status read. Table 6 describes the status information data format.

During shutdown (SMBSUS = 0 and SHDNB-0 = 0, or SMBSUS = 1 and SHDNB-1 = 0), the MAX1611 serial interface remains fully functional and can be used to set either the SHDNB-0 or SHDNB-1 bits in order to return the MAX1611 to its normal operational state.

### Chopping the Lamp Current

Chopping the lamp current allows lower sustainable light levels without lamp flicker. Intensity is varied by controlling the on-time duty cycle. Tying MINDAC to VL activates a special mode, which allows the CCFL intensity to

be varied by turning the lamp on and off at a frequency faster than the eye can detect. The SS pin pulls to GND during off time and rises to 2.7V during on time. During on time, the CSAV pin regulates to REF / 8 (250mV). During off time, the BATT-to-LX power switch is forced off and the CC compensation node goes high impedance. Omit R5, R6, and C4 of the circuit in Figure 4.

In this mode, leave SS floating and increase the CC capacitance to  $0.1\mu F$ . Also, insert a  $330\Omega$  resistor in series with D1 (Figure 4) to prevent the open-lamp detection circuit from being tripped by the repeated striking of the lamp. The SS pin will oscillate at the switching frequency divided by 1024 (283Hz with SYNC = REF). The intensity can be varied with the duty cycle at the SS pin. The duty cycle is set by the DAC in 3% increments. Duty cycle will vary with intensity. Full-scale yields a 100% duty cycle. DAC codes 00001, 00010, and 00011 all yield the

minimum 9% duty cycle. DAC code 00000 shuts off the lamp entirely (0% duty cycle). Figure 14 shows the chopped waveforms with the DAC set to mid-scale.

### **Applications Information**

Directly Regulating the Lamp Current The MAX1610/MAX1611 can directly regulate the CCFL current by tapping into the secondary of T1 (Figure 15). This allows more precise setting of the maximum lamp current ( $I_L$ ). The disadvantage of this approach is that the secondary-to-ground voltage is twice that shown in Figure 4, increasing the likelihood of the thermometer effect, where one end of the lamp is brighter than the other. Figure 15 uses the same component values as Figure 4, except for R1, R40, D40, and D41. D40 and D41 are the same type of diode as D1. R1 should be  $0.68\Omega \pm 10\%$  to set a peak current limit of about 735mA. Use a  $107\Omega \pm 1\%$  resistor for R40 to set a lamp current of 5mARMs. This circuit accepts a wide range of lamp types without component adjustments.

#### **Component Suppliers**

Table 7 lists three different sources for C1. C1 requires a low dissipation factor to prevent overheating as energy is cycled between C1 and the T1 magnetizing induc-

tance in the Royer resonant tank. Table 8 lists suppliers for the high-voltage ballast capacitor, C2.

Figure 14. Chopped Waveforms

Figure 15. Directly Regulating the CCFL Current

**Table 7. Capacitor C1 Supplier Information**

| PART         | SUPPLIER              | LOCATION     | PHONE         | FAX               | NOTES/CONTACT                                                      |

|--------------|-----------------------|--------------|---------------|-------------------|--------------------------------------------------------------------|

|              | WIMA                  | Elmsford, NY | 914-347-2474  | 914-347-7230      | Dissipation factor (tan δ) at 1kHz and 20°C ≤ 0.008.               |

| SMD7.3104    |                       | Germany      | (0621) 8785-0 | (0621) 8710457158 |                                                                    |

|              |                       | Hong Kong    | 5-70-11-51    | 58-06-84-74       | at 11012 and 20 0 3 0.000.                                         |

| CHEV0025J104 | PACCOM<br>Electronics | Redmond, WA  | 206-883-9200  | 206-881-6959      | Dissipation factor (tan $\delta$ ) at 1kHz $\leq$ 0.002.           |

| 4040N104M250 | NOVACAP               | Valencia, CA | 805-295-5920  | 805-295-5928      | Dissipation factor (tan $\delta$ ) at 1kHz and 20°C $\leq$ 0.0015. |

**Table 8. Capacitor C2 Supplier Information**

| PART             | SUPPLIER                  | LOCATION       | PHONE          | FAX            |

|------------------|---------------------------|----------------|----------------|----------------|

|                  |                           | Olean, NY      | 716-372-6611   | 716-372-6316   |

| 1808HA330KATMA   | AVX/Kyocera               | Vancouver, WA  | 206-696-2840   | 206-695-5836   |

| TOUGHASSUKATIVIA |                           | Germany        | 08131 9004-0   | 08131 9004-44  |

|                  |                           | Hong Kong      | 852-363-3303   | 852-765-8185   |

|                  | Murata                    | Smyrna, GA     | 404-436-1300   | 404-436-3030   |

| GHM1040SL330J3K  |                           | Germany        | 49-911-66870   | 49-911-6687193 |

|                  |                           | Taiwan         | 886-2-562-4218 | 886-2-536-6721 |

| 302C1812A330K    | Metuchen Capacitors, Inc. | Old Bridge, NJ | 908-679-3366   | 908-679-3222   |

| 302R29N330K      | Johanson Dielectrics      | Sylmar, CA     | 818-364-9800   | 818-364-6100   |

\_\_\_\_\_Chip Information

**TRANSISTOR COUNT: 5457**

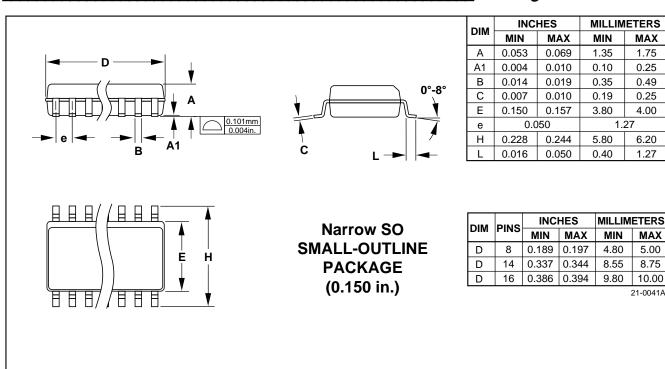

### Package Information

MAX

1.75

0.25

0.49

0.25

4.00

6.20

1.27

MAX

5.00 8.75

10.00

21-0041A

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.