3-W STEREO AUDIO POWER AMPLIFIER WITH ADVANCED DC VOLUME CONTROL

Check for Samples: TPA6013A4

#### **FEATURES**

www.ti.com

- Advanced 32-Steps DC Volume Control

- Steps from -40 to 18 dB

- Fade Mode

- Maximum Volume Setting for SE Mode

- Adjustable SE Volume Control Referenced to BTL Volume Control

- 3 W Into 3-Ω Speakers

- Stereo Input MUX

- Headphone Mode

- Pin-to-pin compatible with TPA6011A4 and TPA6012A4

- 24-pin PowerPAD™ Package (PWP)

#### **APPLICATIONS**

- Notebook PC

- LCD Monitors

- Pocket PC

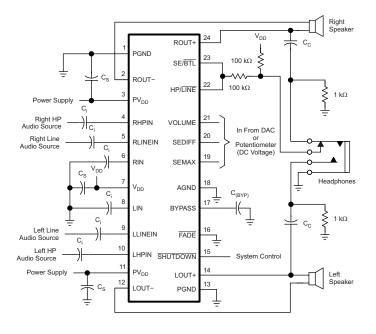

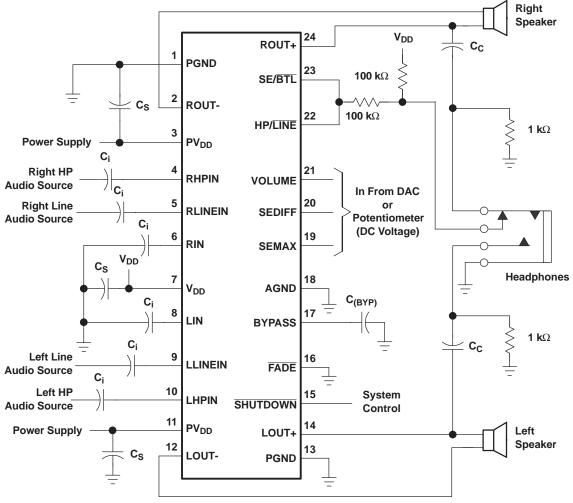

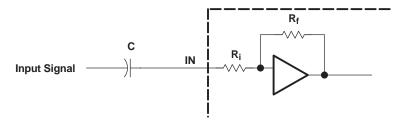

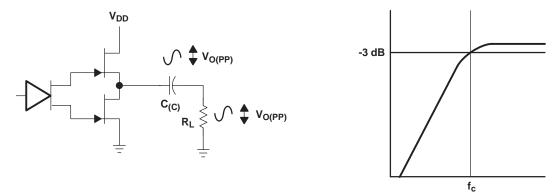

#### APPLICATION CIRCUIT

#### **DESCRIPTION**

The TPA6013A4 is a stereo audio power amplifier that drives 3 W/channel of continuous RMS power into a 3- $\Omega$  load. Advanced dc volume control minimizes external components and allows BTL (speaker) volume control and SE (headphone) volume control. Notebook and pocket PCs benefit from the integrated feature set that minimizes external components without sacrificing functionality.

To simplify design, the speaker volume level is adjusted by applying a dc voltage to the VOLUME terminal. Likewise, the delta between speaker volume and headphone volume can be adjusted by applying a dc voltage to the SEDIFF terminal. To avoid an unexpected high volume level through the headphones, a third terminal, SEMAX, limits the headphone volume level when a dc voltage is applied. Finally, to ensure a smooth transition between active and shutdown modes, a fade mode ramps the volume up and down.

#### DC VOLUME CONTROL

Figure 1. Application Circuit and DC Volume Control

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

S001

SLOS635 – NOVEMBER 2009 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **AVAILABLE OPTIONS**

| т             | PACKAGE                |

|---------------|------------------------|

| IA            | 24-PIN TSSOP (PWP) (1) |

| -40°C to 85°C | TPA6013A4PWP           |

The PWP package is available taped and reeled. To order a taped and reeled part, add the suffix R to the part number (e.g., TPA6013A4PWPR).

#### LEAD (PB-FREE) ORDERING INFORMATION

| ORDERABLE DEVICE | STATUS (1) | ECO-STATUS (2) |

|------------------|------------|----------------|

| TPA6013A4PWPG4   | Active     | Pb-Free        |

| TPA6013A4PWPRG4  | Active     | and Green      |

- (1) The marketing status values are defined as follows:

- (a) ACTIVE: This device recommended for new designs.

- (b) LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

- (c) NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

- (d) PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

- (e) OBSOLETE: TI has discontinued production of the device.

- (2) Eco-Status Information Additional details including specific material content can be accessed at www.ti.com/leadfree

- (a) N/A: Not yet available Lead (Pb)-Free, for estimated conversion dates go to www.ti.com/leadfree.

- (b) **Pb-Free:** TI defines "Lead (Pb)-Free" or "Pb-Free" to mean RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and, if designed to be soldered, suitable for use in specified lead-free soldering processes.

- (c) Green: TI devices "Green" to mean Lead (Pb)-Free and in addition, uses package materials that do not contain halogens, including bromine (Br), or antimony (Sb) above 0.1% of total product weight.

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                    | UNIT                             |

|------------------|----------------------------------------------------|----------------------------------|

| $V_{SS}$         | Supply voltage, V <sub>DD</sub> , PV <sub>DD</sub> | –0.3 V to 6 V                    |

| $V_{I}$          | Input voltage                                      | –0.3 V to V <sub>DD</sub> +0.3 V |

|                  | Continuous total power dissipation                 | See Dissipation Rating Table     |

| $T_A$            | Operating free-air temperature range               | -40°C to 85°C                    |

| $T_{J}$          | Operating junction temperature range               | -40°C to 150°C                   |

| T <sub>stg</sub> | Storage temperature range                          | –65°C to 150°C                   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR             | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| PWP     | 2.7 mW                | 21.8 mW/°C                  | 1.7 W                 | 1.4 W                 |

Submit Documentation Feedback

#### RECOMMENDED OPERATING CONDITIONS

|                                          |                                                    |                       | MIN | MAX                 | UNIT |

|------------------------------------------|----------------------------------------------------|-----------------------|-----|---------------------|------|

| $V_{SS}$                                 | Supply voltage, V <sub>DD</sub> , PV <sub>DD</sub> |                       | 4.0 | 5.5                 | V    |

| V <sub>IH</sub> High-level input voltage | SE/BTL, HP/LINE, FADE                              | 0.8 × V <sub>DD</sub> |     | V                   |      |

|                                          | High-level input voltage                           | SHUTDOWN              | 2   |                     | V    |

| \/                                       |                                                    | SE/BTL, HP/LINE, FADE |     | $0.6 \times V_{DD}$ | V    |

| V <sub>IL</sub>                          | Low-level input voltage                            | SHUTDOWN              |     | 0.8                 | V    |

| T <sub>A</sub>                           | Operating free-air temperatu                       | re                    | -40 | 85                  | °C   |

#### **ELECTRICAL CHARACTERISTICS**

$T_A = 25$ °C,  $V_{DD} = PV_{DD} = 5.5 \text{ V}$  (unless otherwise noted)

|                     | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                                                                                                                       | MIN | TYP | MAX | UNIT             |

|---------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------------------|

| 1.1/                | Output offset voltage (measured differentially)                                   | V <sub>DD</sub> = 5.5 V, Gain = 0 dB, SE/BTL = 0 V                                                                                                                                                                                    |     | 2   | 30  | mV               |

| V <sub>00</sub>     | Output onset voltage (measured differentially)                                    | $V_{DD} = 5.5 \text{ V}, \text{ Gain} = 18 \text{ dB}, \text{ SE}/\overline{\text{BTL}} = 0 \text{ V}$                                                                                                                                |     | 2.6 | 50  | mV               |

| PSRR                | Power supply rejection ratio                                                      | $V_{DD} = PV_{DD} = 4.0 \text{ V to } 5.5 \text{ V, Gain} = 0 \text{ dB}$                                                                                                                                                             |     | -80 |     | dB               |

| I <sub>IH</sub>     | High-level input current (SE/BTL, FADE, HP/LINE, SHUTDOWN, SEDIFF, SEMAX, VOLUME) | $V_{DD} = PV_{DD} = 5.5 \text{ V},$<br>$V_{I} = V_{DD} = PV_{DD}$                                                                                                                                                                     |     |     | 1   | μΑ               |

| I <sub>IL</sub>     | Low-level input current (SE/BTL, FADE, HP/LINE, SHUTDOWN, SEDIFF, SEMAX, VOLUME)  | V <sub>DD</sub> = PV <sub>DD</sub> = 5.5 V, V <sub>I</sub> = 0 V                                                                                                                                                                      |     |     | 1   | μA               |

|                     | Supply current, no load                                                           | $V_{DD} = PV_{DD} = 5 \text{ V, SE/BTL} = 0 \text{ V,}$<br>SHUTDOWN = 2 V                                                                                                                                                             |     | 6.7 | 9.0 | mA               |

| I <sub>DD</sub>     | Зирріу сипені, по юда                                                             | $V_{DD} = PV_{DD} = 5 \text{ V, SE/BTL} = 5 \text{ V,}$<br>SHUTDOWN = 2 V                                                                                                                                                             |     | 4.5 | 6   | IIIA             |

| I <sub>DD</sub>     | Supply current, max power into a $3-\Omega$ load                                  | $\label{eq:decomposition} \begin{array}{l} V_{DD} = 5 \text{ V} = \text{PV}_{DD}, \text{ SE/BTL} = 0 \text{ V}, \\ \hline \text{SHUTDOWN} = 2 \text{ V}, \text{ R}_{L} = 3\Omega, \\ P_{O} = 2 \text{ W}, \text{ stereo} \end{array}$ |     | 1.5 |     | A <sub>RMS</sub> |

| I <sub>DD(SD)</sub> | Supply current, shutdown mode                                                     | SHUTDOWN = 0.0 V                                                                                                                                                                                                                      |     | 10  | 25  | μΑ               |

#### **OPERATING CHARACTERISTICS**

$\underline{T}_{A}$  = 25°C,  $V_{DD}$  = PV<sub>DD</sub> = 5 V,  $R_{L}$  = 3  $\Omega$ , Gain = 6 dB, Stereo (unless otherwise noted)

| PARAMETER             |                                               | TEST CONDITIONS                                                                               |                       | MIN  | TYP   | MAX  | UNIT          |

|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|------|-------|------|---------------|

|                       |                                               | THD = 1%, f = 1 kHz, $R_L$ = 16 Ω (SE)                                                        |                       |      | 195   |      | mW            |

| D                     | Output name                                   | THD = 10%, f = 1 kHz, $R_L$ = 16 $\Omega$ (SE)                                                |                       |      | 235   |      | mW            |

| Po                    | Output power                                  | THD = 1%, f = 1 kHz, $R_L = 3 \Omega$ (BTL)                                                   |                       |      | 2.0   |      | W             |

|                       |                                               | THD = 10%, f = 1 kHz, $V_{DD}$ = 5.5 V, $R_L$ =3                                              | Ω (BTL)               |      | 3.2   |      | VV            |

| THD+N                 | Total harmonic distortion + noise             | $P_{O} = 0.9 \text{ W}, R_{L} = 8 \Omega \text{ (BTL)}, f = 20 \text{ Hz to } 20 \text{ Hz}$  | 0 kHz                 |      | <0.1% |      |               |

|                       |                                               | $P_{O} = 0.1 \text{ W}, R_{L} = 16 \Omega \text{ (SE)}, f = 20 \text{ Hz to } 20 \text{ kHz}$ |                       |      | 0.03% |      |               |

| V <sub>OH</sub>       | High-level output voltage                     | $R_L = 8 \Omega$ , Measured between output and V                                              | <sub>DD</sub> = 5.5 V |      |       | 700  | mV            |

| V <sub>OL</sub>       | Low-level output voltage                      | $R_L$ = 8 Ω, Measured between output and GND, $V_{DD}$ = 5.5 V                                |                       |      |       | 400  | mV            |

| V <sub>(Bypass)</sub> | Bypass voltage (Nominally V <sub>DD</sub> /2) | Measured at pin 17, No load, V <sub>DD</sub> = 5.5 V                                          |                       | 2.65 | 2.75  | 2.85 | V             |

|                       | Cupply ripple rejection ratio                 | $f = 1 \text{ kHz}$ , Gain = 0 dB, $C_{(BYP)} = 1 \mu F$                                      | BTL (4Ω)              |      | -66   |      | dB            |

|                       | Supply ripple rejection ratio                 |                                                                                               | SE (32Ω)              |      | -60   |      | dB            |

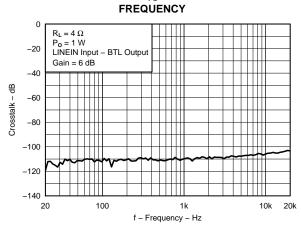

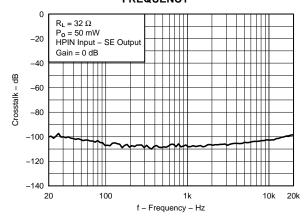

|                       | Cranatalle                                    |                                                                                               | BTL                   |      | 110   |      | dB            |

|                       | Crosstalk                                     |                                                                                               | SE                    |      | 102   |      | dB            |

|                       | Noise output voltage                          | $f$ = 20 Hz to 20 kHz, Gain = 0 dB, $C_{(BYP)}$ = 1 $\mu F$                                   |                       |      | 36    |      | $\mu V_{RMS}$ |

| Z <sub>I</sub>        | Input impedance (see Figure 17)               | VOLUME = 5 V                                                                                  |                       |      | 12    |      | kΩ            |

Copyright © 2009, Texas Instruments Incorporated

Submit Documentation Feedback

P0110-01

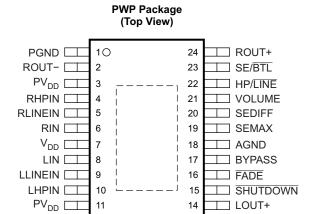

#### **PIN Functions**

13

□ PGND

LOUT-

12

| PIN             |       |     | DESCRIPTION                                                                                                                              |

|-----------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.   | I/O | DESCRIPTION                                                                                                                              |

| PGND            | 1, 13 | _   | Power ground                                                                                                                             |

| LOUT-           | 12    | 0   | Left channel negative audio output                                                                                                       |

| $PV_{DD}$       | 3, 11 | -   | Supply voltage terminal for power stage                                                                                                  |

| LHPIN           | 10    | ı   | Left channel headphone input, selected when HP/LINE is held high                                                                         |

| LLINEIN         | 9     | Ĺ   | Left channel line input, selected when HP/LINE is held low                                                                               |

| LIN             | 8     | ı   | Common left channel input for fully differential input. AC ground for single-ended inputs.                                               |

| V <sub>DD</sub> | 7     | -   | Supply voltage terminal                                                                                                                  |

| RIN             | 6     | ı   | Common right channel input for fully differential input. AC ground for single-ended inputs.                                              |

| RLINEIN         | 5     | I   | Right channel line input, selected when HP/LINE is held low                                                                              |

| RHPIN           | 4     | ı   | Right channel headphone input, selected when HP/LINE is held high                                                                        |

| ROUT-           | 2     | 0   | Right channel negative audio output                                                                                                      |

| ROUT+           | 24    | 0   | Right channel positive audio output                                                                                                      |

| SHUTDOWN        | 15    | I   | Places the amplifier in shutdown mode if a TTL logic low is placed on this terminal                                                      |

| FADE            | 16    | I   | Places the amplifier in fade mode if a logic low is placed on this terminal; normal operation if a logic high is placed on this terminal |

| BYPASS          | 17    | ı   | Tap to voltage divider for internal mid-supply bias generator used for analog reference                                                  |

| AGND            | 18    | -   | Analog power supply ground                                                                                                               |

| SEMAX           | 19    | I   | Sets the maximum volume for single ended operation. DC voltage range is 0 to V <sub>DD</sub> .                                           |

| SEDIFF          | 20    | ı   | Sets the difference between BTL volume and SE volume. DC voltage range is 0 to V <sub>DD</sub> .                                         |

| VOLUME          | 21    | I   | Terminal for dc volume control. DC voltage range is 0 to V <sub>DD</sub> .                                                               |

| HP/LINE         | 22    | I   | Input MUX control. When logic high, RHPIN and LHPIN inputs are selected. When logic low, RLINEIN and LLINEIN inputs are selected.        |

| SE/BTL          | 23    | ı   | Output MUX control. When this terminal is high, SE outputs are selected. When this terminal is low, BTL outputs are selected.            |

| LOUT+           | 14    | 0   | Left channel positive audio output.                                                                                                      |

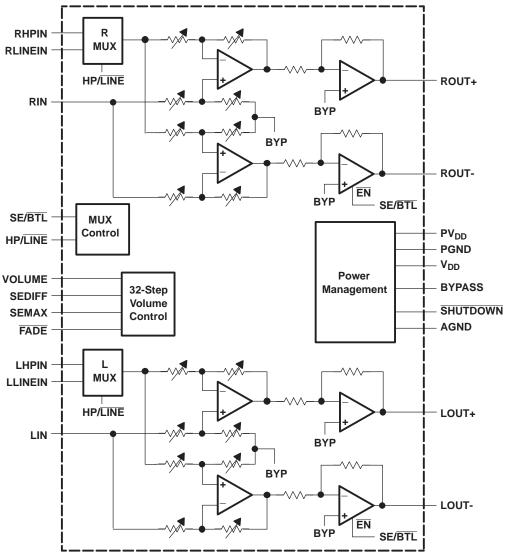

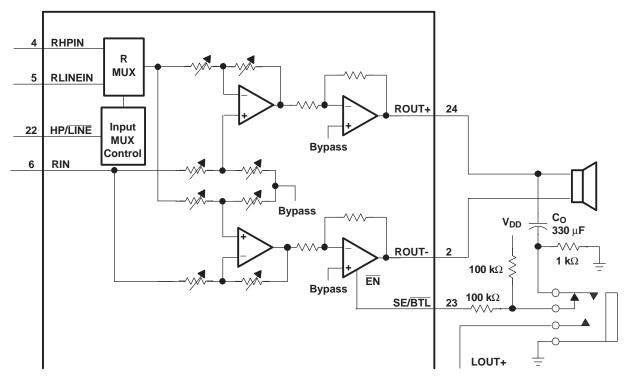

### **FUNCTIONAL BLOCK DIAGRAM**

NOTE: All resistor wipers are adjusted with 32-step volume control.

Table 1. DC Volume Control (BTL Mode,  $V_{DD} = 5 \text{ V})^{(1)}$

| VOLUME   | E (PIN 21) | GAIN OF AMPLIFIER           |

|----------|------------|-----------------------------|

| FROM (V) | TO (V)     | GAIN OF AMPLIFIER (Typ) (2) |

| 0.00     | 0.26       | <b>–</b> 85                 |

| 0.33     | 0.37       | -40                         |

| 0.44     | 0.48       | -34                         |

| 0.56     | 0.59       | -31                         |

| 0.67     | 0.70       | -28                         |

| 0.78     | 0.82       | -25                         |

| 0.89     | 0.93       | -22                         |

| 1.01     | 1.04       | -19                         |

| 1.12     | 1.16       | -16                         |

| 1.23     | 1.27       | -13                         |

| 1.35     | 1.38       | -10                         |

| 1.46     | 1.49       | -7                          |

| 1.57     | 1.60       | -4                          |

| 1.68     | 1.72       | -2                          |

| 1.79     | 1.83       | -0                          |

| 1.91     | 1.94       | 2                           |

| 2.02     | 2.06       | 4                           |

| 2.13     | 2.17       | 6                           |

| 2.25     | 2.28       | 8                           |

| 2.36     | 2.39       | 10                          |

| 2.47     | 2.50       | 11                          |

| 2.58     | 2.61       | 12                          |

| 2.70     | 2.73       | 13                          |

| 2.81     | 2.83       | 14                          |

| 2.92     | 2.95       | 14.5                        |

| 3.04     | 3.06       | 15                          |

| 3.15     | 3.17       | 15.5                        |

| 3.26     | 3.29       | 16                          |

| 3.38     | 3.40       | 16.5                        |

| 3.49     | 3.51       | 17                          |

| 3.60     | 3.63       | 17.5                        |

| 3.71     | 5.00       | 18                          |

<sup>(1)</sup> For other values of  $V_{DD}$ , scale the voltage values in the table by a factor of  $V_{DD}/5$ . (2) Tested in production. Remaining gain steps are specified by design.

SLOS635 - NOVEMBER 2009 www.ti.com

Table 2. DC Volume Control (SE Mode,  $V_{DD} = 5 \text{ V})^{(1)}$

| ME - SEDIFF or SEMAX | GAIN OF AMPLIFIER                                                                                                                                          |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TO (V)               | (Тур)                                                                                                                                                      |

| 0.26                 | -85 <sup>(2)</sup>                                                                                                                                         |

| 0.37                 | -46                                                                                                                                                        |

| 0.48                 | -40                                                                                                                                                        |

| 0.59                 | -37                                                                                                                                                        |

| 0.70                 | -34                                                                                                                                                        |

| 0.82                 | <del>-</del> 31                                                                                                                                            |

| 0.93                 | -28                                                                                                                                                        |

| 1.04                 | <b>–</b> 25                                                                                                                                                |

| 1.16                 | -22                                                                                                                                                        |

| 1.27                 | <b>–19</b>                                                                                                                                                 |

| 1.38                 | -16                                                                                                                                                        |

| 1.49                 | -13                                                                                                                                                        |

| 1.60                 | -10                                                                                                                                                        |

| 1.72                 | -8                                                                                                                                                         |

| 1.83                 | -6 <sup>(2)</sup>                                                                                                                                          |

| 1.94                 | -4                                                                                                                                                         |

| 2.06                 | -2                                                                                                                                                         |

| 2.17                 | 0 <sup>(2)</sup>                                                                                                                                           |

| 2.28                 | 2                                                                                                                                                          |

| 2.39                 | 4                                                                                                                                                          |

| 2.50                 | 5                                                                                                                                                          |

| 2.61                 | 6 <sup>(2)</sup>                                                                                                                                           |

| 2.73                 | 7                                                                                                                                                          |

| 2.83                 | 8                                                                                                                                                          |

| 2.95                 | 8.5                                                                                                                                                        |

| 3.06                 | 9                                                                                                                                                          |

| 3.17                 | 9.5                                                                                                                                                        |

| 3.29                 | 10                                                                                                                                                         |

| 3.40                 | 10.5                                                                                                                                                       |

| 3.51                 | 11                                                                                                                                                         |

| 3.63                 | 11.5                                                                                                                                                       |

| 5.00                 | 12                                                                                                                                                         |

|                      | 0.26 0.37 0.48 0.59 0.70 0.82 0.93 1.04 1.16 1.27 1.38 1.49 1.60 1.72 1.83 1.94 2.06 2.17 2.28 2.39 2.50 2.61 2.73 2.83 2.95 3.06 3.17 3.29 3.40 3.51 3.63 |

<sup>(1)</sup> For other values of  $V_{DD}$ , scale the voltage values in the table by a factor of  $V_{DD}/5$ . (2) Tested in production. Remaining gain steps are specified by design.

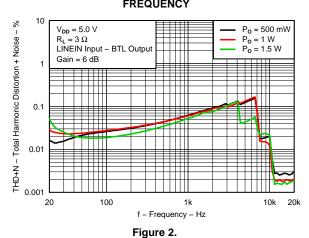

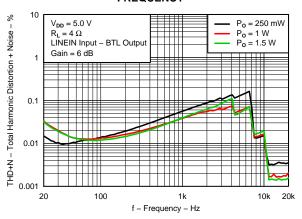

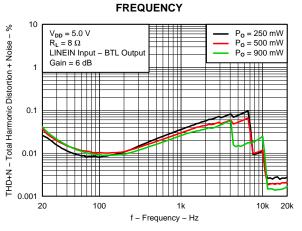

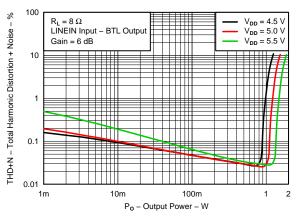

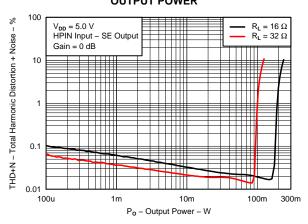

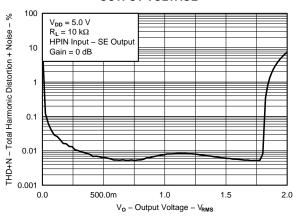

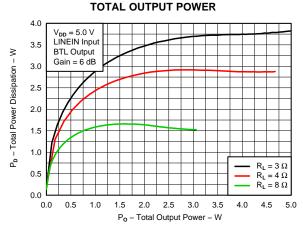

#### TYPICAL CHARACTERISTICS

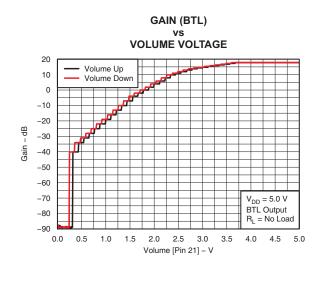

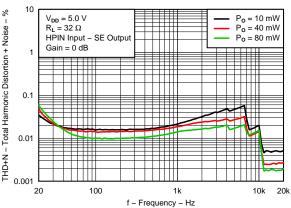

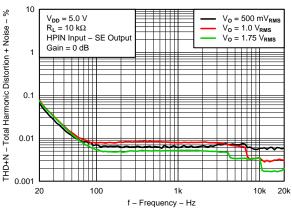

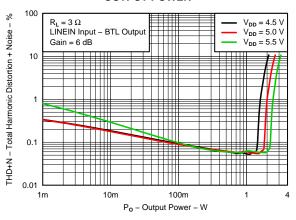

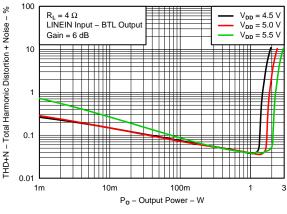

Test conditions (unless otherwise noted) for typical operating performance:  $V_{DD}=5.0~V,~C_{IN}=1~\mu F,~C_{BYPASS}=1~\mu F,~T_A=27^{\circ}C,~SHUTDOWN=V_{DD}$

#### **Table of Graphs**

|                 | Gain (BTL)                                 | vs Volume voltage     | Figure 1                     |

|-----------------|--------------------------------------------|-----------------------|------------------------------|

| THD+N           | Total harmonia distortion plus poice (PTI) | vs Frequency          | Figure 2, Figure 3, Figure 4 |

| THUTIN          | Total harmonic distortion plus noise (BTL) | vs Output power       | Figure 7, Figure 8, Figure 9 |

|                 |                                            | vs Frequency          | Figure 5, Figure 6           |

| THD+N           | Total harmonic distortion plus noise (SE)  | vs Output power       | Figure 10                    |

|                 |                                            | vs Output voltage     | Figure 11                    |

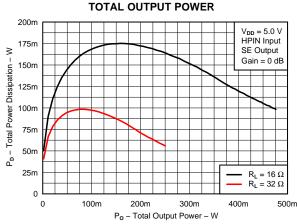

| P <sub>D</sub>  | Total power dissipation (BTL)              | vs Total output power | Figure 12                    |

| P <sub>D</sub>  | Total power dissipation (SE)               | vs Total output power | Figure 13                    |

|                 | Crosstalk (BTL)                            | vs Frequency          | Figure 14                    |

|                 | Crosstalk (SE)                             | vs Frequency          | Figure 15                    |

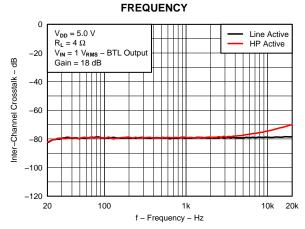

|                 | Inter-channel crosstalk                    | vs Frequency          | Figure 16                    |

|                 | Input impedance                            | vs Gain               | Figure 17                    |

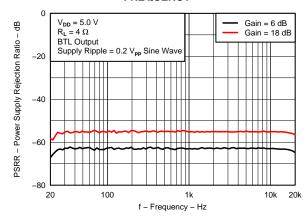

| PSRR            | Power supply rejection ratio (BTL)         | vs Frequency          | Figure 18                    |

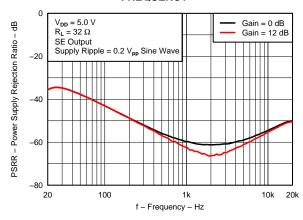

| PSRR            | Power supply rejection ratio (SE)          | vs Frequency          | Figure 19                    |

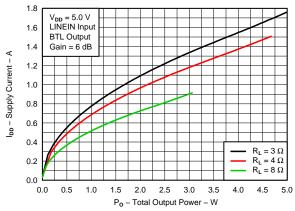

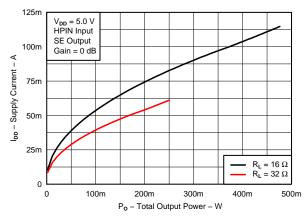

| I <sub>DD</sub> | Supply current (BTL)                       | vs Total output power | Figure 20                    |

| I <sub>DD</sub> | Supply current (SE)                        | vs Total output power | Figure 21                    |

# TOTAL HARMONIC DISTORTION + NOISE (BTL) vs FREQUENCY

TOTAL HARMONIC DISTORTION + NOISE (BTL)

vs

FREQUENCY

Figure 3.

### TOTAL HARMONIC DISTORTION + NOISE (BTL) vs

Figure 4.

# TOTAL HARMONIC DISTORTION + NOISE (SE) vs FREQUENCY

Figure 5.

# TOTAL HARMONIC DISTORTION + NOISE (SE) vs FREQUENCY

Figure 6.

## TOTAL HARMONIC DISTORTION + NOISE (BTL) vs OUTPUT POWER

Figure 7.

# TOTAL HARMONIC DISTORTION + NOISE (BTL) vs OUTPUT POWER

Figure 8.

# TOTAL HARMONIC DISTORTION + NOISE (BTL) vs OUTPUT POWER

Figure 9.

SLOS635 – NOVEMBER 2009 www.ti.com

#### TEXAS INSTRUMENTS

## TOTAL HARMONIC DISTORTION + NOISE (SE) vs OUTPUT POWER

Figure 10.

## TOTAL HARMONIC DISTORTION + NOISE (SE) vs OUTPUT VOLTAGE

Figure 11.

### TOTAL POWER DISSIPATION (BTL) vs

Figure 12.

### TOTAL POWER DISSIPATION (SE)

Figure 13.

### CROSSTALK (BTL)

Figure 14.

# CROSSTALK (SE) vs FREQUENCY

Figure 15.

Figure 16.

#### **INPUT IMPEDANCE** GAIN 120k Differential Single-Ended 100k Input Impedance – Ω 80k 60k 40k 20k $V_{DD} = 5.0 \text{ V}$ R<sub>L</sub> = No Load -40 -35 -30 -25 -20 -15 -10 0 5 -5 10 15 20 Gain - dB

Figure 17.

### POWER SUPPLY REJECTION RATIO (BTL)

#### vs FREQUENCY

Figure 18.

# POWER SUPPLY REJECTION RATIO (SE) vs FREQUENCY

Figure 19.

# SUPPLY CURRENT (BTL) vs TOTAL OUTPUT POWER

Figure 20.

# SUPPLY CURRENT (SE) vs TOTAL OUTPUT POWER

Figure 21.

## TEXAS INSTRUMENTS

#### APPLICATION INFORMATION

#### **SELECTION OF COMPONENTS**

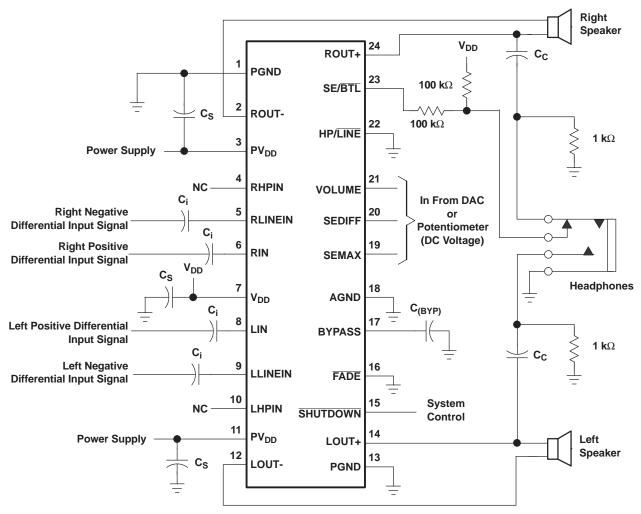

Figure 22 and Figure 23 are schematic diagrams of typical notebook computer application circuits.

A. A 0.1-µF ceramic capacitor should be placed as close as possible to the IC. For filtering lower-frequency noise signals, a larger electrolytic capacitor of 10 µF or greater should be placed near the audio power amplifier.

Figure 22. Typical TPA6013A4 Application Circuit Using Single-Ended Inputs and Input MUX

A. A 0.1-μF ceramic capacitor should be placed as close as possible to the IC. For filtering lower-frequency noise signals, a larger electrolytic capacitor of 10 μF or greater should be placed near the audio power amplifier.

Figure 23. Typical TPA6013A4 Application Circuit Using Differential Inputs

#### SE/BTL OPERATION

The ability of the TPA6013A4 to easily switch between BTL and SE modes is one of its most important cost saving features. This feature eliminates the requirement for an additional headphone amplifier in applications where internal stereo speakers are driven in BTL mode but external headphone or speakers must be accommodated. Internal to the TPA6013A4, two separate amplifiers drive OUT+ and OUT-. The SE/BTL input controls the operation of the follower amplifier that drives LOUT- and ROUT-. When SE/BTL is held low, the amplifier is on and the TPA6013A4 is in the BTL mode. When SE/BTL is held high, the OUT- amplifiers are in a high output impedance state, which configures the TPA6013A4 as an SE driver from LOUT+ and ROUT+. IDD is reduced by approximately one-third in SE mode. Control of the SE/BTL input can be from a logic-level CMOS source or, more typically, from a resistor divider network as shown in Figure 24. The trip level for the SE/BTL input can be found in the recommended operating conditions table.

Figure 24. TPA6013A4 Resistor Divider Network Circuit

Using a 1/8-in. (3,5 mm) stereo headphone jack, the control switch is closed when no plug is inserted. When closed the  $100-k\Omega/1-k\Omega$  divider pulls the SE/BTL input low. When a plug is inserted, the  $1-k\Omega$  resistor is disconnected and the SE/BTL input is pulled high. When the input goes high, the OUT– amplifier is shut down causing the speaker to mute (open-circuits the speaker). The OUT+ amplifier then drives through the output capacitor ( $C_0$ ) into the headphone jack.

#### **HP/LINE OPERATION**

The HP/LINE input controls the internal input multiplexer (MUX). Refer to the block diagram in Figure 24. This allows the device to switch between two separate stereo inputs to the amplifier. For design flexibility, the HP/LINE control is independent of the output mode, SE or BTL, which is controlled by the aforementioned SE/BTL pin. To allow the amplifier to switch from the LINE inputs to the HP inputs when the output switches from BTL mode to SE mode, simply connect the SE/BTL control input to the HP/LINE input.

When this input is logic high, the RHPIN and LHPIN inputs are selected. When this terminal is logic low, the RLINEIN and LLINEIN inputs are selected. This operation is also detailed in Table 3 and the trip levels for a logic low  $(V_{IL})$  or logic high  $(V_{IH})$  can be found in the *recommended operating conditions* table.

#### **SHUTDOWN MODES**

The TPA6013A4 employs a shutdown mode of operation designed to reduce supply current ( $I_{DD}$ ) to the absolute minimum level during periods of nonuse for battery-power conservation. The SHUTDOWN input terminal should be held high during normal operation when the amplifier is in use. Pulling SHUTDOWN low causes the outputs to mute and the amplifier to enter a low-current state,  $I_{DD}$  = 20  $\mu$ A. SHUTDOWN should never be left unconnected because amplifier operation would be unpredictable.

SLOS635 - NOVEMBER 2009 www.ti.com

| Table 3. HP/LINE | , SE/BTL. | and Shutdown | <b>Functions</b> |

|------------------|-----------|--------------|------------------|

|------------------|-----------|--------------|------------------|

|         | INPUTS (1) | AMPLIFIER STATE |       |        |  |  |

|---------|------------|-----------------|-------|--------|--|--|

| HP/LINE | SE/BTL     | SHUTDOWN        | INPUT | OUTPUT |  |  |

| Х       | Х          | Low             | X     | Mute   |  |  |

| Low     | Low        | High            | Line  | BTL    |  |  |

| Low     | High       | High            | Line  | SE     |  |  |

| High    | High Low   |                 | HP    | BTL    |  |  |

| High    | High       | High            | HP    | SE     |  |  |

<sup>(1)</sup> Inputs should never be left unconnected.

#### **FADE OPERATION**

For design flexibility, a fade mode is provided to slowly ramp up the amplifier gain when coming out of shutdown mode and conversely ramp the gain down when going into shutdown. This mode provides a smooth transition between the active and shutdown states and virtually eliminates any pops or clicks on the outputs.

When the FADE input is a logic low, the device is placed into fade-on mode. A logic high on this pin places the amplifier in the fade-off mode. The voltage trip levels for a logic low (VIL) or logic high (VIH) can be found in the recommended operating conditions table.

When a logic low is applied to the FADE pin and a logic low is then applied on the SHUTDOWNpin, the channel gain steps down from gain step to gain step at a rate of two clock cycles per step. With a nominal internal clock frequency of 58 Hz, this equates to 34 ms (1/24 Hz) per step. The gain steps down until the lowest gain step is reached. The time it takes to reach this step depends on the gain setting prior to placing the device in shutdown. For example, if the amplifier is in the highest gain mode of 18 dB, the time it takes to ramp down the channel gain is 1.05 seconds. This number is calculated by taking the number of steps to reach the lowest gain from the highest gain, or 31 steps, and multiplying by the time per step, or 34 ms.

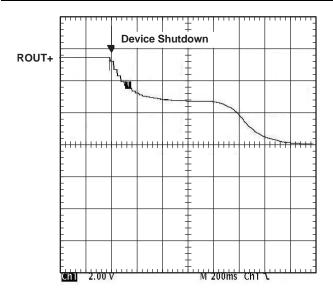

After the channel gain is stepped down to the lowest gain, the amplifier begins discharging the bypass capacitor from the nominal voltage of  $V_{DD}/2$  to ground. This time is dependent on the value of the bypass capacitor. For a 0.47-µF capacitor that is used in the application diagram in Figure 22, the time is approximately 500 ms. This time scales linearly with the value of bypass capacitor. For example, if a 1-µF capacitor is used for bypass, the time period to discharge the capacitor to ground is twice that of the 0.47-µF capacitor, or 1 second. Figure 25 is a waveform captured at the output during the shutdown sequence when the part is in fade-on mode. The gain is set to the highest level and the output is at  $V_{DD}$  when the amplifier is shut down.

When a logic high is placed on the SHUTDOWN pin and the FADE pin is still held low, the device begins the start-up process. The bypass capacitor will begin charging. Once the bypass voltage reaches the final value of V<sub>DD</sub>/2, the gain increases from the lowest gain level to the gain level set by the dc voltage applied to the VOLUME, SEDIFF, and SEMAX pins.

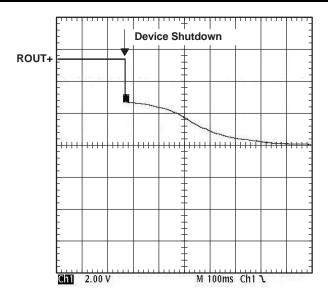

In the fade-off mode, the amplifier stores the gain value prior to starting the shutdown sequence. The output of the amplifier immediately drops to V<sub>DD</sub>/2 and the bypass capacitor begins a smooth discharge to ground. When shutdown is released, the bypass capacitor charges up to V<sub>DD</sub>/2 and the channel gain returns immediately to the value stored in memory. Figure 26 is a waveform captured at the output during the shutdown sequence when the part is in the fade-off mode. The gain is set to the highest level, and the output is at V<sub>DD</sub> when the amplifier is shut down.

The power-up sequence is different from the shutdown sequence and the voltage on the FADEpin does not change the power-up sequence. Upon a power-up condition, the TPA6013A4 begins in the lowest gain setting and steps up every 2 clock cycles until the final value is reached as determined by the dc voltage applied to the VOLUME, SEDIFF, and SEMAX pins.

Copyright © 2009, Texas Instruments Incorporated

SLOS635 – NOVEMBER 2009 www.ti.com

Figure 25. Shutdown Sequence in the Fade-on Mode

Figure 26. Shutdown Sequence in the Fade-off Mode

#### **VOLUME, SEDIFF, AND SEMAX OPERATION**

Three pins labeled VOLUME, SEDIFF, and SEMAX control the BTL volume when driving speakers and the SE volume when driving headphones. All of these pins are controlled with a dc voltage, which should not exceed  $V_{DD}$ .

When driving speakers in BTL mode, the VOLUME pin is the only pin that controls the gain. Table 1 shows the gain for the BTL mode. The voltages listed in the table are for  $V_{DD} = 5$  V. For a different  $V_{DD}$ , the values in the table scale linearly. If  $V_{DD} = 4$  V, multiply all the voltages in the table by 4 V/5 V, or 0.8.

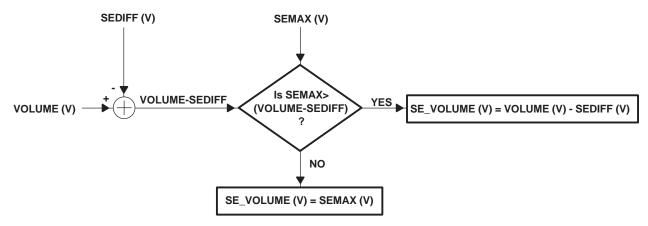

The TPA6013A4 allows the user to specify a difference between BTL gain and SE gain. This is desirable to avoid any listening discomfort when plugging in headphones. When switching to SE mode, the SEDIFF and SEMAX pins control the singe-ended gain proportional to the gain set by the voltage on the VOLUME pin. When SEDIFF = 0 V, the difference between the BTL gain and the SE gain is 6 dB. Refer to the section labeled *bridge-tied load versus single-ended load* for an explanation on why the gain in BTL mode is 2x that of single-ended mode, or 6dB greater. As the voltage on the SEDIFF terminal is increased, the gain in SE mode decreases. The voltage on the SEDIFF terminal is subtracted from the voltage on the VOLUME terminal and this value is used to determine the SE gain.

Some audio systems require that the gain be limited in the single-ended mode to a level that is comfortable for headphone listening. Most volume control devices only have one terminal for setting the gain. For example, if the speaker gain is 18 dB, the gain in the headphone channel is fixed at 12 dB. This level of gain could cause discomfort to listeners and the SEMAX pin allows the designer to limit this discomfort when plugging in headphones. The SEMAX terminal controls the maximum gain for single-ended mode.

The functionality of the SEDIFF and SEMAX pin are combined to set the SE gain. A block diagram of the combined functionality is shown in Figure 27. The value obtained from the block diagram for SE\_VOLUME is a dc voltage that can be used in conjunction with Table 2 to determine the SE gain. Again, the voltages listed in the table are for  $V_{DD} = 5$  V. The values must be scaled for other values of  $V_{DD}$ .

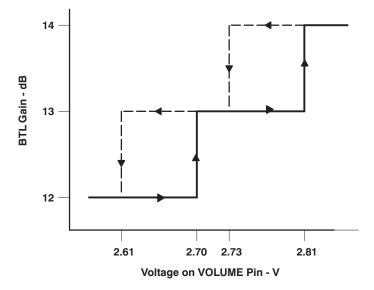

Table 1 and Table 2 show a range of voltages for each gain step. There is a gap in the voltage between each gain step. This gap represents the hysteresis about each trip point in the internal comparator. The hysteresis ensures that the gain control is monotonic and does not oscillate from one gain step to another. If a potentiometer is used to adjust the voltage on the control terminals, the gain increases as the potentiometer is turned in one direction and decreases as it is turned back the other direction. The trip point, where the gain

actually changes, is different depending on whether the voltage is increased or decreased as a result of the hysteresis about each trip point. The gaps in Table 1 and Table 2 can also be thought of as indeterminate states where the gain could be in the next higher gain step or the lower gain step depending on the direction the

where the gain could be in the next higher gain step or the lower gain step depending on the direction the voltage is changing. If using a DAC to control the volume, set the voltage in the middle of each range to ensure that the desired gain is achieved.

A pictorial representation of the volume control can be found in Figure 28. The graph focuses on three gain steps with the trip points defined in Table 1 for BTL gain. The dotted line represents the hysteresis about each gain step.

Figure 27. Block Diagram of SE Volume Control

Figure 28. DC Volume Control Operation

SLOS635-NOVEMBER 2009 www.ti.com

### **INSTRUMENTS**

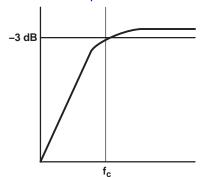

#### INPUT RESISTANCE

Each gain setting is achieved by varying the input resistance of the amplifier, which can range from its smallest value to over six times that value. As a result, if a single capacitor is used in the input high-pass filter, the -3 dB or cutoff frequency also changes by over six times.

Figure 29. Resistor on Input for Cut-Off Frequency

The input resistance at each gain setting is given in Figure 17.

The -3-dB frequency can be calculated using Equation 1.

$$f_{-3 \text{ dB}} = \frac{1}{2\pi \text{ CR}_{i}} \tag{1}$$

#### INPUT CAPACITOR, C;

In the typical application an input capacitor (C<sub>i</sub>) is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case, C<sub>i</sub> and the input impedance of the amplifier (R<sub>i</sub>) form a high-pass filter with the corner frequency determined in Equation 2.

$$f_{c(highpass)} = \frac{1}{2\pi R_i C_i}$$

(2)

The value of C<sub>i</sub> is important to consider as it directly affects the bass (low frequency) performance of the circuit. Consider the example where  $R_i$  is 70 k $\Omega$  and the specification calls for a flat-bass response down to 40 Hz. Equation 2 is reconfigured as Equation 3.

$$C_{i} = \frac{1}{2\pi R_{i} f_{c}} \tag{3}$$

In this example, C<sub>i</sub> is 56.8 nF, so one would likely choose a value in the range of 56 nF to 1 µF. A further consideration for this capacitor is the leakage path from the input source through the input network (C) and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at V<sub>DD</sub>/2, which is likely higher than the source dc level. Note that it is important to confirm the capacitor polarity in the application.

### POWER SUPPLY DECOUPLING, C(S)

The TPA6013A4 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F placed as close as possible to the device  $V_{DD}$  lead, works best. For filtering lower-frequency noise signals, a larger aluminum electrolytic capacitor of 10  $\mu$ F or greater placed near the audio power amplifier is recommended.

#### MIDRAIL BYPASS CAPACITOR, C(BYP)

The midrail bypass capacitor  $(C_{(BYP)})$  is the most critical capacitor and serves several important functions. During start-up or recovery from shutdown mode,  $C_{(BYP)}$  determines the rate at which the amplifier starts up. The second function is to reduce noise produced by the power supply caused by coupling into the output drive signal. This noise is from the midrail generation circuit internal to the amplifier, which appears as degraded PSRR and THD+N.

Bypass capacitor ( $C_{(BYP)}$ ) values of 0.47- $\mu$ F to 1- $\mu$ F ceramic or tantalum low-ESR capacitors are recommended for the best THD and noise performance. For the best pop performance, choose a value for  $C_{(BYP)}$  that is equal to or greater than the value chosen for  $C_i$ . This ensures that the input capacitors are charged up to the midrail voltage before  $C_{(BYP)}$  is fully charged to the midrail voltage.

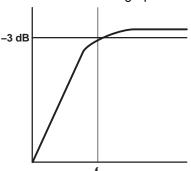

### OUTPUT COUPLING CAPACITOR, C(C)

In the typical single-supply SE configuration, an output coupling capacitor  $(C_{(C)})$  is required to block the dc bias at the output of the amplifier, thus preventing dc currents in the load. As with the input coupling capacitor, the output coupling capacitor and impedance of the load form a high-pass filter governed by Equation 4.

$$f_{c(high)} = \frac{1}{2\pi R_L C_{(C)}}$$

(4)

The main disadvantage, from a performance standpoint, is the load impedances are typically small, which drives the low-frequency corner higher, degrading the bass response. Large values of  $C_{(C)}$  are required to pass low frequencies into the load. Consider the example where a  $C_{(C)}$  of 330  $\mu F$  is chosen and loads vary from 3 $\Omega$  ,4  $\Omega$ , 8 $\Omega$ , 32 $\Omega$ , 10 k $\Omega$ , and 47 k $\Omega$ . Table 4 summarizes the frequency response characteristics of each configuration.

Table 4. Common Load Impedances vs Low Frequency

Output Characteristics in SE Mode

|                | •                |                  |  |  |

|----------------|------------------|------------------|--|--|

| R <sub>L</sub> | C <sub>(C)</sub> | LOWEST FREQUENCY |  |  |

| 3 Ω            | 330 μF 161 Hz    |                  |  |  |

| 4 Ω            | 330 μF 120 Hz    |                  |  |  |

| 8 Ω            | 330 µF           | 60 Hz            |  |  |

| 32 Ω           | 330 µF           | 15 Hz            |  |  |

| 10,000 Ω       | 330 µF           | 0.05 Hz          |  |  |

| 47,000 Ω       | 330 µF           | 0.01 Hz          |  |  |

Copyright © 2009, Texas Instruments Incorporated

SLOS635 – NOVEMBER 2009 www.ti.com

As Table 4 indicates, most of the bass response is attenuated into a 4- $\Omega$  load, an 8- $\Omega$  load is adequate, headphone response is good, and drive into line level inputs (a home stereo for example) is exceptional.

#### **USING LOW-ESR CAPACITORS**

Low-ESR capacitors are recommended throughout this applications section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor.

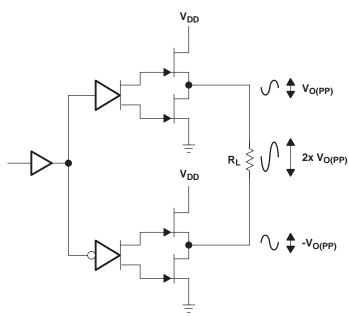

#### **BRIDGE-TIED LOAD vs SINGLE-ENDED LOAD**

Figure 30 shows a Class-AB audio power amplifier (APA) in a BTL configuration. The TPA6013A4 BTL amplifier consists of two Class-AB amplifiers driving both ends of the load. There are several potential benefits to this differential drive configuration, but, initially consider power to the load. The differential drive to the speaker means that as one side is slewing up, the other side is slewing down, and vice versa. This in effect doubles the voltage swing on the load as compared to a ground referenced load. Plugging  $2 \times V_{O(PP)}$  into the power equation, where voltage is squared, yields  $4 \times$  the output power from the same supply rail and load impedance (see Equation 5).

$$V_{(rms)} = \frac{V_{O(PP)}}{2\sqrt{2}}$$

$$Power = \frac{V_{(rms)}^{2}}{R_{L}}$$

(5)

Figure 30. Bridge-Tied Load Configuration

20

SLOS635 - NOVEMBER 2009 www.ti.com

In a typical computer sound channel operating at 5 V, bridging raises the power into an 8-Ω speaker from a singled-ended (SE, ground reference) limit of 250 mW to 1 W. In sound power that is a 6-dB improvement, which is loudness that can be heard. In addition to increased power there are frequency response concerns. Consider the single-supply SE configuration shown in Figure 31. A coupling capacitor is required to block the dc offset voltage from reaching the load. These capacitors can be quite large (approximately 33µF to 1000µF), so they tend to be expensive, heavy, occupy valuable PCB area, and have the additional drawback of limiting low-frequency performance of the system. This frequency limiting effect is due to the high-pass filter network created with the speaker impedance and the coupling capacitance and is calculated with Equation 6.

$$f_{(c)} = \frac{1}{2\pi R_L C_C} \tag{6}$$

For example, a 68-μF capacitor with an 8-Ω speaker would attenuate low frequencies below 293 Hz. The BTL configuration cancels the dc offsets, which eliminates the need for the blocking capacitors. Low-frequency performance is then limited only by the input network and speaker response. Cost and PCB space are also minimized by eliminating the bulky coupling capacitor.

Figure 31. Single-Ended Configuration and Frequency Response

Increasing power to the load does carry a penalty of increased internal power dissipation. The increased dissipation is understandable considering that the BTL configuration produces 4x the output power of the SE configuration. Internal dissipation versus output power is discussed further in the crest factor and thermal considerations section.

#### SINGLE-ENDED OPERATION

In SE mode (see Figure 31), the load is driven from the primary amplifier output for each channel (OUT+).

The amplifier switches single-ended operation when the SE/BTL terminal is held high. This puts the negative outputs in a high-impedance state, and effectively reduces the amplifier's gain by 6 dB.

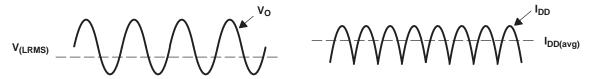

#### BTL AMPLIFIER EFFICIENCY

Class-AB amplifiers are inefficient. The primary cause of these inefficiencies is voltage drop across the output stage transistors. There are two components of the internal voltage drop. One is the headroom or dc voltage drop that varies inversely to output power. The second component is due to the sine-wave nature of the output. The total voltage drop can be calculated by subtracting the RMS value of the output voltage from V<sub>DD</sub>. The internal voltage drop multiplied by the RMS value of the supply current (IDD rms) determines the internal power dissipation of the amplifier.

An easy-to-use equation to calculate efficiency starts out as being equal to the ratio of power from the power supply to the power delivered to the load. To accurately calculate the RMS and average values of power in the load and in the amplifier, the current and voltage waveform shapes must first be understood (see Figure 32).

Copyright © 2009, Texas Instruments Incorporated Submit Documentation Feedback

Figure 32. Voltage and Current Waveforms for BTL Amplifiers

Although the voltages and currents for SE and BTL are sinusoidal in the load, currents from the supply are very different between SE and BTL configurations. In an SE application the current waveform is a half-wave rectified shape, whereas in BTL it is a full-wave rectified waveform. This means RMS conversion factors are different. Keep in mind that for most of the waveform both the push and pull transistors are not on at the same time, which supports the fact that each amplifier in the BTL device only draws current from the supply for half the waveform. The following equations are the basis for calculating amplifier efficiency.

Efficiency of a BTL amplifier

$$=\frac{P_L}{P_{SUP}}$$

Where:

$$P_L = \frac{V_L rms^2}{R_L}, \text{ and } V_{LRMS} = \frac{V_P}{\sqrt{2}}, \text{ therefore, } P_L = \frac{V_P^2}{2R_L}$$

and  $P_{SUP} = V_{DD} I_{DD} avg$  and  $I_{DD} avg = \frac{1}{\pi} \int_0^\pi \frac{V_P}{R_L} \sin(t) \, dt = \frac{1}{\pi} \times \frac{V_P}{R_L} \left[ \cos(t) \right]_0^\pi = \frac{2V_P}{\pi R_L}$  Therefore,

$$P_{SUP} = \frac{2 V_{DD} V_P}{\pi R_L}$$

(7)

substituting P<sub>L</sub> and P<sub>SUP</sub> into Equation 7,

Efficiency of a BTL amplifier

$$= \frac{\frac{V_P^2}{2 R_L}}{\frac{2 V_{DD} V_P}{\pi R_L}} = \frac{\pi V_P}{4 V_{DD}}$$

Where:

Therefore,

$$\eta_{BTL} = \frac{\pi \sqrt{2 P_L R_L}}{4 V_{DD}}$$

$V_{D} = \sqrt{2 P_{I} R_{I}}$

$P_L$  = Power delivered to load  $P_{SUP}$  = Power drawn from power supply  $V_{LRMS}$  = RMS voltage on BTL load  $R_L$  = Load resistance

$V_P$  = Peak voltage on BTL load  $I_{DD}$ avg = Average current drawn from the power supply  $V_{DD}$  = Power supply voltage  $\eta_{BTL}$  = Efficiency of a BTL amplifier

s for four different output power levels. Note that the efficiency

Table 5 employs Equation 8 to calculate efficiencies for four different output power levels. Note that the efficiency of the amplifier is quite low for lower power levels and rises sharply as power to the load is increased resulting in a nearly flat internal power dissipation over the normal operating range. Note that the internal dissipation at full output power is less than in the half power range. Calculating the efficiency for a specific system is the key to proper power supply design. For a stereo 1-W audio system with 8- $\Omega$  loads and a 5-V supply, the maximum draw on the power supply is almost 3.25 W.

SLOS635 - NOVEMBER 2009 www.ti.com

| Table 5. Efficiency vs Output Power | er in 5-V. 8-Ω BIL System | S |

|-------------------------------------|---------------------------|---|

|-------------------------------------|---------------------------|---|

| OUTPUT POWER<br>(W) | EFFICIENCY<br>(%) | PEAK VOLTAGE<br>(V) | INTERNAL DISSIPATION (W) |  |  |  |

|---------------------|-------------------|---------------------|--------------------------|--|--|--|

| 0.25                | 31.4              | 2.00                | 0.55                     |  |  |  |

| 0.50                | 44.4              | 2.83                | 0.62                     |  |  |  |

| 1.00                | 62.8              | 4.00                | 0.59                     |  |  |  |

| 1.25                | 70.2              | 4.47 <sup>(1)</sup> | 0.53                     |  |  |  |

<sup>(1)</sup> High peak voltages cause the THD to increase.

A final point to remember about Class-AB amplifiers (either SE or BTL) is how to manipulate the terms in the efficiency equation to utmost advantage when possible. Note that in equation 8, VDD is in the denominator. This indicates that as V<sub>DD</sub> goes down, efficiency goes up.

#### **CREST FACTOR AND THERMAL CONSIDERATIONS**

Class-AB power amplifiers dissipate a significant amount of heat in the package under normal operating conditions. A typical music CD requires 12 dB to 15 dB of dynamic range, or headroom above the average power output, to pass the loudest portions of the signal without distortion. In other words, music typically has a crest factor between 12 dB and 15 dB. When determining the optimal ambient operating temperature, the internal dissipated power at the average output power level must be used. From the TPA6013A4 data sheet, one can see that when the TPA6013A4 is operating from a 5-V supply into a 3- $\Omega$  speaker, that 4-W peaks are available. Use equation 9 to convert watts to dB.

$$P_{dB} = 10 Log \frac{P_W}{P_{ref}} = 10 Log \frac{4 W}{1 W} = 6 dB$$

(9)

Subtracting the headroom restriction to obtain the average listening level without distortion yields:

- 6 dB 15 dB = -9 dB (15-dB crest factor)

- 6 dB 12 dB = -6 dB (12-dB crest factor)

- 6 dB 9 dB = -3 dB (9-dB crest factor)

- 6 dB 6 dB = 0 dB (6-dB crest factor)

- 6 dB 3 dB = 3 dB (3-dB crest factor)

To convert dB back into watts use equation 10.

$$P_W = 10^{PdB/10} \times P_{ref}$$

- = 63 mW (18-db crest factor)

- = 125 mW (15-db crest factor)

- = 250 mW (12-db crest factor)

- = 500 mW (9-db crest factor)

- = 1000 mW (6-db crest factor)

- = 2000 mW (3-db crest factor)

(10)

This is valuable information to consider when attempting to estimate the heat dissipation requirements for the amplifier system. Comparing the worst case, which is 2 W of continuous power output with a 3-dB crest factor, against 12-dB and 15-dB applications significantly affects maximum ambient temperature ratings for the system. Using the power dissipation curves for a 5-V, 3-Ω system, the internal dissipation in the TPA6013A4 and maximum ambient temperatures is shown in Table 6.

#### Table 6. TPA6013A4 Power Rating, 5-V, 3-Ω Stereo

| AVERAGE OUTPUT POWER | POWER DISSIPATION (W/Channel)                                                 | MAXIMUM AMBIENT<br>TEMPERATURE                                                                                                                                               |

|----------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 W (3 dB)           | 1.7                                                                           | −3°C                                                                                                                                                                         |

| 1 W (6 dB)           | 1.6                                                                           | 6°C                                                                                                                                                                          |

| 500 mW (9 dB)        | 1.4                                                                           | 24°C                                                                                                                                                                         |

| 250 mW (12 dB)       | 1.1                                                                           | 51°C                                                                                                                                                                         |

| 125 mW (15 dB)       | 0.8                                                                           | 78°C                                                                                                                                                                         |

| 63 mW (18 dB)        | 0.6                                                                           | 96°C                                                                                                                                                                         |

|                      | 2 W (3 dB)<br>1 W (6 dB)<br>500 mW (9 dB)<br>250 mW (12 dB)<br>125 mW (15 dB) | AVERAGE OUTPUT POWER     (W/Channel)       2 W (3 dB)     1.7       1 W (6 dB)     1.6       500 mW (9 dB)     1.4       250 mW (12 dB)     1.1       125 mW (15 dB)     0.8 |

#### Table 7. TPA6013A4 Power Rating, 5-V, 8-Ω Stereo

| PEAK OUTPUT POWER<br>(W) | AVERAGE OUTPUT POWER        | POWER DISSIPATION<br>(W/Channel) | MAXIMUM AMBIENT<br>TEMPERATURE |

|--------------------------|-----------------------------|----------------------------------|--------------------------------|

| 2.5                      | 1250 mW (3-dB crest factor) | 0.55                             | 100°C                          |

| 2.5                      | 1000 mW (4-dB crest factor) | 0.62                             | 94°C                           |

| 2.5                      | 500 mW (7-dB crest factor)  | 0.59                             | 97°C                           |

| 2.5                      | 250 mW (10-dB crest factor) | 0.53                             | 102°C                          |

The maximum dissipated power  $(P_{D(max)})$  is reached at a much lower output power level for an 8- $\Omega$  load than for a 3- $\Omega$  load. As a result, this simple formula for calculating  $P_{D(max)}$  may be used for an 8- $\Omega$  application.

$$P_{D(max)} = \frac{2V_{DD}^2}{\pi^2 R_L} \tag{11}$$

However, in the case of a 3- $\Omega$  load, the  $P_{D(max)}$  occurs at a point well above the normal operating power level. The amplifier may therefore be operated at a higher ambient temperature than required by the  $P_{D(max)}$  formula for a 3- $\Omega$  load.

The maximum ambient temperature depends on the heat-sinking ability of the PCB system. The derating factor for the PWP package is shown in the *dissipation rating table*. Use equation 12 to convert this to  $\theta_{JA}$ .

$$\Theta_{JA} = \frac{1}{\text{Derating Factor}} = \frac{1}{0.022} = 45^{\circ}\text{C/W}$$

(12)

To calculate maximum ambient temperatures, first consider that the numbers from the dissipation graphs are per channel, so the dissipated power needs to be doubled for two channel operation. Given  $\theta_{JA}$ , the maximum allowable junction temperature, and the total internal dissipation, the maximum ambient temperature can be calculated using Equation 13. The maximum recommended junction temperature for the TPA6013A4 is 150°C. The internal dissipation figures are taken from the Power Dissipation vs Output Power graphs.

$$T_A Max = T_J Max - \Theta_{JA} P_D$$

= 150 - 45(0.6 × 2) = 96°C (15-dB crest factor) (13)

#### **NOTE**

Internal dissipation of 0.6 W is estimated for a 2-W system with 15-dB crest factor per channel.

Table 6 and Table 7 show that some applications require no airflow to keep junction temperatures in the specified range. The TPA6013A4 is designed with thermal protection that turns the device off when the junction temperature surpasses 150°C to prevent damage to the IC. Table 6 and Table 7 were calculated for maximum listening volume without distortion. When the output level is reduced the numbers in the table change significantly. Also, using  $8-\Omega$  speakers increases the thermal performance by increasing amplifier efficiency.

24

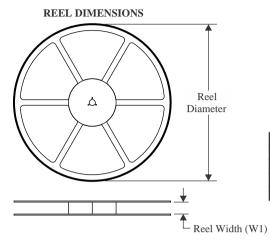

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

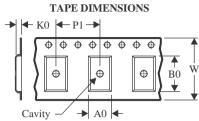

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

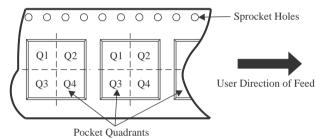

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA6013A4PWPR | HTSSOP          | PWP                | 24 | 2000 | 330.0                    | 16.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 16.0      | Q1               |

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

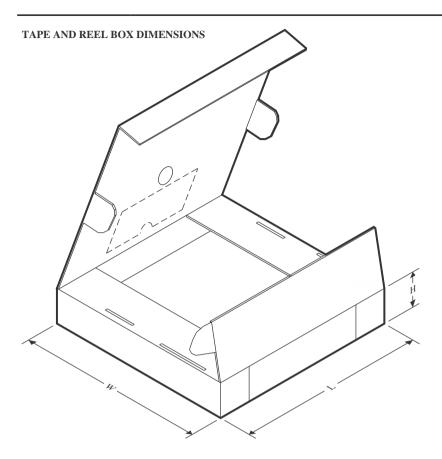

#### \*All dimensions are nominal

| Device        | Package Type Package Drawing |     | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|------------------------------|-----|------|------|-------------|------------|-------------|--|

| TPA6013A4PWPR | HTSSOP                       | PWP | 24   | 2000 | 356.0       | 356.0      | 35.0        |  |

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

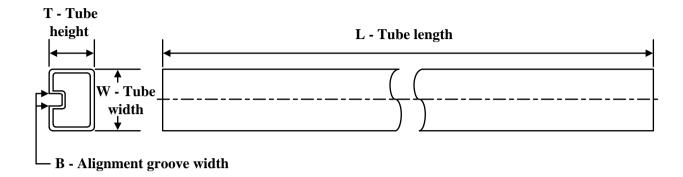

#### **TUBE**

#### \*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPA6013A4PWP | PWP          | HTSSOP       | 24   | 60  | 530    | 10.2   | 3600   | 3.5    |

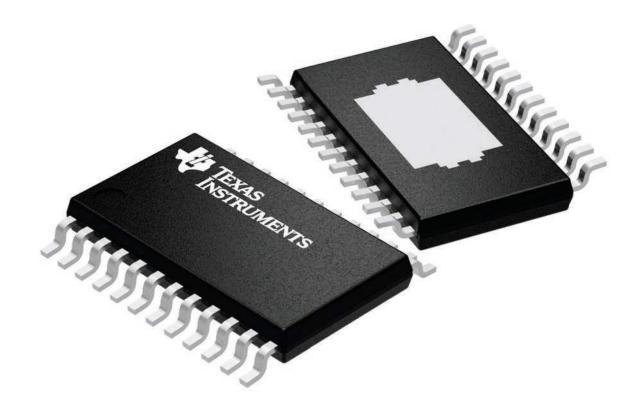

4.4 x 7.6, 0.65 mm pitch

PLASTIC SMALL OUTLINE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

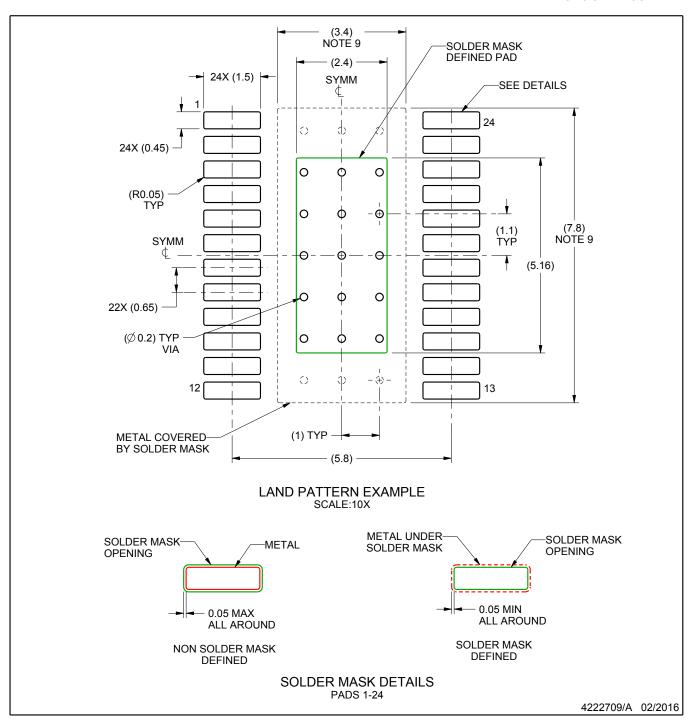

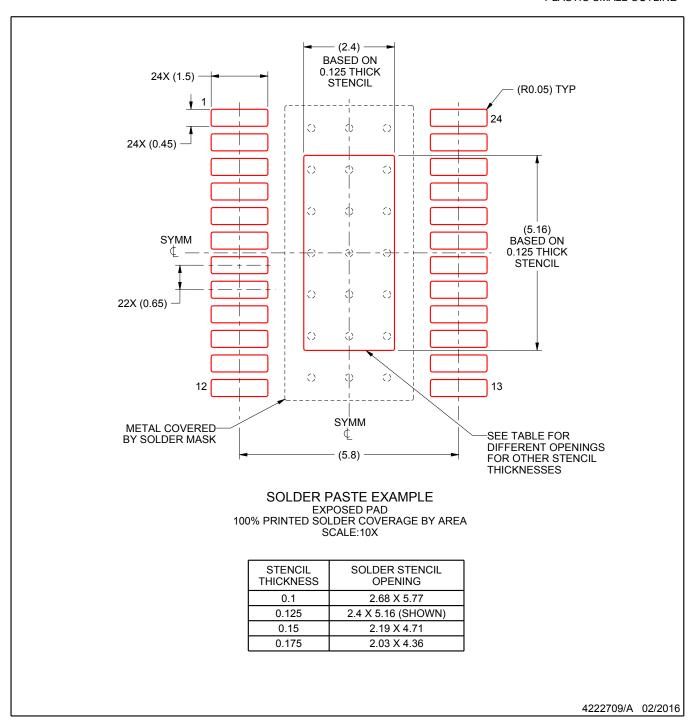

### PowerPAD™ TSSOP - 1.2 mm max height

PLASTIC SMALL OUTLINE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

- 5. Features may not be present and may vary.

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 11. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated